IND

О)

сл

оо сл

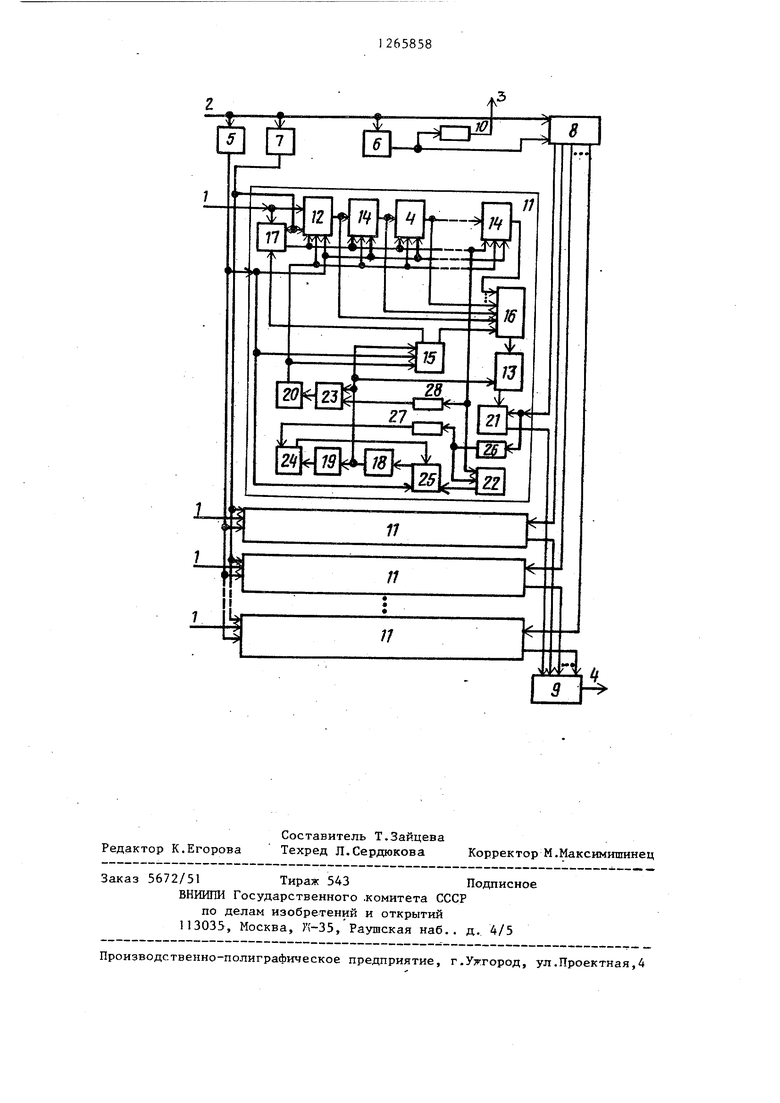

00 Изобретение относится к вычислительной технике, в частности к регистровьпч запоминающим устройствам. Целью изобретения является повышение быстродействия устройства. На чертеже изображена функциональ ная схема предлагаемого устройства. Устройство содержит информационные 1 и установочный 2 входы, тактовый 3 и информационный 4 выходы, фор мирователь 5 импульсов сброса, формирователь 6 тактовых импульсов, тай мер 7, распределитель 8 уровней напряжения, блок элементов ИЛИ 9, блок 10 задержки и блоки 11 памяти. Каждый блок 11 памяти содержит входной регистр 12 слова, выходной регистр 13 слова, регистры 14 сдвига, счетчик 15, селектор 16, формирователь 17 импульсов записи, первый 18 и второй 19 формирователи одиночных импульсов, формирователь 20 импульсов сдвига, элементы И 21-24 с перво го по четвертый, элемент ИЛИ 25, элементы 26-28 задержки с первого по третий. Устройство работает следующим образом. По переднему фронту импульса сбро са на входе 2 устанавливаются в исходное (нулевое) положение таймер 7, .распределитель 8 и запускается формирователь 5. По заднему фронту сбро са запускается таймер 7 и формирователь 6. Формирователь 5 формирует одиночный прямоугольный импульс (уровень логической 1), передний фронт кото рого задержан относительно переднего фронта импульса сброса. По импульсу с выхода формирователя 5 устанавливаются в исходное положение все блоки 11 памяти. По переднему фронту этого импульса в каждом блоке 11 памяти через регистр 12 с информационного входа 1 записывается параллельный двоичный код первоначальной информации, одновременно с этим записывается параллельный двоичный код первоначального момента времени, присутствующего на выходе таймера 7, а также устанавливаются в исходное нулевое положение все разряды регист ров 14, счетчика 15 и через элемент ИЛИ 25 запускается формирователь 18, Уровень логической 1 с выхода формирователя 18 поступает на вход блокировки регистра 13, разрешая запись 82 него через селектор 16 информации выхода регистра 12. Содержимое четчика 15 в этом случае остается ез изменений - равным нулю. По задему фронту импульса с выхода формиователя 5 вся информация из регистра 12 переписывается на выход регистра 13. По заднему фронту импульса на выходе формирователя 18 блокируется регистр 13. Длительность импульса сброса, поступающего на вход 2, выбирается с учетом времени задержки элементов, из которых изготовлено устройство, и времени полного выполнения описанных процессов. После запуска формирователь 6 начинает формировать непрерывную последовательность периодических прямоугольных импульсов, скважность, период и длительность которых выбираются минимальными с учетом времен задержек элементов, входящих в устройство. Эта последовательность импульсов поступает в распределитель 8,выставляющий уровень логической 1 на своем первом вьгкоде (счет слева направо), которьй снимается по переднему фронту следующего импульса с выхода формирователя 6, при этом появляется уровень логической 1 на следующем выходе распределителя 8, С выходов распределителя 8 на каждый блок 11 поочередно поступает импульс опроса (уровень логической 1), во время которого параллельный двоичньм код с выхода элемента И 21 через соответствующий из элементов ИЛИ 9 поступает на выход 4 устройства. Опрос каждого блока 11 производится неза-) висимо от записи в него новой информации. Запись информации в каждый блок 11 производится независимо от записи информации в соседний блок 11. Каждое информационное слово на выходе 4 представлено параллельным двоичным кодом, содержит код информации и код момента времени появления этой информации на соответствующем информационном входе 1 и сопровождается тактовым импульсом, поступающим с выхода формирователя 6 через блок 10 задержки на выход 3. Каждый блок 11 памяти работает следующим образом. Информация поступает со входа 1 на входы формирователя 17 и регистра 12, на другие входы которых с выхода таймера 7 постутшет-параллельный двоичный код момента текущего времени. При изменении любого информационного сигнала (уровня напряжения) на входе 1 формирователь 17 формирует одиночный прямоугольный . импульс записи (уровень логической 1), который появляется на его выходе только сразу же после изменения младшего разряда кода момента текущего времени (таким образом, точност момента времени изменения информации определяется младшим разрядом кода текущего времени).

Длительность импульса записи додж на быть больше длительности импульса с выхода формирователя 18 (например, в два того, чтобы в случае, если импульса записи и импульс опроса с выхода элемента 26 задержки при дут на элемент И 22 с задержкой, то формирователь 18 успеет сформировать импульс и тогда переписывание информационных слов в регистрах 12 и 14 будет продолжено после заднего фронта импульса с выхода формирователя 18, По переднему фронту импульса записи в регистр 12 записывается код изменившейся информации и код момента времени, когда произошло это изменение информации, а в регистр 14 сдвигается информация с выхода регистра 12.

По переднему фронту этого же импульса записи закрывается-элемент И 22 для прохождения через него импульса опроса.

Так как на входе элемента И 23 присутствует уровень логического О, поскольку нет импульса на выходе формирователя 18, то этот же импульс записи через элемент 28 задержки и элемент И 23 запускаетформирователь 20, который формирует одиночный прямоугольный (уровень логической 1) с минимальной длительностью, достаточной для переключения по его переднему фронту счетчика 15 (причем единица к содержимому счетчика 15) для сдвига ниформации, записанной в регистр 12 и регистры 14 на один регистр 14 вправо, а в освобождающийся при этом регистр 12 вписывается новый код информации (в последнем регистре 14, ин информация теряется). При этом код с выхода счетчика 13 поступает на вход селектора 16, который переключается

на выход следующего регистра 14 (одно и то же информационное слово будет присутствовать на входе регистра 13).

При считывании информации из любого блока 11 по переднему фронту импульса опроса информация через элемент И 21 с выхода регистра 13 поступает на вход элемента ИЛИ 9. Этот же импульс опроса через элемент 26 задержки и элемент ИЛИ 25 поступает на вход запуска формирователя 18. Последний формирует импульс, по переднему фронту которого-закрывается элемент И 23, снимается блокировка регистра 13, в счетчика 15 от содержащегоЬя в нем числа вычитается единица и запускается формирователь 19 В регистр 13 с выхода селектора 16 , вписьшается новое информационное слово из предыдущего регистра 14 или из регистра 12, которое через время задержки регистра 13 появляется на его информационном выходе.

Формирователь 19 формирует одиночный прямоугольный импульс (yfjoнень логической 1) с длительностью большей на несколько наносекунд длительности импульса записи плюс длительность импульса опроса. По импульсу с выхода формирователя 19 закрывается элемент И 24 для прохождения повторного импульса опроса с выхода элемента 27 задержки на вход формирователя 18.

Следующий импульс опроса с выхода элемента 26 задержки через открытый элемент И 22 и элемент ИЛИ 25 опять запускает формирователь 18, после чего весь описанный процесс повторяется.

Для нормального функционирования устройства длительность импульса опроса должна быть меньше длительности импульса записи, а также изменение информации на каждом входе 1 устройства должно происходить через интервал времени, не менее чем в три раза больший длительности импульса записи на выходе формирователя I7.

Формулаизобретения

Буферное запоминающее устройство, содержащее формирователь импульсов сброса, таймер, формирователь тактовых импульсов, распределитель уровней напряжения, входы запуска которых являются установочным входом устройства, блок задержки, вход которого соединен с выходом формирователя тактовых импульсов и тактовым входом распределителя уровней напряжения, а выход является тактовым выходом устройства, блок элементов ИЛИ, выход которого является информационным выходом устройства, и блоки памяти, каждый из которых состоит из регистров сдвига, входного регистра слова, формирователя импульсов записи, первого элемента И, элемента ИЛИ, пер .вого и второго элементов задержки, причем выход формирователя импульсов записи соединен с тактовым входом входного регистра слова, вход первого элемента задержки и первый вход первого элемента И каждого блока памяти подключены к одноименному выходу распределителя уровней напряжения выход первого элемента И каждого блока памяти соединен с одноименным входом блока элементов ИЛИ, первые входы формирователей импульсов записи и входных регистров слова подключены к выходу таймера, установочные входы входных регистров слова соединены с выходом формирователя импульсов сброса, вторые входы формирователя импульсов записи и входного регистра слова каждого блока памяти являются одноименным информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в каждьй блок памяти введены счетчик, селектор , выходной регистр слова, формирователь импульсов сдвига, формирователи одиночных импульсов, зглементы И с второго по четвертый и третий элемент задержки, причем информационные входы селектора соедине1Ш с выходами входного регистра слова и регистров сдвига, выход селектора подключей к входу выходного регистра слова, выход и вход блокировки которого соединены соответственно с вторым входом первого элемента И и выходом первого формирователя одиночного импульса, первым входом третьего элемента И, входом вьгчитания счетчика и входом второго формирователя одиночного импульса, выход которого подключен к iiepBOMy входу четвертого элемента И, второй вход которого соединен с выходом второго элемента задержки, вход которого подключен к выходу первого элемента задержки и прямому входу второго элемента И, выход которого соединен с первым входом элемента ИДИ, второй вход которого подключен к выходу четвертого элемента И, а выход - к входу первого формирователя одиночного импульса, второй вход третьего элемента И соединен с выходом третьего элемента задержки, а выход - с входом формирователя импульсов сдвига, выход которого подключен к управляющим входам регистров сдвига входного регистра слова и входу сложения счетчика, первый и второй выходы которого соединены соответственно с управляющим входом селектора и с входом блокировки формирователя импульсов записи, выход которого подключен к тактовым входам регистров сдвига,ин- версному входу второго элемента И и входу третьего элемента задержки,информационньй вход каждого последующего регистра сдвига соединен с выходом предыдущего регистра сдвига, а информационный вход первого регистра сдвига - с выходом входного регистра слова, установочные входь регистров сдвига и счетчика и третий вход элемента ИЛИ каждого блока памяти подключены к выходу формирователя импульсов сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Запоминающее устройство | 1985 |

|

SU1288759A1 |

| Устройство для тренировки памяти операторов | 1991 |

|

SU1824647A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть применено в устройствах для контроля электромагнитных контактных систем. Цель изобретения - повьшение быстродействия устройства. Устройство содер жит формирователь импульсов сброса, формирователь тактовых импульсов, таймер, распределитель уровней напряжения, блок элементов ИЛИ, блок задержки и блоки памяти, каждый из которых содержит регистры сдвига, входной регистр слова, элемент ИЛИ, первый элемент И, элементы задержки, фо формирователь импульсов записи и вновь введенные счетчик, селектор, формирователь импульсов сдвига, вы- ходной регистр слова, два формирователя одиночных импульсов, три элемента И. Повышение быстродействия достигается тем, что вновь введенные элементы обеспечивают подключение выхода очередного регистра сдвига через селектор к выходному регистру слова, сдвиг записанной 1Шформации и таким образом подготавливают блок памяти к записи в него новой информации. 1 ил.

| Буферное запоминающее устройство | 1983 |

|

SU1109798A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1169018A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-23—Публикация

1985-02-05—Подача