11, две группы селекторов 12, 13, две группы блоков 14, 15 коррекции, формирователь 17 одиночного импульс блок 16 коррекции, группу элементов ИЛИ 18, элемент 20 задержки, элемент ИЛИ 21 и блок 19 местного управления, содержащий группы элемен- той И 22, дешифраторы 25, элементы ШШ-НЕ 23, группу элементов 24 задержки и элементы ИЛИ 26. Записы1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в многопроцессорных вычислительных комплексах.

Цель изобретения - повышение надежности устройства.

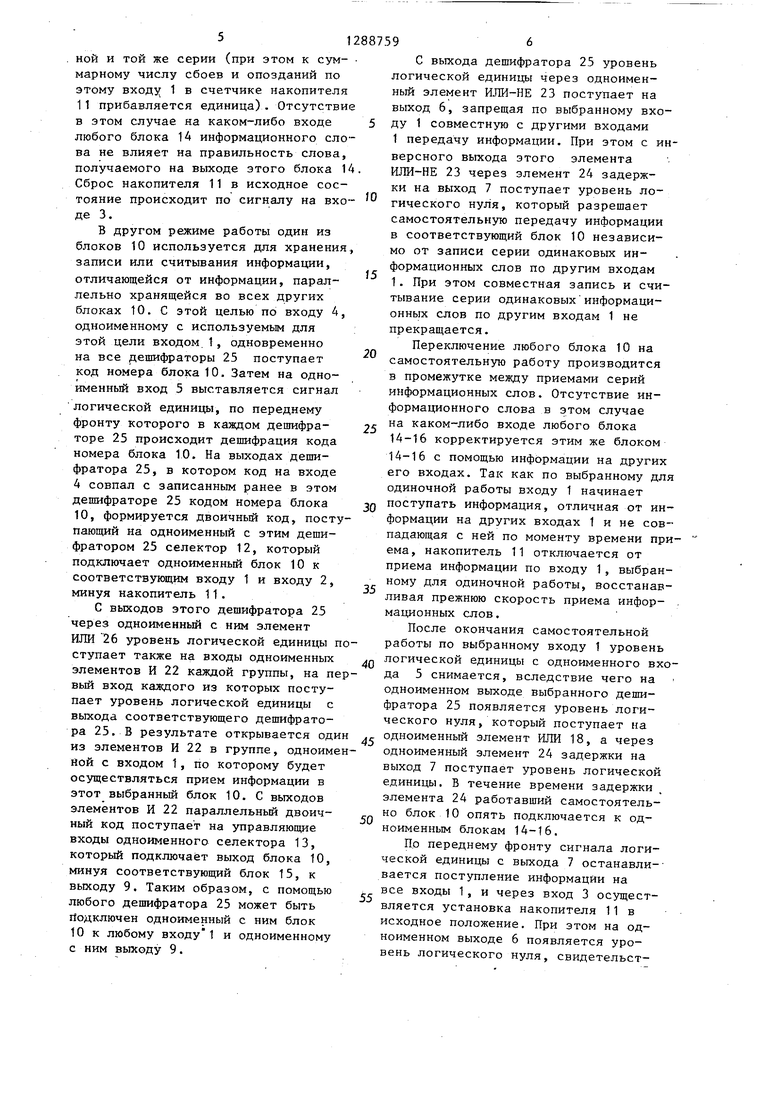

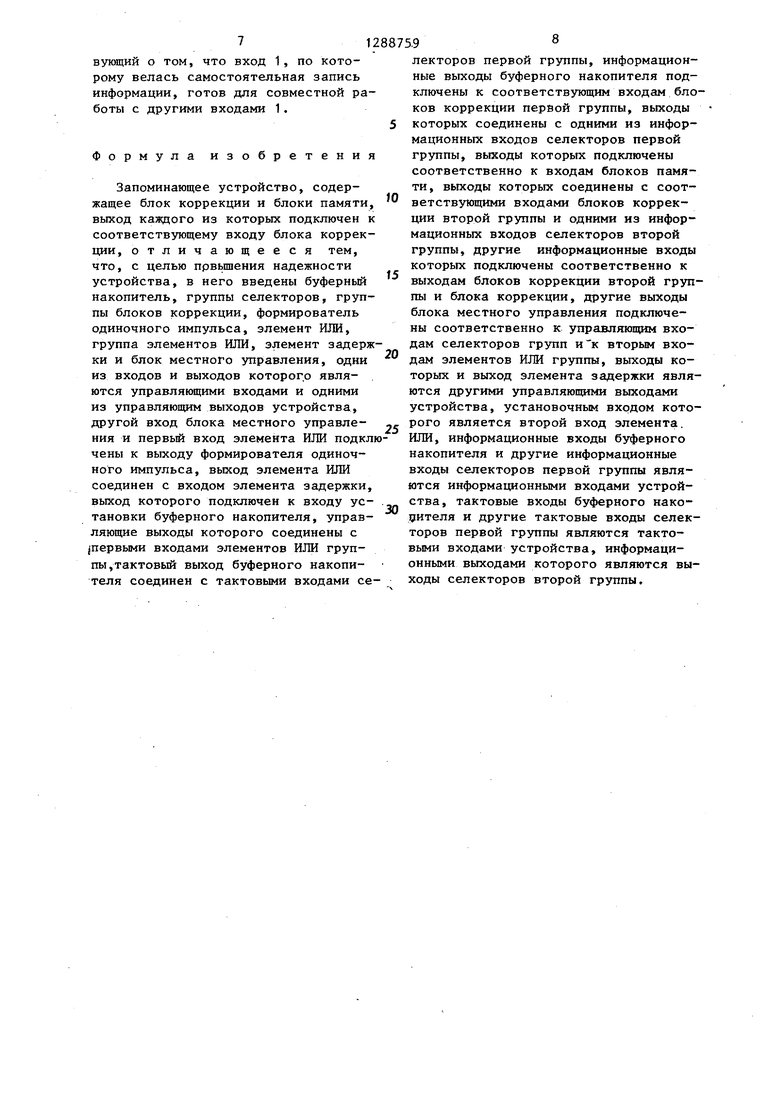

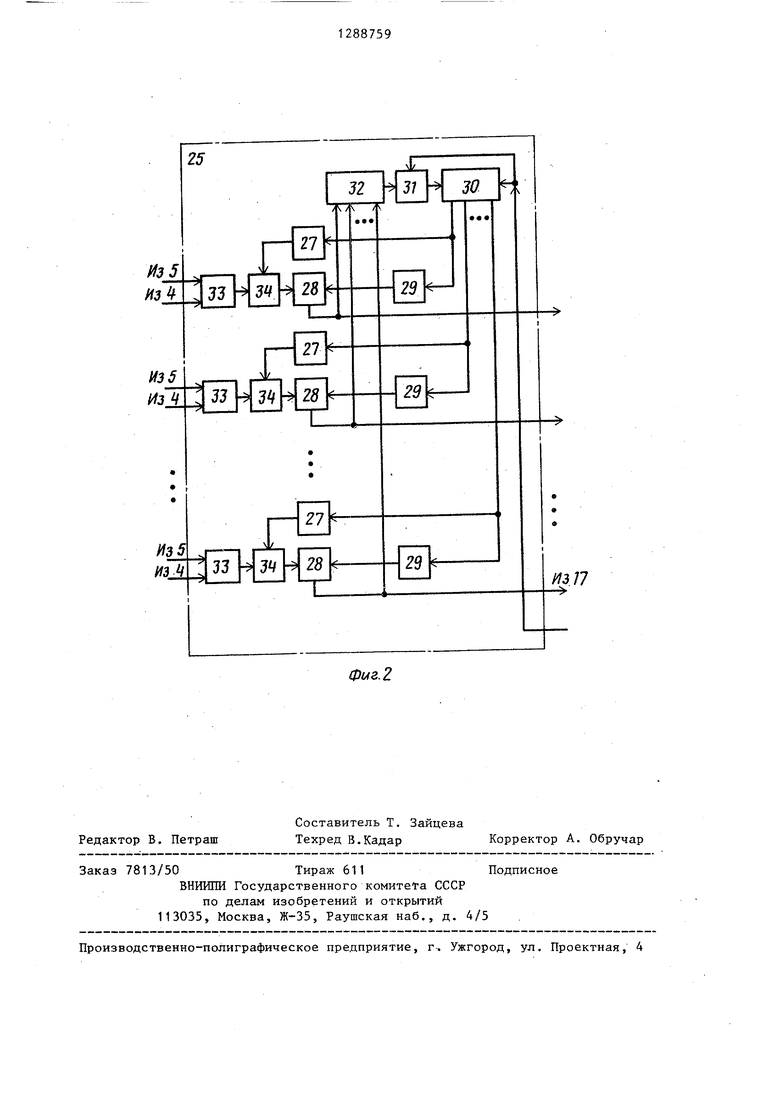

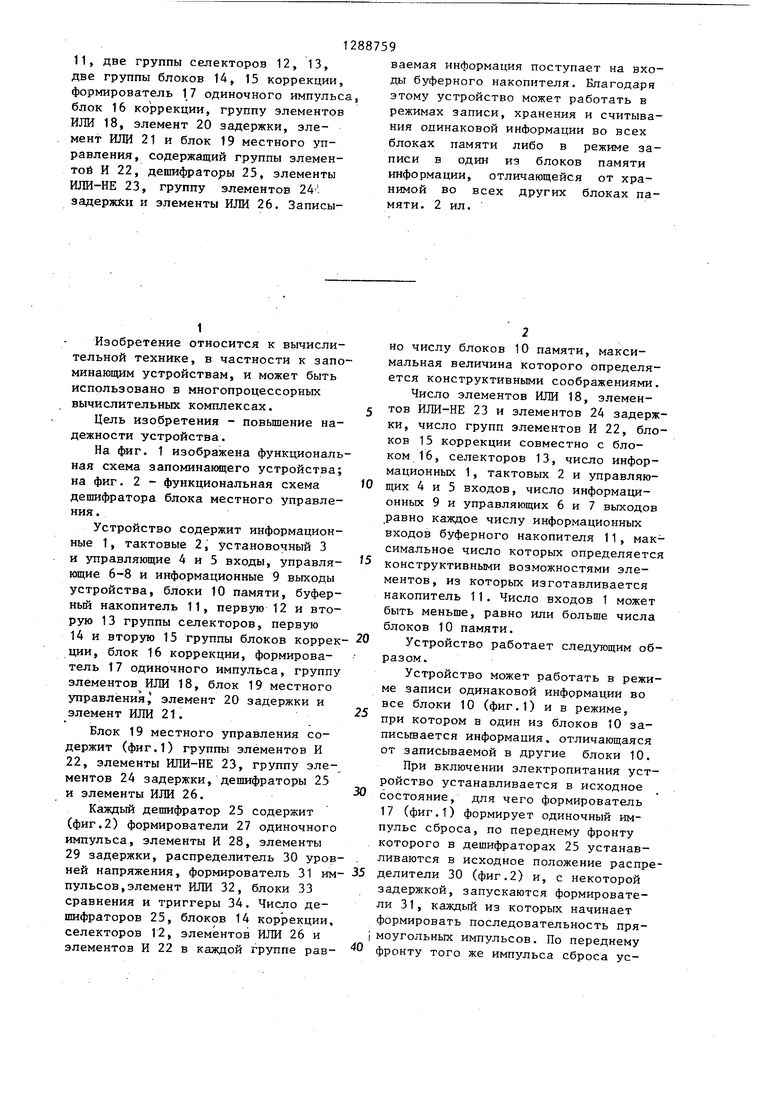

На фиг. 1 изображена функциональная схема запоминающего устройства; на фиг. 2 - функциональная схема дешифратора блока местного управления.

Устройство содержит информационные 1, тактовые 2, установочный 3 и управляющие 4 и 5 входы, управляющие 6-8 и информационные 9 выходы устройства, блоки 10 памяти, буферный накопитель 11, первую 12 и вторую 13 группы селекторов, первую 14 и вторую 15 группы блоков коррекции, блок 16 коррекции, формирователь 17 одиночного импульса, группу элементов ИЛИ 18, блок 19 местного управления, элемент 20 задержки и элемент ИЛИ 21.

Блок 19 местного управления содержит (фиг.1) группы элементов И 22, элементы РШИ-НЕ 23, группу элементов 24 задержки, дешифраторы 25 и элементы ИЛИ 26.

Каждый дешифратор 25 содержит (фиг.2) формирователи 27 одиночного импульса, элементы И 28, элементы 29 задержки, распределитель 30 уровней напряжения, формирователь 31 импульсов, элемент ШШ 32, блоки 33 сравнения и триггеры 34. Число дешифраторов 25, блоков 14 коррекции, селекторов 12, элементов ИЛИ 26 и элементов И 22 з каждой группе равваемая информация поступает на входы буферного накопителя. Благодаря этому устройство может работать в режимах записи, хранения и считывания одинаковой информации во всех блоках памяти либо в режиме записи в один из блоков памяти информации, отличающейся от хранимой во всех других блоках памяти. 2 ил.

но числу блоков 10 памяти, максимальная величина которого определяется конструктивными соображениями.

Число элементов ИЛИ 18, элемен- тов ИЛИ-НЕ 23 и элементов 24 задержки, число групп элементов И 22, блоков 15 коррекции совместно с блоком 16, селекторов 13, число информационных 1, тактовых 2 и управляю- щик 4 и 5 входов, число информационных 9 и управляющих 6 и 7 выходов равно каждое числу информационных входов буферного накопителя 11, максимальное число которых определяется конструктивными возможностями элементов, из которых изготавливается накопитель 11. Число входов 1 может быть меньше, равно или больше числа блоков 10 памяти.

Устройство работает следующим образом.

Устройство может работать в режиме записи одинаковой информации во все блоки 10 (фиг.1) и в режиме, при котором в один из блоков 10 за- письшается информация, отличающаяся от записываемой в другие блоки 10.

При включении электропитания устройство устанавливается в исходное

состояние, для чего формирователь

17 (фиг.1) формирует одиночный импульс сброса, по переднему фронту которого в дешифраторах 25 устанавливаются в исходное положение распределители 30 (фиг.2) и, с некоторой задержкой, запускаются формирователи 31, каждый из которых начинает формировать последовательность пря- i моугольных импульсов. По переднему

фронту того же импульса сброса устанавливается в исходное состояние накопитель 11, при этом на всех выходах 6 устанавливаются уровни логического нуля, а на вькодах 7 - логической единицы.

Импульс сброса поступает на выход 8, в результате чего начинают подаваться сигналы на входы 1 и 2 устройства. По каждому входу 1 поступает информация параллельным двоичным кодом (самокорректирующим или несамокорректирующим) в виде информационных слов, каждое из которьл содержит байты адреса ячейки блока 10, байты информации, разряд операции (при наличии единицы в этом разряде информация записывается в блок 10, а при наличии нуля в этом разряде - считывается из блока 10),

Каждое информационное слово записывается в накопитель 11 по переднему фронту тактового импульса, поступившего одновременно на одноименный вход 2. При этом на одноименном выходе 6 появляется уровень логической единицы, запрещая по этому входу 1 запись следующего информационного слова. Запись каждого информационного слова по входу 1 производится независимо от записи по другим входам 1.

Рассмотрим работу устройства в ржиме записи одинаковой информации . по всем входам 1.

После записи последнего по времени информационного слова серия одинаковых слов поступает на каждый блок 14 с выходов накопителя 11, в каждом из блоков 14 исправляются ошибки (если они имеются) путем сравнения между собой всех записываемых информационных слов одной сери а также путем определения контрольных разрядов и сравнения их с соответствующими контрольными разрядами (если они имеются) в записываемых информационных словах (если информация представлена несамокорректирующим кодом) или путем самокор- ректировл и (если информация представлена самокорректирующим кодом). Откорректированное информационное слово с выхода каждого блока 14 через одноименньм селектор 12 (на управляющих входах которого присутствуют уровни логического нуля) поступает на входы одноименного блока 10. При этом на тактовый вход блоO

5

0

5

ка 10 поступает с выхода накопителя 11 через селектор 12 тактовый импульс, по переднему фронту которого (если в разряде операции информационного слова присутствует единица) записываются в блок 10 байты информации по адресу, код кo opoгo содержится в адресной части этого информационного слова (если в разряде операции присутствует нуль, то считывается информация из блока 10 по тому же адресу). Таким образом, во все блоки 10 одновременно записывается (или считывается) одинаковая информация по одинаковым адресам.

С выходов каждого блока 10 информационное слово поступает на одноименные входы блока 16 и блоков 15. С выходов блока 16 и блоков 15 откорректированное слово через одноименный селектор 13 (на всех управляющих входах селекторов 13 присутствует к код логического нуля) поступает на вьтход 9. На всех выходах 9 в этом случае появляются одинаковые информационные слова.

Функционирование блока 16 и блоков 15 аналогично функционированию блока 14.

После появления импульса на тактовом выходе накопителя 11 на выходах 6 появляются уровни логического нуля, разрешая запись в накопи- тели 11 следукнцей серии информационных слов. Если по какому-либо из входов 1 начинают поступать систематические или случайные ошибки в одном и том же информационном слове разных серий или если это информационное слово в разных сериях систематически, случайно запаздывает свыше заранее заложенной в накопителе 11 допустимой величины, то прием информации по этому входу 1 через допустимое суммарное количество сбоев и опозданий прекращается, а уровень логической единицы с одноименного выхода 6 не снимается, запрещая передачу информации в устройство по этому входу 1.

В случае одноразового опоздания поступления информационного слова по входу 1 свыше допустимой величины накопитель 11 прекращает ожидание этого слова и переписывает на свои выходы уже поступившие в устройство остальные информационные слова од0

0

5

0

5

ной и той же серии (при этом к сум- марному числу сбоев и опозданий по этому входх 1 в счетчике накопителя 11 прибавляется единица). Отсутствие в этом случае на каком-либо входе любого блока 14 информационного слова не влияет на правильность слова, получаемого на выходе этого блока 14 Сброс накопителя 11 в исходное состояние происходит по сигналу на входе 3.

В другом режиме работы один из блоков 10 используется для хранения записи или считывания информации, отличающейся от информации, параллельно хранящейся во всех других блоках 10. С этой целью по входу 4, одноименному с используемым для этой цели входом.1, одновременно на все дешифраторы 25 поступает код номера блока 10. Затем на одноименный вход 5 выставляется сигнал логической единицы, по переднему фронту которого в каждом дешифраторе 25 происходит дешифрация кода номера блока 10. На выходах дешифратора 25, в котором код на входе 4 совпал с записанным ранее в этом дешифраторе 25 кодом номера блока 10, формируется двоичный код, поступающий на одноименный с этим дешифратором 25 селектор 12, который подключает одноименный блок 10 к соответствукнцим входу 1 и входу 2, минуя накопитель 11.

С выходов этого дешифратора 25 через одноименный с ним элемент ИЛИ 26 уровень логической единицы пступает также на входы одноименных элементов И 22 каждой группы, на певый вход каждого из которых поступает уровень логической единицы с выхода соответствующего дешифратора 25. В результате открывается оди из элементов И 22 в группе, одноименой с входом 1, по которому будет осуществляться прием информации в этот выбранный блок 10. С выходов элементов И 22 параллельный двоичный код поступает на управляющие входы одноименного селектора 13, который подключает выход блока 10, минуя соответствующий блок 15, к выходу 9. Таким образом, с помощью любого дешифратора 25 может быть Подключен одноименный с ним блок 10 к любому входу 1 и одноименному с ним выходу 9.

5

0

5

0

5

0

5

0

5

С выхода дешифратора 25 уровень логической единицы через одноименный элемент ИЛИ-НЕ 23 поступает на выход 6, запрещая по выбранному входу 1 совместную с другими входами 1 передачу информации. При этом с инверсного выхода этого элемента ИЛИ-НЕ 23 через элемент 24 задержки на выход 7 поступает уровень логического нуля, который разрешает самостоятельную передачу информации в соответствующий блок 10 независимо от записи серии одинаковых информационных слов по другим входам 1. При этом совместная запись и считывание серии одинаковых информационных слов по другим входам 1 не прекращается.

Переключение любого блока 10 на самостоятельную работу производится в промежутке между приемами серий информационных слов. Отсутствие информационного слова в этом случае на каком-либо входе любого блока 14-16 корректируется этим же блоком 14-16 с помощью информации на других его входах. Так как по выбранному для одиночной работы входу 1 начинает поступать информация, отличная от информации на других входах 1 и не совпадающая с ней по моменту времени приема, накопитель 11 отключается от приема информации по входу 1, выбранному для одиночной работы, восстанавливая прежнюю скорость приема информационных слов.

После окончания самостоятельной работы по выбранному входу 1 уровень логической единицы с одноименного входа 5 снимается, вследствие чего на одноименном выходе выбранного дешифратора 25 появляется уровень логического нуля, который поступает на одноименный элемент ИЛИ 18, а через одноименный элемент 24 задержки на выход 7 поступает уровень логической единицы. В течение времени задержки элемента 24 работавший самостоятельно блок 10 опять подключается к одноименным блокам 14-16.

По переднему фронту сигнала логической единицы с выхода 7 останавли- вается поступление информации на все входы 1, и через вход 3 осуществляется установка накопителя 11 в исходное положение. При этом на одноименном выходе 6 появляется уровень логического нуля, свидетельствукиций о том, что вход 1, по которому велась самостоятельная запись информации, готов для совместной работы с другими входами 1.

Формула изобретения

Запоминающее устройство, содержащее блок коррекции и блоки памяти, выход каждого из которых подключен к соответствующему входу блока коррекции, отличающееся тем, что, с целью првьппения надежности устройства, в него введены буферный накопитель, группы селекторов, группы блоков коррекции, формирователь одиночного импульса, элемент ИЛИ, группа элементов ИЛИ, элемент задержки и блок местного управления, одни из входов и выходов которого являются управляющими входами и одними из управляющим выходов устройства, другой вход блока местного управления и первый вход элемента ИЛИ подключены к выходу формирователя одиночного импульса, выход элемента ИЖ соединен с входом элемента задержки, выход которого подключен к входу установки буферного накопителя, управляющие выходы которого соединены с первьми входами элементов ИЛИ группы,тактовый выход буферного накопителя соединен с тактовыми входами се

5

0

5

0

лекторов первой группы, информационные выходы буферного накопителя подключены к соответствующим входам блоков коррекции первой группы, выходы которых соединены с одними из информационных входов селекторов первой группы, выходы которых подключены соответственно к входам блоков памяти, выходы которых соединены с соответствующими входами блоков коррекции второй группы и одними из информационных входов селекторов второй группы, другие информационные входы которых подключены соответственно к выходам блоков коррекции второй группы и блока коррекции, другие выходы блока местного управления подключены соответственно к управляющим входам селекторов групп и к вторым входам элементов ИЛИ группы, выходы которых и выход элемента задержки являются другими управляюпщми выходами устройства, установочным входом которого является второй вход элемента. ИЛИ, информационные входы буферного накопителя и другие информационные входы селекторов первой группы являются информационными входами устройства, тактовые входы буферного нако- дителя и другие тактовые входы селекторов первой группы являются тактовыми входами устройства, информационными выходами которого являются выходы селекторов второй группы.

Редактор В. Петраш

Составитель Т. Зайцева

Техред В.Кадар Корректор А. Обручар

Заказ 7813/50

l,um.m, Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул Проёктная7А

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1474742A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1265858A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Буферное запоминающее устройство | 1985 |

|

SU1272357A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1985 |

|

SU1257709A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

Изобретение относится к вычислительной технике, в частности, к запоминающим устройствам, и может быть применено в многопроцессорных вычислительных комплексах. Целью изобретения является повышение надежности устройства. Оно содержит -блоки 10 памяти, буферный накопитель fl1 (Л ю 00 00 сд со

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Резервированное запоминающее устройство | 1976 |

|

SU585549A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-02-07—Публикация

1985-08-15—Подача