SbC

(/)

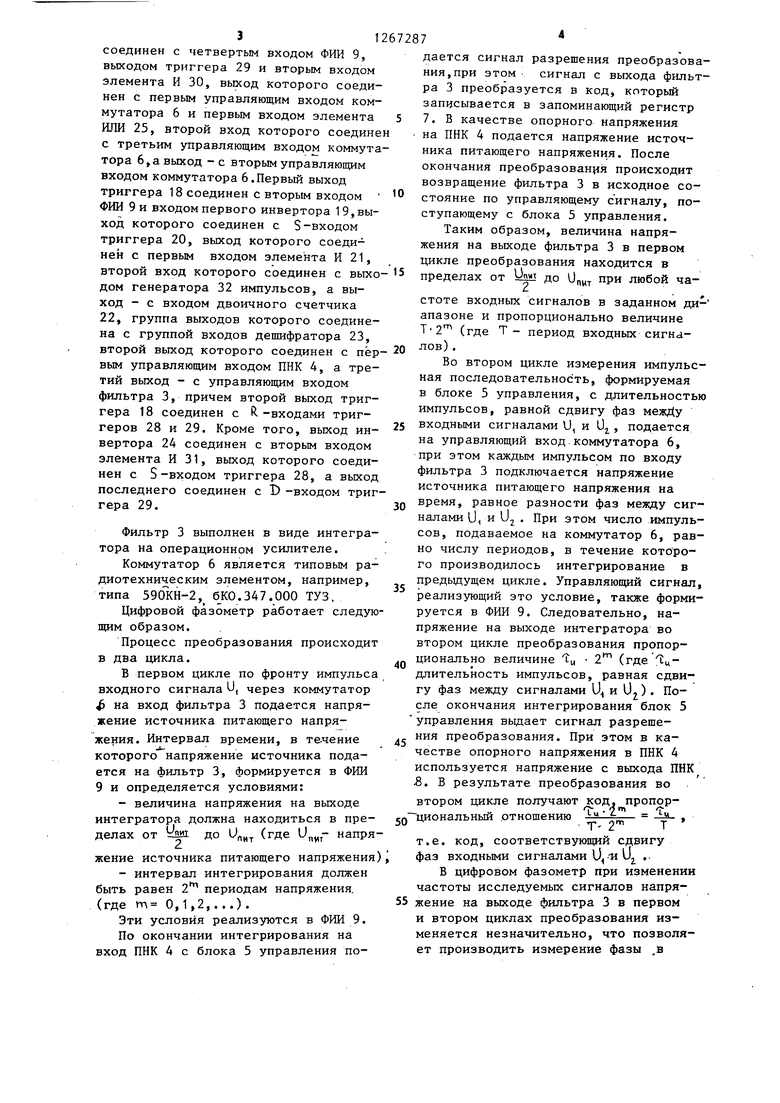

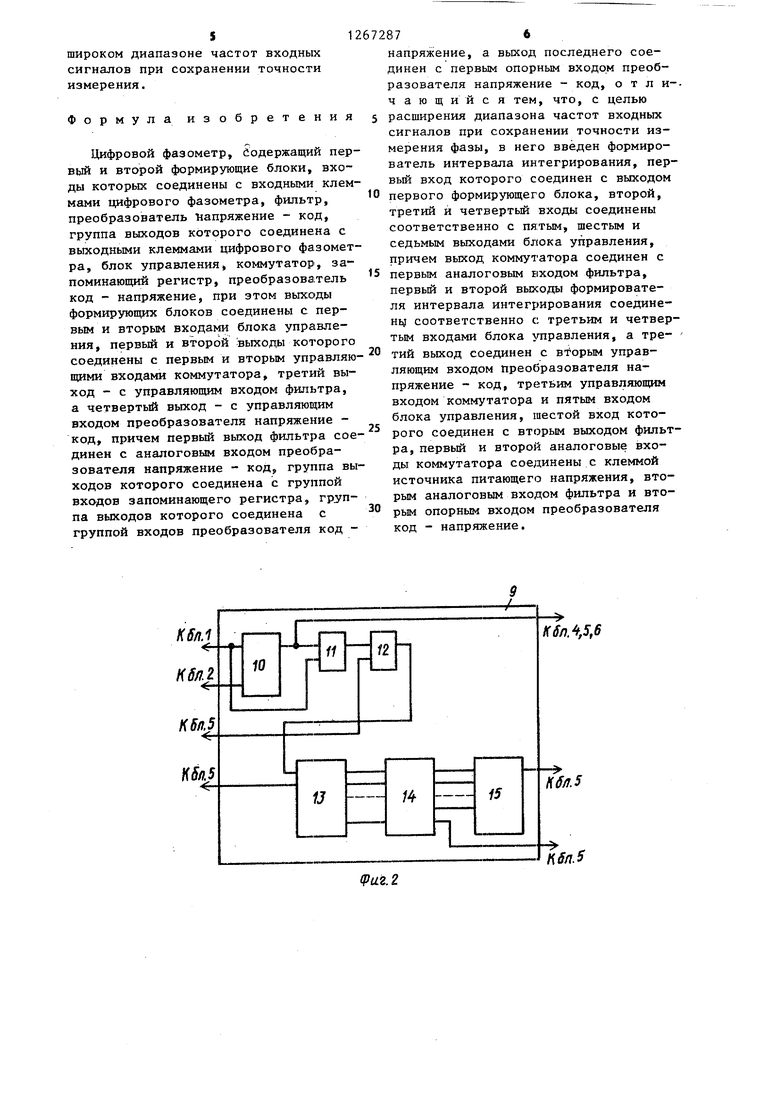

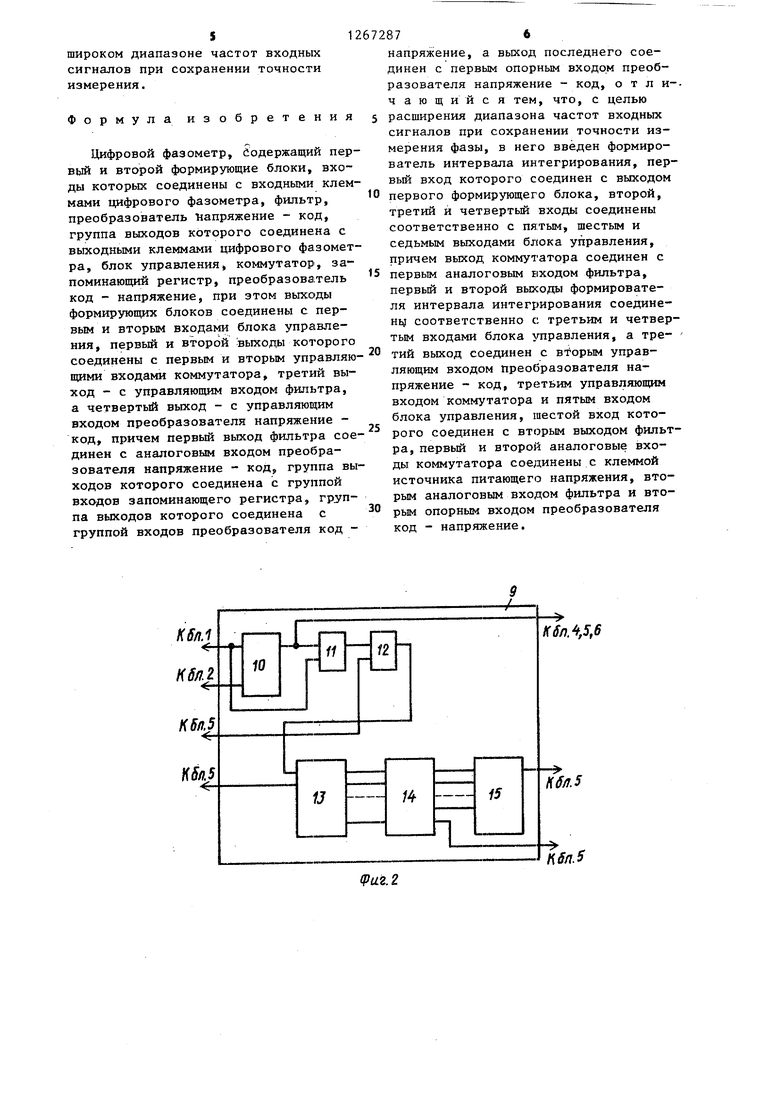

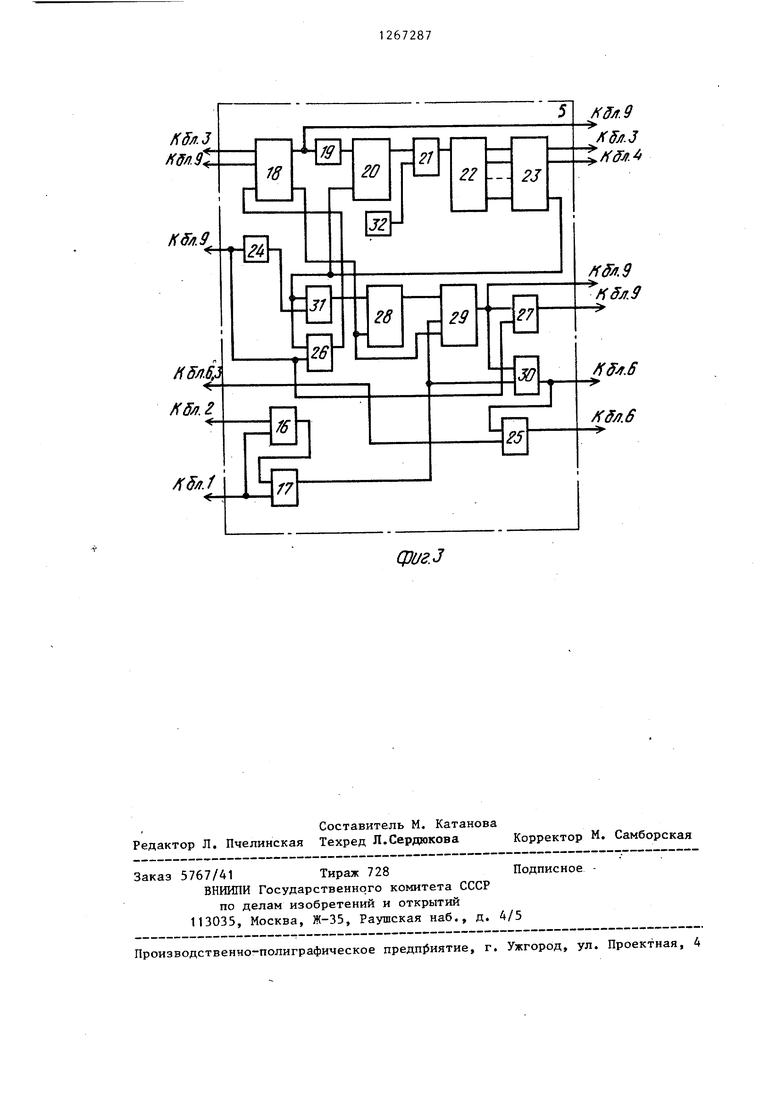

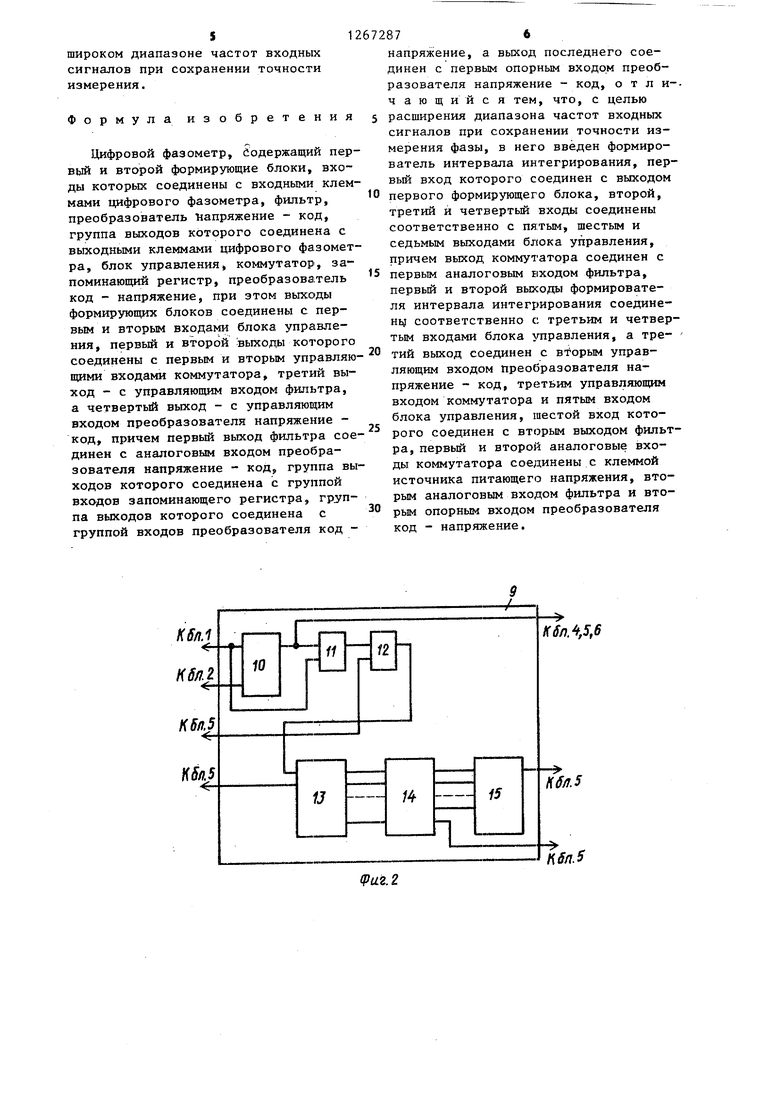

Фаг.1 t Изобретение относится к измерительной технике и может быть исполь зовано в информационно-измерительH1JX системах. Цель изобретения - расширение диапазона часточ входных сигналов при сохранении точности измерения фазы. На Фиг. 1 представлена функциональная схема цифрового фазометраJ на фиг. 2 - функциональная схема формирователя интервала интегрирова ния на фиг. 3 - функциональная схе ма блока управления. Цифровой фазометр, содержит формирующие блоки 1 и 2, фильтр 3, пре образователь 4 напряжение - код (ПН блок 5 управления, коммутатор 6, за поминающий регистр 7, преобразовате 8 код - напряжение (ПКН) и формиров тель 9 интервала интегрирования. Вы ходы формирующих блоков 1 и 2 соеди нены соответственно с первым и.вторым входами блока 5 управления, пер вый и второй выходы которого соединены с первым и вторым управляющими входами коммутатора 6, третий вьпсод с управляющим входом фильтра 3, а четвертьй выход - с управляющим вхо дом ПНК 4. Выход коммутатора б соединен с первым аналоговьм входом фильтра 3, первый выход которого соединен с аналоговьпу входом ПНК 4, группа выходов которого соединена с группой входов запоминающего регистра 7, а группа выходов последнего соединена с группой входов ПКН 8, выход которого соединен с первым опорным входом ПНК 4. Первый вход формирователя 9 интервала интегрирования (ФИИ) соединен с выходом формирующего блока 1, второйд третий и четвертьй входы соединены соответственно с пятым, шестым и седьмым выходами- блока 5 управления, при чем первый и второй выходы ФШ 9 соединены соответственно с третьим и четвертым входами блока 5 управления а третий выход соединен со вторым управляющим входом ПНК 4, третьим управляющим входом коммутатора 6 и пятым входом блока 5 управления, тестой вход которого соединен с вторым выходом фильтра 3. Первый и второй аналоговые входы коммутатора Ь соединен е клеммой источника питающего напряжения, вторым аналоговым входом фильтра 3j BTopBiM опорным вхо87ПКН 8 и опорным входом ПНК ФИИ 9 может содержать, например, триггер 10, элемент И 11, первый элемент ИЛИ 12, реверсивный счетчик 13, дешифратор 14 и второй элемент ИЛИ 15. При этом на J-вход триггера 10 и первый вход элемента И 11 поступает сигнал с выхода формирующего блока 1, на R-вход триггера 10 сигнал с пятого выхода блока 5 управления. С выхода триггера -10 сигнал поступает на третий управляющий вход коммутатора 6 и на второй вход элемента И 11J выход которого соединен с первым входом элемента ИЛИ 12, второй вход которого соединен с шестым выходом блока 5 правления, а вьсходс С-входом реверсивного счетчика 13, управляющий вход которого соединен с седьмым выходом блока 5 управления. Выходы реверсивного счетчика 13 соединены с входами дешифратора 14, выходы которого соединены с входами элемента ИЛИ 15 и с четвертым входом блока 5 управления. Выход элемента ИЛИ 15 соединен с третьим входом блока 5 управления. Блок 5 управления (фиг.З) может состоять из первого элемента И 16j входы которого соединены с выходами формирующих блоков 1 и 2, второго элемента И 17, первый вход которого соединен с выходом формирующего блока 1 , первого триггера 18, первого инвертора 19, второго триггера 20, третьего элемента И 21, двоичного счетчика 22, дешифратора 23, второго инвертора 24 элемента ИЛИ 25, четвертого 26 и пятого 27 элементов И, третьего 28 и четвертого 29 триггеров, шестого 30 и седьмого 31 элементов И и генератора 32 тактовых импульсов. Выход элемента И 16 соединен с вторым входом элемента И 17, выход которого соединен с :С-входом четвертого триггера 29 и первым входом элемента И 30, первого триггера 18 соединен с вторым выходом фильтра 3, С-вход .с первым выходом ФИИ 9, R -вход с выходом элемента И 26, первый вход которого соединен с первым выходом дешифратора 23, первым входом элемента И 31 и R-входом триггера: 20, а второй вход - с вторым выходом ФИИ 9, входом инвертора 24 и первым входом элемента И 27, второй вход которого 31 соединен с четвертым входом ФИИ 9, выходом триггера 29 и вторым входом элемента И 30, выход которого соединен с первым управляющим входом коммутатора 6 и первым входом элемента ИЛИ 25, второй вход которого соедине с третьим управляющим входом коммута тора 6, а выход -с вторым управляющим входом коммутатора 6.Первый выход триггера 18 соединен с вторым входом ФИИ 9 и входом первого инвертора 19,выход которого соединен с S-входом триггера 20, выход которого соединен с первым входом элемента И 21, второй вход которого соединен с выхо дом генератора 32 импульсов, а выход - с входом двоичного счетчика 22, группа выходов которого соединена с группой входов дешифратора 23, второй выход которого соединен с пёр вым управляющим входом ПНК 4, а третий выход - с управляющим входом фильтра 3, причем второй выход триггера 18 соединен с -входами триггеров 28 и 29. Кроме того, выход инвертора 24 соединен с вторым входом элемента И 31, выход которого соединен с S-входом триггера 28, а выход последнего соединен с Г) -входом триг гера 29. Фильтр 3 выполнен в виде интегратора на операционном усилителе. Коммутатор 6 является типовым радиотехническим элементом, например, типа 590кН-2, бКО.347.000 ТУЗ. Цифровой фазометр работает следую щим образом. Процесс преобразования происходит в два цикла. В первом цикле по фронту импульса входного сигнала U, через коммутатор на вход фильтра 3 подается напряжение источника питающего напряжения. Интервал времени, в течение которого напряжение источника подается на фильтр 3, формируется в ФИИ 9 и определяется условиями: -величина напряжения на выходе интегратора должна находиться в пределах от tW до Un (где и„„- напря жение источника питающего напряжения -интервал интегрирования должен быть равен 2 периодам напряжения, (где т 0,1,2,...). Эти условия реализуются в ФИИ 9. По окончании интегрирования на вход ПНК 4 с блока 5 управления по7дается сигнал разрешения преобразования, при этом сигнал с выхода фильтра 3 преобразуется в код который записывается в запоминающий регистр 7. В качестве опорного напряжения на ПНК 4 подается напряжение источника питающего напряжения. После окончания преобразован{1я происходит возвращение фильтра 3 в исходное состояние по управляющему сигналу, поступающему с блока 5 управления. Таким образом, величина напряжения на выходе фильтра 3 в первом цикле преобразования находится в пределах от Уш до при любой частоте входных сигналов в заданном диапазоне и пропорционально величине Т2 (где Т- период входных сигналов) . Во втором цикле измерения импульсная последовательность, формируемая в блоке 5 управления, с длительностью импульсов, равной сдвигу фаз межДу входными сигналами U, и Uj, подается на управляющий вход коммутатора 6, при этом каждым импульсом по входу фильтра 3 подключается напряжение источника питающего напряжения на время, равное разности фаз между сигналами и, и Uj. При этом число импульсов, подаваемое на коммутатор 6, равно числу периодов, в течение которого производилось интегрирование в предыдущем цикле. Управляющий сигнал, реализующий это условие, также формируется в ФИИ 9. Следовательно, напряжение на выходе интегратора во втором цикле преобразования пропорционально величине м 2 (где Тцдлительность импульсов, равная сдвигу фаз между сигналами Ц и и, ). После окончания интегрирования блок 5 управления вьщает сигнал разрешения преобразования. При этом в качестве опорного напряжения в ПНК 4 используется напряжение с выхода ПНК S. В результате преобразования во втором цикле получают пропорциональный отношению - т.е. код, соответствующий сдвигу фаз входными сигналами Ц .-и Uj , В цифровом фазометр при изменении частоты исследуемых сигналов напряжение на выходе фильтра 3 в первом и втором циклах преобразования изменяется незначительно, что позволяет производить измерение фазы в широком диапазоне частот входных сигналов при сохранении точности измерения. Формула изобретения Цифровой фазометр, йодержащий пер вый и второй формирующие блоки, входы которых соединены с входными клем мами цифрового фазометра, фильтр, преобразователь напряжение - код, группа выходов которого соединена с выходными клеммами цифрового фазомет ра, блок управления, коммутатор, запоминающий регистр, преобразователь код - напряжение, при этом выходы формирующих блоков соединены с первым и вторым входами блока управления, первый и второй выходы которого соединены с первым и вторым управляю щими входами коммутатора, третий выход - с управляющим входом фильтра, а четвертьй выход - с управляющим входом преобразователя напряжение код, причем первый выход фильтра сое динен с аналоговым входом преобразователя напряжение - код, группа вы ходов которого соединена с группой входов запоминающего регистра, группа выходов которого соединена с группой входов преобразователя код 876напряжение, а выход последнего соединен с первым опорньм входом преобразователя напряжение - код, отличающийся тем, что, с целью расширения диапазона частот входных сигналов при сохранении точности измерения фазы, в него введен формирователь интервала интегрирования, первый вход которого соединен с выходом первого формирующего блока, второй, третий и четвертьй входы соединены соответственно с пятым, шестым и седьмым выходами блока управления, причем выход коммутатора соединен с первым аналоговым входом фильтра, первый и второй выходы формирователя интервала интегрирования соединеHbj соответственно с третьим и четвертым входами блока управления, а третий выход соединен с вТорым управляющим входом преобразователя напряжение - код, третьим управляющим входом коммутатора и пятым входом блока управления, шестой вход которого соединен с вторым выходом фильтра, первый и второй аналоговые входы коммутатора соединены с клеммой источника питающего напряжения, вторым аналоговым входом фильтра и вторым опорным входом преобразователя код - напряжение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1983 |

|

SU1114977A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство для измерения угла фазового сдвига гармонических сигналов | 1990 |

|

SU1765781A1 |

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| ДОПЛЕРОВСКИЙ ИЗМЕРИТЕЛЬ СОСТАВЛЯЮЩИХ ВЕКТОРА СКОРОСТИ, ВЫСОТЫ И МЕСТНОЙ ВЕРТИКАЛИ ДЛЯ ВЕРТОЛЕТОВ И КОСМИЧЕСКИХ АППАРАТОВ ВЕРТИКАЛЬНОЙ ПОСАДКИ | 1995 |

|

RU2083998C1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Следящий фазометр (его варианты) | 1981 |

|

SU1029095A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

Изобретение может быть использовано в информационно-измерительных системах. Цель изобретения - расширение диапазона частот входных сигналов при.сохранении точности измерения фазы. Цифровой фазометр содержит формирующие блоки 1 и 2, фильтр 3, преобразователь 4 напряжение - код, блок 5 управления, коммутатор 6, запоминающий регистр 7 и преобразователь 8 код - напряжение. Введение формирователя 9 интервала интегрирования и образование новых связей между элементами устройства позволяет достичь поставленную цель 3 ил.

Кбп.1

Ш5

и

Кбп.,5,6

KSfl.5

IS

/4

cpuz.J

| Смирнов П.Т | |||

| Цифровые фазометры | |||

| Л.: Энергия, 1974, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Цифровой фазометр | 1983 |

|

SU1114977A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-10-30—Публикация

1985-04-09—Подача