I

Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах.

Известен цифровой фазометр, содержащий два формирователя, первый и второй делители частоты, триггер, генератор, дополнительный элемент совпадения, счетчик числа измерений, триггер блокировки и регистрирующий счетчик ij .

Недостатком данного устройства являются большие аппаратурные затраты, при его использовании в многоканальных информационно-измерительных системах, в которых используется один преобразователь в цифровой код на все виды измеряемых сигналов.

Наиболее близким к изобретению по технической сущности и назначению является цифровой фазометр с промежуточным преобразованием фазового сдвига в постоянное напряжение, содержащий.первый и второй формирующие блоки, на входы которых подаются напряжения, последовательно соединенные триггер, нормализующий блок, фильтр и преобразователь напряжение - код (ПНК), При этом выходы первого и второго формирующих устройств соединены соответственно с первым и вторым входами триггера. Из сигналов с выхода нормализующего устройства с помощью фил1}Тра вьщеляется постоянная составляющая. Так как длительность импульсов, поступающих на вход фильтр равна временному сдвигу между исследуемыми напряжениями, постоянная составляющая напряжения на выходе фильтра пропорциональна величине измеряемого фазового сдвига. Напряжение с выхода фильтра с помощью ПНК преобразуется в код zT.

Недостатком известного фазометра является его низкое быстродействие обусловленное наличием фильтра.

Целью изобретения является по- вышение быстродействия фазометра.

Цель достигается тем, что в цифровой фазометр, содержащий первый и второй формирующие блоки, входы которых являются входами фазометра, последовательно соединенные нормализующий блок, фильтр и преобразователь напряжение - код, вход которого является выходом фа9772

зометра, введены блок управления, коммутатор, запоминающий регистр и преобразователь код - напряжение, при этом фильтр выполнен в виде управляемого интегратора, выходы формирующих блоков соединены соответственно с первым и вторым входами блока управления, первый и второй выходы которого соединены с аналоговыми входами коммутатора, третий и четвертый выходы - с управляющими входами коммутатора, пятый выход с управляющим входом фильтра, а шестой и седьмой - с управляющими входами преобразователя напряжение - код, причем выход коммутатора соединен с входом нормализующего блока, выходная шина преобразователя напряжение - код соединена с входной шиной запоминающего регистра, выходная шина которого соединена с входной шиной преобразователя код напряжение - код, выход которого подключен к опорному входу преобразователя напряжение - код.

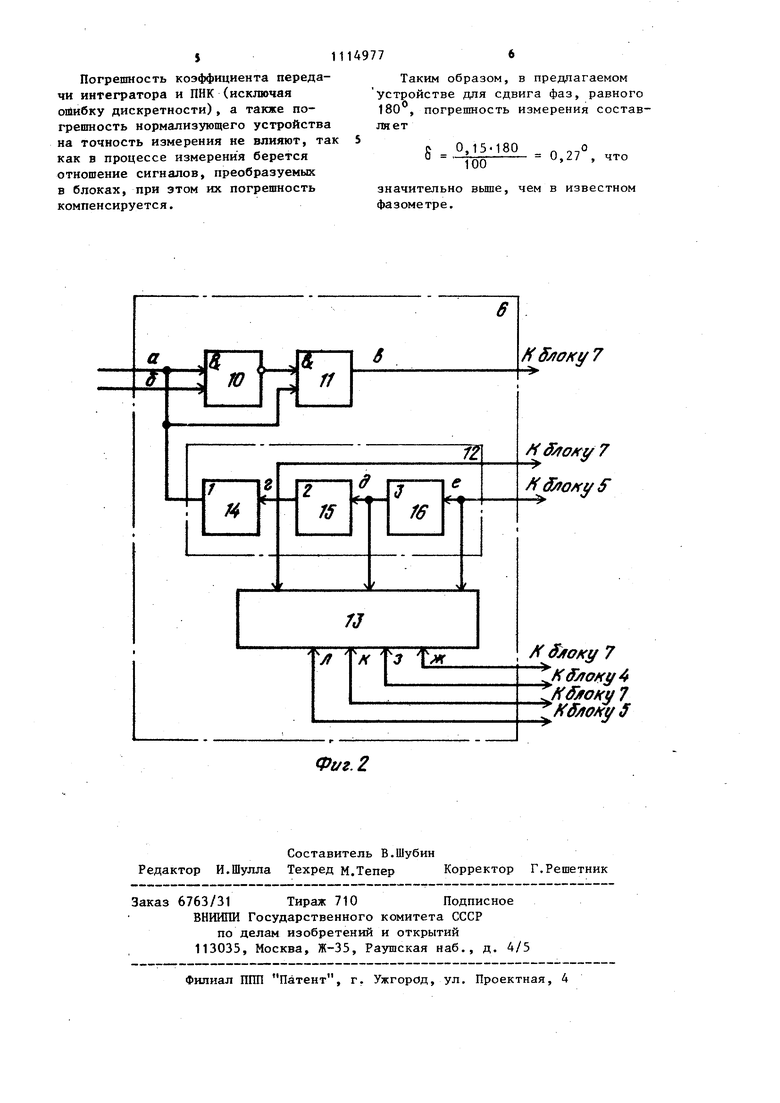

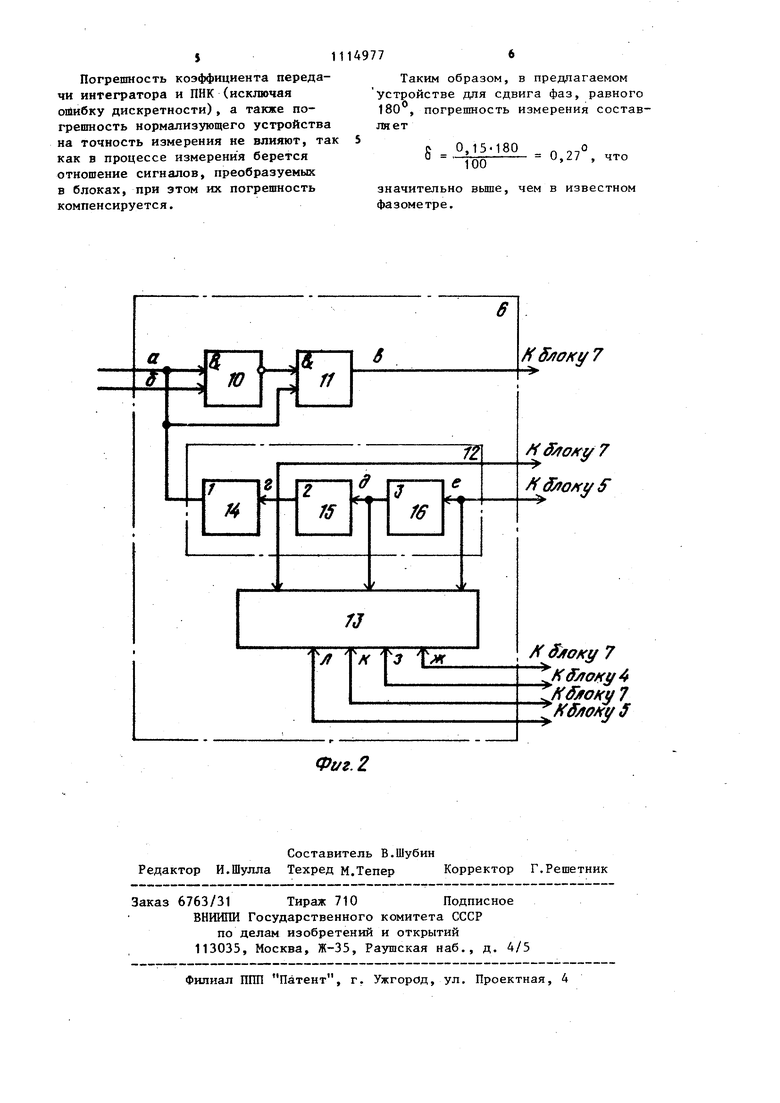

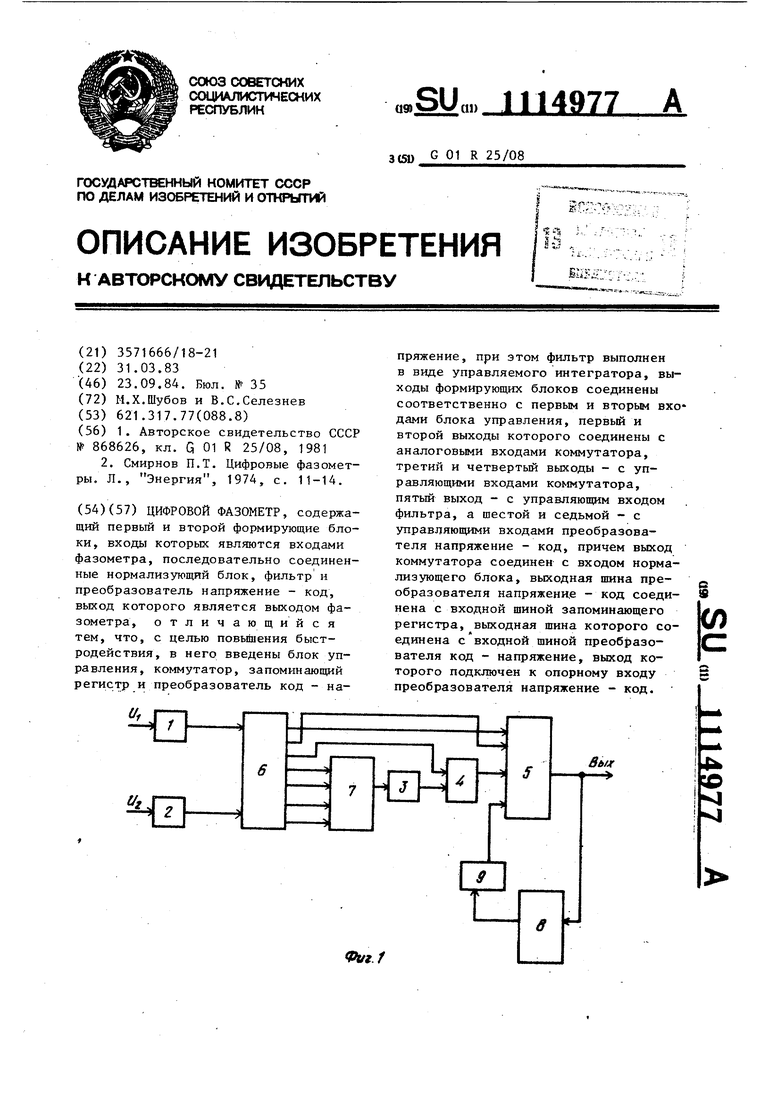

На фиг. 1 представлена функциональная схема предлагаемого фазометра; на фиг. 2 - функциональная схема блока управления.

Фазометр содержит формирующие блоки 1 и 2, на входы которых подаются напряжения U, и О 2 сдвиг фаз между которыми должен быть измерен, нормализующий блок 3, фильтр 4, ПНК

5, выход которого является выходом фазометра, блок 6 управления, коммутатор 7, запоминающий регистр 8, . преобразователь код - напряжение (ПКН) 9, при этом фильтр 4 выполнен в виде управляемого интегратора на операционном усилителе.

Выходы формирующих блоков 1 и 2 соединены соответственно с первым и вторым входами блока 6 управления,

первьй и второй выходы которого соединены с аналоговыми входами коммутатора 7, третий и четвертый выходы - с управляющими входами коммутатора. 7, пятый выход - с управляющим входом фильтра 4, а шестой и седьмой - с управляющими входами ПНК 5, причем выход коммутатора 7 соединен с входе нормализующего блока 3, а выходная щина ПНК 5

соединена с входной шиной запоминающего регистра 8, выходная шина которого соединена с входной щиной ПКН 9 выход которого подключен

3 .

к опорному входу преобразователя ПНК 5.

Блок 6 управления (фиг. 2) может иметь, например, первый элемент И 10, второй элемент И 11,. трехразрядный двоичный счетчик 12, дешифратор 13. При этом на вход элемента И 10 поступают исследуемые сигналы Ui и (J2, ас, его выхода на первый вход элемента И 11, на второй вход которого поступает сигнал Uij Выход элемента И 11 и выход первого разряда элемента 14 счетчика 12 соединены с аналоговыми входами Коммутатора 7. Выходы первого разряда элемента 14, второго разряда элемента 15, третьего разряда элемента 16 счетчика 12 соединены с входами дешифратора 13. Первый и второй выходы дешифратора 13 соединены с управляющими входами коммутатора 7. Выход третьего разряда элемента 16 счетчика 12 и третий выход дешифратора 13 соединены с управляющими входами ПНК 5, четвертый выход дешифратора 13 соединен с управляюш им входом фильтра 4.

Фазометр работает следующим образом.

Напряжения U, и U2 , между которыми измеряется сдвиг фаз, поступают на входы формирующих блоков 1 и 2, вырабатывающих импульсы напряжения прямоугольной формы, фронты которых совпадают с моментом перехода напряжений LI, и Uj через нуль. блоке 6 управления из них формируются две последовательности, одна из которых представляет собой последовательность импульсов, длительностью равной одному периоду напряжения, другая - после;: овательность импульсов длительностью равной сдви фаз между напряжениями и., и Uj. Эти сигналы поступают на двухканальный коммутатор 7, который поочередно поключает сигналы к входу нормализующего блока 3. Управление коммутатором 7 происходит по сигналам, вырабатываемые в блоке 6 управления.

В нормализующем блоке 3 импульсы . нормализуются по уровню напряжения псмощью стабильного источника напряжения. Сигналы, нормированные по амплитуде, с выхода нормализующего блока 3 подаются на фильтр 4, где происходит интегрирование сигнала

14977

течение длительности входного сигнала, поэтому выходной сигнал интегратора прямо пропорционален длительности входного сигнала. После интег5 рирования и преобразования очередного импульса происходит восстановление интегратора в нулевое состояние. Управляющие сигналы для восстановления интегратора вьфабатываются в

0 блоке 6 управления. Сигналы с выхода интегратора преобразуются с помощью ПНК 5 в код.

При преобразовании сигнала, соответствующего длительности, равной

5 одному периоду напряжения } , в качестве опорного напряжения в ПНК 5 используется источник эталонного напряжения и результат преобразования записывается в запоминающий регистре.

0 При преобразовании сигнала, соответствующего длительности, равной сдвигу фаз между напряжениями U и U2B качестве опорного напряжения в ПНК 5 подается сигнал с выхода ПНК 9, на

5 входе которого в этот момент присутствует код, полученный при преобразовании в предьщущем такте сигнала длительностью 11|. В результате получается код, равный отношению длительности

0 импуль.са, равного сдвигу фаз, к периоду сигнала и, т.е. код, соответствующий- сдвигу фаз между напряжениями { иУл. Синхронизация работы ПНК 5 и переключение опорного напря жения в ПНК происходит по сигналам, вырабатываемьм в блоке 6 управления.

В предлагаемом устройстве время определения сдвига фаз определяется временем интегрирования, временем преобразования в цифровой код и временем восстановления интегратора. Интегрирование производится за время, равное длительности одного импульса для каждой последовательности, т.е. для интегрирования обоих последовательностей необходимы два периода исследуеьак сигнапов. Время двух преобразований с помощью ПНК в цифровой код составляет 100 мкс. Время восстановления интегратора составля50 -ет также 100 мкс.

Полное время измерения сдвига фаз в устройстве составляет шесть периодов исследуемых сигналов с частотой 10 кГц.

55 Погрешность измерения в предлагаемом фазометре складьюается из погрешности ПНК, равной 0,1%, и дискретности ПНК, равной 0,05%. S11149 Погрешность коэффициента передачи интегратора и ПНК (исключая ошибку дискретности), а также погрешность нормализующего устройства на точность измерения не влияют, так 5 как в процессе измерения берется отношение сигналов, преобразуемых в блоках, при этом их погрешность компенсируется. 7 Таким образом, в предлагаемом устройстве для сдвига фаз, равного 180 , погрешность измерения составляетft 0,15480 ,. „-,0 b ,|™ 0,27 , что значительно вьш1е, чем в известном фазометре.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1985 |

|

SU1267287A1 |

| Устройство для измерения угла фазового сдвига гармонических сигналов | 1990 |

|

SU1765781A1 |

| Устройство для задания фазового сдвига | 1990 |

|

SU1721537A1 |

| Устройство для определения фазоамплитудной погрешности фазометров | 1988 |

|

SU1597764A1 |

| Радиоимпульсный фазометр | 1984 |

|

SU1201780A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Многоканальный преобразователь напряжение-код | 1980 |

|

SU917336A1 |

| Инфранизкочастотный фазометр | 1990 |

|

SU1775683A1 |

| Фазометр | 1989 |

|

SU1742744A2 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

ЦИФРОВОЙ ФАЗОМЕТР, содержащий первый и второй формирующие блоки, входы которых являются входами фазометра, последовательно соединенные нормализующий блок, фильтр и преобразователь напряжение - код, выход которого является выходом фазометра, отличающийся тем, что, с целью повышения быстродействия, в него введены блок управления, коммутатор, запоминающий регистр и преобразователь код - напряжение, при этом фильтр выполнен в виде управляемого интегратора, выходы формирующих блоков соединены соответственно с первым и вторым вхо дами блока управления, первый и второй выходы которого соединены с аналоговыми входами коммутатора, третий и четвертый выходы - с управляющими входами коммутатора, пятый выход - с управляющим входом фильтра, а шестой и седьмой - с управляющими входами преобразователя напряжение - код, причем выход коммутатора соединен с входом нормализующего блока, выходная шина пре§ образователя напряженне - код соединена с входной шиной запоминающего (Л регистра, выходная шина которого сос единена с входной шиной преобразователя код - напряжение, выход которого подключен к опорному входу преобразователя напряжение - код. lu :о VI ч

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазометр | 1980 |

|

SU868626A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смирнов П.Т | |||

| Цифровые фазометры | |||

| Л., Энергия, 1974, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-23—Публикация

1983-03-31—Подача