Изобретение относится к измерительной технике и может быть использовано для измерения фазовых сдвигов двух гармонических сигналов на входе и выходе испытуемого объекта в широком частотном диапазоне.

Наиболее близким по технической сущности к предлагаемому является устройство - цифровой фазометр, содержащее блоки выделения модуля, инверторы, блок компараторов, блоки сравнения, блок ключей, коммутаторы, преобразователи аналог-код, вычислители и вычитатель ошибки, связанные с фиксированием прохождения сигналами нулевых значений, и в определенном, достаточно узком, частотном диапазоне повышает точность.

Недостатками прототипа являются низкие точность измерения в широком частотном диапазоне и быстродействие, а также

.я

ограниченный углами ±ту диапазон значений измеряемых углов сдвига фаз. Для измерения угла сдвига фаз в устройстве- прототипе необходимо формировать ин- фазные и квадратурные составляющие с

одинаковыми амплитудами, и от точности сдвига фаз между составляющими на 90°, равенства и независимости от частоты амплитуд составляющих зависит точность решения задачи.

Целью изобретения является повышение быстродействия и точности в широком частотном диапазоне.

Сущность изобретения состоит в том, что повышение точности и быстродействия в широком частотном диапазоне достигается благодаря тому, что искомый интервал времени, пропорциональный сдвигу фаз, измеряется как интервал времени, определяемый числом относительно длительных интервалов квантования сигналов (8-16 интервалов на период) между ближайшими значениями первого (опорного) и второго сигналов после изменения их знаков. По- лученный.результат уточняется добавкой, определяемой модупями значений квантованных сигналов непосредственно до и после изменения из знаков Кроме того, по последовательности изменения знаков первого и второго сигналов определяется диапазон фазового сдвига1 от 0 до 180° или от

С

™«й

«««а

180° до 360°. Для этого устройство запоминает текущие и предшествующие отсчеты сигналов и сравнивает знаки этих отсчетов. При равенстве знаков информация о предшествующих отсчетах замещается информацией о текущих отсчетах и т.д. При изменении знака текущего отсчета первого сигнала фиксируется пара соответствующих отсчетов этого сигнала и запускается счетчик числа интервалов квантования. Далее фиксируется первая по времени после изменения знака первого сигнала пара отсчетов второго сигнала, имеющих разные знаки, и производится подсчет числа интервалов квантования между указанными моментами. Зафиксированные знаки одноименных отсчетов обоих сигналов используются для определения идентичности последовательности изменения знаков сигналов.

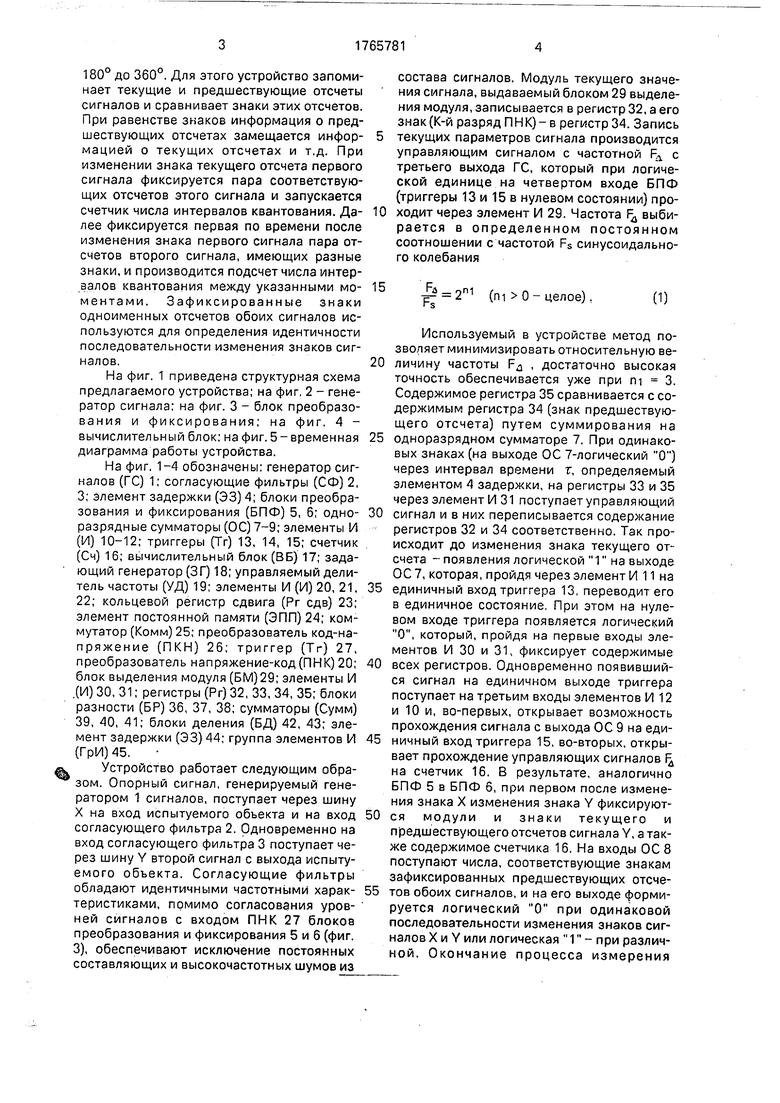

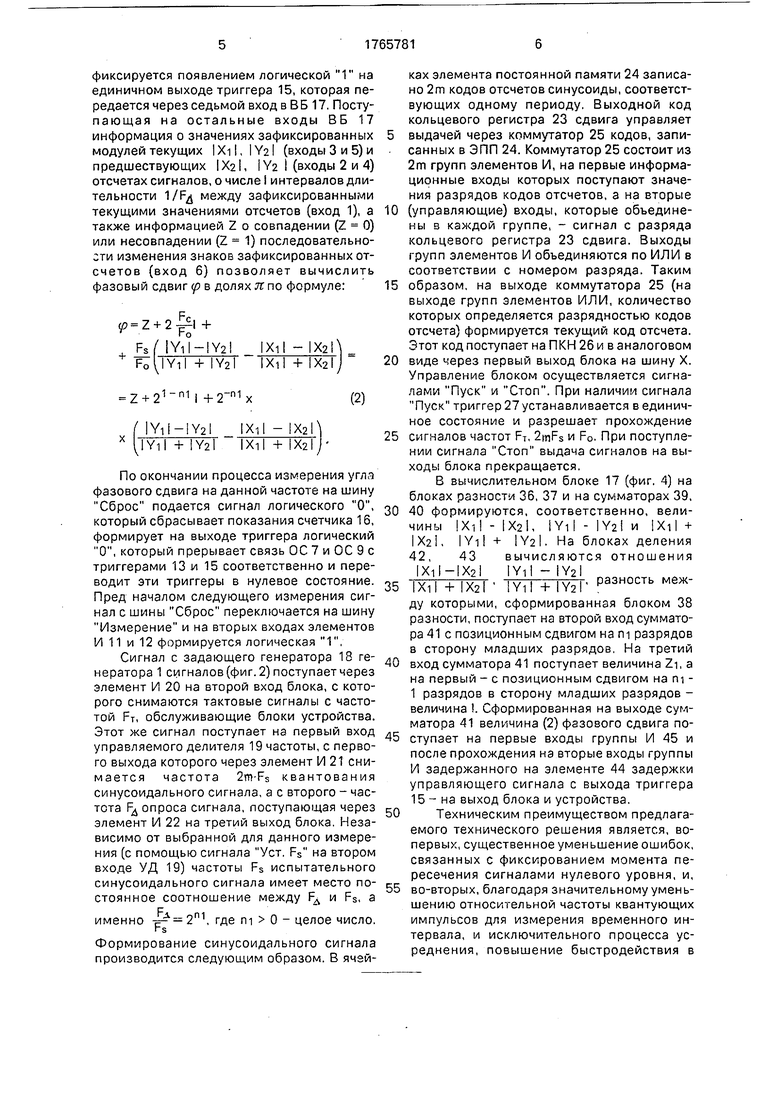

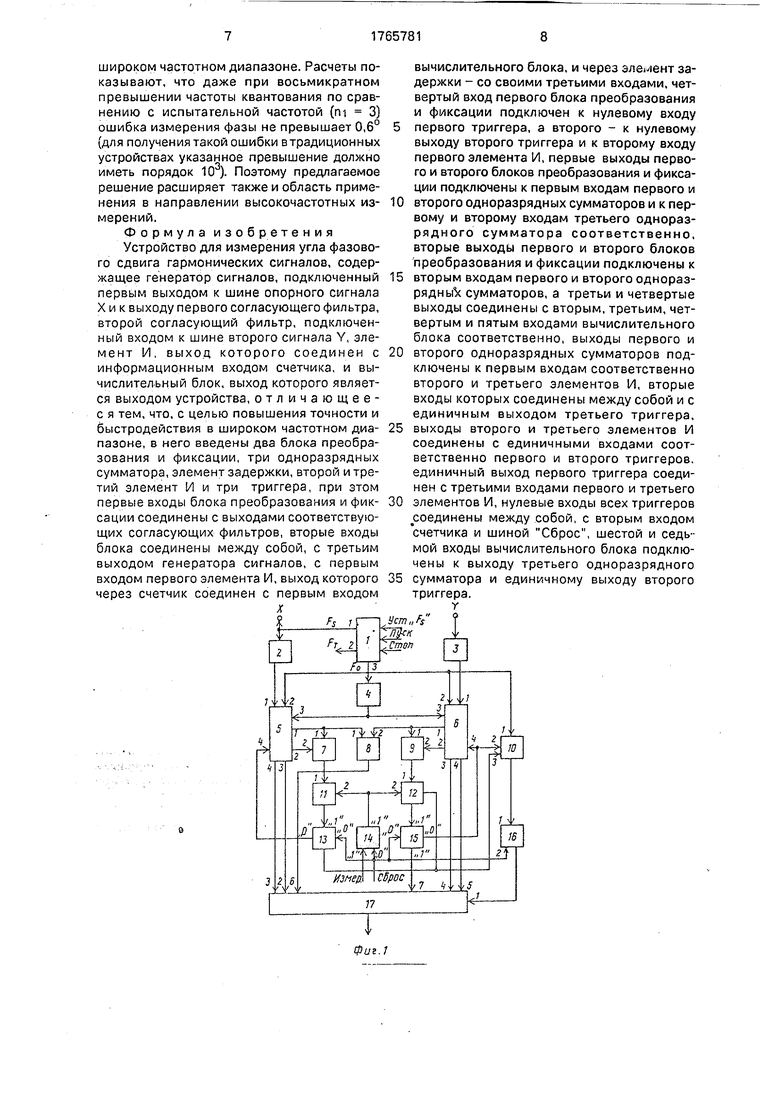

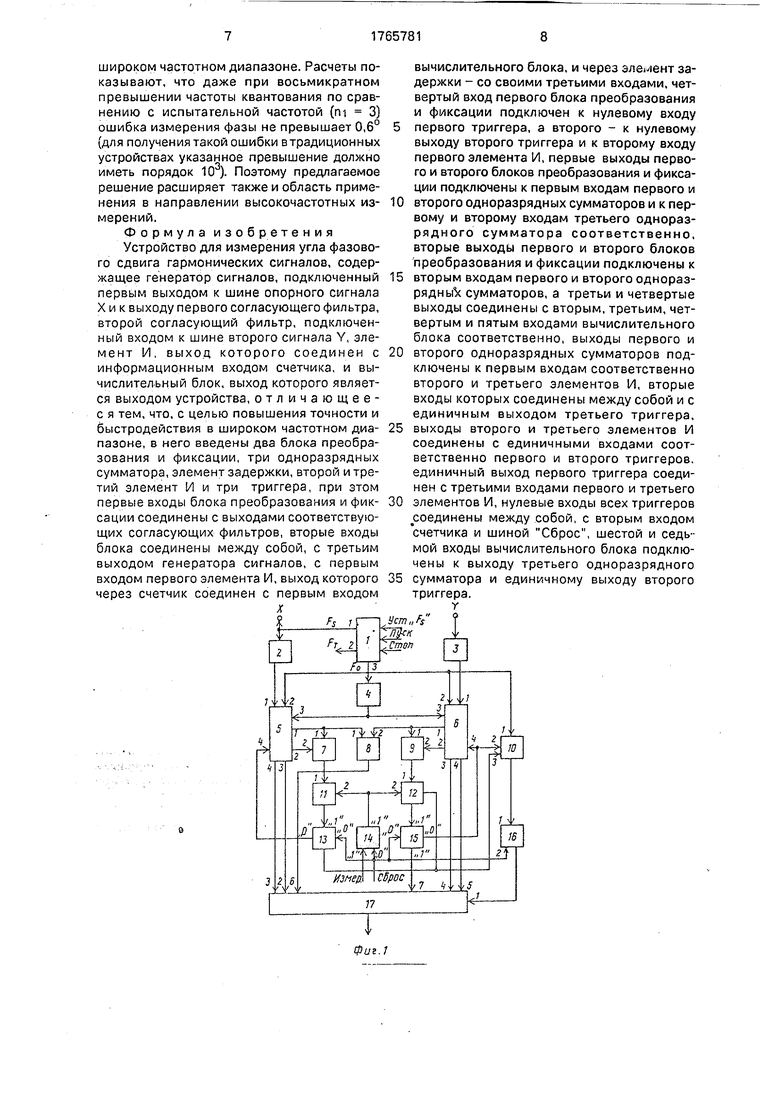

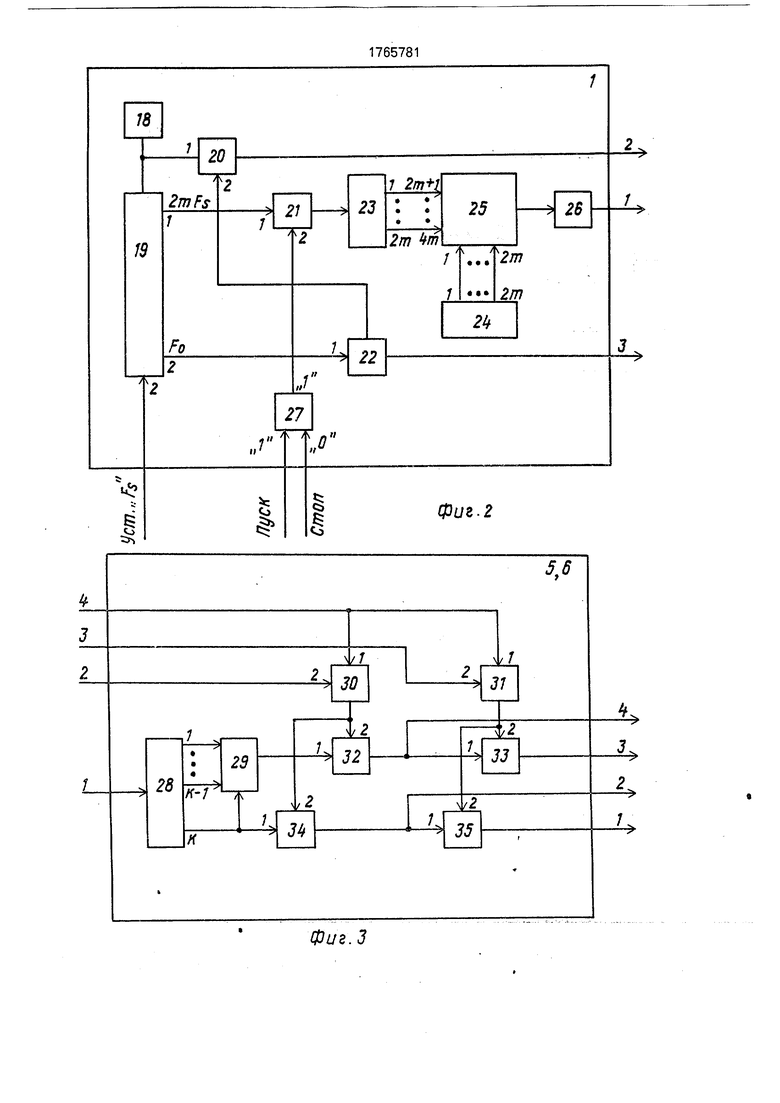

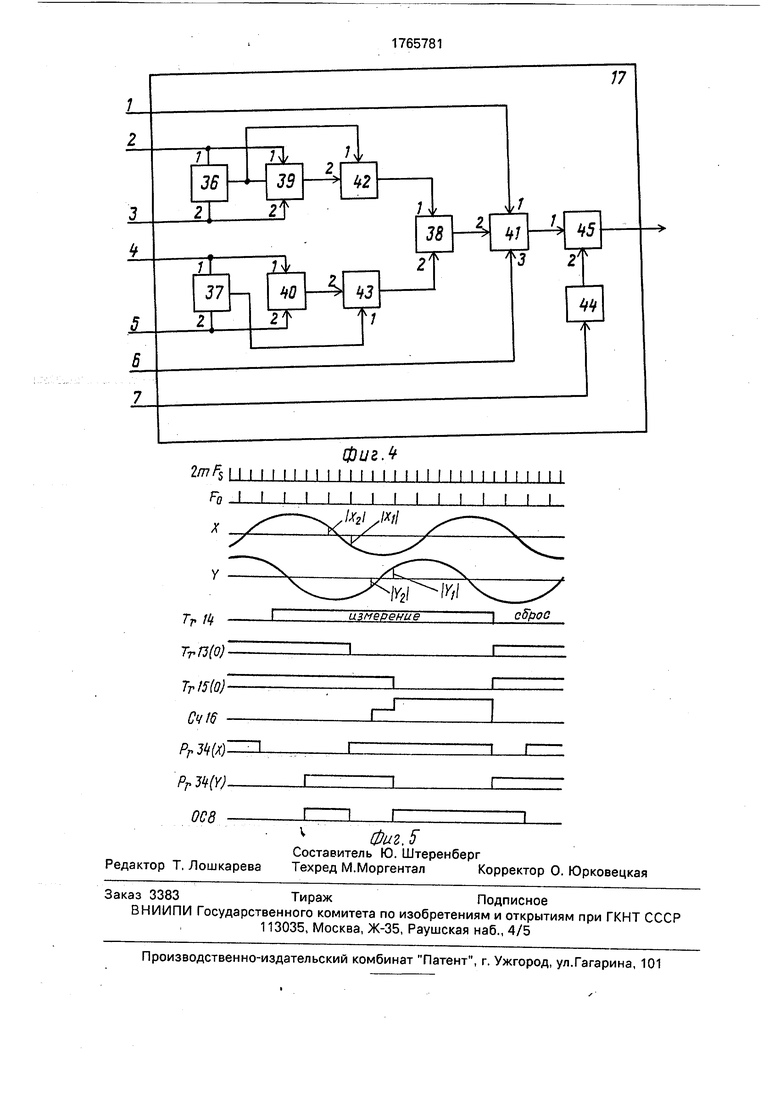

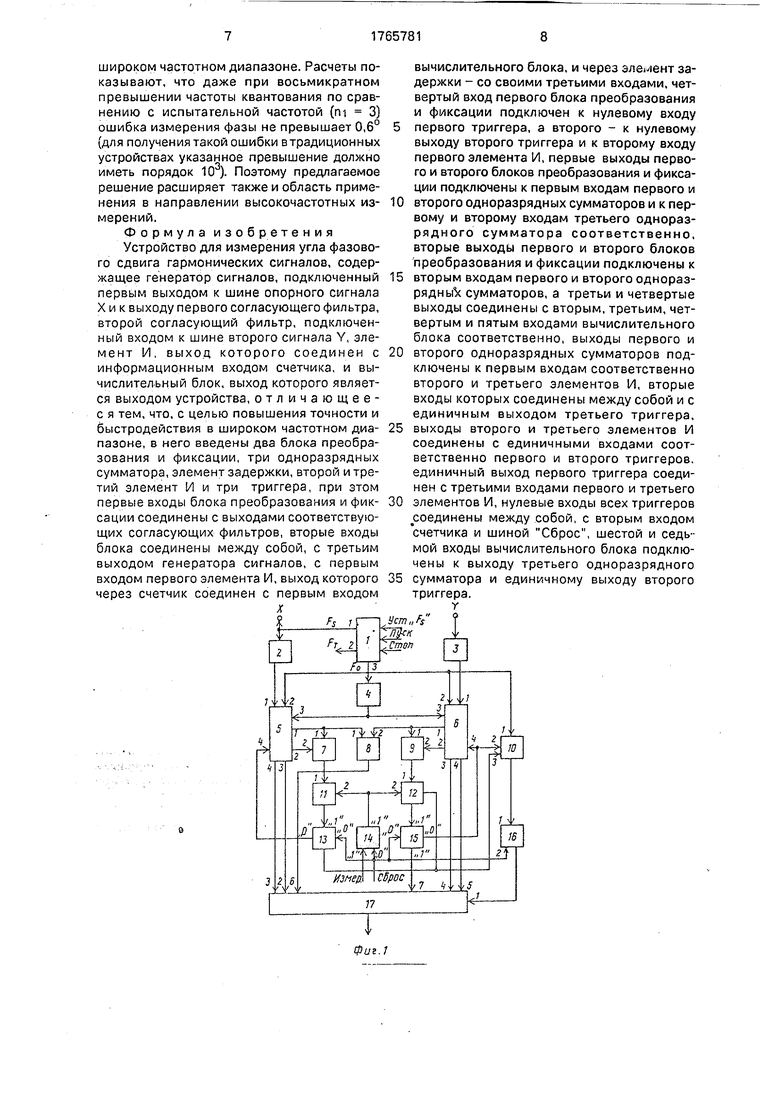

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - генератор сигнала; на фиг. 3 - блок преобразования и фиксирования; на фиг. 4 - вычислительный блок; на фиг. 5-временная диаграмма работы устройства.

На фиг, 1-4 обозначены; генератор сигналов (ГС) 1; согласующие фильтры (СФ) 2, 3; элемент задержки (ЭЗ) 4; блоки преобразования и фиксирования (БПФ) 5, 6; одноразрядные сумматоры (ОС) 7-9; элементы И (И) 10-12; триггеры (Тг) 13, 14, 15; счетчик (Сч) 16; вычислительный блок (ВБ) 17; задающий генератор (ЗГ) 18; управляемый делитель частоты (УД) 19; элементы И (И) 20, 21, 22; кольцевой регистр сдвига (Рг сдв) 23; элемент постоянной памяти (ЭПП) 24; коммутатор (Комм) 25; преобразователь код-на- пряжение (ПКН) 26; триггер (Тг) 27, преобразователь напряжение-код(ПНК) 20; блок выделения модуля (БМ)29; элементы И .(И) 30, 31; регистры (Рг) 32, 33, 34, 35; блоки разности (БР) 36, 37, 38; сумматоры (Сумм) 39, 40, 41; блоки деления (БД) 42, 43; элемент задержки (ЭЗ) 44; группа элементов И (ГрИ) 45.

Устройство работает следующим образом. Опорный сигнал, генерируемый генератором 1 сигналов, поступает через шину X на вход испытуемого объекта и на вход согласующего фильтра 2. Одновременно на вход согласующего фильтра 3 поступает через шину Y второй сигнал с выхода испытуемого объекта. Согласующие фильтры обладают идентичными частотными характеристиками, помимо согласования уровней сигналов с входом ПНК 27 блоков преобразования и фиксирования 5 и 6 (фиг. 3), обеспечивают исключение постоянных составляющих и высокочастотных шумов из

состава сигналов. Модуль текущего значения сигнала, выдаваемый блоком 29 выделения модуля, записывается в регистр 32, а его знак (К-й разряд П Н К) - в регистр 34. Запись

текущих параметров сигнала производится управляющим сигналом с частотной Рд с третьего выхода ГС, который при логической единице на четвертом входе БПФ (триггеры 13 и 15 в нулевом состоянии) проходит через элемент И 29. Частота Fd выбирается в определенном постоянном соотношении с частотой Fs синусоидального колебания

Fa опт Fs

(ni 0 - целое).

0)

Используемый в устройстве метод по- звопяет минимизировать относительную величину частоты Рл , достаточно высокая точность обеспечивается уже при m 3. Содержимое регистра 35 сравнивается с содержимым регистра 34 (знак предшествующего отсчета) путем суммирования на

одноразрядном сумматоре 7. При одинаковых знаках (на выходе ОС 7-логический О) через интервал времени т, определяемый элементом 4 задержки, на регистры 33 и 35 через элемент И 31 поступает управляющий

сигнал и в них переписывается содержание регистров 32 и 34 соответственно. Так происходит до изменения знака текущего отсчета - появления логической 1 на выходе ОС 7, которая, пройдя через элемент И 11 на

единичный вход триггера 13, переводит его в единичное состояние, При этом на нулевом входе триггера появляется логический О, который, пройдя на первые входы элементов И 30 и 31, фиксирует содержимые

всех регистров. Одновременно появившийся сигнал на единичном выходе триггера поступает на третьим входы элементов И 12 и 10 и, во-первых, открывает возможность прохождения сигнала с выхода ОС 9 на единичный вход триггера 15, во-вторых, открывает прохождение управляющих сигналов FA на счетчик 16. В результате, аналогично БПФ 5 в БПФ 6, при первом после изменения знака X изменения знака Y фиксируются модули и знаки текущего и предшествующего отсчетов сигнала Y, а также содержимое счетчика 16. На входы ОС 8 поступают числа, соответствующие знакам зафиксированных предшествующих отсчетов обоих сигналов, и на его выходе формируется логический О при одинаковой последовательности изменения знаков сигналов X и Y или логическая 1 - при различ- ной. Окончание процесса измерения

фиксируется появлением логической 1 на единичном выходе триггера 15, которая передается через седьмой вход в В Б 17. Посту- пающая на остальные входы ВБ 17 информация о значениях зафиксированных модулей текущих |Xil,|Y2| (входы 3 и 5) и предшествующих |Х2|, IY2 I (входы 2 и 4) отсчетах сигналов, о числе I интервалов длительности 1/Рд между зафиксированными текущими значениями отсчетов (вход 1), а также информацией Z о совпадении (Z 0) или несовпадении (Z 1) последовательности изменения знаков зафиксированных от- счетов (вход 6) позволяет вычислить фазовый сдвиг (р в долях п по формуле:

(р Z + 2 +

. Fsf |Yi°-|Y2| FollYil + IY2I

Z + 2

1-Ш

I + 2

-Щ

Yii-iY2l IXil - IX2

Yil + |Y2| IXil + |X2

По окончании процесса измерения угла фазового сдвига на данной частоте на шину Сброс подается сигнал логического О, который сбрасывает показания счетчика 16, формирует на выходе триггера логический О, который прерывает связь ОС 7 и ОС 9 с триггерами 13 и 15 соответственно и переводит эти триггеры в нулевое состояние. Пред началом следующего измерения сигнал с шины Сброс переключается на шину Измерение и на вторых входах элементов И 11 и 12 формируется логическая 1,

Сигнал с задающего генератора 18 генератора 1 сигналов (фиг. 2) поступает через элемент l/l 20 на второй вход блока, с которого снимаются тактовые сигналы с частотой FT, обслуживающие блоки устройства. Этот же сигнал поступает на первый вход управляемого делителя 19 частоты, с первого выхода которого через элемент И 21 снимается частота 2m-Fs квантования синусоидального сигнала, а с второго - частота Рд опроса сигнала, поступающая через элемент И 22 на третий выход блока. Независимо от выбранной для данного измерения (с помощью сигнала Уст. Fs на втором входе УД 19) частоты Fs испытательного синусоидального сигнала имеет место постоянное соотношение между Рд и Fs, a

именно 2П1, где гп 0 - целое число.

Формирование синусоидального сигнала производится следующим образом. В ячей

ках элемента постоянной памяти 24 записано 2 гл кодов отсчетов синусоиды, соответствующих одному периоду. Выходной код кольцевого регистра 23 сдвига управляет

5 выдачей через коммутатор 25 кодов, записанных в ЭПП 24. Коммутатор 25 состоит из 2т групп элементов И, на первые информационные входы которых поступают значения разрядов кодов отсчетов, а на вторые

10 (управляющие) входы, которые объединены в каждой группе, - сигнал с разряда кольцевого регистра 23 сдвига. Выходы групп элементов И объединяются по ИЛИ в соответствии с номером разряда. Таким

15 образом, на выходе коммутатора 25 (на выходе групп элементов ИЛИ, количество которых определяется разрядностью кодов отсчета) формируется текущий код отсчета. Этот код поступает на ПКН 26 и в аналоговом

20 виде через первый выход блока на шину X. Управление блоком осуществляется сигналами Пуск и Стоп. При наличии сигнала Пуск триггер 27 устанавливается в единичное состояние и разрешает прохождение

25 сигналов частот FT, 2mFs и F0. При поступлении сигнала Стоп выдача сигналов на выходы блока прекращается,

В вычислительном блоке 17 (фиг, 4) на блоках разности 36, 37 и на сумматорах 39,

30 40 формируются, соответственно, величины IXil - |X2l, lYil - lYal и IXil + 1X2. lYil + |Y2|. На блоках деления 42, 43 вычисляются отношения Xil-|X2l lYil - IY2|

35 IXil +|X2I lYil + IY2I Разность меж ду которыми, сформированная блоком 38 разности, поступает на второй вход сумматора 41 с позиционным сдвигом на гн разрядов в сторону младших разрядов. На третий

40 вход сумматора 41 поступает величина Zi, a на первый - с позиционным сдвигом на ги - 1 разрядов в сторону младших разрядов - величина . Сформированная на выходе сумматора 41 величина (2) фазового сдвига по45 ступает на первые входы группы И 45 и после прохождения на вторые входы группы И задержанного на элементе 44 задержки управляющего сигнала с выхода триггера 15 - на выход блока и устройства.

50Техническим преимуществом предлагаемого технического решения является, во- первых, существенное уменьшение ошибок, связанных с фиксированием момента пересечения сигналами нулевого уровня, и,

55 во-вторых, благодаря значительному уменьшению относительной частоты квантующих импульсов для измерения временного интервала, и исключительного процесса усреднения, повышение быстродействия в

широком частотном диапазоне. Расчеты показывают, что даже при восьмикратном превышении частоты квантования по сравнению с испытательной частотой (щ 3) ошибка измерения фазы не превышает 0,6° (для получения такой ошибки втрадиционных устройствах указанное превышение должно иметь порядок 10 ). Поэтому предлагаемое решение расширяет также и область применения в направлении высокочастотных из- мерений.

Формула изобретения Устройство для измерения угла фазового сдвига гармонических сигналов, содержащее генератор сигналов, подключенный первым выходом к шине опорного сигнала X и к выходу первого согласующего фильтра, второй согласующий фильтр, подключенный входом к шине второго сигнала Y, элемент И, выход которого соединен с информационным входом счетчика, и вычислительный блок, выход которого является выходом устройства, отличающее- с я тем, что, с целью повышения точности и быстродействия в широком частотном диа- пазоне, в него введены два блока преобразования и фиксации, три одноразрядных сумматора, элемент задержки, второй и третий элемент И и три триггера, при этом первые входы блока преобразования и фик- сации соединены с выходами соответствующих согласующих фильтров, вторые входы блока соединены между собой, с третьим выходом генератора сигналов, с первым входом первого элемента И, выход которого через счетчик соединен с первым входом

х

вычислительного блока, и через элемент задержки - со своими третьими входами, четвертый вход первого блока преобразования и фиксации подключен к нулевому входу первого триггера, а второго - к нулевому выходу второго триггера и к второму входу первого элемента И, первые выходы первого и второго блоков преобразования и фиксации подключены к первым входам первого и второго одноразрядных сумматоров и к первому и второму входам третьего одноразрядного сумматора соответственно, вторые выходы первого и второго блоков преобразования и фиксации подключены к вторым входам первого и второго одноразрядный сумматоров, а третьи и четвертые выходы соединены с вторым, третьим, четвертым и пятым входами вычислительного блока соответственно, выходы первого и второго одноразрядных сумматоров подключены к первым входам соответственно второго и третьего элементов И, вторые входы которых соединены между собой и с единичным выходом третьего триггера, выходы второго и третьего элементов И соединены с единичными входами соответственно первого и второго триггеров, единичный выход первого триггера соединен с третьими входами первого и третьего элементов И, нулевые входы всех триггеров соединены между собой, с вторым входом счетчика и шиной Сброс, шестой и седьмой входы вычислительного блока подключены к выходу третьего одноразрядного сумматора и единичному выходу второго триггера. Y

со h Ю «о fФиг.1

2/77 I I I I I I I I И I И I I И I I I I I I I I I I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Способ определения угла сдвига фаз между двумя гармоническими сигналами | 1990 |

|

SU1837241A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Адаптивный цифровой групповой приемник сигналов управления и взаимодействия с дельта - модуляцией | 1990 |

|

SU1800658A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Коррелятор | 1986 |

|

SU1339584A1 |

Использование: измерительная техника, измерение фазовых сдвигов двух гармонических сигналов на входе и выходе испытуемого объекта в широком частотном диапазоне. Сущность изобретения1 устройство содержит генератор 1 сигналов, согласующие фильтры 2, 3, элемент 4 задержки, блоки преобразования и фиксации 5, 6, одноразрядные сумматоры 7-9, элементы И 10-12, триггеры 13-15, счетчик 16, вычислительный блок 17 5 ил.

| Авторское свидетельство СССР Ns 1546915, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-09-30—Публикация

1990-07-09—Подача