13

15

гг

25

27

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1559337A1 |

| Многофункциональная ячейка однородной структуры | 1989 |

|

SU1663609A1 |

| Устройство для вычисления симметричных булевых функций | 1980 |

|

SU959064A1 |

Изобретение относится к микроэлектронике и импульсной технике и предназначено для реализации симметрических булевых функций. Цель изобретения - упрощение многофункционального логического модуля. Многофункциональный логический модуль содержит логические ячейки 13 - 27, каждая из которых реализована на КМОП-транзисторах и выполняет функцию исключающее ИЛИ между одним из входных сигналов и конъюкцией двух других входных сигналов. 2 ил.

1

19

8

15

tu

9

16

21

Ю

17

23

26

сл ю

00

Фиг.1

Изобретение относится к микроэлектротехнике и импульсной технике и предназначено для реализации симметрических булевых функций (СБФ) п переменных.

Цель изобетения - упрощение многофункционального логического модуля.

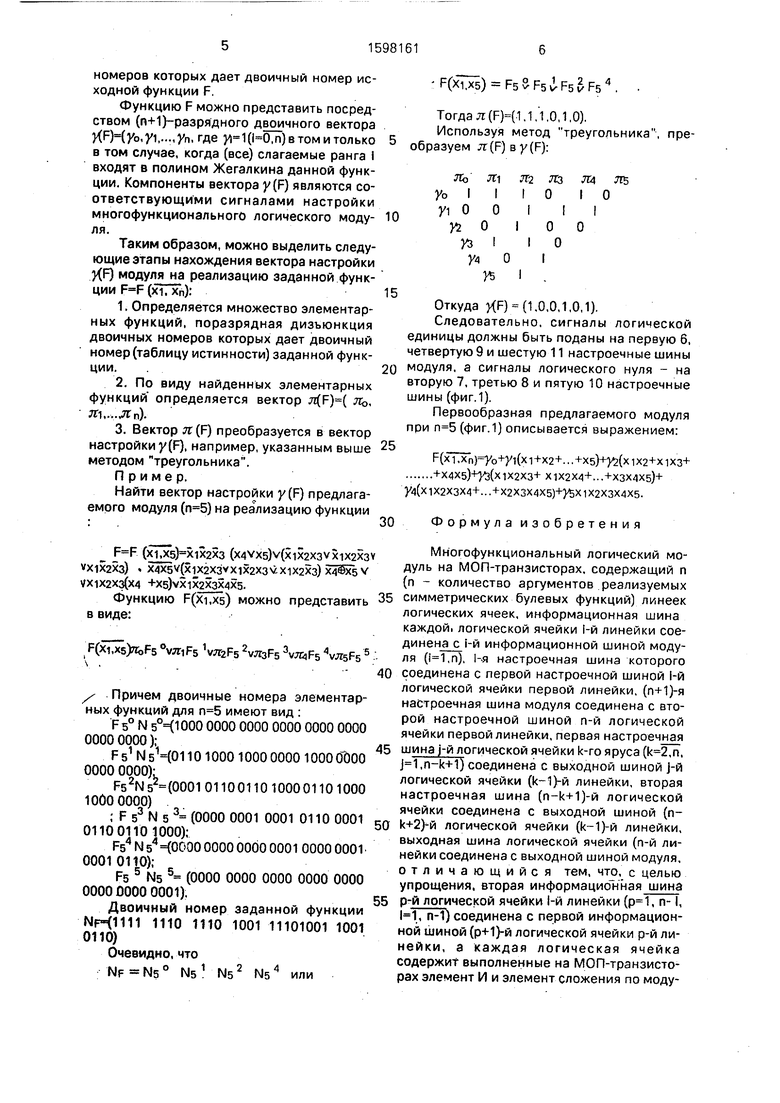

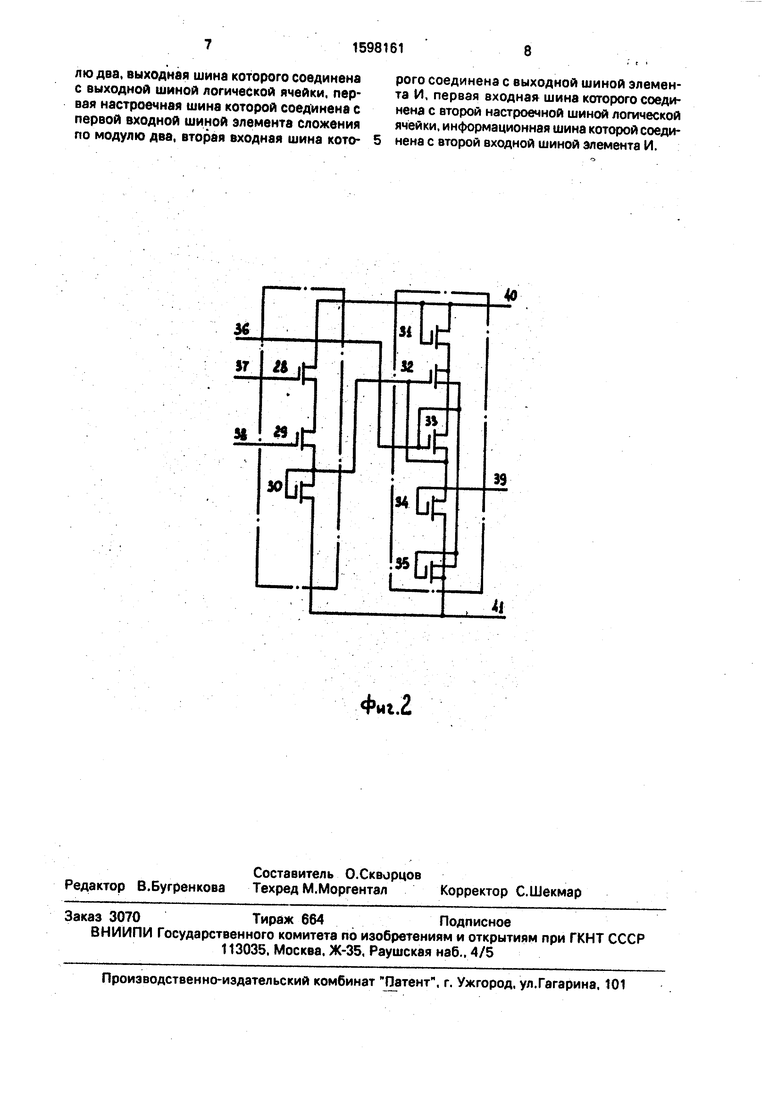

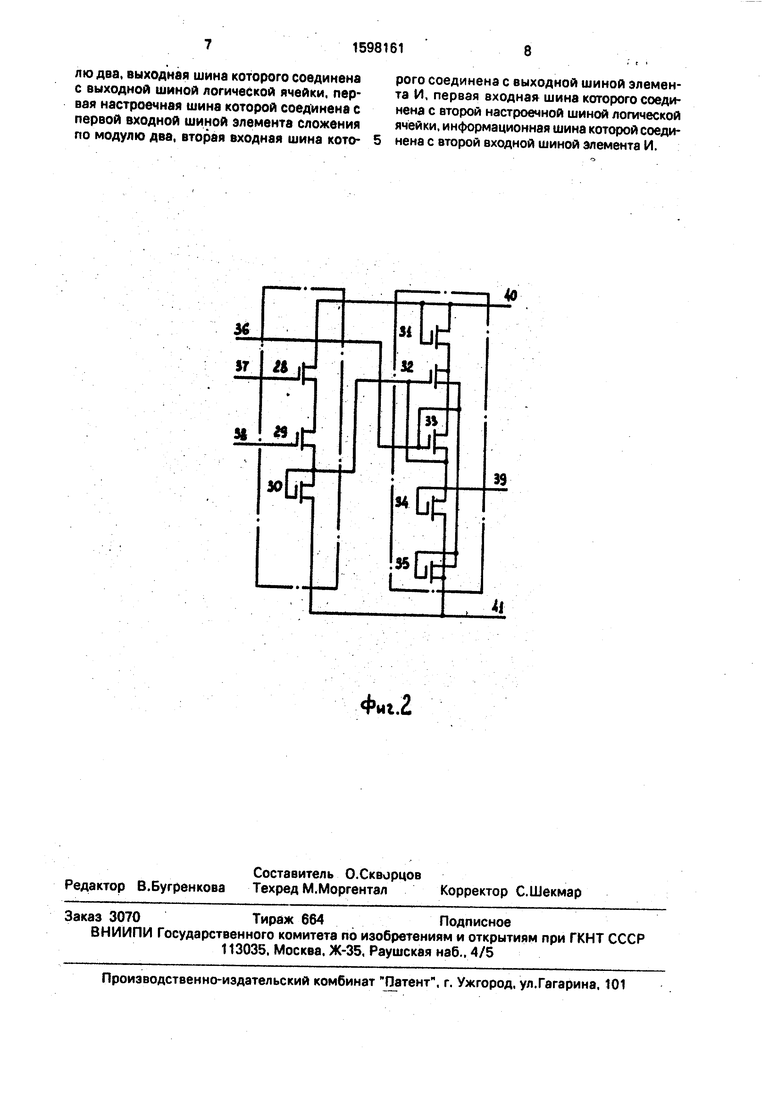

На фиг.1 приведена структурная схема предлагаемого многофункционального логического модуля при на фиг.2 - принципиальная схема логической ячейки на МОП-транзисторах.

Модуль содержит информационных шин 1-5, п+1 настроечных шин 6-11, выходную шину 12, логических ячеек первой линейки 13-17, п-1 логических ячеек второй .линейки 18-21, п-2 логических ячеек третьей линейки 22-24, п-3 логических ячеек четвертой линейки 25 и 26, п-4 логических ячеек пятой линейки 27.

Логический элемент И собран на транзисторах 28-30, элемент сложения по модулю два - на транзисторах 31-35.

Первая входная шина элемента сложения по модулю два (затвор транзистора 33) соединена с первой настроечной шиной 36 логической ячейки, вторая настроечная шина 37 которой соединена с первой входной шиной элемента И (затвор транзистора 28), вторая входная шина которого (затвор транзистора 29) соединена с информационной шиной 38 логической ячейки. Выходная шина элемента И (сток транзистора 30) соединена с второй входной шиной элемента сложения по модулю два (затвор транзистора 32), выходная шина которого (сток транзистора 34)соединена с выходной шиной 39 логической ячейки. Электрическое питание элементов И и сложения по модулю два осуществляются по шинам 40 и 41.

Логическая ячейка описывается выражением

y Ul+U2X,

где у - сигнал на выходной шине ячейки; Uji,1,2 - сигнал на j-й настроечной шине ячейки; х - сигнал на информационной шине ячейке.

В общем случае многофункциональный логический модуль на МОП-транзисторах, реализующий все функции п переменных, содержит п информационных и п+1 настроечных шин, п линеек логических ячеек, каждая Ья () из которых содержит п-1+1 ячеек. Информационная шина каждой логической ячейки 1-й линейки соединена с 1-й информационной шиной модуля, 1-я настроечная шина которого соединена с первой настроечной шиной t-й логической ячейки первой линейки, (п+1)-я настроечная шина модуля соединена с второй настроечной шиной п-й логической ячейки первой линейки. Первая настроечная шина J-й логической ячейки k-ro яруса (,,n-k+l) соединена с выходной шиной J-й логической ячейки (k-1)-й линейки, вторая настроеч5 ная шина (n-k+1)-й логической ячейки соединена с выходной шиной (n-k+2)-й логической ячейки (k-1)-й линейки. Выходная шина логической ячейки п-й линейки соединена с выходной шиной

0 модуля. Вторая информационная шина р-й логической ячейки 1-й линейки ( ,п-1, ,п- I) соединена с первой информационной шиной (р+1)-1-й, логической ячейки 1-й линейки.

5 Каждая логическая ячейка содержит выполненные на МОП-транзисторах элемент И и элемент сложения по модулю два, выходная шина которого соединена с выходной шиной логической ячейки, первая

0 настроечная шина которой соединена с первой входной шиной элемента сложения по модулю два. вторая входная шина которого соединена с выходной шиной элемента И, первая входная шина которого соединена с

5 второй настроечной шиной логической ячейки, информационная шина которой соединена с второй входной шиной элемента И,

Многофункциональный логический модуль работает следующим образом.

0

5

0

5

0

5

На информационные шины подаются двоичные переменные xi...xn, на настроеч- ные шины - сигналы настройки уо.. .уп... п. значения которых принадлежит множеству {0,1}. На выходной шине реализуется некоторая функция п переменных (xi, Хп), определяемая вектором у (F)( уо. У..-У п). Поясним алгоритм настройки модуля. Пусть симметрическая булева функция F существенно зависит от п аргументов xi, Х2хп и

ai, 32аг - рабочие числа, где 1 г п+1.

Такую функцию обозначим через Fn -....аг Если , то функция Fna называется элементарной (или фундаментальной) функцией. Произвольная функция (xi, Х2хп) может быть задана двоичным вектором XF) (

ль, л 1тг п), где т - значение F на (любом)

наборе значений п аргументов с I единицами ( п). Очевидно, что , тогда и только тогда, когда i e{ai, а2...аг} и, кроме того, имеет место

F ЛoFSVгr1F,lv...VлhFR.

Следовательно, определение вектора л(F)(лb, щ,...л,п) некоторой функции F сводится к нахождению таких элементных функций, поразрядная дизъюнкция двоичных

номеров которых дает двоичный номер исходной функции F,

Функцию F можно представить посредством (п+1)-разрядного двоичного вектора )(Уо, 1,...,уп. где (.п)втомитолько в том случае, когда (все) слагаемые ранга I входят в полином Жегалкина данной функции. Компоненты вектора y{F) являются соответствующими сигналами настройки многофункционального логического моду- ля.

Таким образом, можно выделить следующие этапы нахождения вектора настройки XF) модуля на реализацию заданной функции (xi. хп):

Пример.

Найти вектор настройки y(F) предлагаемого модуля () на реализацию функции : .

(Х1.Х5)Х1Х2ХЗ (Х4УХ5)У(Х1Х2ХЗУХ1Х2ХЗ VX1X2X3) . X4X5V(X1X2X3VX1X2X3VX1X2X3) VX1X2X3(X4 +X5)VX 1x2x3X4x5.

функцию F(xi,x5) МОЖНО представить в виде:

,F( %Л:1Р5 ЧлзРз Л5Р5 5

-

Причем двоичные номера элементарных функций для имеют вид :

F5° N 5°(1000 0000 0000 0000 0000 0000 00000000):

Fs N540110100010000000100007)00 0000 0000)(0001 01100110 100001101000 10000000)

: F 5 N 5 (0000 0001 0001 0110 0001 011001101000):

FS N 5 (0000 0000 0000 0001 0000 0001 00010110):

FS Ns (0000 0000 0000 0000 0000 0000 DODO 0001),

Двоичный номер заданной функции NF-(IIII 1110 1110 1001 11101001 1001 0110)

Очевидно, что : N5 N5 N5 или

-F(X1,X5) F5&F5J-F5 F5 .

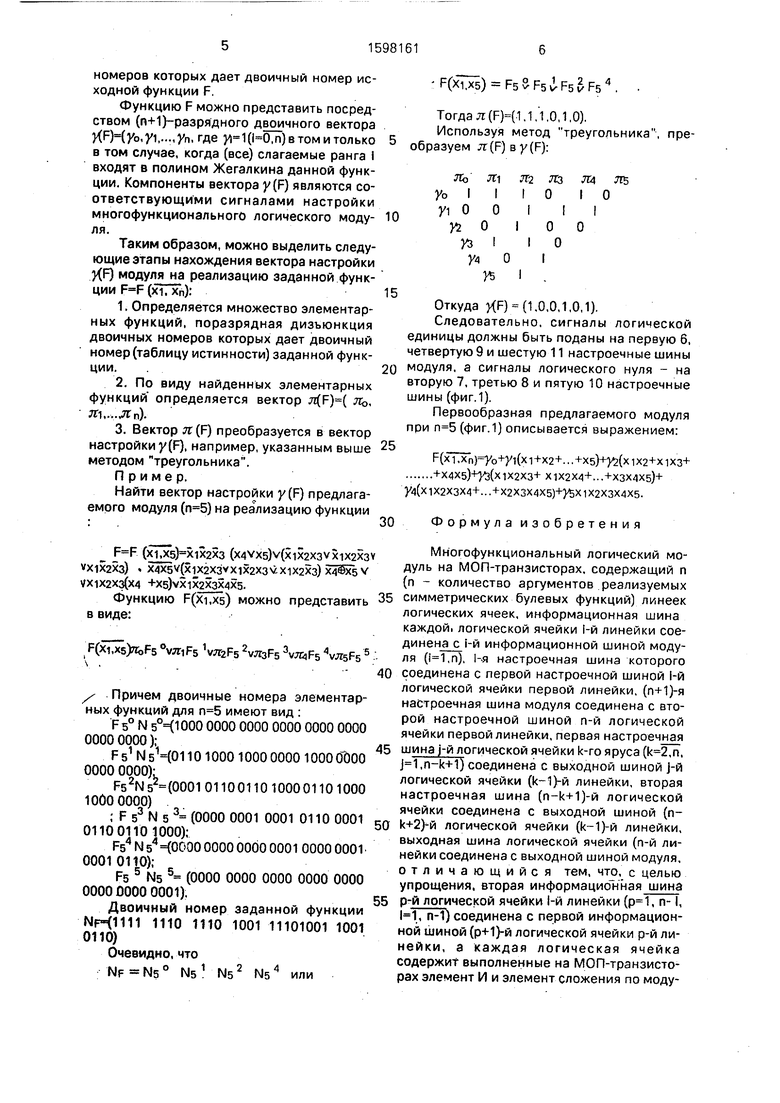

Toгдaл(F)(1.1,1,0,1,0). Используя метод треугольника, преобразуем 7г(Р) ву(Р):

ЛЬ Я1 Я2 ЛЭ Л4 ЛВ

УО I I I О 10 У1 О О I II Х2 о I о о УЗ 10 У4 о I У5 I .

Откуда ) (1,0,0,1,0,1).

Следовательно, сигналы логической единицы должны быть поданы на первую 6, четвертую 9 и шестую 11 настроечные шины модуля, а сигналы логического нуля - на вторую 7, третью 8 и пятую 10 настроечные шины (фиг,1).

Первообразная предлагаемого модуля при (фиг.1) описывается выражением:

F(xTx n)yo+yi(xi+x2+.. .+Х5)+у2(х 1Х2+Х1ХЗ+

+Х4Х5)+уЗ(х1Х2ХЗ+Х1Х2Х4+...)+

У4(х1Х2ХЗХ4+... + Х2ХЗХ4Х5)+ Х1Х2ХЗХ4Х5.

Ф О р м у Л а И 3 О б р е Т е н И Я

Многофункциональный логический модуль на МОП-транзисторах, содержащий п (п - количество аргументов реализуемых симметрических булевых функций) линеек логических ячеек, информационная шина каждой логической ячейки 1-й линейки сое- динена с 1-й информационной шиной модуля ,п), 1-.Я настроечная шина которого соединена с первой настроечной шиной 1-й логической ячейки первой линейки, (п+1)-я настроечная шина модуля соединена с второй настроечной шиной п-й логической ячейки первой линейки, первая настроечная шина j-й логической ячейки k-ro яруса (k, ,n-k+1) соединена с выходной шиной j-й логической ячейки ( линейки, вторая настроечная шина (n-k+1)-й логической ячейки соединена с выходной шиной (п- k+2)-й логической ячейки (k-1)-й линейки, выходная шина логической ячейки (п-й линейки соединена с выходной шиной модуля, отличающийся тем, что, с целью упрощения, вторая информацио нная шина р-й логической ячейки 1-й линейки (, п-1, , п-1) соединена с первой информационной шиной (р+1)-й логической ячейки р-й линейки, а каждая логическая ячейка содержит выполненные на МОП-транзисторах элемент И и элемент сложения по модулю два, выходная шина которого соединена с выходной шиной логической ячейки, первая настроечная шина которой соединена с первой входной шиной элемента сложения по модулю два, вторая входная шина которого соединена с выходной шиной элемента И, первая входная шина которого соединена с второй настроечной шиной логической ячейки, информационная шина которой соеди- нена с второй входной шиной элемента И,

Фмг.2

| Применение интегральных микросхем в электронной вычислительной технике; Справочник/ Под ред | |||

| Б.Н, Файзулаева Б.В | |||

| Тарабрина | |||

| - М.; Радио и связь, 1987 С.56, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| / | |||

Авторы

Даты

1990-10-07—Публикация

1989-02-23—Подача