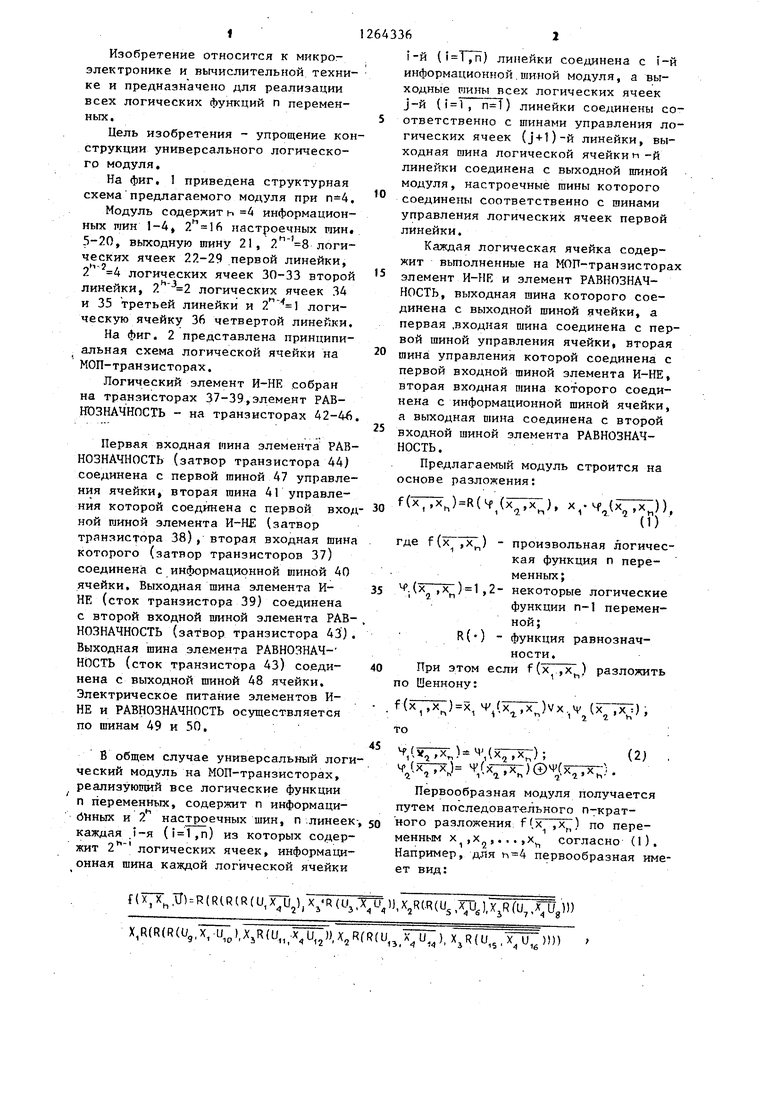

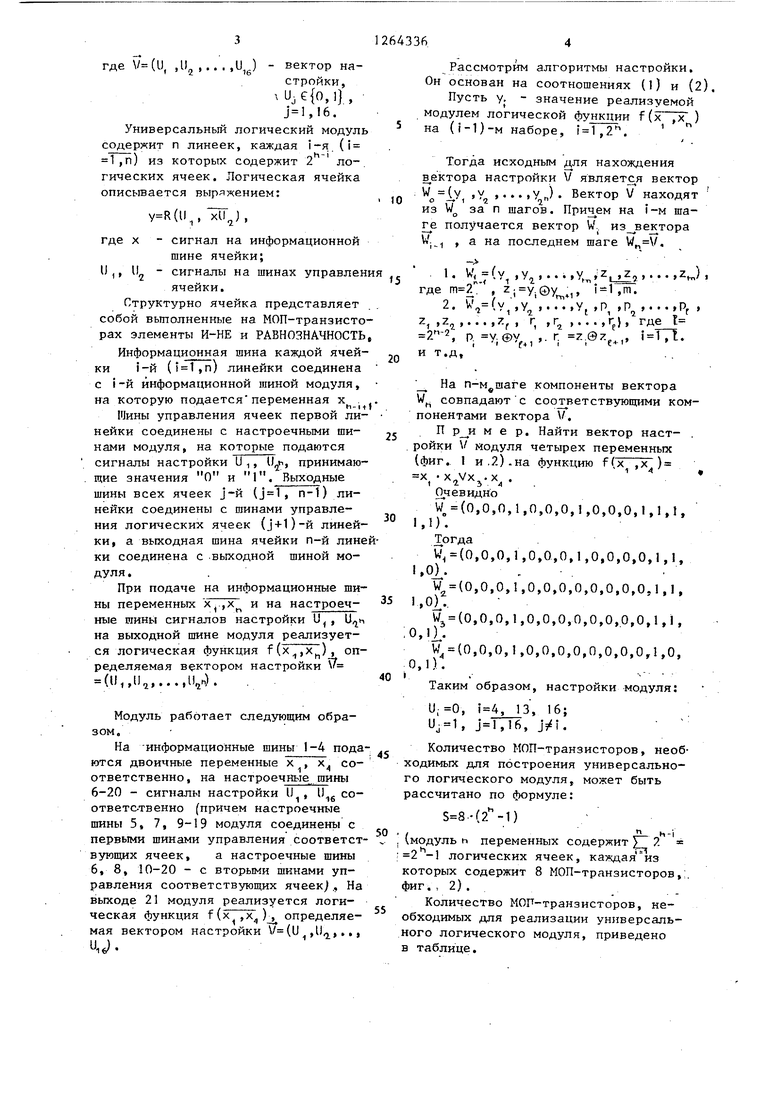

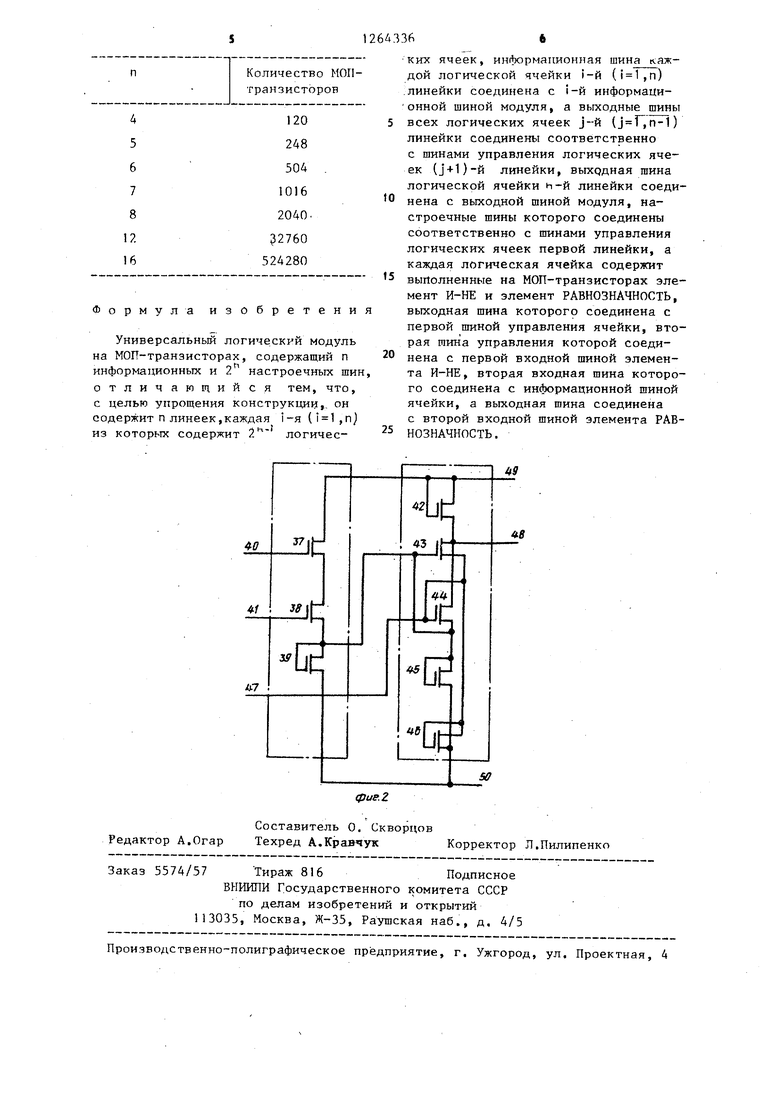

Изобретение относится к микроэлектронике и вычислительной технике и предназначено для реализации всех логических функций п переменных. Цель изобретения - упрощение кон струкции универсального логического модуля. На фиг. I приведена структурная схемапредлагаемого модуля при п-4. Модуль содержит и информационных гаин 1-А, настроечных шин, 5-20, выходную шину 21, логических ячеек 22-29 первой линейки, 2 логических ячеек 30-33 второй линейки, логических ячеек 34 и 35 третьей линейки и 2 логическую ячейку 36 четвертой линейки. На фиг. 2 представлена принципиальная схема логической ячейки на МОП-транзисторах. Логический элемент И-НЕ собран на транзисторах 37-39,элемент РАВНОЗНАЧНОСТЬ - на транзисторах 42-46 Первая входная мина элемента РАВ НОЗНАЧНОСТЬ (затвор транзистора 44) соединена с первой шиной 47 управле ния ячейки, вторая гаина 4Г управления которой соединена с первой вхо ной шиной элемента И-НЕ (затвор транзистора 38), вторая входная шин которого (затвор транзисторов 37) соединена с информационной тиной 40 ячейки. Выходная шина элемента ИНЕ (сток транзистора 39) соединена с второй входной шиной элемента РАВ НОЗНАЧНОСТЬ (затвор транзистора 43) Выходная шина элемента РАВНОЗНАЧНОСТЬ (сток транзистора 43) соедииена с выходной шиной 48 ячейки. Электрическое питание элементов ИНЕ и РАВНОЗНАЧНОСТЬ осуществляется по шинам 49 и 50. В общем случае универсальный логический модуль на МОП-транзисторах, реализующий все логические функции п переменных, содержит п информацибиных и 2 настроечных шин, п .линеек-, каждая .i-я (,n) из которых содержит логических ячеек, информационная шина каждой логической ячейки

f(X,X,TT) R(R(R(R(U,),(U3,TTr)),X,R(.R(U,TuJ,(U,)))

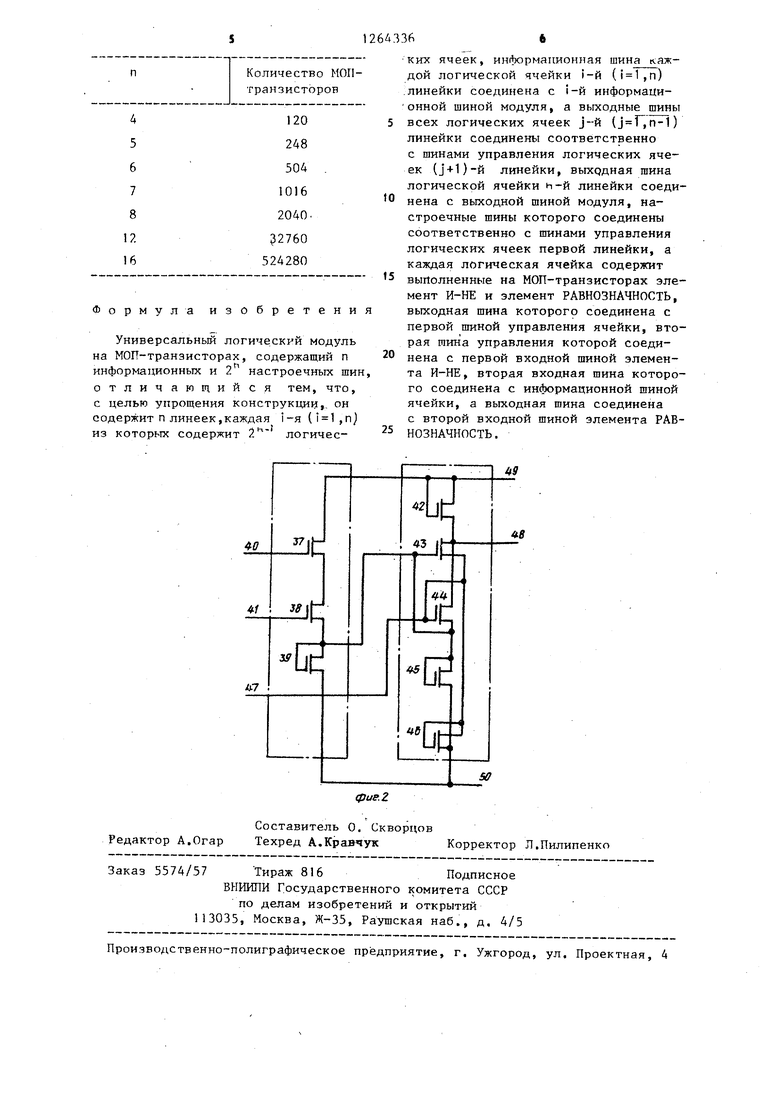

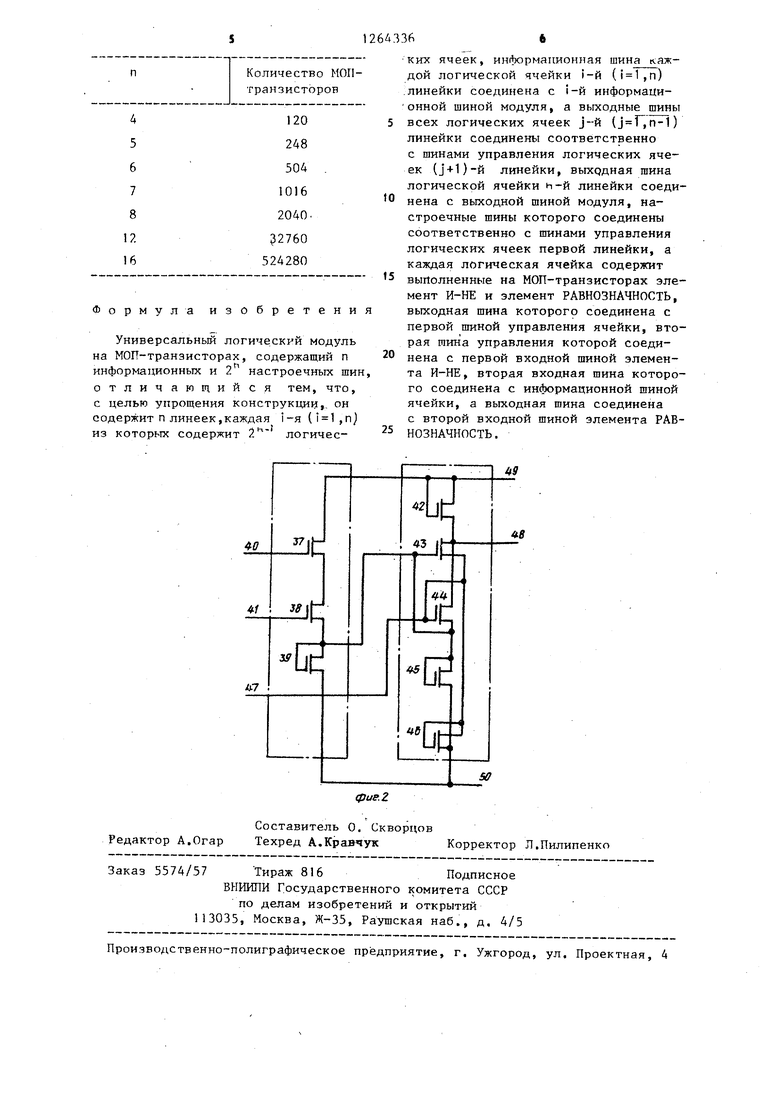

X,R(R(R(0,,X,-U,)X,R(U,,.X,U,2))X,R(R(U,,X;U,),(U,5,X,U,)))) 62 i-й (,п) линейки соединена с 1-й информационной.шиной модуля, а выходные шины всех логических ячеек j-й (, ) линейки соединены соответственно с шинами управления логических ячеек (j+l)-H линейки, выходная шина логической ячейки и-и линейки соединена с выходной шиной модуля, настроечные шины которого соединены соответственно с шинами управления логических ячеек первой линейки. Каждая логическая ячейка содержит вьтолненные на МОП-транзисторах элемент H-HR и элемент РАВНОЗНАЧНОСТЬ, выходная шина которого соединена с выходной шиной ячейки, а первая .входная шина соединена с первой шиной управления ячейки, вторая гаина управления которой соединена с первой входной шиной элемента И-НЕ, вторая входная шина которого соединена с информационной шиной ячейки, а выходная шина соединена с второй входной шиной элемента РАВНОЗНАЧНОСТЬ. Предлагаемый модуль строится на основе разложения: ), ..j), f(3rTxJ R(4.(x где f(x ,х) - произвольная логическая функция п переменных;Ч.(х Гх) 1,2- некоторые логические функции п-1 переменной;R() - функция равнозначности. При этом если f(х,х) разложить по Шеннону: f(vx;)x, ,(y,)vx,V (), )); J ,(r Первообразная модуля получается путем последовательного п-кратного разложения f,x ,х) по переменным X ,х ,...,х согласно (1). Например, для первообразная имеет вид: где V(U, .Uj ,.. . ,U,J - вектор настройки, ,ib ,16. Универсальный логический модуль содержит п линеек, каждая -я ( 1,п) из которых содержит 2 логических ячеек. Логическая ячейка описывается выряжением: - сигнал на информационной шине ячейки; сигналы на шинах управлен ячейки. Структурно ячейка представляет собой вьтолненные на МОП-транзисто рах элементы И-НЕ и РАВНОЗНАЧНОСТЬ Информационная шина каждой ячейки i-й (,п) линейки соединена с i-й информационной шиной модуля, на которую подаетсяпеременная х . Шины управления ячеек первой линейки соединены с настроечными шинами модуля, на которые подаются сигналы настройки U ,, U,, принимающие значения О и 1. Выходные шины всех ячеек j-й ( п-1) линейки соединены с шинами управления логических ячеек (j+1)-й линейки, а выходная шина ячейки п-й лине ки соединена с выходной шиной модуля . При подаче на информационные шипеременных х,х на настроечные шины сигналов настройки U , на выходной шине модуля реализуется логическая функция f(х,х), определяемая вектором настройки V (U,,lJ,,...,l.). . Модуль работает следующим образом. На -информационные шины 1-4 пода ЮТСЯ двоичные переменные х ответственно, на настроечные шины 6-20 - сигналы настройки U , i6 °ответственно (причем настроечные шины 5, 7, 9-19 модуля соединень с первыми управления соответст вующих ячеек, а настроечные шины 6, 8, 10-20 - с вторыми шинами управления соответствующих ячеек ., На выходе 21 модуля реализуется логическая функция f(х ,х), определяемая вектором настройки V(U U,.., Рассмотрим алгоритмы настройки. Он основан на соотношениях (1) и (2). Пусть у. - значение реализуемой модулем логической функции f(х ,х ) на (i-l)-M наборе, i 1,2. Тогда исходным для нахождения в ектора настройки / являетм вектор о, Виктор V находят из W за п шагов. Причтем на i-м шаге получается вектор W, из ектора а на последнем шаге . 1. V,C (y -j ,...,где . , .У;&У i-1 ,ni. 2. V, (y.,y ,....y, ,p. ,p, ,. .-РГ ) где 2, Z,j , . . . , г . -- P, У;©У,,. г. 7-.&7.,,, И Т.Д, На компоненты вектора совпадаютс соо гветствующими комонентами вектора V/. П мер. Найти вектор наст- . ойки / модуля четырех переменных фиг. 1 и,2).на функцию f{x ,х ) х,.x. V р чевидно W (0,0,0,1,0,0,0,1,0,0,0,1,1,1, ,1). Ц(0,0,0,1,0,0,0,1,0,0,0,0,1,1, ,0). W (0,0,0,1,0,0,0,0,0,0,0,0.1,1, ,0.. W (0,0,0,1,0,0,0,0,0,0,0,0,1,1, W (0,0,0,1,0,0,0,0,0,0,0,0,1,0, ,1), Таким образом, настройки модуля: и,0, , 13, 16; и,1, ,i6, jVi. Количество МОП-транзисторов, необдимых для построения универсальнологического модуля, может быть ссчитано по формуле: .-(Р.-) одуль h переменных содержит У 2 -1 логических ячеек, каждая°из торых содержит 8 МОП-транзисторов,;, г., 2). Количество МОП-транзисторов, неходимых для реализации универсальго логического модуля, приведено таблице. Формула изобретени Универсальный логический модуль на МОП-транзисторах, содержащий п информационных и 2 настроечных ши отличающийся тем, что с целью упрощения конструкции,- он содержитплинеек,каждая i-я (,n из которых содержит логичес6Ьких ячеек, информационная шина каждой логической ячейки i-й (,n) линейки соединена с i-й информационной шиной модуля, а выходные шины всех логических ячеек --й {j r,n-l) линейки соединены соответственно с шинами управления логических ячеек )-й линейки, выхрдная шина логической ячейки и-и линейки соединена с выходной шиной модуля, настроечные шины которого соединены соответственно с шинами управления логических ячеек первой линейки, а каждая логическая ячейка содержит выполненные на МОП-транзисторах элемент И-НЕ и элемент РАВНОЗНАЧНОСТЬ, выходная шина которого соединена с первой шиной управления ячейки, вторая шина управления которой соединена с первой входной шиной элемента И-НЕ, вторая входная шина которого соединена с информационной шиной ячейки, а выходная шина соединена с второй входной шиной элемента РАВНОЗНАЧНОСТЬ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Универсальный логический модуль | 1985 |

|

SU1269121A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

Изобретение относится к микроэлектронике и вычислительной технике и предназначено для реализации всех логических функций п переменных. Цель изобретения - упрощение конструкции модуля. Устройство содержит п информационных шин 1-4 и 2 настроечных шин 5-20. Наличие п линеек, каждая i-я (,n) из которых содержит 2 логических ячеек при условии, что каждая логическая ячейка состоит из выполненных на МОП-транзисторах элементов И-НЕ и с РАВНОЗНАЧНОСТЬ, позволяет модулю (Л обладать регулярной структурой и делает его более однородным. 1 табл., 2 ил. ю О5 4 00 00 05

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 0 |

|

SU333550A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Якубайтис Э.А | |||

| Универсальные логические элементы | |||

| - Автоматика и вычислительная техника, 1973, № 5. | |||

Авторы

Даты

1986-10-15—Публикация

1985-06-04—Подача