(54) УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1985 |

|

SU1254486A1 |

| Устройство для обработки приоритетов запросов прерываний | 1987 |

|

SU1562909A1 |

| Устройство для прерывания программ | 1985 |

|

SU1341636A1 |

| Устройство переменного приоритета | 1984 |

|

SU1171793A1 |

| Устройство системного контроля для мультипроцессорной системы | 1987 |

|

SU1462342A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство для прерывания программ | 1983 |

|

SU1168945A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Устройство переменного приоритета | 1986 |

|

SU1399740A1 |

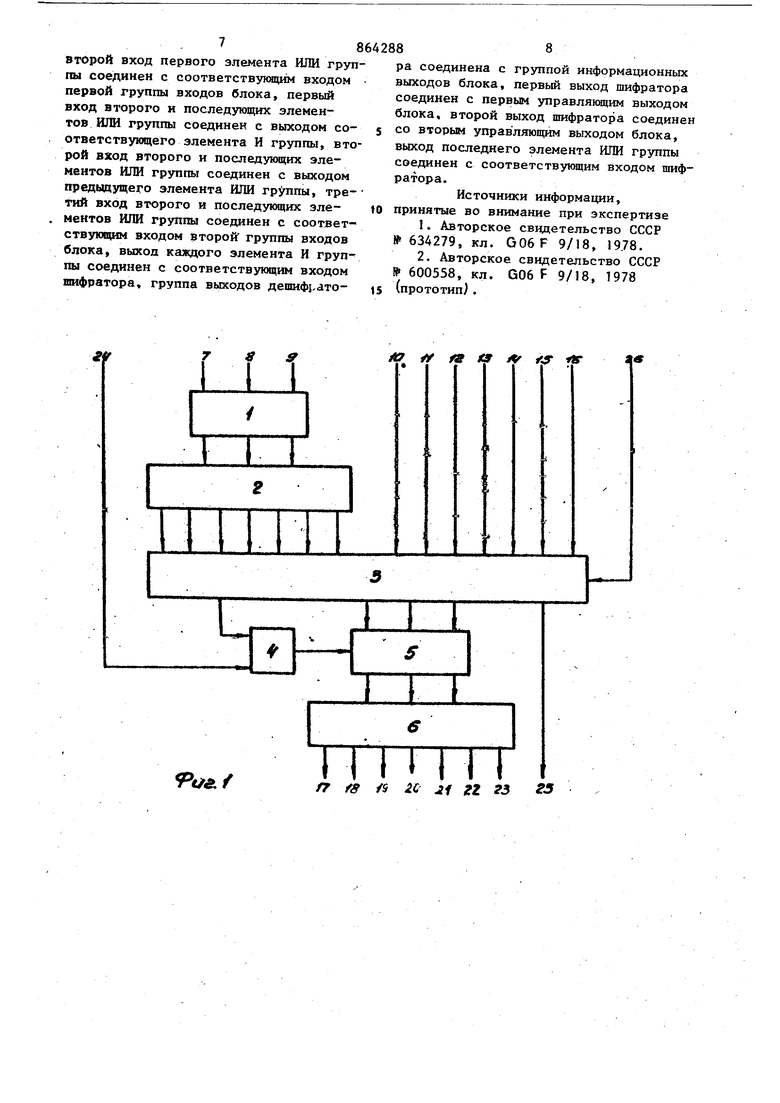

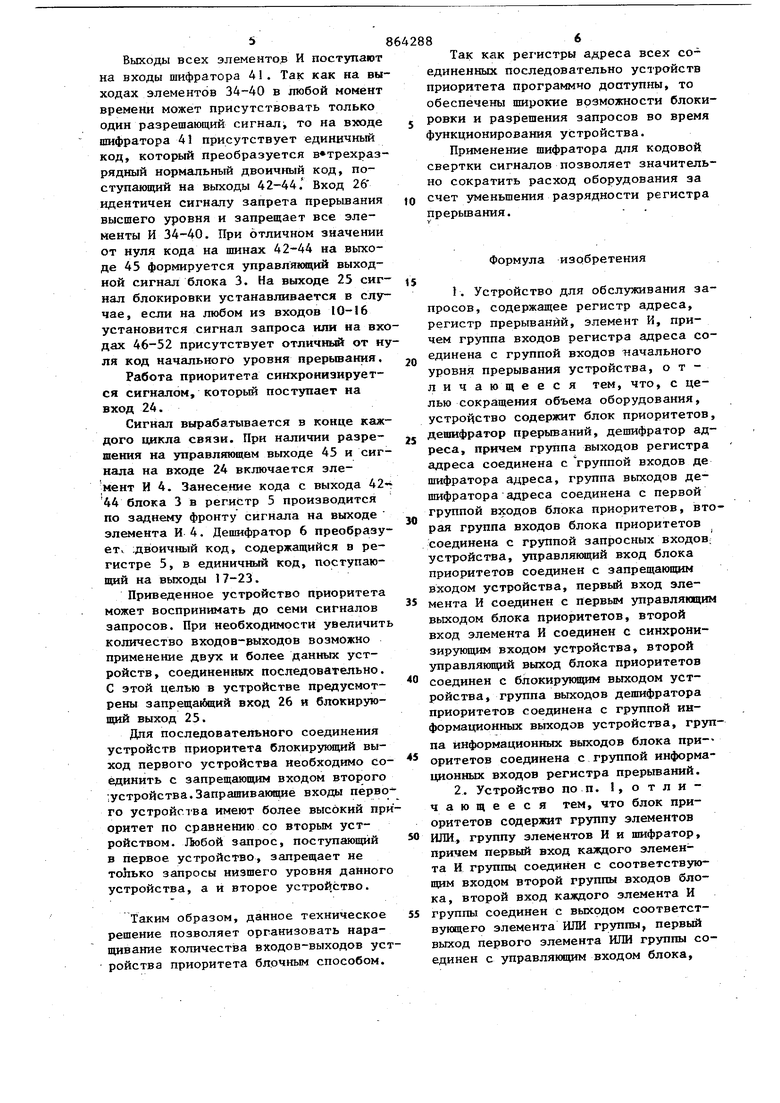

Изобретение относится к вычислительной технике и может найти применение в системах, используювдх изменяемую дисциплину обслуживания. Известно устройство, содержащее у лы анализа состояния канала, триггер запросов l. Недостатком такого устройства является большой объем оборудования. Наиболее близким по технической СУ1ЦНОСТИ и достигаемому результату к предлагаемому является устройство, содержащее регистр адреса, регистр прерываний, элементы И, дешифратор 2, Недостатком такого устройства явля ется большой объем оборудования. Цель изобретения -- сокращение объема оборудования. Поставленная цель достигается тем что в устройство для обслуживания запросов, содержащее регистр адреса, регистр прерываний, элемент И, причем группа входов регистра адреса соедине на с группой входов начального уровня прерывания устройства, введены блок приоритетов, дешифратор прерываний, дешифратор адреса, причем группа выходов регистра адреса соединена с группой входов дешифратора адреса, группавыходов дешифратора адреса соединена с первой грзгппой входов блока приоритетов, вторая группа входов блока приоритетов соединена с группой запросных входов устройства, управлякяцнй вход блока приоритетов соединен с запрещающим входом устройства, первый вход элемента И соединен с первьм управляющим выходом блока приоритетов, второй вход элемента И соединен синхронизирующим входом устройства, второй управляющий выход блока приоритетов соединен с блокирующим выходом устройства, группа выходов дешифратора приоритетов соединена с группой информационных выходов устройства, группа информациоиных выходов блока приоритетов соединена с группой ин- 38 формационных входов регистра прерываБлок приоритетов содержит группу элементов ИЛИ, группу элементов И и шифратор, причем первый вход каждого элемента И группы соединен с соответствующим входом второй группы входов блока, второй вход каждого элемен та И группы соединен с выходом соответствующего элемента ШШ групгая, пер вый вход первого элемента соединен с управляющим входом блока, второй вход первого элемента ИЛИ группы соединен с соответствующим входом, первой группы входов блока, первый вход дторого ;и последующих элементов ИЛИ группы j соединен с выходом соответствуклцего элемента И группы, второй вход второго и последующих элементов ИЛИ группы соединен с выходом предыдущего эле мента ИЛИ группы, третий вход второго и последукицих элементов ИЛИ группы соединен с соответстнующим входом второй группы входов блока, выход ка;ждого элемента И группы соединен с соотвётствузоцим входом пшфратора, группа выходов дешифратора соединена с группой информационных выходов бло ка первь1й выход шифратора соединен с первым управляющим выходом лока, второй выход птфратора соединен со вторым урравляющим выходом блока, вы ход последнего элемента ИЛИ группы соединен с соответствующим входог шифратора. На фиг. 1 изображена структзфная схема устройства; на фиг. 2 - схема блока приоритетов. Устройство содержит регистр 1 адреса дешифратор 2 адреса, блок 3 при оритетов. Элемент И 4, регистр 5 пре рываний, дешифратор 6 прерываний, входы 7-9 начального уровня прерывания, группа запросных входив 10-16 устройства, группа информационных вх дов устройства 17-23, синхронизирующий вход 24 устройства, блокирующий выход 25 устройства, запрещающий вход 26 устройства, группа элементов Или 27-33 блока приоритетов, гру па элементов И 34-40 блока приоритетов, шифратор 41 блока приоритетов, информационные выходы 42-44 блока пр оритетов, первый управляющий выход 4 блока приоритетов, первая группа вхо дов 46-52 блока приоритетов. Устройство работает следующим образом. На входы 7-9 блока приоритета подается двоичный код начального уровня прерывания, который записывается в регистр .1. Двоичный код, занесенный в регистр 1 преобразуется дешифратором 2 в единичный код и подается на первую группу входов 46-52 блока приоритетов. На вторую группу входов блока приоритетов постзшают запросы от внешних устройств с группы запросных входов 10-16, Единичный код начального уровня прерывания подается на входы 46-52, связанные соответственно со входами группы элементов ИЛИ 27-33, На выходах элементов ИЛИ 27-33 формируются сигналы запрета, которые поступают на запрещающие входы группы элементрв, И 34-40. Если логическая единица . . присутствует иа входе 48 блока приоритетов, что соответствует двоичному оду 111 в регистре адреса, то на вы-f Ьсоде элемента ИЛИ 27 установится сигнал запрета, который непосредственно запретит элемент И 35, а через- элементы ИЛИ 28-33 запретит соответственно элементы 34-40. Таким образом, код 1J1 в регистре адреса полностью запирает блок приоритетов. Легко показать, что наличие логической единицы на любомиз входов 49-54 запрещает соответств5РЮщий элемент И 35-40 и все последующие. При коде 000 в регистре адреса , блок приоритетов полностью разрешен и обрабатывает все входные запросы Запросы от внешних устройств поступают иа входы 10-16. Если на входы устройства поступают одновременно несколько запросов, то код на выходах блока 3 соответствует тому сигналу запроса, приоритет которого выше. Приоритетность сигналов определяется номерами входов, к которым они подключаются. Так запрос, поступающий на вход 16, имеет низший приоритет, а на вход 10 - высший. Запрос от внешнего устройства поступает на вход одного из элементов И 34-40. Если на втором входе данного элемента запрет отсутствует, то на его выходе формируется сигнал, который поступает на вход интегратора 41. Одновременно сигнал с выхода открытого, элемента И по-, ступает на все последующие элементы ШШ, запрещакяцие все элементы И менее приоритетных входов. S Выходы всех элементов И поступают на входы шифратора 41. Так как на вы ходах элементов 34-40 в любой момент времени может присутствовать только один разрешающий сигнал, то на входе шифратора 41 присутствует единичный код, который преобразуется в трехраз рядный нормальный двоичный код, поступающий на выходы 42-44. Вход 26 идентичен сигналу запрета прерывания высшего уровня и запрещает все элементы И 34-40. При отличном значении от нуля кода на шинах 42-44 на выходе 45 формируется управляющий выходной сигнал блока 3. На выходе 25 сиг нал блокировки устанавливается в слу чае, если на любом из входов 10-16 установится сигнал запроса или на вх дах 46-52 присутствует отличный от н ля код начального уровня прерьгаания. Работа приоритета синхронизируется сигналом, который поступает на вход 24. Сигнал вырабатывается в конце каждого цикла связи. При наличии разрешения на управлшощвм выходе 45 и сигнала на входе 24 включается элемент И 4. Занесение кода с выхода 42 44 блока 3 в регистр 5 производится по заднему фронту сигнала на выходе элемента И 4. Дешифратор 6 преобразует двоичный код, содержащийся в регистре 5, в единичный код, поступающий на выходы 17-23. Приведенное устройство приоритета может воспринимать до семи сигналов запросов. При необходимости увеличить количество входов-выходов возможно применение двух и более данных устройств, соединенных последовательно. С этой целью в устройстве предусмотрены запрещайщий вход 26 и блокирующий выход 25. Для последовательного соединения устройств приоритета блокирунмций выход первого устройства необходимо соединить с запрещающим входом второго устройства.Запрашивакицие входы первого устройства имеют более высокий при оритет по сравнению со вторым устройством. Лобой запрос, поступающий в первое устройство, запрещает не тоЬько запросы низшего уровня данного устройства, а и второе устройство. Таким образом, данное техническое решение позволяет организовать наращивание количества входов-выходов уст ройства приоритета блочным способом. 88 Так как рег-истры адреса всех соединенных последовательно устройств приоритета программно доступны, то обеспечены широкие возможности блокировки и разрешения запросов во время функционирования устройства. Применение шифратора для кодовой свертки сигналов позволяет значительно сократить расход оборудования за счет уменьшения разрядности регистра прерьтания. Формула изобретения 1. Устройство для обслуживания запросов, содержащее регистр адреса, регистр прерываний, элемент И, причем группа входов регистра адреса соединена с группой входов начального уровня прерывания устройства, отличающееся тем, что, с целью сокращения объема оборудования, устройство содержит блок приоритетов, дешифратор прерываний, дешифратор адреса, причем группа выходов регистра адреса соединена с группой входов де шифратора адреса, группа выходов дешифратора адреса соединена с первой группой входов блока приоритетов, вторая группа входов блока приоритетов соединена с группой запросных входов; устройства, управляющий вход блока приоритетов соединен с запрещающим входом устройства, первый вход элемента И соединен с первым управляющим выходом блока приоритетов, второй вход элемента И соединен с синхрони зирующим входом устройства, второй управляющий выход блока приоритетов соединен с блокирукяцим выходом устройства, группа выходов дешифратора приоритетов соединена с группой информационных выходов устройства, группа информационных выходов блока при- оритетов соединена с группой информационных входов регистра прерываний. 2. Устройство по п. 1, о т л и чающееся тем, что блок приоритетов содержит группу элементов ИЛИ, группу элементов И и шифратор, причем первый вход каждого элемента И группы соединен с соответствующим входом второй группы входов блока, второй вход каждого элемента И группы соединен с выходом соответствующего элемента ИЛИ группы, первый выход первого элемента ИЛИ группы соединен с управляющим входом блока. второй вход первого элемента ИЛИ груп пы соединен с соответствукнцим входом первой группы входов блока, первый вход второго и последующих элементов ШШ группы соединен с выходом соответствующего элемента И группы, вто рой вход второго и последующих элементов ИЛИ группы соединен с выходом предьщущего элемента ШШ группы, третий вход второго и последукицих элементов ШШ группы соединен с соответствующим входом второй грзгппы входов блока, выход каждого элемента И группы соединен с соответствующим входом вшгфратора, группа выходов дешиф1-ато

т I I

Т1 I

9VA/

/7 fs /S if jf zi гз

ЛУ fit f9 fS -ЛР

г т

2S 8 pa соединена с группой информационных выходов блока, первый выход шифратора соединен с первым управлякицим выходом блока, второй выход шифратора соединен со вторым управляющим выходом блока, выход последнего элемента ИЛИ группы соединен с соответствугацим входом шифратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свчцвтельство СССР 634279, кл. G06F 9/18, 19.78. 2.Авторское свидетельство СССР 600558, кл. G06 F 9/18, 1978 (прототип.

Авторы

Даты

1981-09-15—Публикация

1979-12-07—Подача