Изобретение относится к вычислительной технике, в частности к устройствам связи с объектами управления вычислительных комплексов, и предназначено ДЛЯ приема сигналов от двухпози ционных датчиков и ввода информации об их состоянии в ЭВМ с формированием инициативного сигнала запроса на прерывание текущей программы центрального процессора...

Цепь изобретения - повышение пропускной способности устройства за счет работы как в режиме опроса, так и в режиме прерывания.

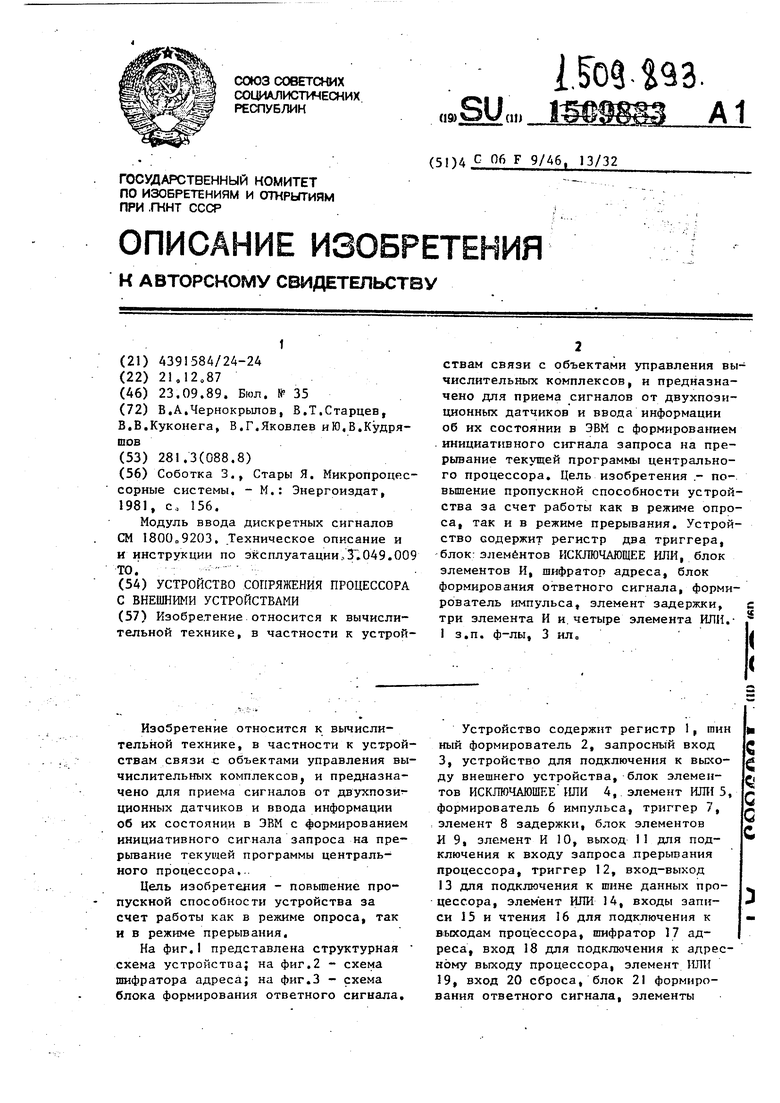

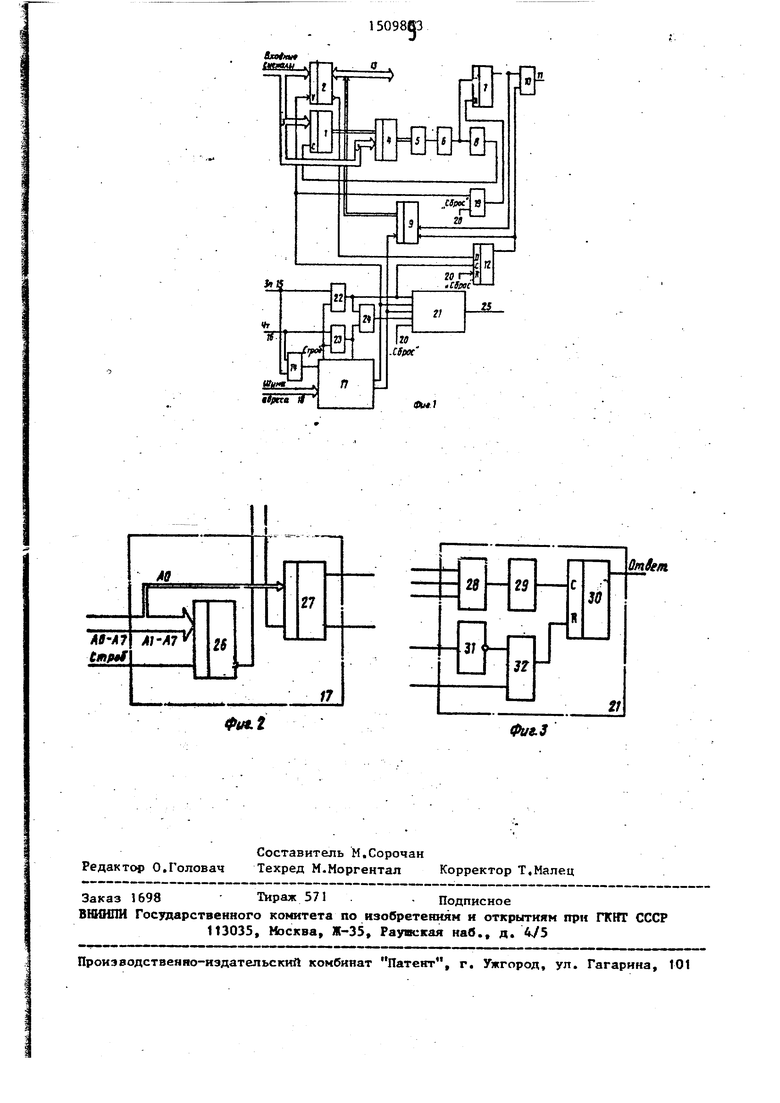

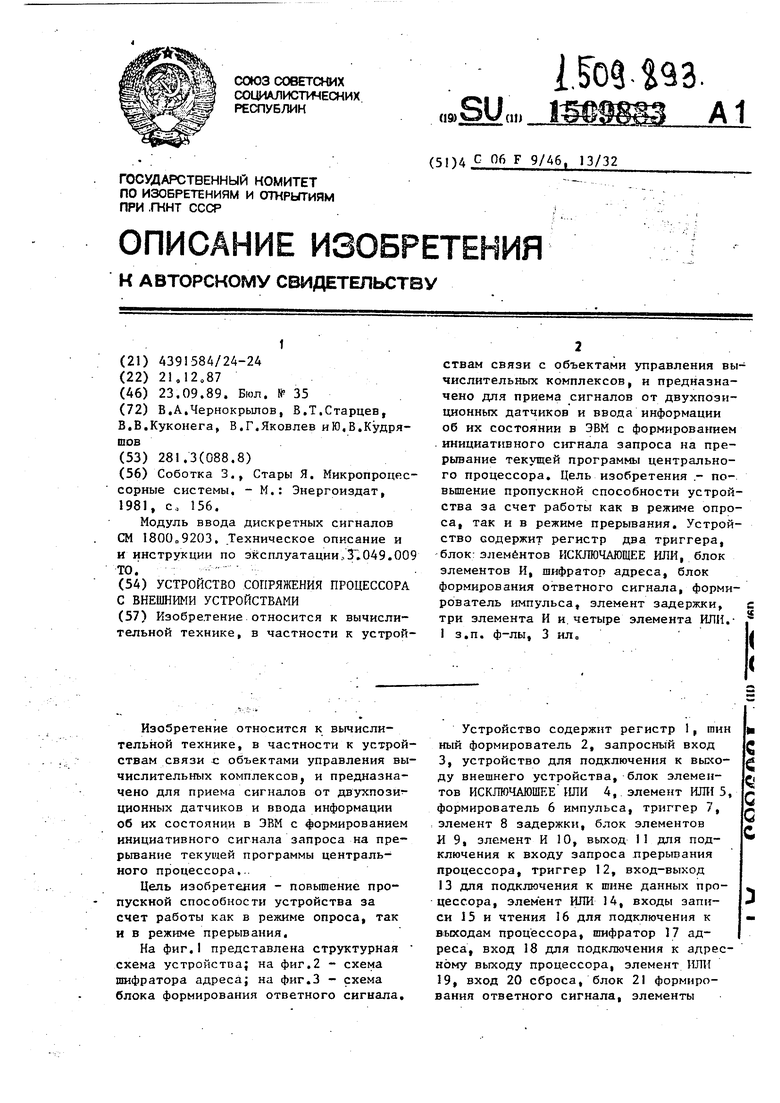

На фиг.1 представлена структурная схема устройства; на фиг.2 - схема шифратора адреса; на фиг.З - схема блока формирования ответного сигнала.

Устройство содержит регистр 1, тин ный формирователь 2, запросный вход 3, устройство ДЛЯ подключения к выходу внешнего устройства, блок элементов ИСКЛЮЧАЮЩЕЕ РШИ 4,. элемент ИЛИ 5, формирователь 6 импульса, триггер 7, , элемент 8 задержки, блок элементов И 9, элемент И 10, выход 11 для подключения к входу запроса прерывания процессора, триггер 12, вход-выход 13 ДЛЯ подключения к шине данных процессора, элемент ИЛИ 14, входы записи 15 и чтения 16 ДЛЯ подключения к выходам процессора, шифратор 17 адреса, вход 18 ДЛЯ подключения к адресному выходу процессора, элемент ИЛИ 19, вход 20 сброса, блок 21 формирования ответного сигнала, элементы

Q ff

W

v

150 зад ь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения ЭВМ с внешним накопителем | 1988 |

|

SU1672459A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1176341A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения ведущей и ведомой ЭВМ | 1989 |

|

SU1679493A1 |

Изобретение относится к вычислительной технике , в частности, к устройствам связи с объектами управления вычислительных комплексов, и предназначено для приема сигналов от двухпозиционных датчиков и ввода информации об их состоянии в ЭВМ с формированием инициативного сигнала запроса на прерывание текущей программы центрального процессора. Цель изобретения - повышение пропускной способности устройства за счет работы как в режиме опроса, так и в режиме прерывания. Устройство содержит регистр, два триггера, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов И, шифратор адреса, блок формирования ответного сигнала, формирователь импульса, элемент задержки, три элемента И и четыре элемента ИЛИ. 1 з.п. ф-лы, 3 ил.

И 22, 23, элемент ИЛИ 2А, выход 25 ответа для подключения к входу процессора, неполные дешифраторы 26 и 27 элемент ИЛИ 28, формирователь 29 им- пульса, триггер 30, элемент НЕ 31 и элемент ИЛИ 32,

Устройство работает следующим образом.

Перед началом работы (при включе- д НИИ энергопитания ЭВМ или нажатии кнопки Сброс) устройство устанавливается в исходное состояние сигналом Сброс по входу 20, что приводит к обнулению,триггеров 12 и 7 и означа- 15 ет состояние триггера .12 Запрещено и отсутствие изменений состояний на входах устройства. При обращении центрального процессора ЭВМ к устройству и режиме ЗАПИСЬ на информационном 20 входе-выходе 13 устанавливается информация, предназначенная для передачи в устройство: на входе 18 адреса комбинация сигналов, соответствующая коду базового адреса устройства и раз-25 решающая работу шинного формировате-. ля 2, управляющего триггерами 12 и 7, задающая направление передачи информации по информационному входу-выхог- ду 13 от системного интерфейса ЭВМ зо через шинный формирователь 2 в триггер 12. На выходе шифратора 17 адреса при наличии на входе 15 команды Запись вьфабатывается сигнал, поступающий через.дешифратор 26 (фиг,2) 5 и блок 21 () на выход 25 Ответ, устройства, означающий, что на входе- выходе 13 подготовлена информация для передачи и записи в триггер 12. Запись в триггер 12 логической 1 переводит 40 его в состояние Разрешено, а логического о в состояние Запрещено. Таким образом, осуществляется программное управление триггером 12.

45

При обращении процессора к устройству ввода по команде Чтение на входе 16 на входе 18 адреса устанавливается комбинация сигналов, соот- :;-ветствующая коду базового адреса на JQ - згаииях АО и А1 (фиг.2), комбинация :- 7Еигналов, соответствующая коду разре- :я1ения работы шинного формирователя 2 «ли блока элементов И, задающая на- ; правление лередачи ичформащш по вхо- ЯУ-выходу 13 в системный интерфейс ЭВМ при наличии команды Чтение на j входе 16, при этом на выходе ш1-1фра- тора 17 адреса вырабатывается сигнал.

3запроса, а блок элементов И 9 - о состоянии триггеров 7 и 12,

Рассмотрим работу устройства при формировании сигнала запроса на пре- рьшание..

В исходном состоянии оба входа все логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

4имеют одинаковый логический уровень, так как в регистре 1 записано текущее состояние входных сигналов 3. При изменении состояния i-ro входа 3 на противоположное входы i-ro логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ А имеют различные логические уровни и на выходе образуется сигнал несравнения, который через эле.мент ИЛИ 5 воздействует на вход формирователя 6 импульса, в результате чего на выходе формирователя 6 импульса вырабатывается импульс, который переводит триггер 7

в единичное состояние, и через элемент 8 задержки поступает на синхро- вход регистра I, в результате чего в i-й разряд.регистра 1 заносится новое состояние i-ro входа входного сигнала 3, что приводит i-й логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ А в исходное состояние. Таким образом, при условии нахождения триггера 12 в состоянии Разрешено оба входа элемента И 10 имеют уровень логической 1, что ведет к появлению сигнала запроса, на-- прерывание на вькоде 11 устройства. При вьтолнении центральным процессором ЭВМ операции Чтение из шинного формирователя 2 происходит определение, по какому именно входу прип1ел сигнал с входа 3 сигналов, и автоматически осуществляется сброс триггера 7 в нулевое состояние, что, в свою очередь, снимает сигнал запроса на прерывание с выхода 11 системного интерфейса ЭВМ.

Таким образом, устройство может работать в двух режимах: как устройство ввода дискретной информации, опрос которого производится в любое время по инициативе центрального процессора, и в режиме инициативной работы устройства, что позиоляст по сигналам от двухпозициониых датчиков-, соответственио выбрать нужную подпрограмму обработки полученного прег рывания, т.е. обеспечить мультипрограммный режим работы и управления несколькими независимыми технологическими объектами от одной ЭВМ.

Формула изобретения

1509883

са первого триггера, вход устройства для подключения к выходу записи про- , цессора соединен с первыми входами третьего элемента ИЛИ и второго элемента И, вьпсоп которого соединен с первьм входом четвертого элемента ИЛИ, вторым входом блока форт1рования ответного сигнала и тактовьи входом JO второго триггера, выход которого соединен с вторым пходом первого элемента И и вторым входом блока элементов И, третий вход которого соединен с третьим входом блока формирования J5 ответного сигнала и первым выходом шифратора адреса, вход устройства для подключения к выходу чтения процессора с вторым входом третьего элемента ИЛИ и первым- входом 20 третьего элемента И, выход которого соединен с первым стробнрующим входом шифратора адреса и вторым входом четвертого элемента ИЛИ, выход которого соединен с четвертым входом блока фор- 25 мирования ответного сигнала, пятый вход которого соединен с вторым входом второго элемента ИЛИ, управляющим входом шичпого формирователя и вторым выходом шифратора адреса, второй стро- ЗЯ бирующий вход и третий выход которого соединены соответственно с выходом третьего элемента ИЛИ и вторыми входами второго и третьего элементов И, выход элемента задержки соединен с входом записи регистра, выход шинного формирователя соединен с информационным входом второго триггера,

2, Устройство по п. 1, отличающееся тем, что,блок форми- Q рования ответного сигнала содержит триггер, два элемента ИЛИ, формирователь импульса и элемент НЕ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход и выг. 5 ход которого соединены соответственно с первым входом блока формирования ответного сигнала и входом Сброса триггера, выход которого является выходом блока формирования ответного 0 сигнала, второй и третий входы которого соединены соответственно с первым и вторым входами второго элемента ШШ, выход которого через формирователь импульса соединен с тактовым вхо- 5 дом триггера, четвертьй и пятый входы блока формирования ответного сигнала соединены соответственно с входом элемента НЕ и третьим входом второго элемента ШШ.

5

ixetnit

flpttu я

ф{л2

ЛиЛ

28

23

30

з; -I I I 32 Фи9.3

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропроцессорные системы | |||

| - М.: Энергоиздат, 1981, Со 156 | |||

| Всасывающе-нагнетательное устройство для передвижения судов | 1925 |

|

SU1800A1 |

| Техническое описание и и инструкции по эксплуатации,.009 ТО | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-09-23—Публикация

1987-12-21—Подача