тивной выборки результатов преобразования, а запоминающее устройство 9 выполнено ассоциативным с плавающей адресацией каналов. Преобразователь также содержит многофазный генератор 5, блок 6 управления, счетчик 7 пре,образования, формирователь 8 адреса. Данный преобразователь позволяет по высить зксплуатационную эффективность аппаратуры научных исследований и повысить достоверность получаемых результатов. 7 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1988 |

|

SU1654822A1 |

| УСТРОЙСТВО СОРТИРОВКИ СЛОВ | 2002 |

|

RU2223538C2 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU424233A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сбора и анализа данных о работе электронной вычислительной машины | 1974 |

|

SU522502A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2212715C2 |

| Адаптивный статистический анализатор | 1980 |

|

SU955090A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1429169A1 |

Изобретение может быть использовано в цифровых измерительных приборах и информационно-измерительннх комплексах. Целью изобретения является повышение надежности и повышение достоверности преобразования. Для достижения цели в многоканальный преобразователь интервалов времени в код введены блок 4 асинхронно-синхронного ввода и селектор 10 ассоциа

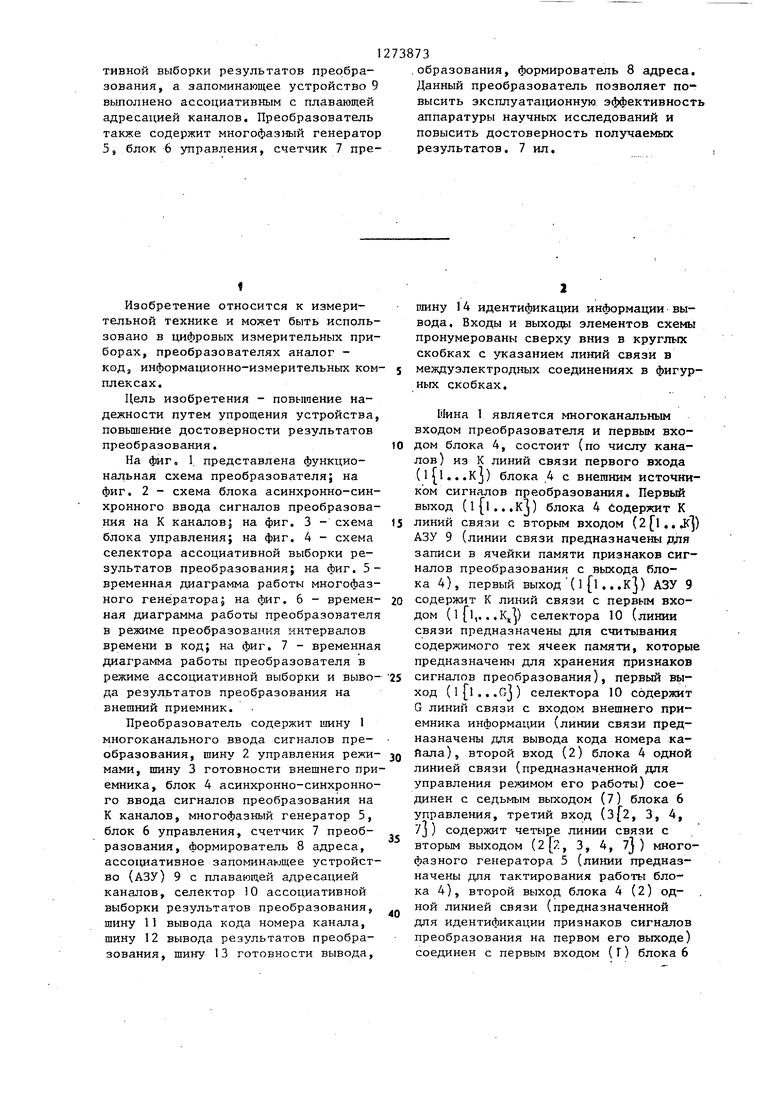

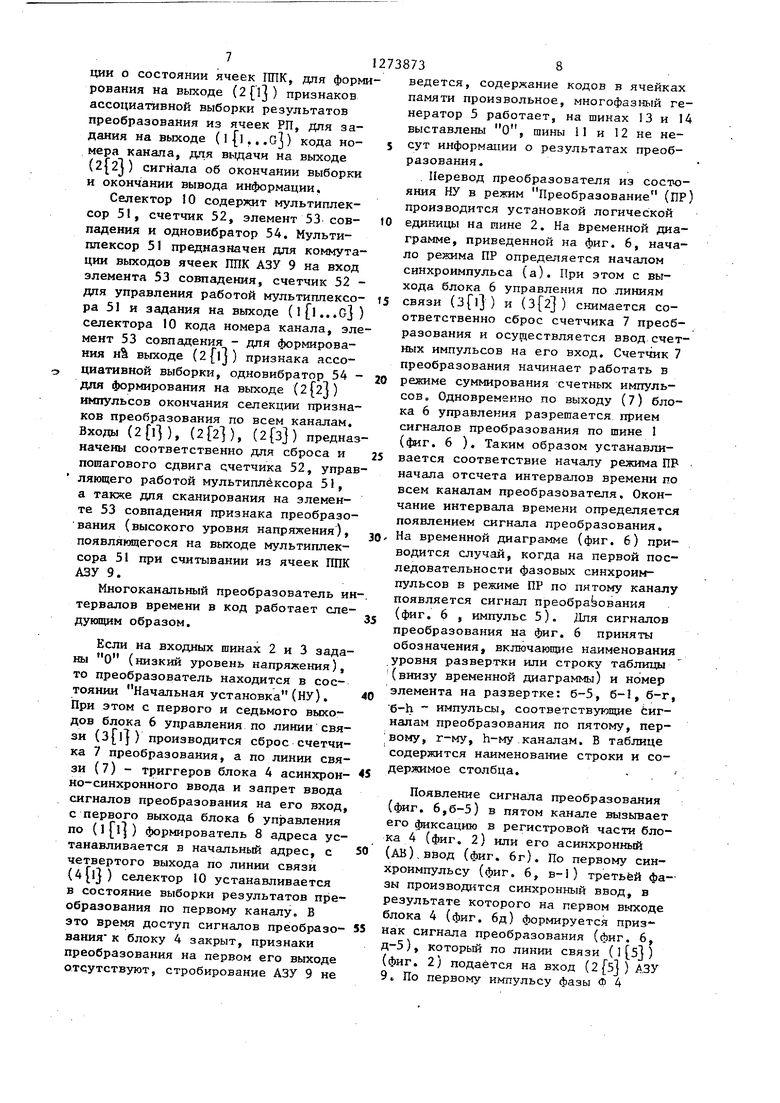

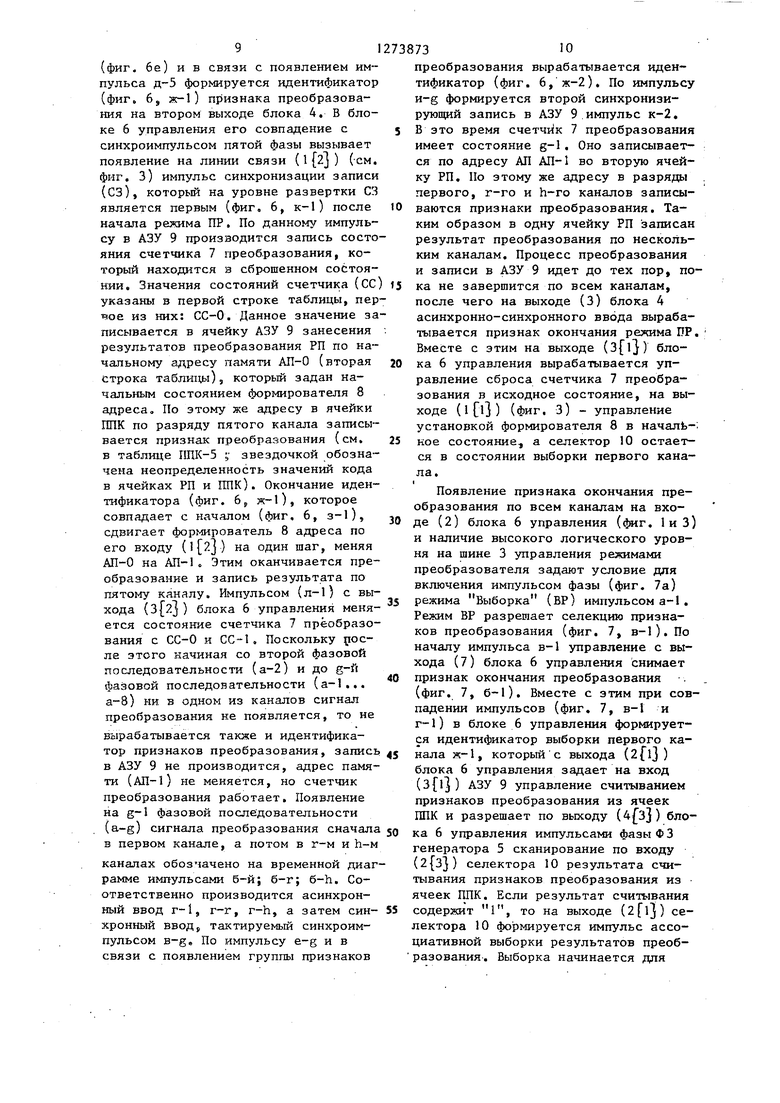

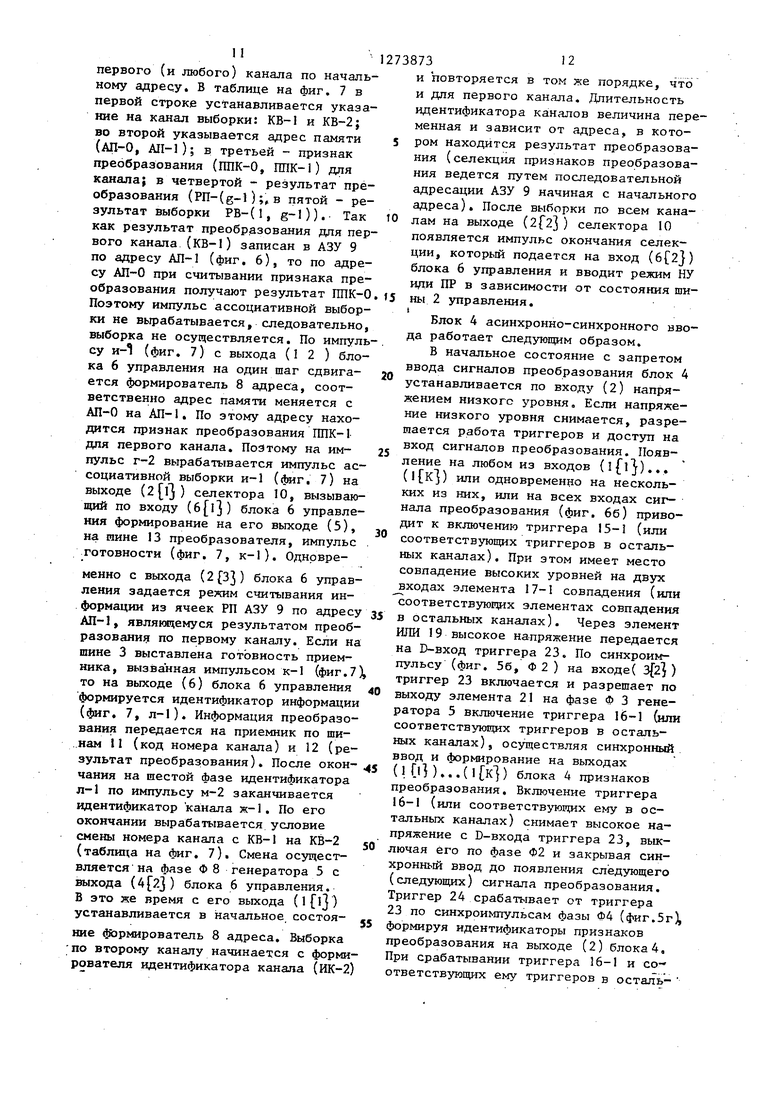

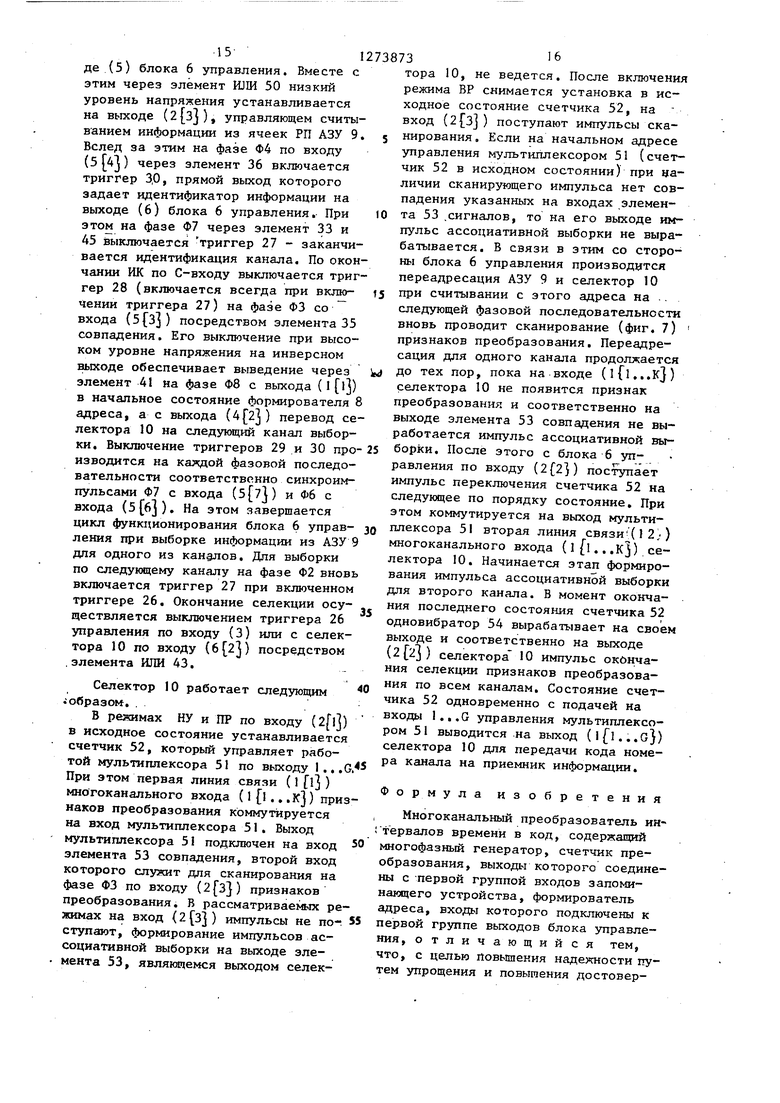

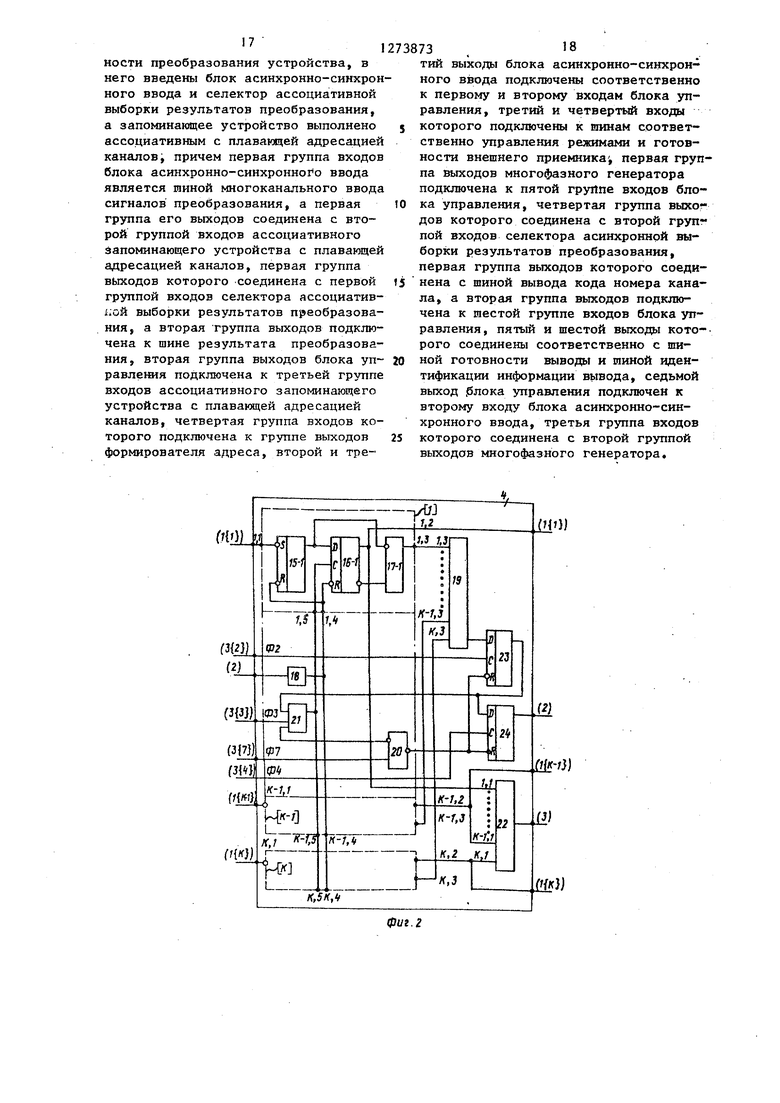

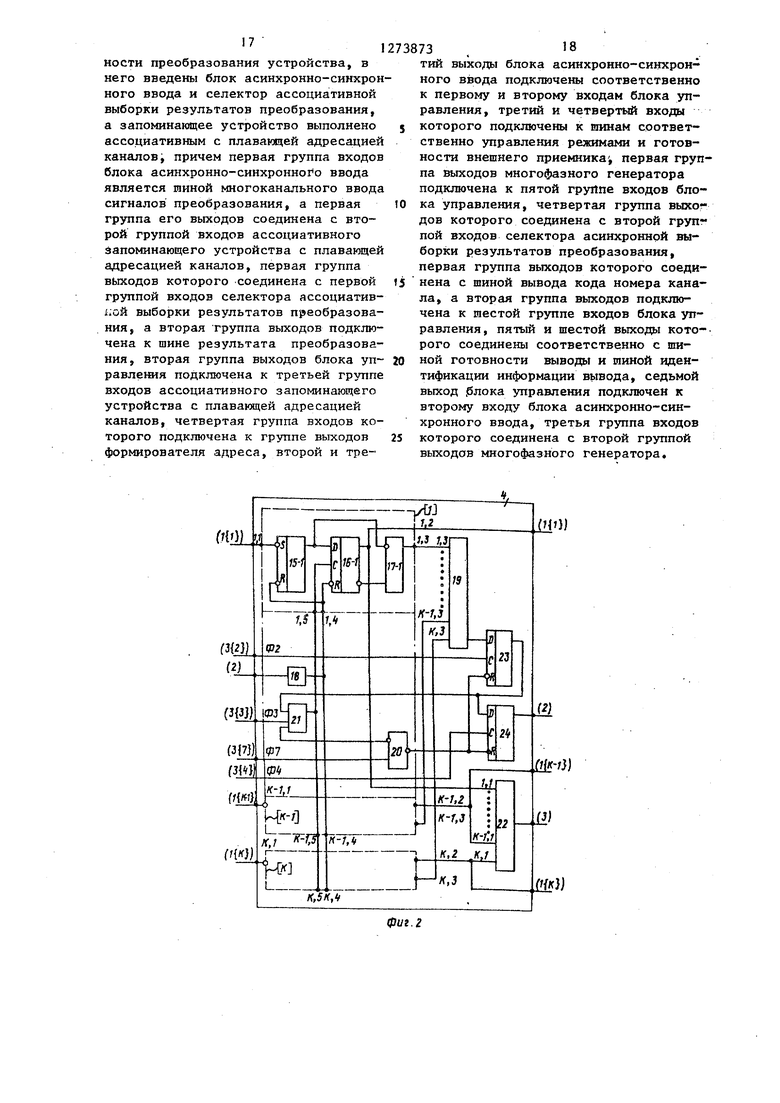

Изобретение относится к измерительной технике и может быть использовано в цифровых измерительных приборах, преобразователях аналог код, информационно-измерительных ком плексах. Цель изобретения - повышение надежности путем упрощения устройства, повьшение достоверности результатов преобразования. На фиг, 1. представлена функционадьная схема преобразователя; на фиг, 2 - схема блока асинхронно-синхронного ввода сигналов преобразования на К каналов; на фиг. 3 - схема блока управления; на фиг. А - схема селектора ассоциативной выборки результатов преобразования; на фиг. 5временная диаграмма работы многофазного генератора, на фиг, 6 - временная диаграмма работы преобразователя в режиме преобразования интервалов времени в код; на фиг, 7 - временная диаграмма работы преобразователя в режиме ассоциативной выборки и вывода результатов преобразования на внешний приемник. Преобразователь содержит шину 1 многоканального ввода сигналов преобразования, шину 2 управления режимами, шину 3 готовности внешнего при емника, блок 4 асинхронно-синхронного ввода сигналов преобразования на К каналов, многофазный генератор 5, блок 6 управления, счетчик 7 преобразования, формирователь 8 адреса, ассо1Ц1ативное запоминающее устройство (АЗУ) 9 с плавающей адресацией каналов, селектор 10 ассоциативной выборки результатов преобразования, шину 11 вывода кода номера канала, шину 12 вывода результатов преобразования, шину 13 готовности вывода. пшну 14 идентификации информации вывода. Входы и выходы элементов схемы пронумерованы сверху вниз в круглых скобках с указанием линий связи в междуэлектродных соединениях в фигурных скобках. Шина I является многоканальным входом преобразователя и первым входом блока 4, состоит (по числу каналов) из К линий связи первого входа (.,.Kj) блока 4 с внешним источником сигналов преобразования. Первый выход (I{I,,,K) блока 4 Содержит К линий связи с вторым входом (,,,K) АЗУ 9 (линии связи предназначены для записи в ячейки памяти признаков сигналов преобразования с выхода блока 4), первый выход(,,.К) АЗУ 9 содержит К линий связи с первым входом (ifl,, ,,Кцр селектора 10 (линии связи предназначены для считывания содержимого тех ячеек памяти, которые предназначены для хранения признаков сигналов преобразования), первый выход (,,,GJ) селектора 10 содержит G линий связи с входом внешнего приемника информации (линии связи предназначены для вывода кода номера кайала), второй вход (2) блока 4 одной линией связи (предназначенной для управления режимом его работы) соединен с седьмым выходом (7) блока 6 управления, третий вход (, 3, 4, 7j) содержит четыре линии связи с вторым выходом (, 3, 4, 7j ) многофазного генератора 5 (линии предназначены для тактирования работы блока 4), второй выход блока 4 (2) одной линией связи (предназначенной для идентификации признаков сигналов преобразования на первом его выходе) соединен с первым входом (Г) блока 6 управления третий выход (3) одной линией связи (предназначенной для передачи признака окончания ввода сигналов преобразования по всем каналам) соединен с вторым входом (2) блока 6 управления, третий вход (З) и четвертый вход (4) которого соединены соответственно с шиной. 2 и гаиной 3, пятый вход (...8) блока 6 управления содержит восемь линий связи с первым выходом (1 1...83) многофазного генератора 5 (линии свя зи предназначены для тактирования ра боты блока 6 управления), шестой вход 6{1, 2j) блока 6 управления со держит две линии связи с вторым выходом (, 2J) селектора 10 (первая из линий связи предназначена для ввода в блок 6 управления признака ассоциативной выборки результатов преобразования, вторая - для ввода импульса,:-который является признаком окончания выборки результатов преобразования по всем каналам), третий выход (, 21) блока 6 управле 1ия содержит две линии связи с первым входом (, 2| ) счетчика 7 преобразования (первая из них предназначена для сброса счетчика, вторая - для ввода счетных импульсов), второй выход (2(1, 2, 3J) блока 6 управления содержит три линии связи с третьим входом (3fl, 2, З) АЗУ 9 (предназначенных для управления режимами его работы), первый выход (I l , 2) блока 6 управления содержит две линии связи с первым входом ( 2j ) формиро вателя В адреса (предназначенных для его начальной установки и пошагового сдвига), четвертый выход (, 2, З блока 6 управления содержит три линии связи с вторым входом (2fl, 2, 3j ) селектора 10 (предназначенных для начальной установки, пошагового сдвига и сканирования селектора 10), пятый (5) и шестой (6) выходы соединены соответственно с шинами 13 и 14 преобразователя. Многофазный генератор 5 предназна чен ддя формирования восьми серий синхроимпульсов (фиг, 5а-з) на восьми равных между собой следующих друг за другом временных фазах Ф1-Ф8, составляняцих полный период циклического функционирования генератора. Первый выход- (...в ) многофазного генератора 5 содержит восемь линий связи каждая из которых имеет номер, совпа734дающий с номером фазы в фигурных скобках. Второй выход (, 3, 4, генератора 5 содержит линии ввода синхронизирующих импульсов второй, третьей, четвертой и седьмой фаз. Генератор с указаннь1м видом функциони- рования может быть построен на любой из известных схем, в том числе по схеме последовательного соединения задающего генератора, делителя частоты и дешифратора на три двоичных входа и восемь выходов. Счетчик 7 преобразования предназначен для преобразования интервалов времени в код путем последовательного счета импульсов с известным периодом следования на преобразуемом интервале времени. Счетчик преобразования с числом разрядов N может быть построен с использованием интегральных микросхем типа К155ИЕ5, Формирователь 8 адреса предназначен для задания кодовой последовательности, посредством которой осуществляется последовательная адреса- ция ячеек памяти АЗУ 9 при записи и считывании информации; Формирователь 8 может быть-построен на счетчике последовательного типа с общим коэффициентом пересчета, равным числу каналов К. Вход (1f 1, 2})формирователя адреса 8 предназначен для сброса счетчика и задания на его входе счетных импульсов. Число двоичных разрядов на выходе (...Gj) равно G, где . АЗУ 9 предназначено для записи по входу (...Й) информации о признаках преобразования и по входу(.. .N}-) результатов преобразования, для хранения , последующей выборки и вывода нформа1Ц1и на внешний приемник АЗУ 9 содержит два вида ячеек: ППК - К-разрядные ячейки запоминания и хранения ризнаков преобразования для каждого канала и РП - N-разрядные ячейки заоминания и хранения результатов пребразования с плавающей -адресацией аналов. Общее количество ячеек РП авно числу каналов К, число разряов в ячейке равно числу раз1)ядов N четчика преобразования. АЗУ 9 может ыть выполнено на любой из известных хем с применением, например, микрохем типа К155РУ2. Блок 4 предназначен для поканалього асинхронного ввода сигналов пребр зования по входам (),...,

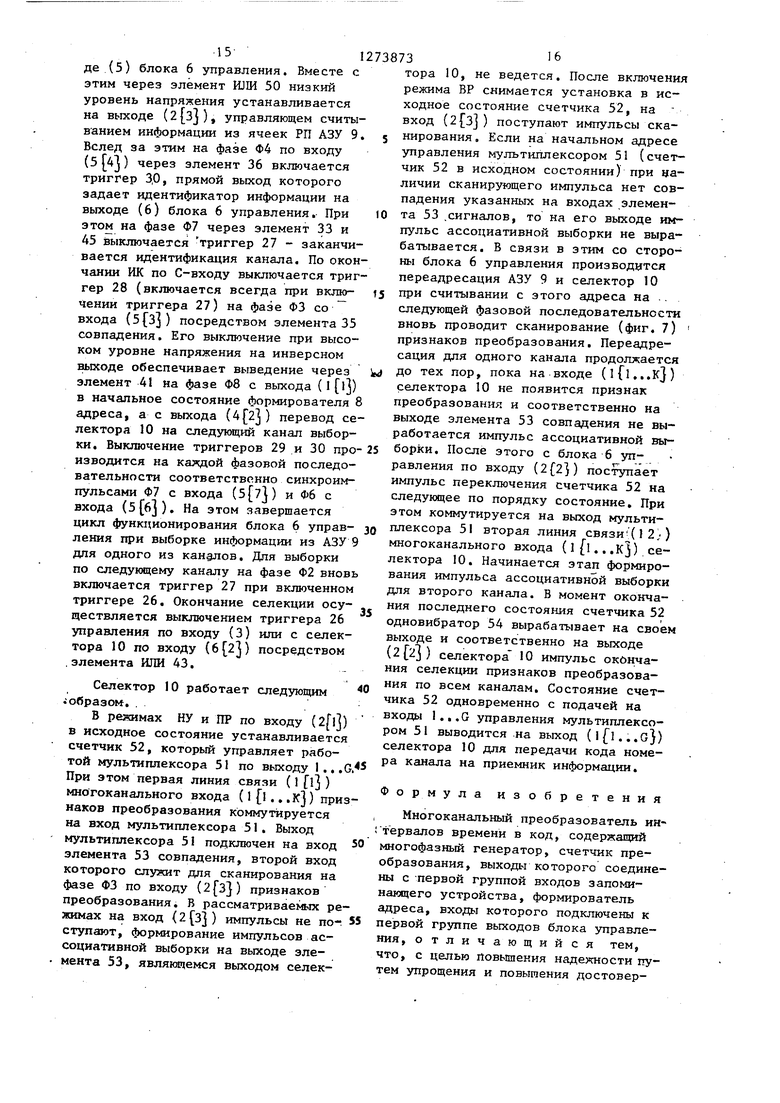

(1 {К-l ) 5 ( к ) 5 nokaHanbHoro синхронного (тактируемого) формирования по входным сигналам приянаков преобразования на выходах {1 (ij ),..,, (), (), выдачи импульсов идентификации на выходе (2), выдачи признака окончания ввода сигналов по всем каналам на выходе (З). Блок 4 содержит регистровую часть, которая состоит из однотипных по всем каналам преобразования ячеек, пронумерованных .в квадратных скобках от ГО до к. Каждая ячейка (на фиг, 2 см. l) содержит триггер 15-1 I5-K асинхронного ввода, триггер 161 - 16-К синхронного формирования признака преобразования, элементы 17-1 - 17-К совпадения, предназначенные для запуска общей для всех каналов синкрониэирующей частоты схемы, собранной на элементах ИЛИ 18 - 20, элементах 21 и 22 совпадения и триггерах 23 и 24, Синхронизирующая часть схемь предназначена для формирования на выходе элемента 21 совпадения импульсов управления работой триггеров 16-1 - 16-К, для выдачи с выхода триггера 24 идентификатора признаков преобразования и с выхода элемента 22 совпадения признака окончания ввода сигналов преобразования . Регистровые ячейки имеют по одному автономному входу 1,1... К,1, которые являются входами (1{}}).,о() блока 4 соответствен но, по два автономных выхода 1, 2.,. Kj 2 и 1, З.а.К, 3 первые из которых являются выходами ( )... (1 кр блока 4, а вторые; подсоединены к входам элемента ЯЛИ 19, выходы 1 , 4.. К, 4 предназначены для установки триггеров регистровых ячеек в исходное состояние, выходы 1, 5...К, 5 для синхронизации формирования признаков преобразования. Входы (), (), (), (3{7) блока 4 предназначены для тактирования его работы синхроимпульсами, фаза которых указана в обозначениях линий связи в фигурных скобках. Блок 4 может быт построен, в частности, на микросхема серии К155«

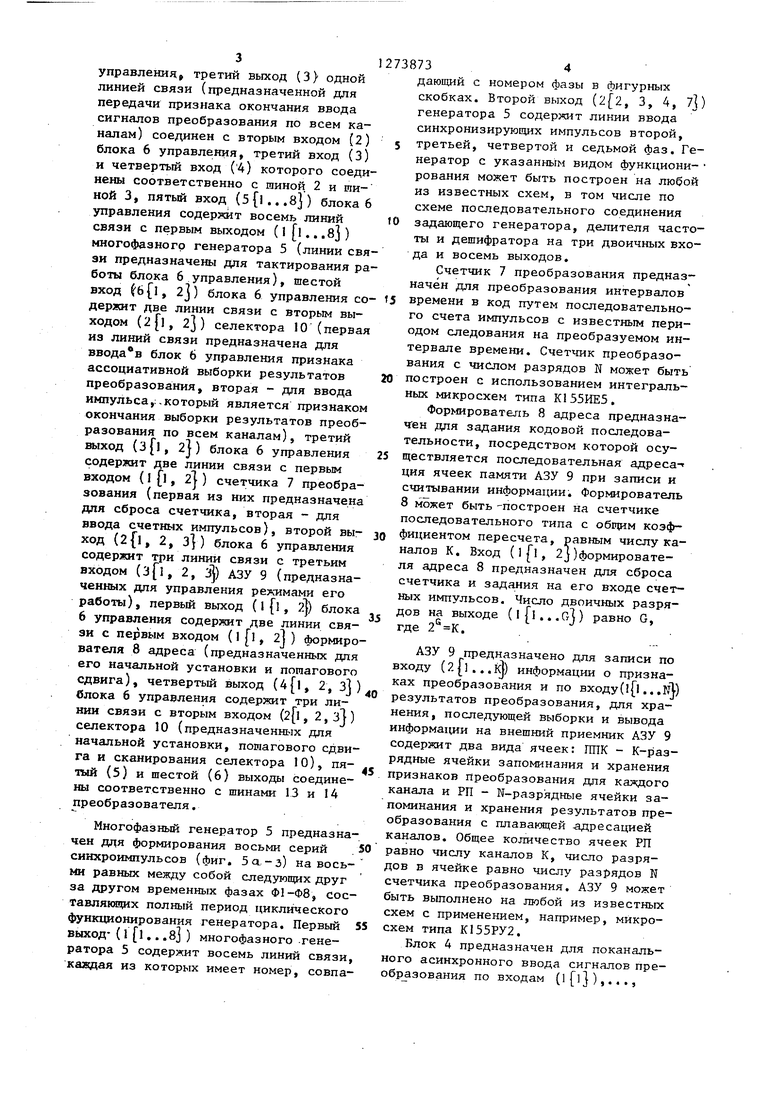

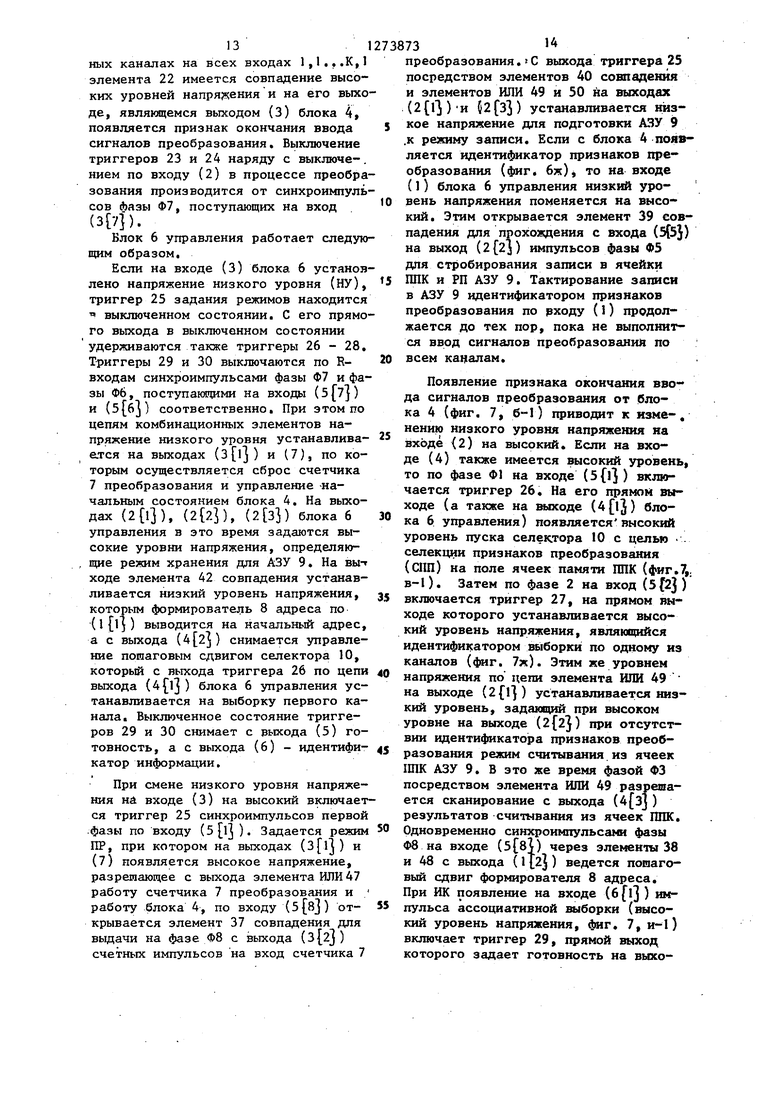

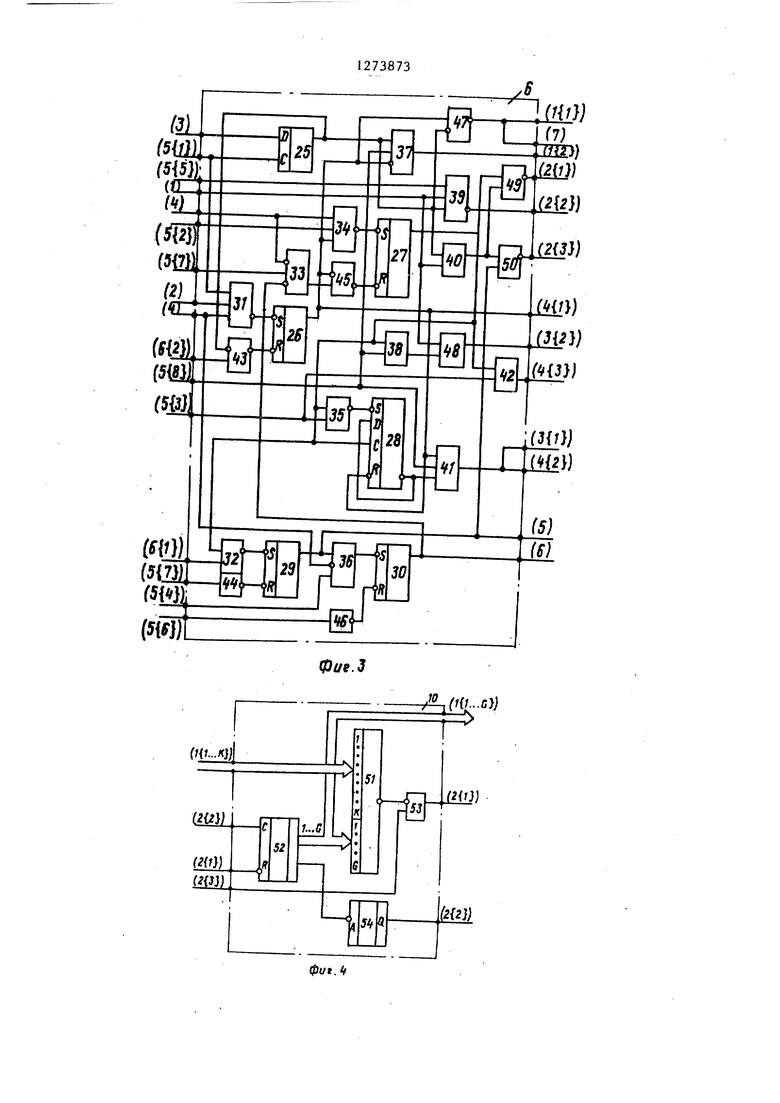

Блок 6 управления предназначен для задания режимов и осуществления взаимодействия меазду отдельными блоками преобразователя, а также для управления взаимодействием между преобразователем и внешними средствами

ввода сигналов и вывода результатов преобразования. Он содержит триггер 25 для задания режима преобразова-. ния, триггер 26 начальной установки и пуска селектора 10, триггер 27 идентификации поканальной выборки результатов преобразования, триггер 28 смены канала выборки, триггер 29 готовности, триггер 30 идентификации информации на выходе преобразователя элементы 31-42 совпадения и элементы ШШ 43-50, предназначенные для управления работойтриггеров 25-30 и формирования на выходе блока 6 управления сигналов, обеспечивающих взаимодействие блоков структурной схемы преобразователя и его взаимодействие с внешними устройствами. Выходы блока 6 управления предназначены: (3{lj), () - для управления сбросом счетчика преобразования и задания на его входе счетньк импульсов; (20), (2(2}), () - дня управления режимами работы АЗУ 9, причем линия связи (2f2j) предназначена для стробирования АЗУ 9 при синхронной записи.по одному и тому же адресу признаков преобразования в ячейки ППК и результатов преобразования в ячейки РП; ( - для управления считыванием признаков преобразования из ячеек ППК; (2f3J) для управления считыванием результатов преобразования из ячеек РП; (ifl) ( ) - для управления установкой в начальное состояние и управления пошагЬвым сдвигом формирователя 8 адреса соответственно; (), ()для управления селектором 10 начальной установки, пошаговым сдвигом и. сканированием результатов считывания признаков преобразования; (5) - для вывода готовности; (6) - для вывода идентификатора информации; (7) -для управления доступом сигналов преобразования на вход преобразователя. Входы (О, (2) блока 6 управления предназначены соответственно для ввода импульсов идентификации появления признаков преобразования и признаков окончания ввода сигналов преобразования; входы (3) и (4) - для задания режимов работы; входы (5fl )../5{8рдля тактирования работы блока 6 управления.

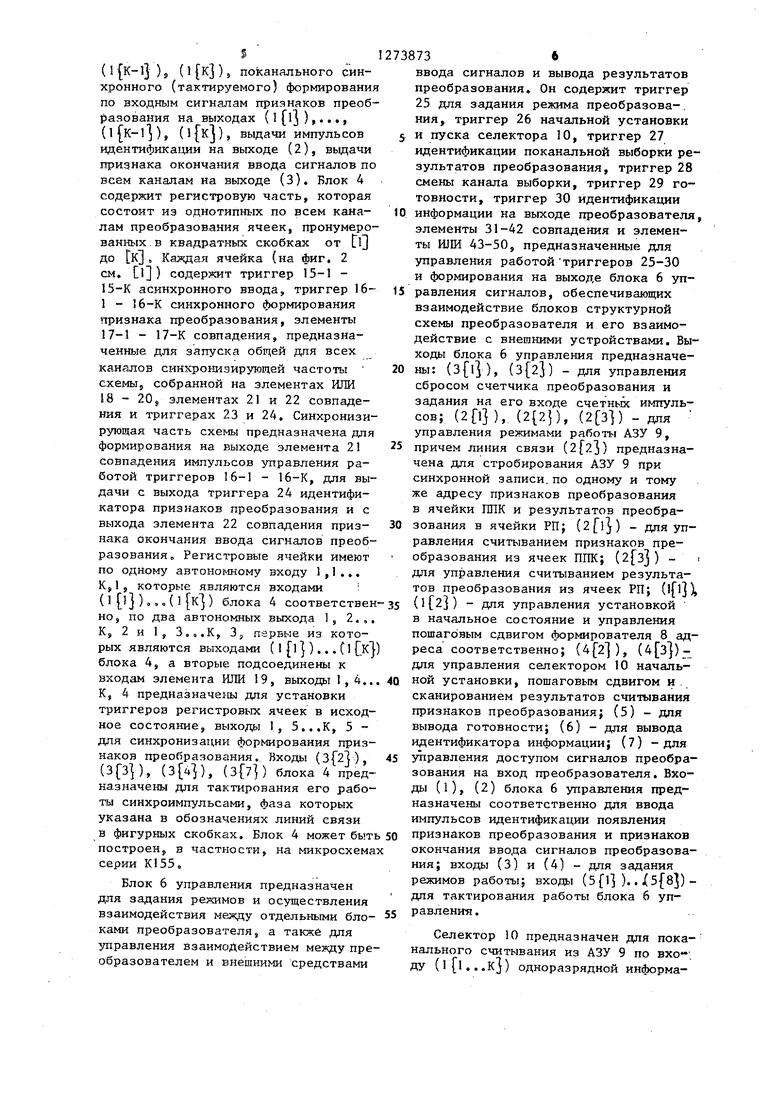

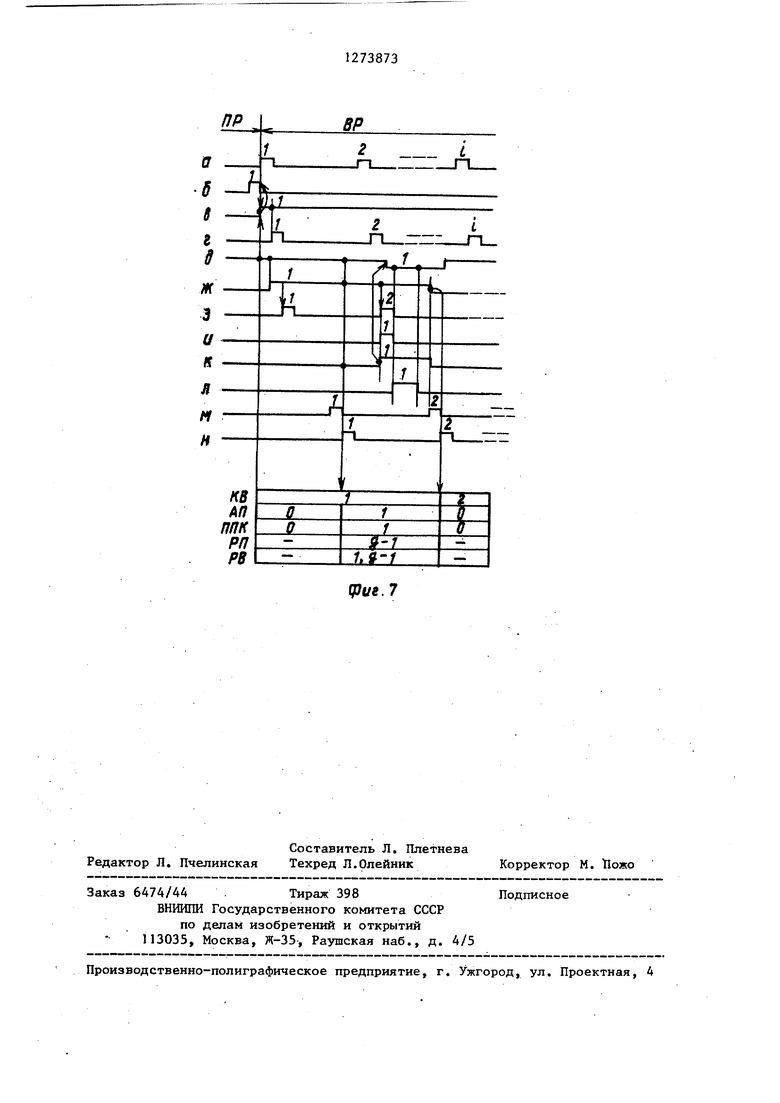

Селектор 10 предназначен для поканального считывания из АЗУ 9 по вхо-; ДУ (...Kj) одноразрядной информации о состоянии ячеек ГШК, для форм рования на выходе (2{l) признаков ассоциатавной выборки результатов преобразования из ячеек РП, для задания на выходе (1 {) .,.G) кода номера канала, для выдачи на выходе (2{2J) сигнала об окончании выборки и окончании вывода информации, Селектор 10 содержит мультиплексор 51, счетчик 52, элемент 53 совпадения и одновибратор 54. Мультиплексор 51 предназначен для коммута ции выходов ячеек ППК АЗУ 9 на вход элемента 53 совпадения, счетчик 52 для управления работой мультиплексоpa 51 и задания на выходе (,..С} селектора 10 кода номера канала, эле мент 53 совпадения - для формирования н выходе (2 f 1 ) признака ассоциативной выборки, одновибратор 54 для формирования на выходе (2f2j) импульсов окончания селекции признаков преобразования по всем каналам. Входы (2fl), (2 2), () предназ начены соответственно для сброса и пошагового сдвига счетчика 52, управ ляющего работой мультиплексора 5I, а также для сканирования на элементе 53 совпадения признака преобразования (высокого уровня напряжения), появлякяцегося на выходе мультиплексора 51 при считывании из ячеек ППК АЗУ 9. Многоканальный преобразователь ин тервалов времени в код работает следукнцим образом. Если на входных шинах 2 и 3 заданы О (низкий уровень напряжения), то преобразователь находится в состоянии Начальная установка(НУ). При этом с первого и седьмого выходов блока 6 управления по линии связи () производится сброс счетчика 7 преобразования, а по линии связи (7) - Триггеров блока 4 асинхрон- но-синхронного ввода и запрет ввода сигналов преобразования на его вход, с первого выхода блока 6 управления по (1 1}) формирователь 8 адреса устанавливается в начальный адрес, с четвертого выхода по линии связи (4{lJ) селектор 10 устанавливается в состояние выборки результатов преобразования по первому каналу. В это время доступ сигналов преобразования к блоку 4 закрыт, признаки преобразования на первом его выходе отсутствуют, стробирование АЗУ 9 не ведется, содержание кодов в ячейках памяти произвольное, многофазный генератор 5 работает, на шинах 13 и 14 выставлены О, шины 11 и 12 не несут информации о результатах преобразования. Перевод преобразователя из состояния НУ в режим преобразование (ПР) производится установкой логической единицы на шине 2. На временной диаграмме, приведенной на фиг. 6, начало режима ПР определяется началом синхроимпульса (а). При этом с выхода блока 6 управления по линиям связи (3(|} ) и () снимается соответственно сброс счетчика 7 преобразования и осуществляется ввод счетных импульсов на его вход. Счетчик 7 преобразования начинает работать в режиме суммирования счетных импульсов . Одновременно по выходу (7) блока 6 управления разрешается прием сигналов преобразования по шине 1 (фиг. 6 ). Таким образом устанавливается соответствие началу режима ПР начала отсчета интервапов времени по всем каналам преобразователя. Окончание интервала времени определяется появлением сигнала преобразования. На временной диаграмме (фиг. 6) приводится случай, когда на первой последовательности фазовых синхроимпульсов в режиме ПР по пятому каналу появляется сигнал преобразования (фиг. 6 , импульс 5). Для сигналов преобразования на фиг. 6 приняты обозначения, включающие наименования уровня развертки или строку таблицы (внизу временной диаграммы) и номер элемента на развертке: 6-5, 6-1, б-г, б-h импульсы, соответствующие :игналам преобразования по пятому, первому, г-му, h-му.каналам. В таблице содержится наименование строки и содержимое столбца.- . Появление сигнала преобразования (фиг. 6,6-5) в пятом канале вызывает его фиксацию в регистровой части блока 4 (фиг, 2) или его асинхронный (АН),ввод (фиг. 6г). По первому синроимпульсу (фиг. 6, B-i) третьей фазы производится синхронный ввод, в езультате которого на первом выходе блока 4 (фиг. 6д) формируется приз ак сигнала преобразования (фиг. 6, -5), который по линии связи () (фиг. 2) подаётся на вход (2 5) АЗУ . По первому импульсу фазы Ф 4

(фиг. бе) ив связи с появлением импульса д-5 формируется идентификатор (фиг. 6, ж-1) признака преобразования на втором выходе блока 4, В блоке 6 управления его совпадение с синхроимпульсом пятой фазы вызывает появление на линии связи (I (2 ) Сем. фиг. 3) импульс синхронизации записи (СЗ), который на уровне развертки СЗ является первым (фиг, 6, к-1) после начала режима ПР, По данному импульсу в АЗУ 9 производится запись состояния счетчика 7 преобразования, который находится в сброшенном состоянии. Значения состояний счетчика (СС указаны в первой строке таблицы, перчое из них: СС-0. Данное значение записывается в ячейку АЗУ 9 занесения результатов преобразования РП по начальному адресу памяти АП-0 (вторая строка таблихда), который задан начальным состоянием формирователя 8 адреса. По этому же адресу в ячейки ППК по разряду пятого канала записывается признак преобразования (см. в таблице ППК-5 ; звездочкой обозначена неопределенность значений кода в ячейках РП и ППК). Окончание идентификатора (фиг. 6, ж-), которое совпадает с началом (фиг. 6, з-1), сдвигает формирователь 8 адреса по его входу ( ) на один шаг, меняя АП-0 на АП-1. Этим оканчивается преобразование и запись результата по пятому каналу. Импульсом () с выхода () блока 6 управления меняется состояние счетчика 7 преобразования с СС-0 и СС-1, Поскольку росле этого начиная со второй фазовой последовательности (а-2) и до g-й фазовой последовательности (а-1... а-З) ни в одном из каналов сигнал преобразования не появляется, то не

вырабатывается также и идентификатор признаков преобразования, запись в АЗУ 9 не производится, адрес памяти (АП-1) не меняется, но счетчик преобразования работает. Появление на g-1 фазовой последовательности (a-g) сигнала преобразования сначала в первом канале, а потом в г-м и h-м

каналах обозначено на временной диаграмме импульсами б-й; б-г; б-h. Соответственно производится асинхронный ввод г-1, г-г, r-h, а затем синхронный ввод, тактируемый синхроимпульсом B-g, По импульсу e-g и в связи с появлением группы признаков

преобразования вырабатывается идентификатор (фиг. 6, ж-2). По импульсу H-g формируется второй синхронизирующий запись в АЗУ 9 импульс к-2. В это время счетчик 7 преобразования имеет состояние g-1. Оно записывается по адресу АП АП-1 во вторую ячейку РП. По этому же адресу в разряды первого, г-го и h-ro каналов записываются признаки преобразования. Таким образом в одну ячейку РП записан результат преобразования по нескольким каналам. Процесс преобразования и записи в АЗУ 9 идет до тех пор, пока не завершится по всем каналам, после чего на выходе (3) блока 4 асинхронно-синхронного ввода вырабатывается признак окончания режима ПР. Вместе с этим на выходе (3{lj) блока 6 управления вырабатывается управление сброса счетчика 7 преобразования в исходное состояние, на выходе (1 l ) (фиг. 3) - управление установкой формирователя 8 в началЬкое состояние, а селектор 10 остается в состоянии выборки первого канала.

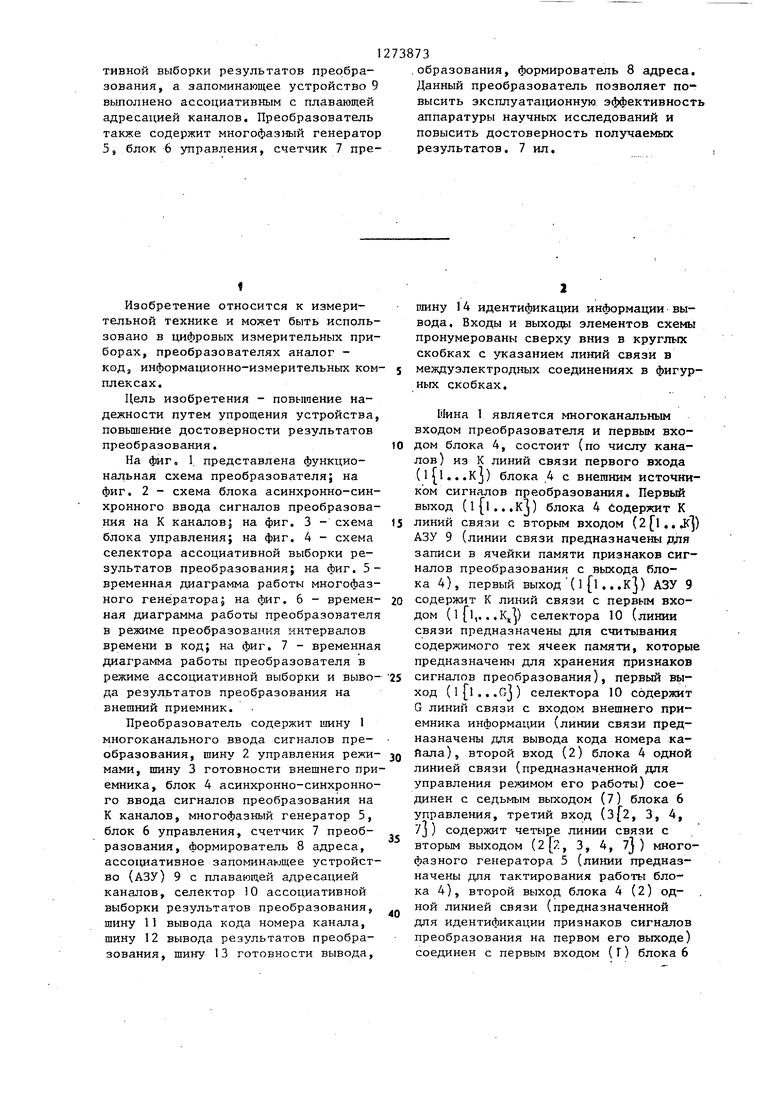

Появление признака окончания преобразования по всем каналам на входе (2) блока 6 управления (фиг. 1иЗ) и наличие высокого логического уровня на шине 3 управления режимами преобразователя задают условие для включения импульсом фазы (фиг. 7а) режима Выборка (ВР) импульсом а-1 . Режим ВР разрепшет селекцию признаков преобразования (фиг. 7, в-1). По началу импульса в-1 управление с выхода (7) блока 6 управления снимает признак окончания преобразования (фиг. 7, 6-1). Вместе с этим при совпадении импульсов (фиг. 7, в-1 и г-1) в блоке 6 управления формируется идентификатор выборки первого канала ж-1, который с выхода (2fl3 ) блока 6 управления задает на вход (3{1) АЗУ 9 управление считыванием признаков преобразования из ячеек ППК и разрешает по выходу () блоа 6 управления импульсами фазыФЗ генератора 5 сканирование по входу (2{3) селектора 10 результата считывания признаков преобразования из чеек ППК. Если результат считывания содержит 1, то на выходе (2fl}) сеектора 10 формируется импульс ассоиативной выборки результатов преобазования. Выборка начинается для первого (и любого) канала по начальному адресу. В таблице на фиг. 7 в первой строке устанавливается указание на канал выборки: КВ-1 и КВ-2; во второй указывается адрес памяти (АП-О, AII-1); в третьей - признак преобразования (ППК-О, 1ШК-1) для канала; в четвертой - результат преобразования (Pn-(g-l);, в пятой - результат выборки РВ-(1, g-l)). Так как результат преобразования для пер вого канала (КВ-1) записан в АЗУ 9 по адресу АП-1 (фиг, 6), то по адресу АП-0 при считывании признака преобразования получают результат ППК-О Поэтому импульс ассоциативной выборки не вьфабатывается, следовательно, выборка не осуществляется. По импуль су и-1 (фиг. 7) с выхода (12) блока 6 управления на один шаг сдвигается формирователь 8 адреса, соответственно адрес памяти меняется с АП-0 на АП-1, По этому адресу находится признак преобразования Ш1К-1 для первого канала. Поэтому на импульс г-2 вырабатывается импульс ассоциативной выборки и-1 (фиг, 7) на выходе (2{l) селектора 10, вызывающий по входу () блока 6 управления формирование на его выходе (5), на шине 13 преобразователя, импульс готовности (фиг. 7, к-1). Одновременно с выхода (2(3) блока 6 управления задается режим считывания информации из ячеек РП АЗУ 9 по адресу АП-1, являющемуся результатом преобразовалия по первому каналу. Если на шине 3 выставлена готовность приемника, вызванная импульсом к-1 (фиг.7 то на выходе (6) блока 6 управления формируется идентификатор информации (фиг, 7, л-1). Информация преобразования передается на приемник по ши..нам 11 (код номера канала) и 12 (ре. зультат преобразования). После окончания на шестой фазе идентификатора л-1 по импульсу м-2 заканчивается идентификатор канала ж-1. По его окончании вырабатывается условие смены номера канала с КВ-1 на КВ-2 (таблица на фиг, 7). Смена осуществляется на фазе Ф 8 генератора 5 с выхода () блока 6 управления. В это же время с его выхода (1 f 1J ) устанавливается в начальное состояние рмирователь 8 адреса. Выборка ПО второму каналу начинается с форми рователя идентификатора канала (ИК-2 и повторяется в том же порядке, что и для первого канала. Длительность идентификатора каналов величина переменная и зависит от адреса, в котором находится результат преобразования (селекция признаков преобразования ведется путем последовательной адресации АЗУ 9 начиная с начального адреса). После выборки по всем каналам на выходе (2f2) селектора 10 появляется импульс окончания селекции, который подается на вход () блока 6 управления и вводит режим НУ иди ПР в зависимости от состояния шины 2 управления. 1 Блок 4 асинхронно-синхронного ввода работает следуюпц1М образом. В начальное состояние с запретом ввода сигналов преобразования блок 4 устанавливается по входу (2) напряжением низкого уровня. Если напряжение низкого уровня снимается, разрешается работа триггеров и доступ на вход сигналов преобразования. Появление на любом из входов (ifl}).., () или одновременно на нескольких из них, или на всех входах сигнала преобразования (фиг. 6б) приводит к включению триггера 15-1 (или соответствующих триггеров в остальных каналах). При этом имеет место совпадение высоких уровней на двух входах элемента I7-I совпадения (или соответствующих элементах совпадения в остальных каналах). Через элемент иЛИ 19 высокое напряжение передается на D-вход триггера 23. По синхроимпульсу (фиг. 56, Ф 2 ) на входе( ) триггер 23 включается и разрешает по выходу элемента 21 на фазе Ф 3 генератора 5 включение триггера 16-1 (или соответствующих триггеров в остальных каналах), осуществляя синхронный ввод и формирование на выходах ,i.i,j; г i-utt. ла (1 fl)...() блока 4 признаков преобразования. Включение триггера 16-1 (или соответствующих ему в остальных каналах) снимает высокое напряжение с D-входа триггера 23, выключая его по фазе Ф2 и закрывая синхронный ввод до появления следующего (следующих) сигнала преобразования. Триггер 24 срабатывает от триггера 23 по синхроимпульсам фазы Ф4 (фиг.5г формируя идентификаторы признаков преобразования на выходе (2) блока 4, При срабатывании триггера 16-1 и соответствующих ему триггеров в остальных каналах на всех входах 1,1...К, элемента 22 имеется совпадение высоких уровней напряжения и на его выхо де, являкяцемся выходом (З) блока 4, появляется признак окончания ввода сигналов преобразования. Быключение триггеров 23 и 24 наряду с выключе-. нием по входу (2) в процессе преобра зования производится от синхроимпуль сов базы Ф7, поступающих на вход (). Блок 6 управления работает следую щим образом. Если на входе (З) блока 6 установ лено напряжение низкого уровня (НУ), триггер 25 задания режимов находится выключенном состоянии. С его прямо го выхода в выключенном состоянии удерживаются также триггеры 26 - 28, Триггеры 29 и 30 выключаются по Rвходам синхроимпульсами фазы Ф7 и фазы Фб, поступаняцими на входы (5 7) и (5(б) соответственно. При этом по цепям комбинационных элементов напряжение низкого уровня устанавливается на выходах () и (7), по которым осуществляется сброс счетчика 7 преобразования и управление начальным состоянием блока 4. На выходах (), (2(2), () блока 6 управления в это время задаются высокие уровни напряжения, определяю, щие режим хранения для АЗУ 9. На выт ходе элемента 42 совпадения устанавливается низкий уровень напряжения, которым формирователь 8 адреса по (1{lJ) выводится на начальный адрес, а с выхода () снимается управление пошаговым сдвигом селектора 10, который с выхода триггера 26 по цепи выхода ( ) блока 6 управления устанавливается на выборку первого канала. Выключенное состояние триггеров 29 и 30 снимает с вькода (5) готовность , а с выхода (6) - идентификатор информации. При смене низкого уровня напряжения на входе (З) на высокий включает ся триггер 25 синхроимпульсов первой фазы по входу (5 l ). Задается режим ПР, при котором на выходах () и (7) появляется высокое напряжение, разрешающее с выхода элемента ИЛИ 47 работу счетчика 7 преобразования и работу блока 4, по входу (5{8j) открывается элемент 37 совпадения для вьщачи на фазе Ф8 с выхода (3{2j) счетных импульсов на вход счетчика 7 преобразования, С выхода триггера 25 посредством элементов 40 совпадения и элементов ИЛИ 49 и 50 йа выходах (2{13)и ) устанавливается низкое напряжение для подготовки АЗУ 9 .к режиму записи. Если с блока 4 появляется идентификатор признаков преобразования (фиг, 6ж) то на входе (О блока 6 управления низкий уровень напряжения поменяется на высокий. Этим открывается элемент 39 совпадения для прохождения с входа (5{5}) на выход (2{2) импульсов фазы Ф5 дпя стробирования записи в ячейки ПИК и РП АЗУ 9. Тактирование записи в АЗУ 9 идентификатором признаков преобразования по рходу (1) продолжается до тех пор, пока не выполнится ввод сигналов преобразования по всем ка1 1алам. Появление признака окончания ввода сигналов преобразования от блока 4 (фиг. 7, 6-1) приводит к изме-, нению низкого уровня напряжения на входе (2) на высокий. Если на входе (4) также имеется высокий уровень, то по фазе Ф1 на входе (5{l ) включается триггер 26, На его прямом выходе (а также на выходе (4fl3) блока 6 управления) появляетсявысокий уровень пуска селектора 10 с целью . селекции признаков преобразования (сип) на поле ячеек памяти Ш1К (фиг,7,. B-I), Затем по фазе 2 на вход (5(2 ) включается триггер 27, на прямом выходе которого устанавливается высокий уровень напряжения, являюоцсйся идентификатором выборки по одному из каналов (фиг. 7ж), Этим же уровнем напряжения по° цепи элемента ИЛИ 49 на выходе (2(1) устанавливается низкий уровень, задающий при высоком уровне на выходе (2(2}) при отсутствии идентификатора признаков преобразования режим считывания из ячеек ПИК АЗУ 9, В это же время фазой ФЗ посредством элемента ИЛИ 49 разрешается сканирование с выхода () результатов считывания из ячеек ППК, Одновременно синхроимпульсами фазы Ф8 на входе () через злементы 38 и 48 с выхода (1123) ведется пошаговый сдвиг формирователя 8 адреса. При ИК появление на входе ( ) импульса ассоциативной выборки (высокий уровень напряжения, фиг, 7, ) включает триггер 29, прямой выход которого задает готовность на выходе (5) блока 6 управления. Вместе с этим через элемент ИЛИ 50 низкий уровень напряжения устанавливается на выходе (), управляющем считыванием информации из ячеек РП АЗУ 9. Вслед за этим на фазе Ф4 по входу (ЗГА) через элемент 36 включается триггер 3,0, прямой выход которого задает идентификатор информации на выходе (6) блока 6 управления. При этом на фазе Ф7 через элемент 33 и 45 йыключается триггер 27 - заканчивается идентификация канала. По окон чании Ж по С-входу выключается триг гер 28 (включается всегда при включении триггера 27) на фазе ФЗ со входа (5{3) посредством элемента 35 совпадения. Его выключение при высоком уровне напряжения на инверсном выходе обеспечивает выведение через элемент 41 на фазе Ф8 с выхода (1 ij) в начальное состояние формирователя адреса, а с выхода () перевод се лектора 10 на следующий канал выборки. Выключение триггеров 29 и 30 про изводится на каждой фазовой последовательности соответственно синхроимпульсами Ф7 с входа () и Фб с входа (5 б). На этом завершается цикл функционирования блока 6 управления при выборке информации из АЗУ для одного из кандлов. Для выборки по следующему каналу на фазе Ф2 внов включается триггер 27 при включенном триггере 26. Окончание селекции осуществляется выключением триггера 26 управления по входу (3) или с селектора 10 по входу () посредством .элемента ИЛИ 43. Селектор 10 работает следующим iобразом.. В режимах НУ и ПР по входу (2fl) в исходное состояние устанавливается счетчик 52, который управляет рабо„ -С1 1 „ той мультиплексора 51 по выходу 1 .. .G При этом первая линия связи (1 fl ) многоканального входа (1{| ...К) приз наков преобразования коммутируется на вход мультиплексора 51. Выход мультиплексора 51 подключен на вход элемента 53 совпадения, второй вход которого служит для сканирования на фазе ФЗ по входу () признаков преобразования. В рассматриваемых режимах на вход () импульсы не по-г ступают, формирование импульсов ассоциативной выборки на выходе элемента 53, являющемся выходом селектора 10, не ведется. После включения режима ВР снимается установка в исходное состояние счетчика 52, на вход {2{з) поступают импульсы сканирования . Если на начальном адресе управления мультиплексором 51 (счетчик 52 в исходном состоянии) при иаличии сканирующего импульса нет совпадения указанных на входах элемента 53 .сигналов, то на его выходе импульс ассоциативной выборки не вырабатывается. В связи в этим со стороны блока 6 управления производится переадресация АЗУ 9 и селектор 10 при считывании с этого адреса на . следующей фазовой последовательности вновь проводит сканирование (фиг. 7) признаков преобразования. Переадресация для одного канала продолжается до тех пор, пока на входе (lxl.«.Kj) селектора 10 не появится признак преобразования и соответственно на выходе элемента 53 совпадения не выработается импульс ассоциативной выборки. После этого с блока 6 управления по входу (2(2}) поступает импульс переключения счетчика 52 на следующее по порядку состояние. При этом коммутируется на выход мультиплексора 51 вторая линия съязи{12 ;} многоканального входа (1 l...к}) селектора 10. Начинается этап формирования импульса ассоциативной выборки для второго канала. В момент окончания последнего состояния счетчика 52 одновибратор 54 вырабатывает на своем выходе и соответственно на выходе (2f2j) селектора 10 импульс окончания селекции признаков преобразования по всем каналам. Состояние счетчика 52 одновременно с подачей на входы l.,.G управления мультиплексором 51 выводится на выход (l.,.G}) селектора 10 для передачи кода номерз канала на приемник информации. Формула изобретения Многоканальный преобразователь интервалов времени в код, содержащий многофазный генератор, счетчик преобразования, выходы которого соединены с Первой группой входов запоминающего устройства, формирователь адреса, входы которого подключены к ервой группе выходов блока управления, отличающийся тем, что, с целью Повышения надежности путем упрощения и повышения достовер17

ности преобразования устройства, в него введены блок асинхронно-синхроН ного ввода и селектор ассоциативной выборки результатов преобразования, а запоминаняцее устройство выполнено ассоциативным с плавающей адресацией каналов; причем первая группа входов блока асинхронно-синхронног о ввода является ииной многоканального ввода сигналов преобразования, а первая группа его выходов соединена с второй группой входов ассоциативного запоминающего устройства с плавающей адресацией каналов, первая группа выходов которого соединена с первой группой входов селектора ассоциативкой выборки результатов преобразования, а вторая группа выходов подключена к шине результата преобразования, вторая группа выходов блока управлею1я подключена к третьей группе входов ассоциативного запоминающего устройства с плавающей адресацией каналов, четвертая группа входов которого подключена к группе выходов формирователя адреса, второй и тре7387318

тий выходы блока асинхронно-синхронного ввода подключены соответственно к первому и второму входам блока управления, третий и четвертый входы 5 которого подключены к шинам соответственно управления режимами и готовности внешнего приемника, первая группа выходов многофазного генератора подключена к пятой группе входов бло)0 ка управления, четвертая группа выхогдов которого соединена с второй групг пой входов селектора асинхронной выборки результатов преобразования, первая группа выходов которого соеди 5 нена с шиной вывода кода номера канала, а вторая группа выходов подключена к шестой группе входов блока управления, пятый и шестой выходы кото-рого соединены соответственно с ши20 ной готовности выводы и шиной идентификации информации вывода, седьмой выход .блока управления подключен к второму входу блока асинхронно-синхронного ввода, третья группа входов

5 которого соединена с второй группой выходов многофазного генератора.

ШЯ

(5Ш

Фие.З

v

ФГ-Л Ь Ф2 -П

д фз .

г

2 ф -П.

; гт

g ФУ П

f Ф -П1 /Ч 077 -П:

// . -jn. Ф8

jn

фуг.5

qJue.

| Многоканальный измеритель временных интервалов | 1981 |

|

SU970306A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Многоканальное устройство для измерения временных интервалов в непериодических последовательностях импульсов | 1982 |

|

SU1034013A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-11-30—Публикация

1985-07-02—Подача