(/ С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения последовательности чисел с плавающей запятой | 1984 |

|

SU1182512A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1290300A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1988 |

|

SU1589270A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1273921A1 |

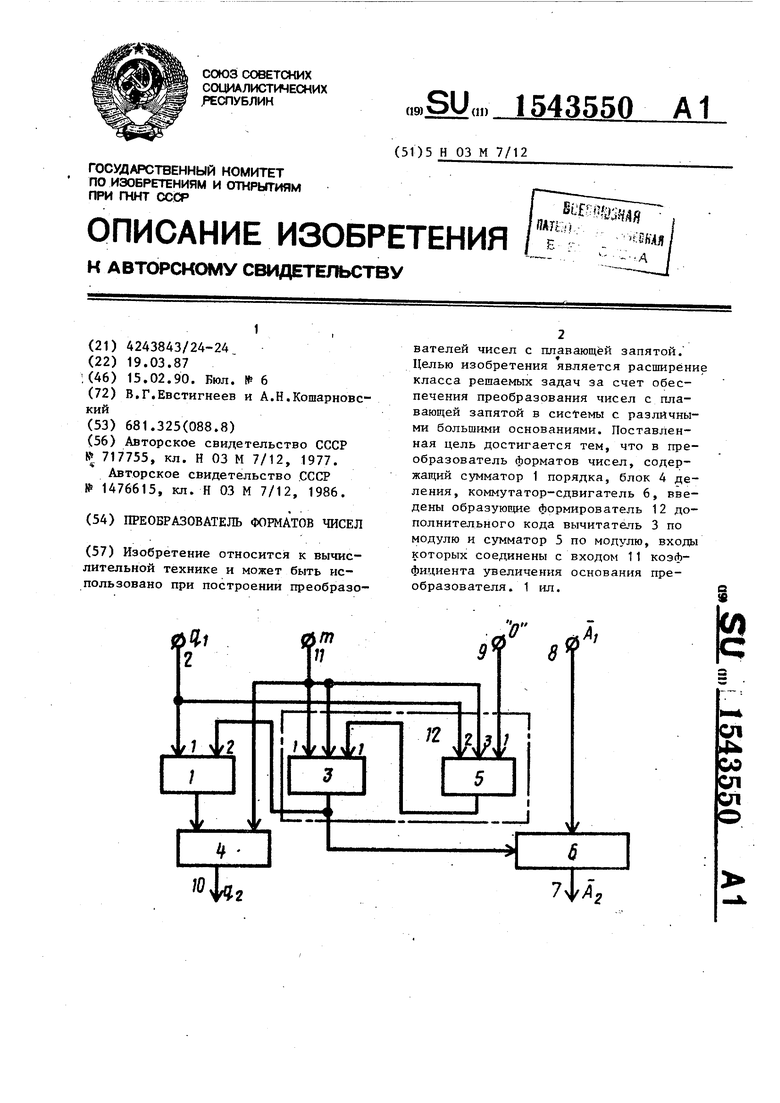

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей чисел с плавающей запятой. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования чисел с плавающей запятой в системы с различными большими основаниями. Поставленная цель достигается тем, что в преобразователь форматов чисел, содержащий сумматор порядка 1, блок деления 4, коммутатор-сдвигатель 6, формирователь дополнительного кода 12, формирователь дополнительного кода 12, введены вычитатель по модулю три и сумматор по модулю пять, входы которых соединены с входом 11 коэффициента увеличения основания преобразователя. 1 ил.

ел

4Ь СО СЛ СП

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей чисел с плавающей запятой.

Цель изобретения - расширение класа решаемых задач за счет обеспечения преобразования чисел с плавающей Запятой в системы с различными большими основаниями.

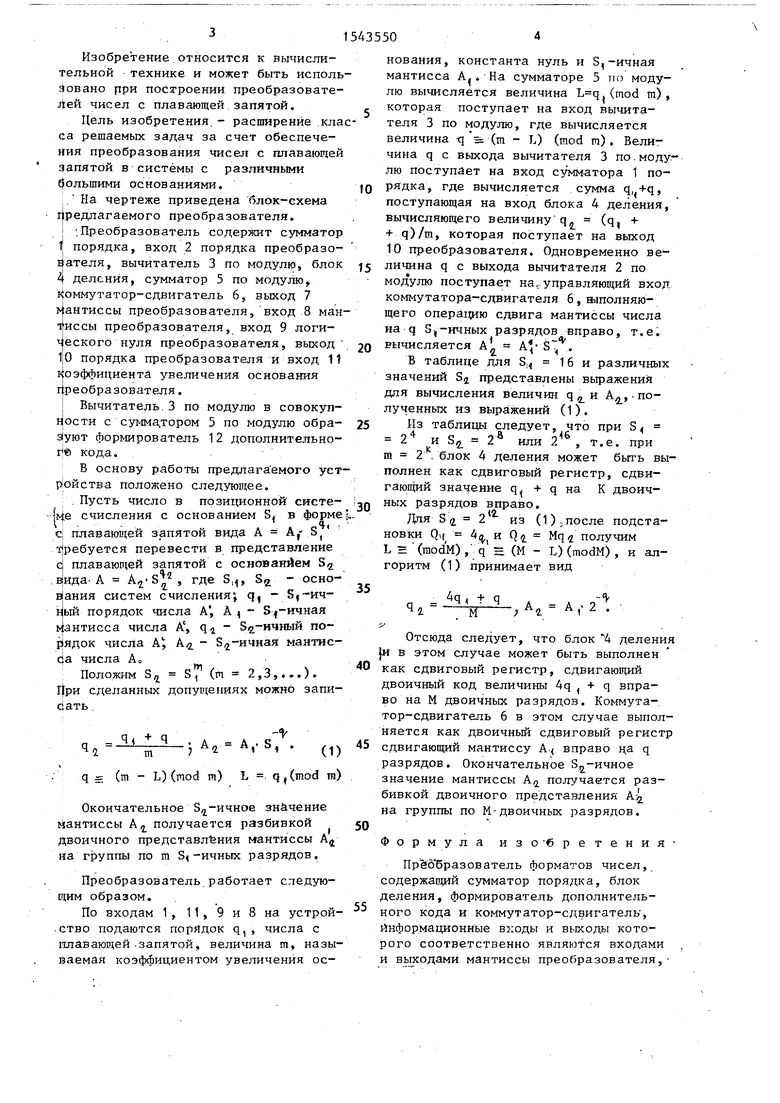

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит сумматор т порядка, вход 2 порядка преобразователя, вычитатель 3 по модулю, блок 4 деления, сумматор 5 по модулю, г оммутатор-сдвигатель 6, выход 7 }4антиссы преобразователя, вход 8 ман т|иссы преобразователя, вход 9 логи- ч|еского нуля преобразователя, выход 1,0 порядка преобразователя и вход 11 Коэффициента увеличения основания преобразователя.

Вычитатель 3 по модулю в совокуп- н|ости с сумма/тором 5 по модулю обрадуют формирователь 12 дополнительного кода.

В основу работы предлагаемого устройства положено следующее.

Пусть число в позиционной систе- |ме счисления с основанием S в форме с плавающей запятой вида А A,- S( ребуется перевести в представление о плавающей запятой с основанием S А , где S.,, 5г - основания систем счисления; q, - 5,-ич- ный порядок числа А , А , - З -ичная мантисса числа Ас, q - З -ичный по- числа А , А - 82-ичная мантис- 0а числа А„

Положим S S, (m 2,3,...). Г|ри сделанных допущениях можно записать

q + q

m

; 1

A,- S,

(1)

q г (m - L)(mod m) L q,(mod m)

Окончательное S -ичное значение мантиссы Аг получается разбивкой двоичного представления мантиссы А4 на группы по m S -ичных разрядов.

Преобразователь работает следующим образом.

По входам 1, 11, 9 и 8 на устрой етво подаются порядок q,, числа с плавающей запятой, величина т, назы йаемая коэффициентом увеличения осй-

нования, константа нуль и S,-ичная мантисса А,. На сумматоре 5 по модулю вычисляется величина .(mod m), которая поступает на вход вычита- теля 3 по модулю, где вычисляется величина -q (m - L) (mod т) . Величина q с выхода вычитателя 3 по модулю поступает на вход сумматора 1 поo Ряяка, где вычисляется сумма , поступающая на вход блока 4 деления, вычисляющего величину q. (qt + + q)/m, которая поступает на выход 10 преобразователя. Одновременно ве5 личина q с выхода вычитателя 2 по модулю поступает на управляющий вход коммутатора-сдвигателя 6, выполняющего операцию сдвига мантиссы числа на q S -ичных разрядов вправо, т.е.

0 вычисляется А A S .

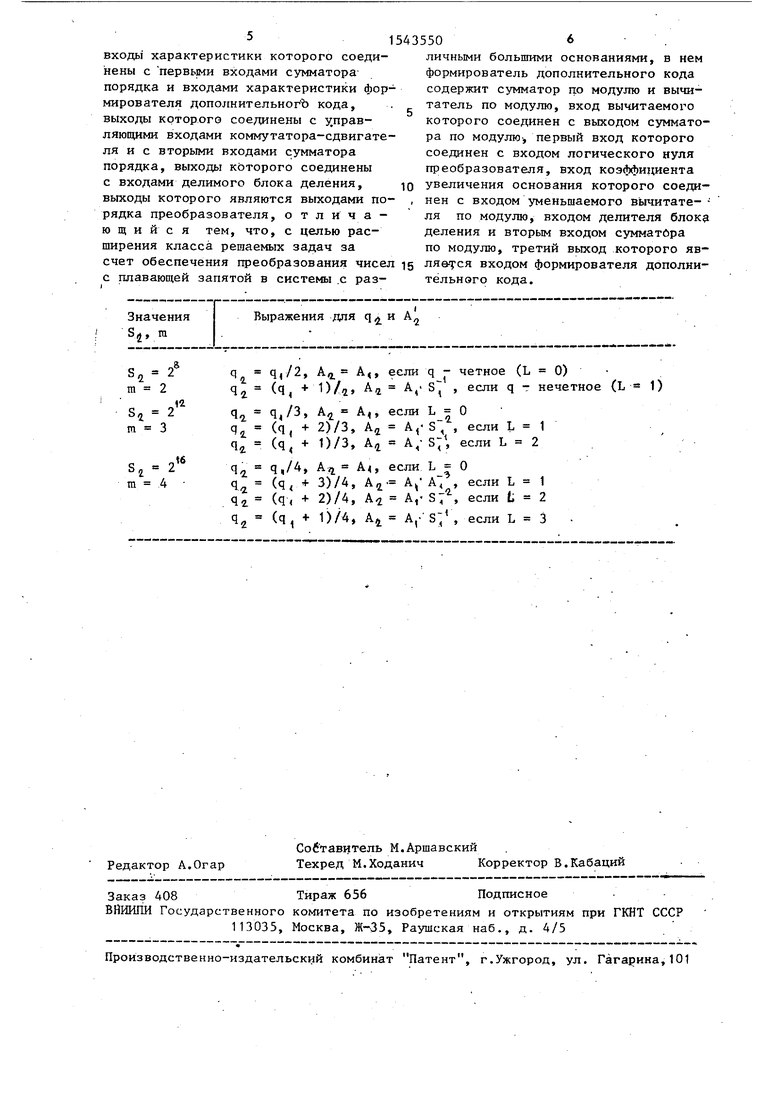

В таблице для S,,, 16 и различных значений 5а представлены выражения для вычисления величин q и А, полученных из выражений (1).

5 Из таблицы следует, что при S - 24 и S 2й или 246 , т.е. при m 2 блок 4 деления может быть выполнен как сдвиговый регистр, сдвигающий значение qf + q на К двоичQ ных разрядов вправо.

Для SЈ 2 из (1),после подстановки Q(( 4jj.( и QЈ Mq получим L (modM), q (M - L)(modM), и алгоритм (1) принимает вид

,

35

„ 4q t q A д о Ч qlИ) А - АГ 2

Отсюда следует, что блок 4 деления }и в этом случае может быть выполнен

как сдвиговый регистр, сдвигающий двоичный код величины 4q { + q вправо на М двоичных разрядов. Коммута- тор-сдвигатель 6 в этом случае выполняется как двоичный сдвиговый регистр

сдвигающий мантиссу А вправо ца q разрядов. Окончательное S -ичное значение мантиссы А/j получается разбивкой двоичного представления А на группы по М-двоичных разрядов.

Формула изобретенияПреобразователь форматов чисел, содержащий сумматор порядка, блок деления, формирователь дополнительного кода и коммутатор-сдвигатель, информационные входы и выходы которого соответственно являются входами и выходами мантиссы преобразователя,

входа характеристики которого соединены с первыми входами сумматора порядка и входами характеристики формирователя дополнительной кода, выходы которого соединены с управляющими входами коммутатора-сдвигате- ля и с вторыми входами сумматора порядка, выходы которого соединены с входами делимого блока деления, выходы которого являются выходами по- рядка преобразователя, отличающийся тем, что, с целью расширения класса решаемых задач за

счет обеспечения преобразования чисел 15 ляе-тся входом формирователя дополни- с плавающей запятой в системы с раз- тельного кода.

б

- ЧЧ I 1 -1t - ч

q,/3, A4 А,, если L О (q + 2)/3, Аа A,- S, , если L 1 (q, + О/З, А4 А; 5 если L 2

q q,/4, A4 А, если L О Ч„ (Ч« + 3)/4, Аг- Ан- , если L 1 q (q, + 2)/4, А A,- S;4, если L 2 q2 (q , DM, А4 A,- , если L 3

личными большими основаниями, в нем формирователь дополнительного кода содержит сумматор по модулю и вычи- татель по модулю, вход вычитаемого которого соединен с выходом сумматора по модулю-, первый вход которого соединен с входом логического нуля преобразователя, вход коэффициента увеличения основания которого соединен с входом уменьшаемого вычитате- ля по модулю, входом делителя блока деления и вторым входом сумматора по модулю, третий выход которого яв

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-15—Публикация

1987-03-19—Подача