(54) АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1980 |

|

SU903983A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU842962A1 |

| Ассоциативная запоминающая матрица | 1981 |

|

SU1005188A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU900315A1 |

| Ассоциативная запоминающая матрица | 1979 |

|

SU886051A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU907582A1 |

I

Изобретение относится к запоминающим устройствам.

Известна ассоциативная запоминающая матрица, содержащая элементы памяти с подключенными к ним шинами опроса, записи, считывания LlJ .

Недостатком этой матрицы является сложность конструкции.

Наиболее близкой по технической сущности к предлагаемой является ассоциативная запоминающая матрица, содержащая строки и столбцы элементов ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две группы блоков выдачи, гри группы входных элементов НЕ, а также входные шины поиска (записи), шины выбора строки, выходные шины считывания и шины результата по, иска, позволяющие выполнить операции записи информации с выходных шин в любые элементы ассоциативной памяти и считывание из них информации, сравнения содержимого этих элементов с информацией на входных шинах и маскирование затшси и сравнение определенных столбцов памяти t2j.

Недостатком этой матрицы является отсутсивие контроля ее исправности, что снижает надежность матрицы.

Цель изобретения - повышение надежности матрицы.

Поставленная цель достигается тем,

10 что в ассоциативную запоминающую матрицу, содержащую элементы памяти, прячем входы элементов памяти, принадлежащих одноименному столбцу матрицы, подключены к соответствующим вхоцным

15 информационным и маскирующим шинам,а выходы - к выходным информационным шинам входы элементов памяти, принадлежащих одноименной строке матрицы, соединены с соответствующими шинами выборки строки,

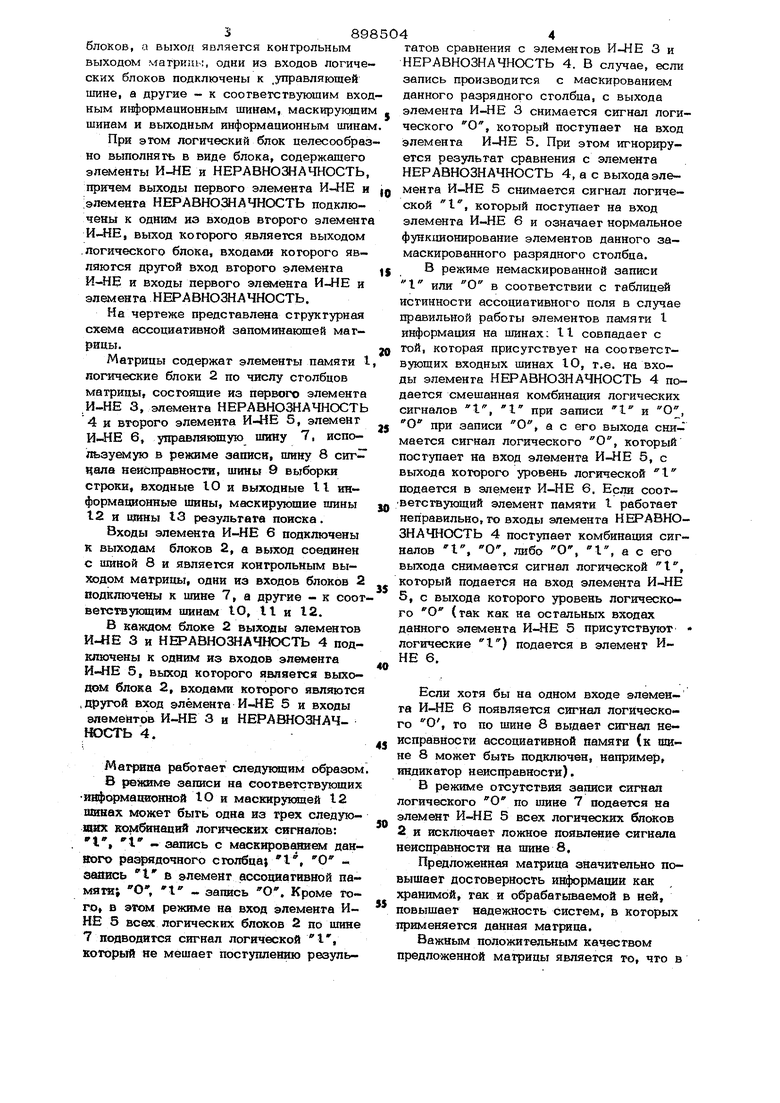

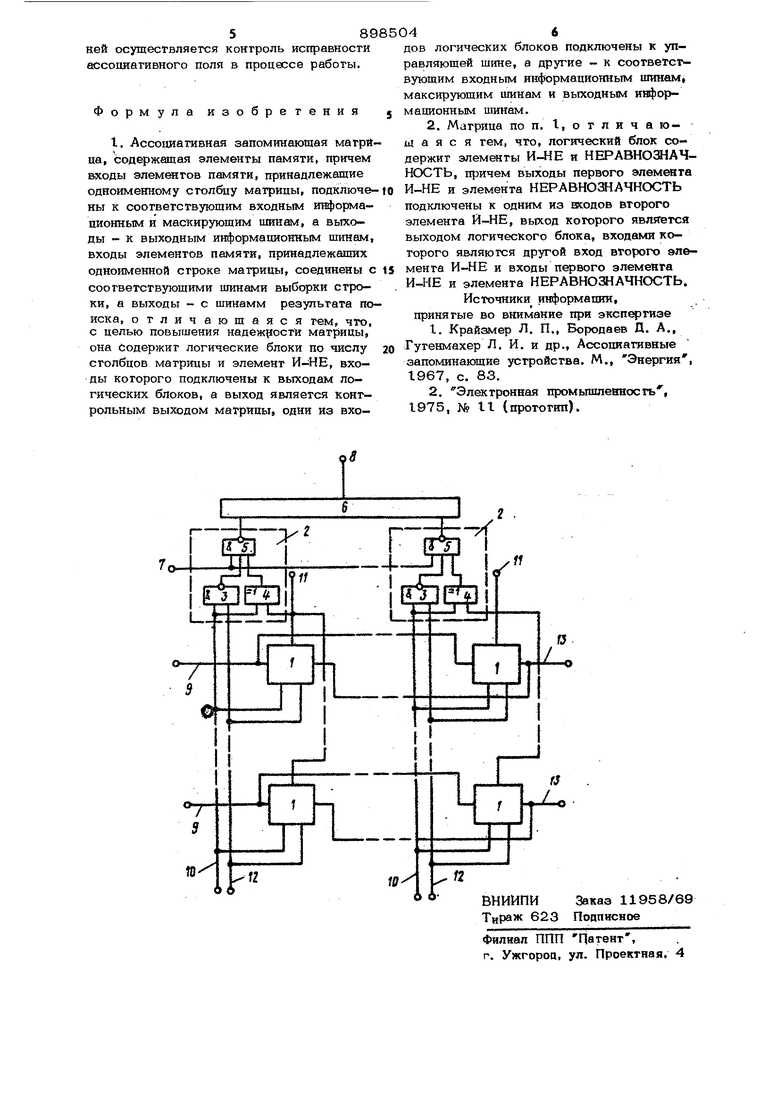

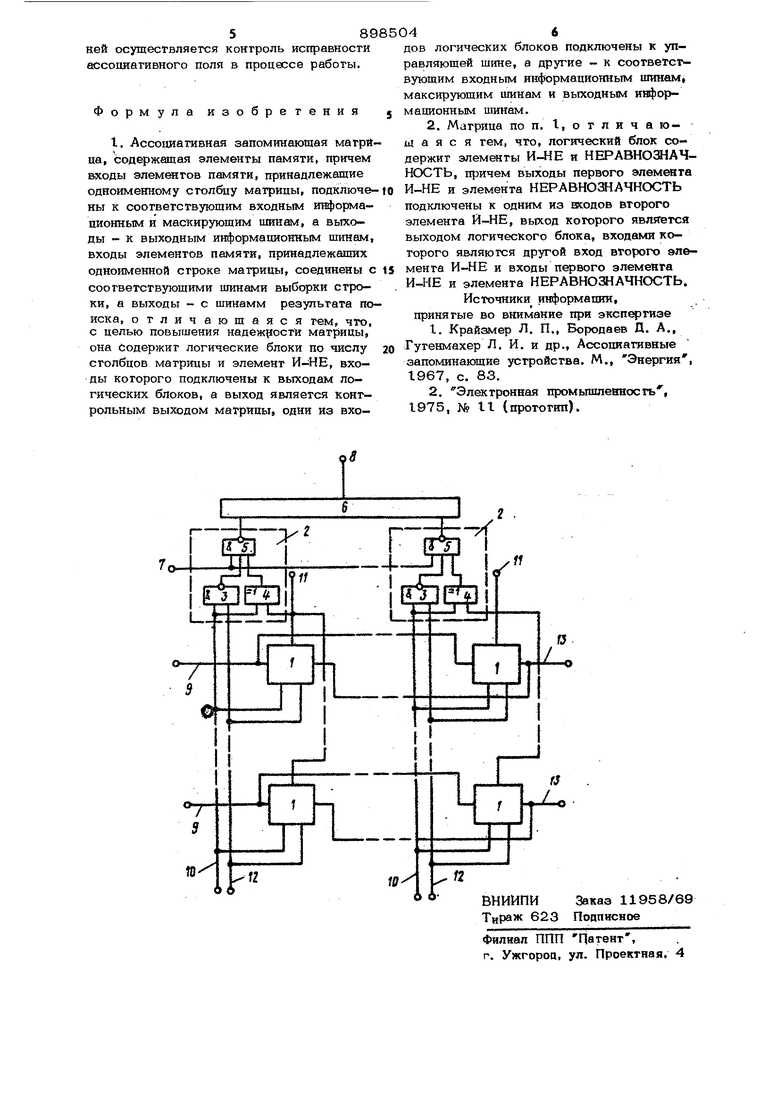

20 а выходы - с шинами результата поиска, введены логические блоки по числу стрлбцов матрицы и элемент И-НЕ, входы которого подключены к выходам логических блоков, а выход являегся контрольным выходом магрины, одни из входов логиче ских блоков подключены к .управляющей шине, а другие - к соогвегствуюшим вхо ным информационным шинам, маскируклли шинам и выходным информационным шина При этом логический блок целесообраз но выполнять в виде блока, содержащего элементы И-НЕ и НЕРАВНОЗНАЧНОСТЬ, причем выходы первого элемента И-НЕ и элеменга НЕРАВНОЙ А ЧНОСТЬ подключены к одним из входов второго элемент И-НЕ, выход которого является выходом .логического блока, входами которого являются другой вход второго элемента И-НЕ и входы первого элемента И-НЕ и элемента НЕРАВНОЗНАЧНОСТЬ. На чертеже представлена структурная схема ассоциативной запоминающей матрицы. Матрицы содержат элементы памяти I ногические блоки 2 по числу столбцов матрицы, состоящие из первого элемента И-НЕ 3, элемента НЕРАВНОЗНАЧНОСТЬ 4 и второго элемента И-НЕ 5, элемент И-НЕ 6, управляющую щину 7, используемую в режиме записи, шину 8 сиг чала неисправности, шины 9 выборки строки, входные Ю и выходные 11 информационные шины, маскирующие шины 12 я щины 13 реэультага поиска. Входы элемента И-НЕ 6 подключены к выходам блоков 2, а выход соединен с шиной 8 и является контрольным вызйэдом матрицы, одни из входов блоков 2 подключены к шине 7, а другие - к соот ветствующим шинам Ю, И и 12. В каждом блоке 2 выходы элементов HOiE 3 и НЕРАВНОЗНАЧ1ЮСТЬ 4 подключены к одним из входов элемента Й-НЕ 5, выход которого являегся выходом блока 2, входами которого являются .другой вход элемента И-НЕ 5 и входы элементов И-НЕ 3 и НЕРАВНОЖАЧШЭСТЬ 4. Матрина работает следукяцим образом 8 записи на соответствующих иаформацгонвсй Ю и маскирукяней 12 шинах может быть одна из трех следующих комбинаций логических сигналов: I, I „ запись с маскировевшем данного разрядочного столбца} 1, О зааись 1 в элемеат ассодаативной памяти; О, t - запись О. Кроме того, в эюм режиме на вход элемента ИНЕ 5 всех логических блоков 2 по шине 7 додводится сигнал логической 1, который не мешает поступлению резуль89татов сравнения с элементов ИЛЕ 3 и НЕРАВНОЗНАЧНОСТЬ 4. В случае, если запись производится с маскированием данного разрядного столбца, с выхода элемента И-НЕ 3 снимается сигнал логического О, который поступает на вход элемента И-НЕ 5. При этом игнорируется результат сравнения с элемента НЕРАВНОЗНАЧНОСТЬ 4, а с выхода элемента И-НЕ 5 снимается сигнал логической 1, который поступает на вход элемента И-НЕ 6 и означает нормальное функционирование элементов данного замаскированного разрядного столбца. В режиме немаскированной записи 1 или О в соответствии с таблицей истинности ассоциативного поля в случае правильной работы элементов памяти 1 информация на шинах; II совпадает с той, которая присутствует на соответствующих входных шинах Ю, т.е. на входы элемента НЕРАВНОЗНАЧНОСТЬ 4 подается смешанная комбинация логических сигналов 1, 1 при записи I и О, О при записи О, а с его выхода снимается сигнал логического О, который поступает на вход элемента И-НЕ 5, с выхода которого уровень логической 1 подается в элемент И-НЕ 6. Если соответствующий элемент памяти 1 работает неправильно, то входы элемента НЕРАВНОЗНАЧНОСТЬ 4 поступает комбинация сигналов 1, О, либо О, 1, а с его выхода снимается сигнал логической 1, который подается на вход элемента И-НЕ 5, с выхода которого уровень логического О (так как на остальных входах данного элемента И-НЕ 5 присутствуют логические 1) подается в элемент ЕСЛИ хотя бы на одном входе элемента И-НЕ 6 появляется сигнал логического О , то по шине 8 выдает сигнал неисправности ассоциативной памяти (к шине 8 может быть подключен, например, индикатор неисправности). В реншме отсутствия записи сигнал логического О по шике 7 подается на элемент И-НЕ 5 всех логических блсжов 2 и исключает ложное появление сигнала неисправности на шине 8, Предложенная матрица значительно повышаег достоверность информации как хранимой, гак и обрабатываемой в ней, повышает надежность систем, в которых применяется данная матщца. Важным положительным качеством предложенной матрицы является то, что в

ней осущесгвляетчзя коигроль исправности ассоциагивного поля в процессе работы.

Формула изобретения

I. Ассоциативная запоминающая матрица, содержащая элементы памяти, причем входы элементов памяти, принадлежащие одноименному столбцу матрицы, подключены к соответствующим входным ш ормационным и маскирующим шинам, а выходы - к выходным информационным шинам, входы элементов памяти, принадлежащих одноименной строке матрицы, соединены с соответствующими шинами выборки строки, а выходы - с шинамм результата поиска, отличающаяся тем, что, с целью повышения надежности матрицы, она Содержит логические блоки по числу столбцов матрицы и элемент И-НЕ, входы которого подключены к выходам логических блоков, а выход является контрольным выходом матрицы, одни из вхо--Ь-;к г

дов логических блоков подключены к управляющей шине, а другие к соответствующим входным информационным ипшаМ( максирующим шинам и выходным информационным шинам.

Источники информации, принятые во внимание при

г .

г-ЧЬ-тГ

Авторы

Даты

1982-01-15—Публикация

1980-04-28—Подача