Изобретение относится к ционной вычислительной технике и может быть использовано в интегральных цифровых и аналоговых микросхемах, например на МДП-структурах.

Цель изобретения - повьшение надежности и нагрузочной способности устройства путем введения в устройство второго триггера, дополнительных логических элементов И-ИЛИ НЕ и магистральных элементов, а также за счет обеспечения большей устойчивости функционирования к разбросу величин емкостных нагрузок на вьшо- дах формирователя и фронтов входных сигналов.

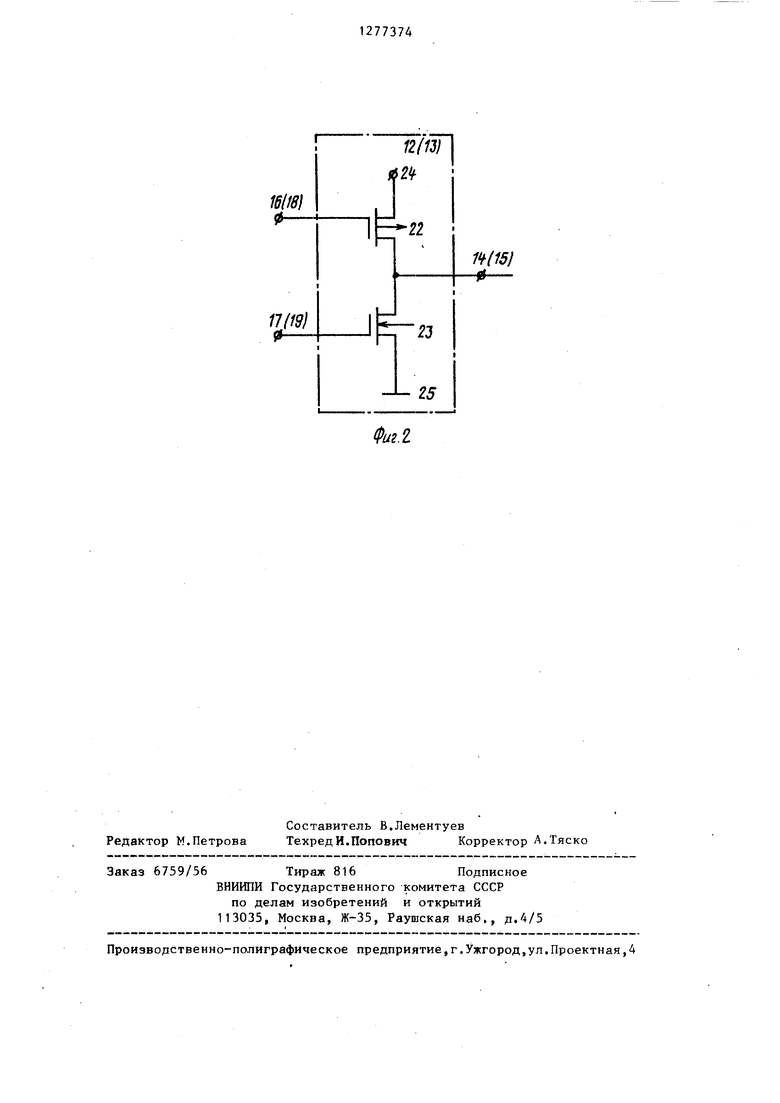

На фиг.1 приведена логическая схема устройства; на фиг.2 - принципиальная схема магистрального элемента

Устройство содержит первый триггер 1, первый 2 и второй 3 элементы И-НЕ, первый 4 и второй 5 элементы НЕ, второй триггер 6, пять элементов |ИЛИ-НЕ 7 - 11, магистральные элемен- :ты 12 и 13.

Первый вывод 14 устройства подклю чен к объединенным между собой входу первого элемента НЕ 4, первым входам первого элемента И-НЕ 2, второго 8 и пятого 11 элементов ИЛИ-НЕ,-а вто- ,рой вывод 15 соединен с входом второго элемента НЕ 5 и первыми входами второго элемента И-НЕ 3, третье- го 9 и четвертого 10 элементов ИЛИ- НЕ. Выходы элементов НЕ 4 и 5 подключены к входам первого элемента ИЛИ-НЕ 7, выход которого подключен к входам сброса триггеров 1 и 6, а выходы третьего 9 и пятого 11 элементов ИЛИ-НЕ соединены соответственно с установочными входами первого 1 и второго 6 триггеров, инверсны выходы которых подключены к вторым выводам соответственно четвертого 10 и второго 8 элементов ИЛИ-НЕ„ Прямые выходы первого 1 и второго 6 триггеров подключены к вторым входам соответственно второго элемента И-НЕ 3, пятого элемента ИЛИ-НЕ 11, первого элемента И-НЕ 2 и третьего элемента ИЛИ-НЕ 9. Выходы второго элемента И-НЕ 3 и четвертого элемента ИЛИ- НЕ 10 соединены соответственно с первым 16 и вторым 17 входами первого магистрального элемента 12, а выходы первого элемента И-НЕ 2 и второго элемента ИЛИ-НЕ 8 подключены соответственно к первому 18 и второ

5

5

му 19 входам второго магистрального элемента 13. Выходы 20 и 21 магистральных элементов 12 и 13 соединены соответственно с первым 14 и вторым 15 выводами устройства.

Первый и второй магистральные элементы вьтолнены в виде последовательно соединенных дополнительных ВДП-транзисторов 22 и 23, стоки которых являются выходом соответствующего магистрального элемента, входами которого являются затворы тех же МДП-транзисторов, истоки которых Под- ключены соответственно к шине 24 пи- 5 тания и общей шине 25 устройства.

Формирователь работает следующим образом.

В исходном состоянии на выводах 14 и 15 устройства поддерживается вы- 0 сокий уровень логической 1, например через внешний резистор от шины 24 питания. При этом через элементы НЕ 4 и 5 и элемент ИЛИ-НЕ 7 на входы сброса триггеров 1 и 6 поступает сигнал, сбрасывающий триггеры в исходное состояние, на прямых выходах - уровни О и на инверсных - уровни 1.

При поступлении на один из выводов двунаправленного формирователя (для определенности на вывод 14) уровня О на выходе элемента ИЛИ-НЕ 11 формируется уровень 1, и триггер 6 устанавливается следующим образом: на прямом выходе триггера формируется

0

5

уровень логической 1, а на инверс 0.

0

ном - уровень логического U. На двух входах элемента ИЛИ-НЕ 8 формируются уровни логического О, а на выходе - уровень логической l соответственно. Транзистор (п-каналь- ный) 23 открывается, и на выходе 21 и выводе 15 формируется усиленный сигнал нулевого уровня, т.е. происходит передача сигнала с одного вы- /вода 14 устройства на другой вывод 15.

Соответствующий уровень логической 1 с прямого выхода триггера 6 поступает на вход элемента ИЛИ-НЕ 9, блокируя тем самым передачу сигнала 0 с вывода 15 двунаправленного формирователя на вьшод 14.

При изменении сигнала с уровня О на уровень 1 на выводе 14 на затво- pie транзистора 23 магистрального элемента 12 формируется О, указанный транзистор закрывается. Соответственно на выходе элемента И-НЕ 2 формируется уровень О и открывается

S

транзистор 22, тем самым на короткий промежуток времени (на время установления уровня логической 1 плюс время сброса триггера 6) открывается указанный транзистор. При этом, чем больше величина емкостной нагрузки, тем больше время включения транзистора 22.

Аналогично переключаются (при поступлении сигнала с вывода 15) пер- вый триггер 1, элемент ИЛИ-НЕ 9,элементы ИЛИ-НЕ 10 и И-НЕ 3.

Таким образом, устройство позволяет значительно быстрее реагировать на изменение сигнала на одном из вы- водов формирователя и при этом блокировать возможный сигнал на другом выводе, причем при различных по величине нагрузках на выводах устройства и при большом разбросе фронтов вход- ных сигналов, и тем самым повысить надежность передачи сигналов. ч

Формула изобретения

1. Двунаправленный формирователь, содержащий первый триггер, первый и второй элементы И-НЕ, первый и второй элементы НЕ, входы которых соответственно соединены с первьви и вто- рым выводами двунаправленного формирователя которые объединены с первыми входами соответственно первого и второго элементов И-НЕ, отличающийся тем, что, с целью повышения надежности и нагрузочной способности, в него введены второй триггер, пять элементов ИЛИ-НЕ и два магистральных элемента, выход первого элемента ИЛИ-НЕ, входы которого подключены к выходам элемен

j 10

Т520

25

зо

5

0

тов НЕ, соединен с входами сброса триггеров, вход первого элемента НЕ соединен с первыми входами второго и пятого элементов ИЛИ-НЕ, а вход второго элемента НЕ соединен с первыми входами третьего и четвертого элементов ИПИ-НЕ, выходы третьего и пятого элементов ИЛИ-НЕ соединены соответственно с установочными входами первого и второго триггеров, инверсные выходы которых подключены к вторым входам соответственно четвертого и второго элементов ИЛИ- НЕ, прямые выходы тех же триггеров соединены с попарно объединенными вторыми выводами соответственно пятого элемента ИЛИ-НЕ, второго элемента И-НЕ и третьего элемента ИЛИ- НЕ, первого элемента И-НЕ, выходы первого и второго элементов И-НЕ подключены к первым входам соответственно второго и первого магистральных элементов,- вторые входы которых подключены к выходам соответственно второго и четвертого элементов ИЛИ- НЕ, выходы первого и второго магистральных элементов подключены соответственно к первым и вторым выводам двунаправленного формирователя. 2. Формирователь по п.1, о т л и- чающийся тем, что первый и второй магистральные элементы выполнены в виде последовательно соединенных МДП-транзисторов дополнительного типа проводимости, стоки тран- зисторов объединены и являются вьпсо- дом магистральных элементов, входа- ми которого являются затворы тех же МДП-транзисторов, истоки которых подключены соответственно к шине питания и общей шине.

Редактор М.Петрова

Составитель В.Лементуев

Техред И.Попович Корректор А.Тяско

Заказ 6759/56 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения к магистрали | 1984 |

|

SU1226480A1 |

| Блок согласования с магистралью | 1977 |

|

SU732841A1 |

| Динамический Д-триггер с третьим состоянием по выходу | 1990 |

|

SU1774472A1 |

| Многоканальное приоритетное устройство | 1982 |

|

SU1038945A1 |

| Устройство для приема и передачи информации | 1983 |

|

SU1092547A1 |

| Формирователь выходного сигнала | 1985 |

|

SU1277384A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Формирователь адреса | 1984 |

|

SU1265853A1 |

| Выходной узел устройства контроля цифровых блоков | 1984 |

|

SU1213444A1 |

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

Изобретение относится к области ,коммутационной вычислительной техники. Может быть использовано в интегральных цифровых и аналоговых микросхемах, например на МДП-структурах. Цель изобретения - повышение надежности и нагрузочной способности устройства - достигается введением второго триггера, дополнительных элементов ИЛИ-НЕ и магистральных элементов, а также за счет обеспечения большей устойчивости функционирования к разбросу величин емкостных нагрузок на выводах формирователя фронтов входных сигналов. Устройство содержит , первый триггер 1, элементы И-НЕ 2 и 3, элементы НЕ 4 и 5, второй триггер 6, элементы ИЛИ-НЕ 7-11, магистральные элементы 12 и 13. Предложенный формирователь срабатывает при большем разбросе фронтов входных сигналов по. сравнению с аналогом и позволяет снизить требования к устройствам, передающим информацию. 1 з.п. ф-лы, 2 ил. с «в (Л 1C ч оо

| Переключающее устройство | 1980 |

|

SU898613A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3769525,кл.307-254, 27.09.72. | |||

Авторы

Даты

1986-12-15—Публикация

1985-07-05—Подача