Изобретение относится к полупроводниковой технике и может быть использовано .в интегральных схемах запоминающих устройств на МДП-транзисторах, имеющих резервные блоки запоминающих ячеек, для программирования адреса дефектного блока.

Цель изобретения - повышение быстродействия устройства, а также повышение надежности программирования.

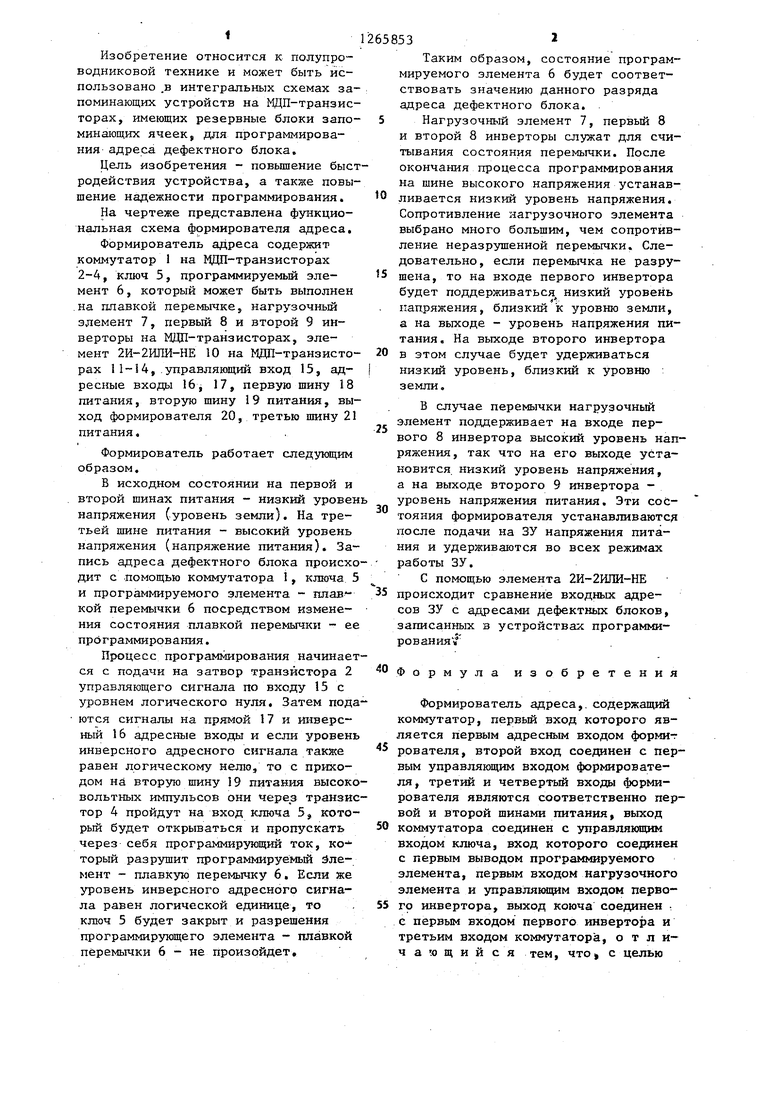

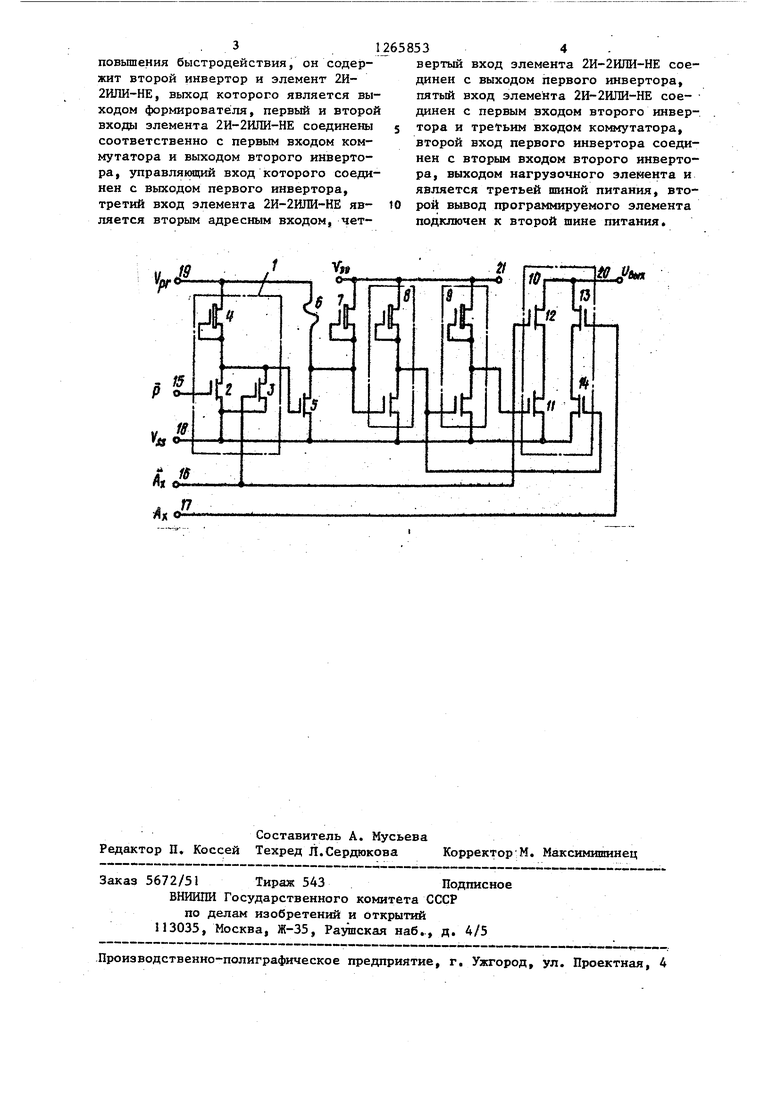

На чертеже представлена функциональная схема формирователя адреса.

Формирователь адреса содерямт коммутатор 1 на МДП-транзисторах 2-4, ключ 5, программируемый элемент 6, который может быть выполнен .на плавкой перемычкеj нагрузочный элемент 7, первый 8 и второй 9 инверторы на МДП-транзисторах, элемент 2И-2ШШ-НЕ 10 на ЩЩ-транзисторах 11-14,.управляющий вход 15, адресные входы 16, 17, первую шину 18 питания, вторую шину 19 питания, выход формирователя 20, третью шину 21 питания.

Формирователь работает следующим образом,

В исходном состоянии на первой и второй шинах питания - низкий уровен напряжения (уровень земли). На третьей шине питания - высокий уровень напряжения (напряжение питания). Запись адреса дефектного блока происходит с помощью коммутатора 1, ключа 5 и программируемого элемента - плавкой перемычки 6 посредством изменения состояния плавкой перемычки - ее программирования.

Процесс программирования начинается с подачи на затвор транзистора 2 управляющего сигнала по входу 15 с уровнем логического нуля. Затем пода ются сигналы на прямой 17 и инверсный 16 адресные входы и если уровень инверсного адресного сигнала также равен логическому нелго, то с приходом на вторую шину 19 питания высоковольтных импульсов они через транзистор 4 пройдут на вход ключа 5, который будет открываться и пропускать через себя программирующий ток, который разрушит программируемый Элемент - плавкую перемычку 6. Если же уровень инверсного адресного сигнала равен логической единице, то ключ 5 будет закрыт и разрешения программирующего элемента - плавкой перемычки 6 - не произойдет.

Таким образом, состояние программируемого элемента 6 будет соответствовать значению данного разряда адреса дефектного блока. .

Нагрузочный элемент 7, первый 8 и второй 8 инверторы служат для считывания состояния перемычки. После окончания процесса программирования на шине высокого напряжения устанавливается низкий уровень напряжения. Сопротивление нагрузочного элемента выбрано много большим, чем сопротивление неразрушенной перемычки. Следовательно, если перемычка не разрушена, то на входе первого инвертора будет поддерживаться низкий уровень напряжения, близкий к уровню земли, а на выходе - уровень напряжения питания. На выходе второго инвертора в этом случае будет удерживаться низкий уровень, близкий к уровню : земли,

В случае перемычки нагрузочный элемент поддерживает на входе первого 8 инвертора высокий уровень напряжения, так что на его выходе установится, низкий уровень напряжения, а на выходе второго 9 инвертора - уровень напряжения питания. Эти состояния формирователя устанавливаются после подачи на ЗУ напряжения питания и удерживаются во всех режимах работы ЗУ.

С помощью элемента 2И-2ИЛИ-НЕ происходит сравнение входных адресов ЗУ с адресами дефектньк блоков, записанных в устройствах программирования

Формула изобретения

Формирователь адреса,, содержащий коммутатор, первый вход которого является первым адресным входом форми-г рователя, второй вход соеданен с первым управляющим входом формирователя, третий и четвертый входы формирователя являются соответственно первой и второй шинами питания, выход коммутатора соединен с управлякяцим входом ключа, вход которого соединен с первым выводом программируемого элемента, первым входом нагрузочного элемента и управляющим входом первого инвертора, выход коюча соединен , с первым входом первого инвертора и третьим входом коммутатора, отличающийся тем, что) с целью

.31

повьшения быстродействия, он содержит второй инвертор и элемент 2И2ИЛИ-НЕ, выход которого является выходом формирователя, первый и второй входы элемента 2И-2ИЛИ-НЕ соединены соответственно с первым входом коммутатора и выходом второго инвертора, заправляющий вход которого соединен с выходом первого инвертора, третий вход элемента 2И-2ИЛИ-НЕ является вторым адреснь м входом, чет658534 .

вертый вход элемента 2И-2Ш1И-НЕ соединен с выходом первого инвертора, пятый вход элемента 2И-2ИЛИ-НЕ соединен с первым входом второго инвер5 тора и третьим входом коммутатора, второй вход первого инвертора соединен с вторым входом второго инвертора, выходом нагрузочного элемента и является третьей пшиой питания, вто10 рой вывод программируемого элемента подключен к второй шине питания

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ЭЛЕМЕНТОВ КОНТУРНОГО ИЗОБРАЖЕНИЯ | 1991 |

|

RU2015560C1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Дешифратор для запоминающего устройства с резервированием | 1986 |

|

SU1429166A1 |

| Устройство формирования импульсных сигналов и уровней постоянного напряжения на МДП транзисторах | 1986 |

|

SU1370752A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

Изобретение относится к области полупроводниковой техники и может быть использовано в интегральных схемах запоминакицих устройств на ЦДЛ-транспортах, имеющих резервные блоки запоминающих ячеек, для npof-f раммирования адреса дефектного блока. Целью изобретения является повьшение быстродействия. Формирователь адреса содержит коммутатор на МГЩ-транзист1 торах, ключ, пpoгpaммиpye я.Iй элемент. который может быть выполнен на плавкой перемычке, нагрузочный элемент, первый и второй инверторы, элемент 2И-2ИЛИ-НЕ, управляющий и адресные входы, шины питания. В предложенном формирователе цель достигается за счет введения второго инвертора и элемента . 2И-2ШШ-НЕ, что дает возможность развязать шины прямого и инверсного адресных сигналов друг от друга, позволяет применять для программирования импульсный режим тока без риска неправильного программирования и устранить влияние адресных сигналов друг на друга во всех режис мах работы устройства программировасе ния. Повышение быстродействия достигается за счет отсутствия дополнительных задержек на адресные сигналы. 1 ил.

| Электроника, 1981, № 5, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Там же, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1986-10-23—Публикация

1984-04-09—Подача