1

Изобретение относится.к вычи лительной технике и может быть использовано при проектировании цифровых интегральных схем.

Известен магистральный элемент, используемый в интегральных схемах. Он предназначен для работы на внешнюю магистраль и содержит формирователь логического уровня,выход которого соединен с выходом магистрального элемента и схему управления, выход .которой подключен ко входу формирователя логического уровня,а входы к информационной шине и шине управления выдачей информации.

По технической сущности наиболее (близким к предлагаемому является блок согласования с магистралью, содержащий формирователь логического уровня, элементы НЕ, И-НЕ, КЛИНЕ, информационную шину, подк.точенную к первым входам первых элементов И-НЕ и ИЛИ-НЕ, шина управления блока подключена ко второму входу первого элемента И-НЕ, и через первый элемент НЕ ко второму входу первого элемента ИЛИ-НЕ, выход которого подключен к первому входу фор.мирователя логического уровня.

Логика работы блока согласования с магистралью может быть представлена следующим образом: Инф.Строб.Вых.И-НЕ Вых.ИЛИ-НЕ Вых.М.Э

X О 1 О

1 о

1

о

о

О

10

ФоЕ 1ирование на сигнальной шине строб (на которой формируется сигнал выдачи информации) уровня логического О соответствует формированию на выходе магистрального элемента

5 неопределенного уровня (-). При формировании на сигнальной шине Строб уровня логической 1 на выходе магистрального блока формируется логический уровень, соответствующий поступающей информации.

При организации магистральной структура состояние Отключено должно соответствовать уровню логического 25 о, при этом любой выходной блок

этой магистрали должен иметь возможность установить на магистрали уровень логической 1.

В известном магистральном элементе состояние Отключено соответствует неопределенному логическому уровню, а уровень логического О активный и не позволяет установить извне уровень логической 1.

Время восстановления уровня логического О в этом блоке после выдачи логической 1 существенно в€1лик Это определяется тем, что к выходу блока подключен высокоомный резисто обеспечивающий формирование на выходе в состояние Отключено уровня логического о. Поэтому при переключении блока с уровня логической 1 в состояние Отключено (доопределяется до уровня логического о) требуется существенное время.

Цель изобретения - повышение надежности и б лстродействия.

Цель достигается тем, что блок согласования с магистралью содержит элемент И и триггер, первый вход

которого является выходом блока, второй вход подключен к шине управления, выход триггера и шина управления подключены соответственно к первому и второму входу второго элемента ИЛИ-НЕ, выход которого подклю:Чен к первому входу второго элемента И-НЕ, второй вход которого через второй элемент НЕ подключен к выход 0лока согласования, входы элемента И подключены соответственно к выходам первого и второго элементов И-НЕ, выход элемента И подключен ко второму входу формирователя логического уровня, а формирователь логического уровня содержит два р-каналных транзистора и один п-кангшьный ,МДП транзистор, стоки которых подключены к выходу формирователя логического уровня, истоки двух р-каналных МДП транзисторов подключены к ,шине питания, сток п-канального МДП .транзистора подключен к шине нулевого потенциала, затвор - к первому входу формирователя логического уровня, затвор первого р-канального МДП транзистора подключен ко второму входу формирователя логического уровня, затвор второго р-канального транзистора подключен к шине нулевого потенциала.

Триггер предназначен Для запоминания импульса выдачи информации под действием уровня логической 1 с выхода блока и сигнала с выхода триггера на одном входе формирователя внешнего логического уровня устанавливается сигнал обеспечивающий формирование на выходе магистрального элемента уровня логического 0. После установления на выходе блока уровня логического О триггер сбрасывается и выходной элемент отключается.

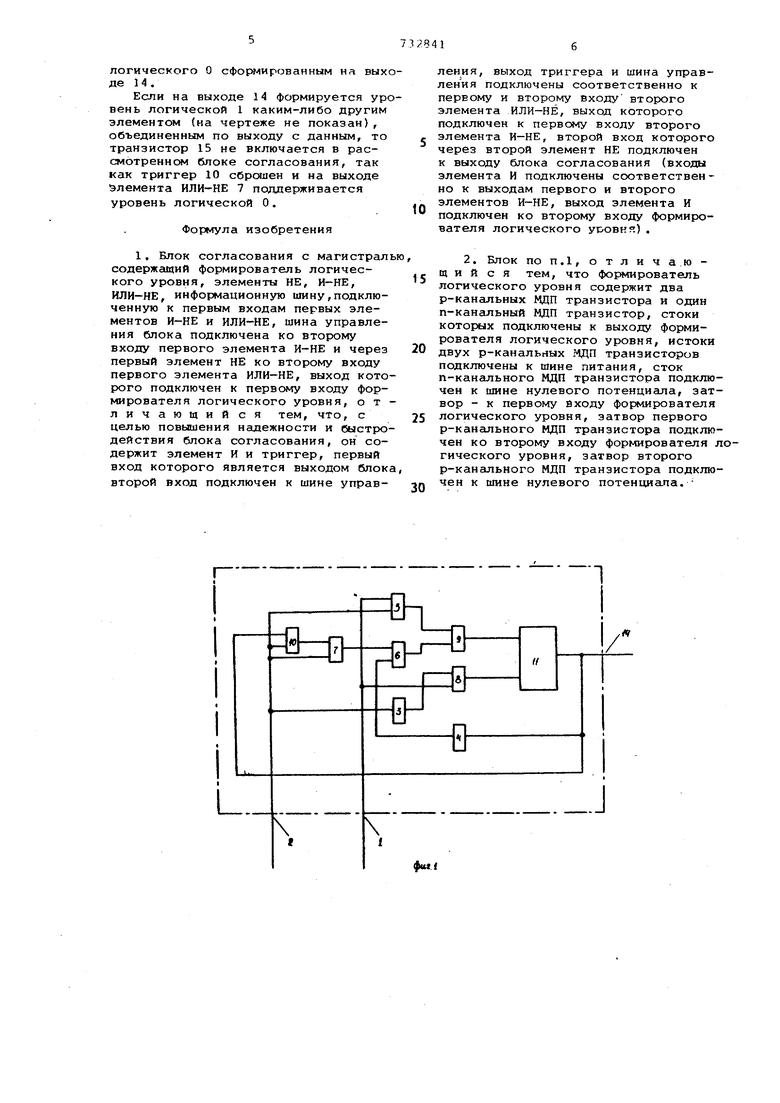

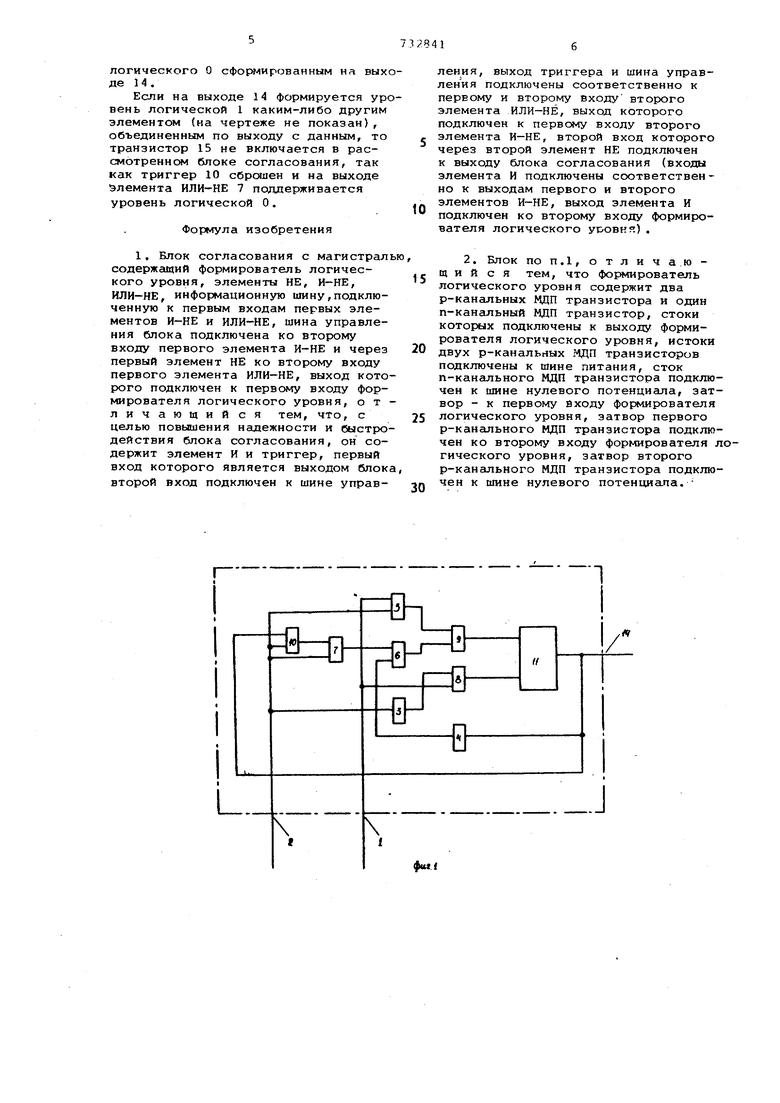

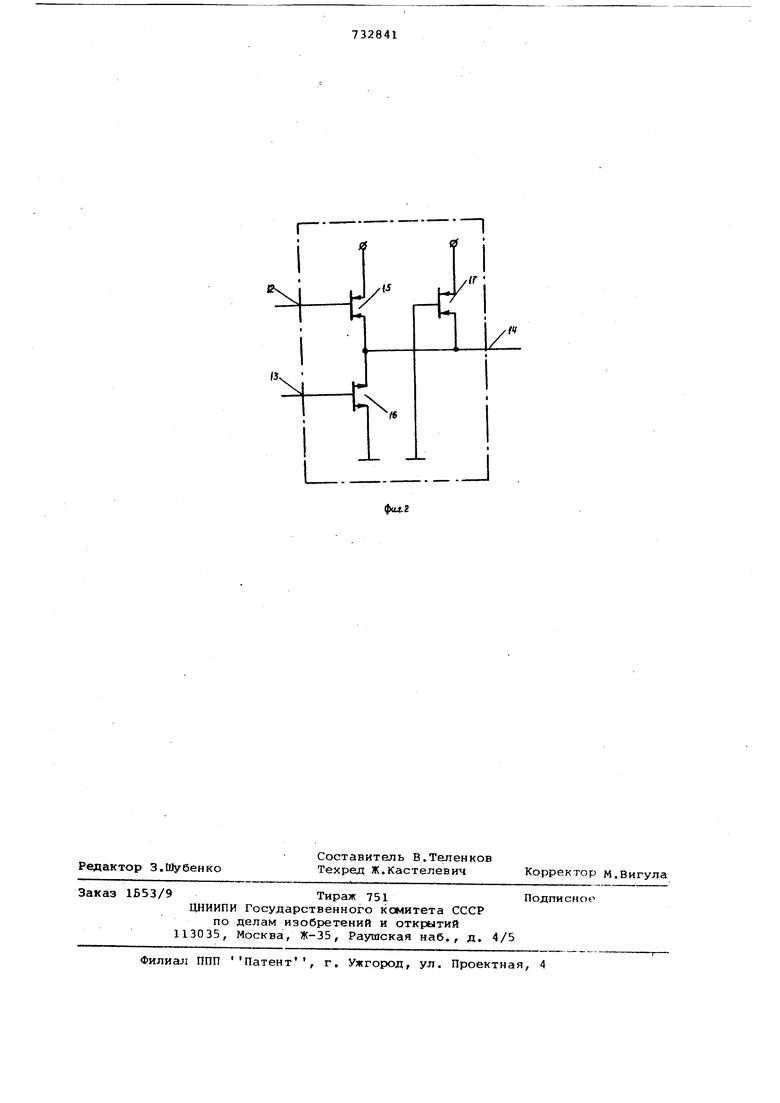

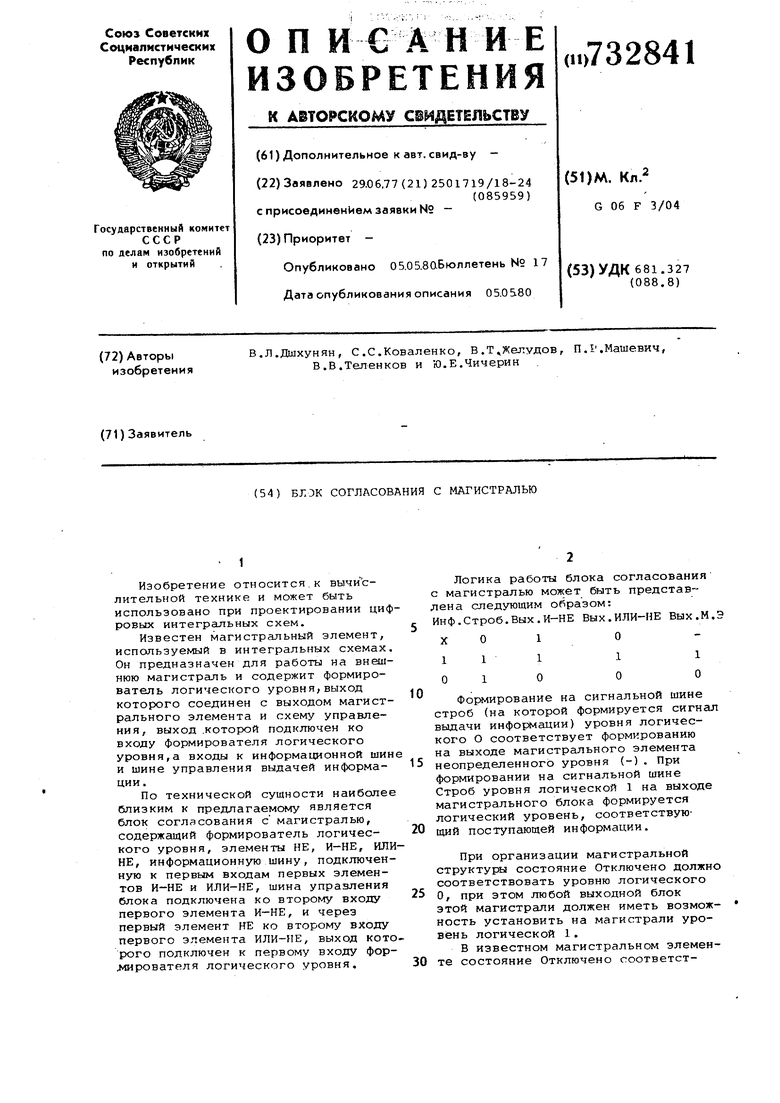

На фиг.1 представлена функциональная схема магистрального элемента; на фиг.2 - принципиальная схема формирователя выходного угхзвня.

Магистральный элемент содержит информационную шину 1 , шины .2 управления, элементы НЕ 3 и 4, элементы И-НЕ 5 и 6, элементы ИЛИ 7 и 8, элемент И 9, триггер 10, формирователь 11 выходного уровня, входы J 2 и 13 формировател-я выходjHoro уровня, выход 14 блока согласования с магистралью, р-канальный МДП транзистор 15, п-каиальный транзистор 16, р-канальный МДП транзистор 17.

Вход 12 формирователя 11 подклю5 чей к затвору транзистора 15, а вход 13 к затвору транзистора 16. Стоки транзисторов 15, 16 и 17 объединены и образуют выход 14 магистрального элемента.

Рассмотрим выдачу информации,

соответствующую выдаче логического О

(высокий уровень потенциала на выходе 14 блока согласования с магистралью) и логической 1 (низкий уровень сигнала на выходе 14).

5 Выдаче логического О соответствует возбуждение элемента И-НЕ 5, формирование на его выходе логического 0. На выходе элемента И 9 формируется уровень логического О, котоQ рый поступает на вход 12 формирователя 11. Включается р-канальный транзистор 15 и на выходе 14 формируется уровень логического 0. Когда на вход 2 не поступает стробирующий

сигнал, транзистор 15 отмечается и на выходе 14 блока согласования с магистралью поддерживается уровень логического О за счет постоянно включенного высокоомного транзистора 17. Все остальные элементы блока в режиме выдачи логического О не работают. При выдаче логической 1 на выходе элемента ИЛИНЕ 8 формируется уровень логической 1, который поступает на вход

5 13 формирователя 11, включается

п-канальный транзистор 16 и на выходе 14 формируется уровень логической 1. Триггер 10 переключается И формирует на своем выходе логичесQ кий 0. После окончания выдачи информации (на вход 2 поступает уровень логического 0) элемент И-НЕ 7 формирует на своем выходе уровень логической 1. На выходе элемента НЕ 4 уровень логической 1. Возбуждаются элементы И-НЕ 6, И 9, р-канальный транзистор 15 соответственно.

Транзистор 15 открыт до тех пор, пока на выходе 14 не сформируется уровень логического 0. Это обеспечивается обратной связью через элемент НЕ 4, элемент И-НЕ 6 и элемент И 9, транзистор 15 отключается. Уровень логического О на выходе 14 поддерживается высокоомным транзистором 17.

5 Триггер 10 сбрасывается уровнем логического О сформированным на вы де 14. Если на выходе 14 формируется ур вень логической 1 каким-либо другим элементом (на чертеже не показан), объединенным по выходу с данным, то транзистор 15 не включается в рассмотренном блоке согласования, так как триггер 10 сброшен и на выходе Элемента ИЛИ-НЕ 7 поддерживается уровень логической 0. Формула изобретения 1, Блок согласования с магистрал содержащий формирователь логического уровня, элементы НЕ, И-НЕ, ИЛИ-НЕ, информационную шину,подключенную к первым входам первых элементов И-НЕ и ИЛИ-НЕ, шина управления блока подключена ко второму входу первого элемента И-НЕ и через первый элемент НЕ ко второму входу первого элемента ИЛИ-НЕ, выход кото рого подключен к первому входу формирователя логического уровня, от личающийся тем, что, с целью повышения надежности и быстро действия блока согласования, он содержит элемент И и триггер, первый вход которого является выходом блок второй вход подключен к шине управления, выход триггера и шина управления подключены соответственно к первому и второму входу второго элемента ИЛИ-НЁ, выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого через второй элемент НЕ подключен к выходу блока согласования (входы элемента И подключены соответственно к выходам первого и второго элементов И-НЕ, выход элемента И подключен ко второму входу формирователя логического уровня). 2. Блок ПОП.1, о тли ч а.юЩ и и с я тем, что формирователь логического уровня содержит два р-канальных МДП транзистора и один п-канальный МДП транзистор, стоки которых подключены к выходу формирователя логического уровня, истоки двух р-канальных МДП транзисторов подключены к шине питания, сток п-канального МДП транзистора подключен к шине нулевого потенциала, затвор - к первому йходу формирователя логического уровня, затвор первого р-канального МДП транзистора подключен ко второму входу формирователя логического уровня, затвор второго р-канального МДП транзистора подключен к шине нулевого потенциа.па.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь выходного сигнала | 1985 |

|

SU1277384A1 |

| Двунаправленный формирователь | 1985 |

|

SU1277374A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Устройство для подключения к магистрали | 1984 |

|

SU1226480A1 |

| Разрядный формирователь | 1973 |

|

SU636674A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Формирователь выходных сигналов для запоминающего устройства на кмдп-транзисторах | 1978 |

|

SU767835A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

п

&

/

L..

xij/ Hf i

(3v

Jz

w

V

..I

I

Авторы

Даты

1980-05-05—Публикация

1977-06-29—Подача