Изобретение -относится к связи и может 6ь1ть использовано в автоматических цифровых коммутационных систе мах с микропроцессорным управлением,

Цел ь изобретения - сокращение вре установления соединения абонентских линий путем уменьшения времени доступа к ячейкам блока памяти.

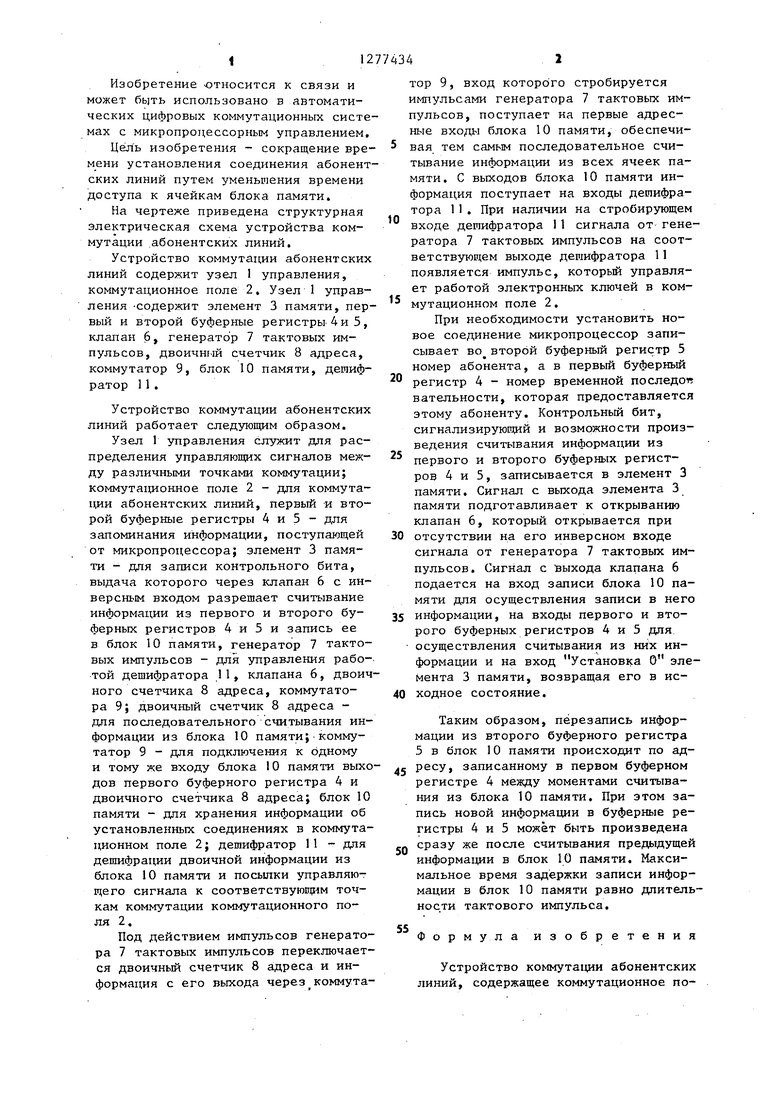

На чертеже приведена структурная электрическая схема устройства коммутации .абонентских линий.

Устройство коммутации абонентских линий содержит узел 1 управления, коммутационное поле 2. Узел 1 управления -содержит элемент 3 памяти, первый и второй буферные регистры 4и 5, клапан 6, генератор 7 тактовых импульсов, двоичный счетчик 8 адреса, коммутатор 9, блок 10 памяти, дешифратор 11 .

Устройство коммутации абонентских линий работает следующим образом.

Узел 1 управления служит для распределения управляющих сигналов между различными точками коммутации; коммутационное поле 2 - для коммутации абонентских линий, первый и второй буферные регистры 4 и 5 - для запоминания информации, поступающей от микропроцессора; элемент 3 памяти - для записи контрольного бита, выдача которого через клапан 6 с инверсным входом разрешает считывание информации из первого и второго буферных регистров 4 и 5 и запись ее в блок 10 памяти, генератор 7 тактовых импульсов - для управления работой дешифратора ,11, клапана 6, двоичного счетчика 8 адреса, коммутатора 9; двоичный счетчик 8 адреса - для последовательного считывания информации из блока 10 памяти; коммутатор 9 - для подключения к одному и тому же входу блока 10 памяти выходов первого буферного регистра 4 и двоичного счетчика 8 адреса; блок 10 памяти - для хранения информации об установленных соединениях в коммутационном поле 2; дешифратор 11 - для дешифрации двоичной информации из блока 10 памяти и посьшки управляющего сигнала к соответствующим точкам коммутации коммутационного поля 2.

Под действием импульсов генератора 7 тактовых импульсов переключается двоичный счетчик 8 адреса и информация с его выхода через коммута

тор 9, вход которого стробируется импульсами генератора 7 тактовых импульсов, поступает на первые адресные входы блока 10 памяти, обеспечивал тем самым последовательное считывание информации из всех ячеек памяти. С выходов блока 10 памяти информация поступает на входы дешифратора 11. При наличии на стробирующем входе дешифратора I1 сигнала от генератора 7 тактовых импульсов на соответствующем выходе дешифратора 11 появляется импульс, которьй управляет работой электронных ключей в ком мутационном поле 2.

При необходимости установить новое соединение микропроцессор записывает во второй буферный регистр 5 номер абонента, а в первый буферный

регистр 4 - номер временной последот вательности, которая предоставляется этому абоненту. Контрольный бит, сигнализируюшд й и возможности произведения считывания информации из первого и второго буферных регистров 4 и 5, записывается в элемент 3 памяти. Сигнал с выхода элемента 3 памяти подготавливает к открыванию клапан 6, который открывается при

0 отсутствии на его инверсном входе сигнала от генератора 7 тактовых импульсов. Сигнал с выхода клапана 6 подается на вход записи блока 10 памяти для осуществления записи в него

5 информации, на входы первого и второго буферных регистров 4 и 5 для осуществления считывания из них информации и на вход Установка О элемента 3 памяти, возвращая его в ис0 ходное состояние.

Таким образом, перезапись информации из второго буферного регистра 5 в блок 10 памяти происходит по адс ресу, записанному в первом буферном регистре 4 между моментами считывания из блока 10 памяти. При этом запись новой информации в буферные регистры 4 и 5 может быть произведена

-J. сразу же после считывания предыдущей информации в блок 10 памяти. Максимальное время задержки записи информации в блок 10 памяти равно длительности тактового импульса.

55

Форм у л а изобретения

Устройство коммутации абонентских линий, содержащее коммутационное поле, к входам которого подключены выходы узла управления, состоящего из первого и второго буферных регистров элемента памяти, генератора тактовых импульсов, двоичного счетчика адреса, блока памяти и дешифратора, к стробиругощему входу которого и входу двоичного счетчика адреса подключен выход генератора тактовых импульсов, при этом выходы второго буферного регистра подключены к входам данных блока памяти, выходы которого подключены к входам дешифратора, выходы которого являются выходами узла управления, отличающееся тем, что, с целью сокращения времени установления соединения абонентских

277434

линий путем уменьшения времени доступа к ячейкам блока памяти, в него введены клапан и коммутатор, выходы которого подключены к адресным вхо- 5 дам блока памяти, к входу записи которого и входам элемента памяти, первого и второго буферных регистров подключен выход клапана, к прямому входу которого подключен выход элемента памяти, при этом выход генератора тактовых импульсов подключен к инверсному входу клапана и стробиру- ющему входу коммутатора, к первым и вторым входам которого подключены 15 соответственно выхода двоичного счетчика адреса и первого буферного регистра.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Цифровое коммутационное устройство | 1985 |

|

SU1378088A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2090982C1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для отображения информации | 1991 |

|

SU1807520A1 |

Изобретение может быть использовано в автоматических цифровых коммутационных системах с микропроцессорным управлением. Цель изобретения - coкpap eниe :времени установления соединения абонентских линий. Устройство содержит коммутационное поле (КП) 2 и узел 1 управления, состоящий из элемента 3 памяти, двух буферных регистров 4 и 5, клапана 6, генератора 7 тактовых импульсов, двоичного счетчика .8 адреса, коммутатора (к) 9, блока 10 памяти (БП) и дешифратора 11. Информация с выхода счетчика 8 через К 9 поступает на адресные входы БП 10, обеспечивая последовательное считывание информации из всех ячеек памяти. Дпя осуществления записи информации в БП 10, на его вход записи подается сигнал с выхода клапана 6. С выходов БП 10 информация поступает в дешифратор 11 , который управляет работой электронных ключей в КП 2. Цель достигается введением клапана 6 и К 9, с помощью которых уменьшается время доступа к ячейкам БП 10. 1 ил. ё СП

| Патент США № 4286119,, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Статья Mikrorechnergestenerter Vermiltlungsmodul nach den Zeitei- lungsprinzip, H | |||

| Petasch, Permnel- detechnik, 21 | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-15—Публикация

1984-12-24—Подача