112

Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам алгебраического суммирования частот частотно импульсных сигналов, и предназначено для преимущественного использования в системах регулирования тягового синхронного электропривора, содерлса щего статические преобразователи частоты.

Цель изобретения - увеличение надежности процесса суммирования.

Особенностью тягового асинхронного электропривода., содержащего статические преобразователи частоты, является многозонное амплитудно-частотное регулирование тягово-энергетичес- ких характеристик асинхронных двигателей, что приводит к необходимости рационального многозонного управле НИН частотой коммутации главньк и коммутирующих вентилей за период выходной частоты статического преобразователя частоты, что накладывает особые требования на протяжении всего срока службы алгебраического суммированного устройства на точность реализации выходной функции в ка;адой зоне многозонного регулирования:

m:

(F, ± F,),

де

вых

FI F. m. быг -1 2

выходная частота алгебраи™ ческого суммирующего устройства;

частота вращения ротора асинхронного двигателя; заданное значение частоты скольжения;

модуль пересчета, дискретно принимающий значения т, - в соответствии с зоной управлен11я частотой коммута- 1ЩИ главных и коммутирующих вентилей за период выходной частоты статического преобразователя частоты.

Су1фшруемые частоты F, и Р мпульсных последовательностей пре бразуют в цифровые коды периодов

т,

2

N,

частот FI и F ;

го генератора;

и цифровой код алгебраической суммы периодов

N

Далее одновременно формируют две импульсные последовательности: в про- цессе первой цепи последовательных делений второй опорной частоты Pgj на цифровые коды периодов первой и второй входных частот (частота F, общем случае больше F )

02

Л,

N,

ог

F

ПИ

Fiu : ЕеЯ- Е1-Ег.

N..

F F

01 -Ot

и в процессе второй цепи последовательных делений второй опорной частоты на цифровые коды алгебраической суммы периодов и модуля пересчета

А2

. FO. .EI.

N,

р (р + -р )

01 ( - 2

Ai

.о.г..

FO, (F, ± F,).mi

30

35

Далее кодируют периоды Тд импульсной последовательности Г., , полученной от первой цепи последовательных делений, импульсами импульсной последовательности Гд (период Тд2)р полученной от 1зторой цепи последовательных делений.

Далее первую опорную частоту делят на полученный код и получают выходную импульсную последовательность с частотой следования импуль45

сов

Е21 N.

m

(F, ±

F,).

, При равенстве нулю одной из входных частот (например ,0) первое деление производят на цифровой код во второй степени периода на равной нулю входной частоты, например на

55 F

Ai

а цифровой код алгебраической суммы периодов приравнивают цифровому коду периода на равной нулю входной частоты (для данного примера N N ), тогда при втором делении сформируются импульсные последовательности

аг

Ng.

Fo2 .:L.El.

N,

Ek.

m;

oi

.02.,

Fa

FO, i

a выражения N,, и

к примера примут вид

для данного

N,

рд2 FOI

m .

F

вых Нц

m;F.

д z

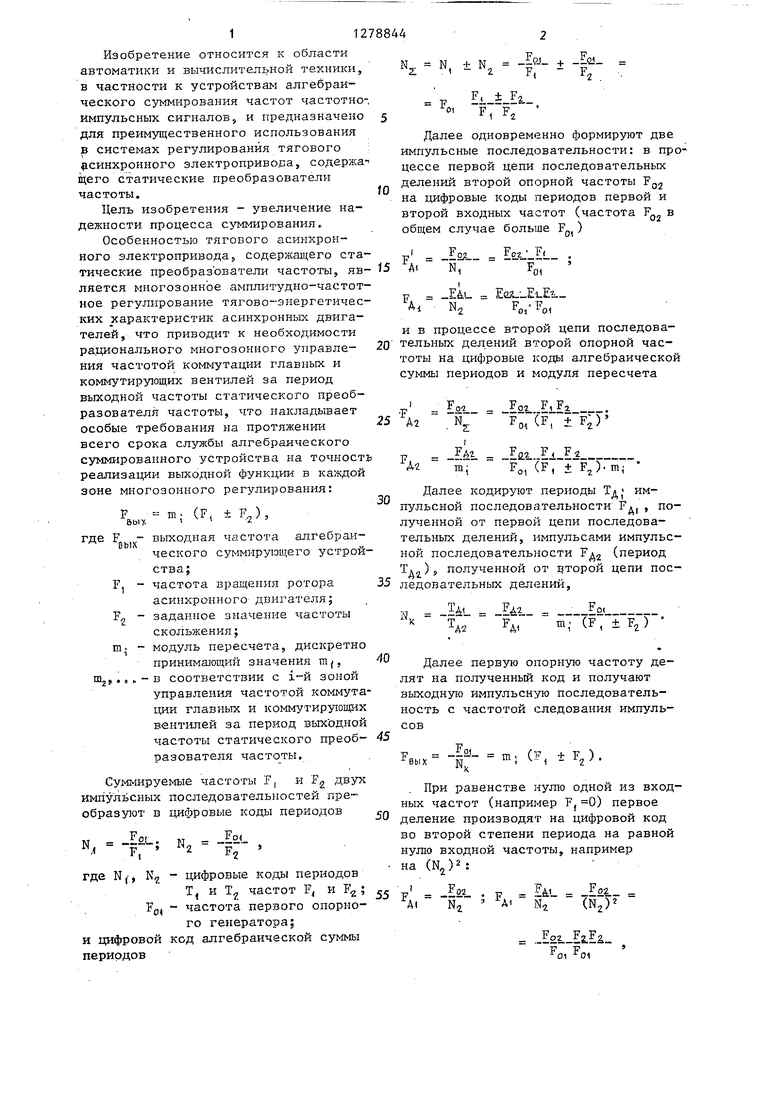

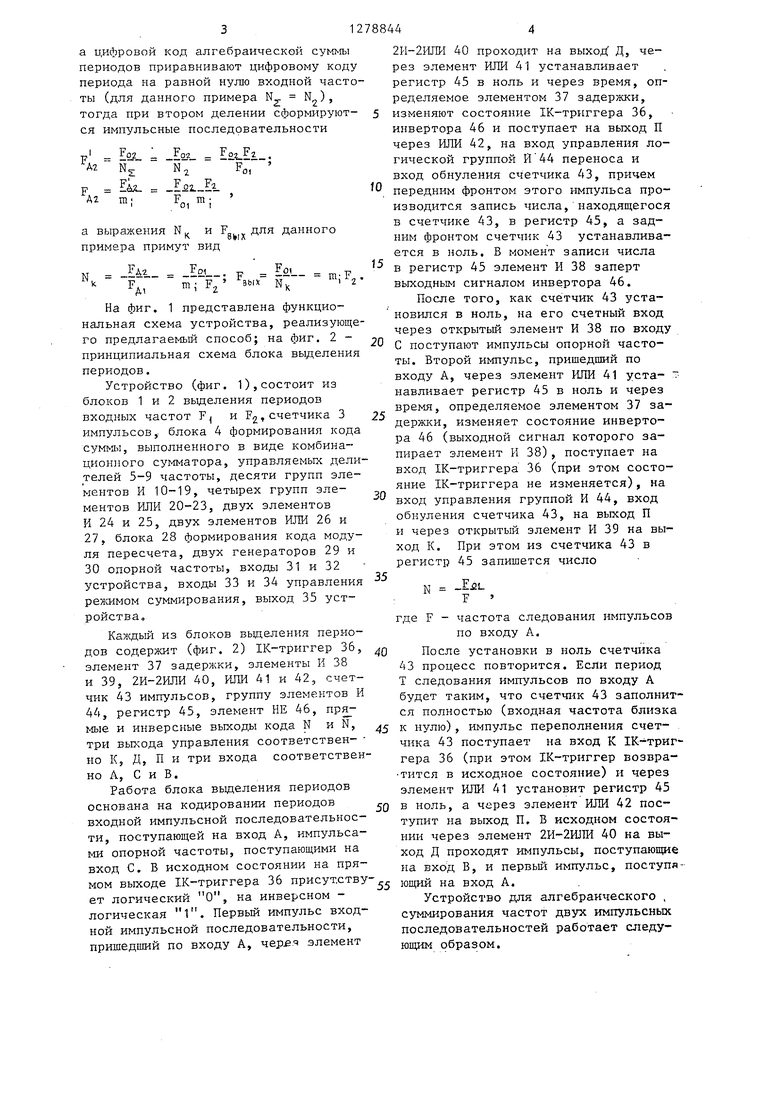

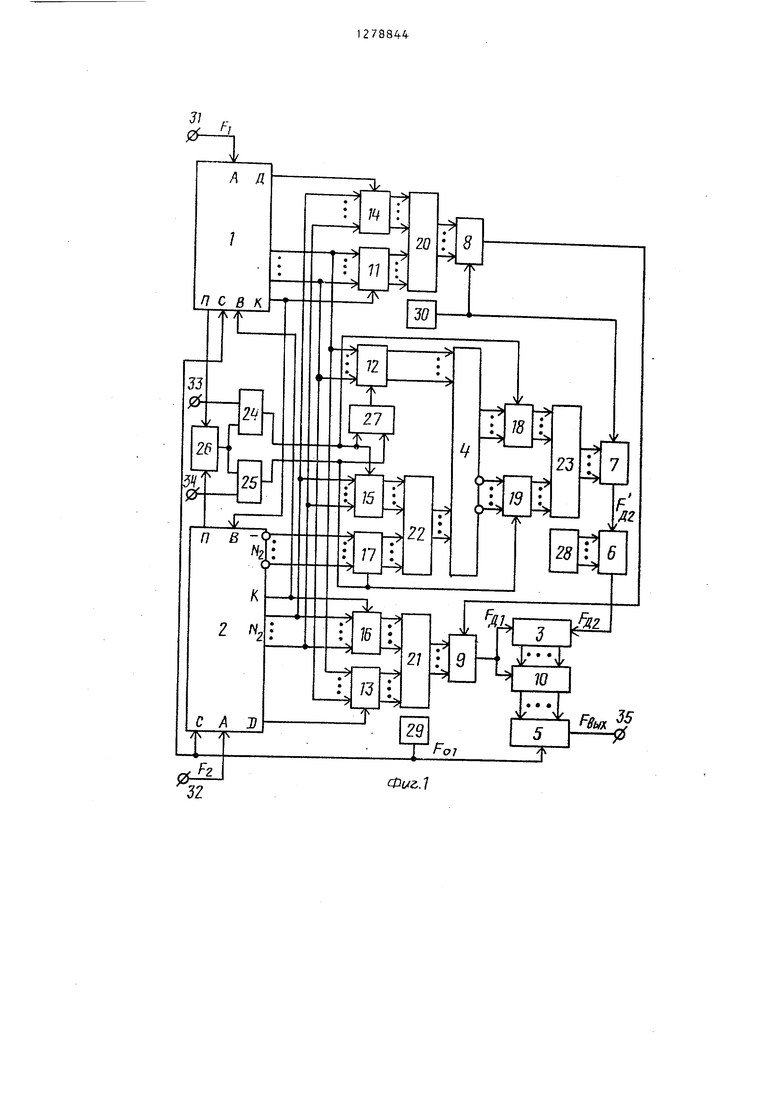

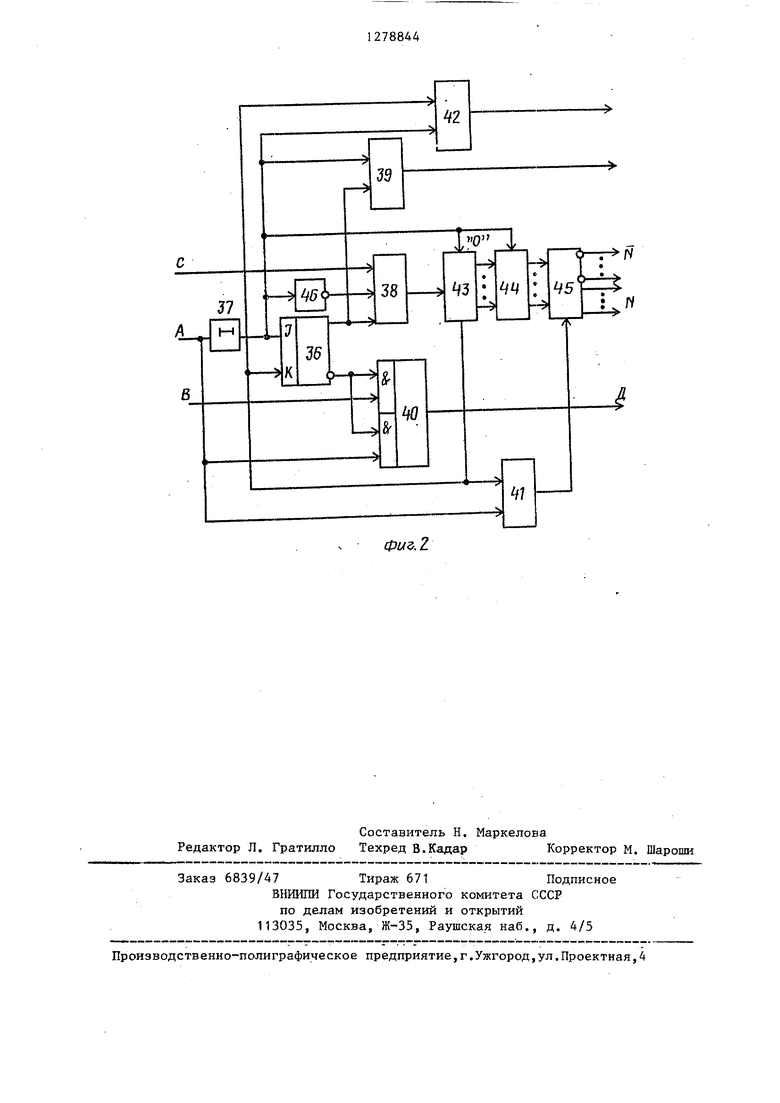

На фиг. 1 представлена функциональная схема устройства, реализующего предлагаемьо способ; на фиг. 2 - принципиальная схема блока выделения периодов.

Устройство (фиг. 1),состоит из блоков 1 и 2 вьщеления периодов

Fg,счетчика

входных частот F и импульсов, блока 4 формирования кода cyMMii, выполненного в виде комбинационного сумматора, управляемых делителей 5-9 частоты, десяти групп элементов И 10-19, четырех групп элементов ИЛИ 20-23, двух элементов И 24 и 25, двух элементов ИЛИ 26 и 27, блока 28 формирования кода модуля пересчета, двух генераторов 29 и 30 опорной частоты, входы 31 и 32 устройства, входы 33 и 34 управления реяхимом суммирования, выход 35 устройства.

Каждый из блоков вьщеления периодов содержит (фиг. 2) 1К-триггер 36, элемент 37 задержки, элементы И 38 и 39, 2И-2ИЛИ 40, ИДИ 41 и 42, счетчик 43 импульсов, группу элементов И 44, регистр 45, элемент НЕ 46, пря мые и инверсные выходы кода N и N, три вькода управления соответствен- но К, Д, П и три входа соответственно А, Си В.

Работа блока вьщеления периодов основана на кодировании периодов входной импульсной последовательности, поступающей на вход А, импульсами опорной частоты, поступающими на вход С. В исходном состоянии на прямом выходе 1К-триггера 36 присут.ству ВТ логический О, на инверсном - логическая 1. Первый импульс входной импульсной последовательности, пришедший по входу А, элемент

2И-21-1ЛИ 40 проходит на выхо Д, через элемент ИЛИ 41 устанавливает регистр 45 в ноль и через время, определяемое элементом 37 задержки, изменяют состояние 1К-триггера 36, инвертора 46 и поступает на выход П через ИЛИ 42, на вход управления логической группой И 44 переноса и вход обнуления счетчика 43, причем передним фронтом этого импульса производится запись числа, находящегося в счетчике 43, в регистр 45, а задним фронтом счетчик 43 устанавливается в ноль. В момент записи числа в регистр 45 элемент И 38 заперт выходньм сигналом инвертора 46.

После того, как счётчик 43 установился в ноль, на его счетный вход через открытьш элемент И 38 по входу С поступают импульсы опорной частоты. Второй импульс, пришедший по входу А, через элемент ИЛИ 41 уста- навливает регистр 45 в ноль и через время, определяемое элементом 37 задержки, изменяет состояние инвертора 46 (выходной сигнал которого запирает элемент И 38), поступает на вход 1К-триггера 36 (при этом состояние 1К-триггера не изменяется), на вход управления группой И 44, вход обнуления счетчика 43, на выход П и через открытый элемент И 39 на выход К. При этом из счетчика 43 в регистр 45 запишется число

N

F

где F - частота следования импульсов по входу А.

После установки в ноль счетчика 43 процесс повторится. Если период Т следования импульсов по входу А будет таким, что счетчик 43 заполнится полностью (входная частота близка

к нулю), импульс переполнения счетчика 43 поступает на вход К 1К-триг- гера 36 (при этом 1К-триггер возвра- тится в исходное состояние) и через элемент ИЖ 41 установит регистр 45

в ноль, а через элемент ИЛИ 42 поступит на выход П. В исходном состоянии через элемент 2И-2ШШ 40 на выход Д проходят импульсы, поступающие на вход В, и первый импульс, поступя- ющий на вход А.

Устройство для алгебраического , суммирования частот двух импульсных последовательностей работает следующим образом.

На входы 31 и 32 (фиг, 1), соединенные соответственно с первыми входами А блоков 1 и 2, соответственно поступают входные импульсные пос-.. ледовательности с частотами F, и F , а на входы 33 и 34 поступают сигналы Q(Q) управления режимом суммирования: соответственно логические 1 и О при сложении и логические О и 1 при вычитании входных частот. На вторые входы С блоков 1 и 2 поступает опорная частота . Блоки 1 и- 2 входные частоты F, и Е преобразовывают в цифровые коды периодов, соответственно N, и N. При каждом формировании N(N) блок 1(2) кратковременно (на время длительности входного импульса) формирует логические 1 на первом К и третьем

20

Далее одновременно формируются две импульсные посдедовательности: Рд, формируется в процессе первой цепи последовательных делений опорП управляющих выходах, если входная

частота F, (F) отлична от нуля, или

на втором Д и третьем П управляющих

выходах, если входная частота F(F)

близка к нулю, или на третьем П уп- код N в управляемом делителе 9 а

равляющем выходе, если входная часто- F. формируется в процессе второй

та F(Fg) равна нулю.-цепи последовательных делений опорКогда входная частота F отлична от нуля, логическая 1, сформированная на первом управляющем выходе К блока 1, поступает на вход управления группы логических элементов И 11 переноса и код N, через группы логических элементов И 11 и ШШ 20 переноса поступает на входы управления и записьшается в управляемом делите30

ной частоты FO на код N, в управля емом делителе 8 и деления полученно импульсной последовательности F, на

ной частоты F на код Nj в управляемом делителе 7 и деления полученной импульсной последовательности

код

т в управляемом делителе 6. Число импульсов N| импульсной последовательности F., поступивших на счетньш вход счетчика 3 за время периода Тд, импульсной последова35 тельности F., поступает на входы уп равления и записывается в управляемом делителе 5, который формирует выходную импульсную последовательность посредством деления опорной

ле 8.

Когда входная частота F отлична от нуля, аналогичным образом код N записывается в управляемом делителе 9.

Логическая 1, сформированная нь, третьем управляющем выходе П блока 1 или 2, поступает на соответствующие

входы ИЛИ 26 и в режиме сложения час- ходе Д блока 1, поступает на вход тот через И 24 поступает на управляю- управления группы элементов И 14 и ,

код Nj, с блока 2 через группы эле-.

ментов И 14 и ИЛИ 20 поступает на

щие входы групп элементов И 15 и 18

и через ИЛИ 27 - на управляющий вход

группы элементов И 12. При этом на

первый вход блока 4 формирования ко- Q управляемом делителе 8, при этом

зходы управления и записьшается в

первая цепь последовательных делений осуществляет деление опорной частоты Ff,2 н а код N2 в управляемом делителе 8 и деление полученной импульсной ее последовательности Fд на код N в управляемом делителе 9, а логическая 1, сформированная на третьем управляющем выходе П блока 1, поступает на вход ИЛИ 26 управления, при

да суммы поступает через группу элементов И 12 код N(, а на второй вход через группы элементов И 15 и ИЛИ 22 поступает код N. Код суммы периодов Nf через группы элементов И 18 и ШШ 23 пост пает на входы управления и записывается в управляемом делителе 7. В режиме вычитания kacTOT логическая 1, сфоршфован

5

0

нал на третьем управляющем выходе П блока 1 или 2, через ИЛИ 26 и И 25 поступает на управляющие входы групп элементов И 17 и 19 через ИЛИ 27 - на управляющий вход группы элементов И 12, При этом на первый вход блока 4 поступает через группу эле- р ентов И 12 код N, , а на второй вход через группы элементов И 17 и ИЛИ 22 с инвер ных выходов блока 2 поступает код N . Код разности периодов Nj. через группы элементов И 19 и ИЛИ 23 с инверсных выходов блока 4 поступает на входы управления и записывается в управляемом делителе 7.

Далее одновременно формируются две импульсные посдедовательности: Рд, формируется в процессе первой цепи последовательных делений опоркод N в управляемом делителе 9 а

ной частоты FO на код N, в управляемом делителе 8 и деления полученной импульсной последовательности F, на

цепи последовательных делений опор

ной частоты F на код Nj в управляемом делителе 7 и деления полученной импульсной последовательности

код

т в управляемом делителе 6. Число импульсов N| импульсной последовательности F., поступивших на счетньш вход счетчика 3 за время периода Тд, импульсной последовательности F., поступает на входы управления и записывается в управляемом делителе 5, который формирует выходную импульсную последовательность посредством деления опорной

частоты FOI на код N. , .

При равенстве нулю одной из входных частот (например F, 0) логическая Vp сформированная на втором вы зходы управления и записьшается в

управляемом делителе 8, при этом

первая цепь последовательных делений осуществляет деление опорной частоты Ff,2 н а код N2 в управляемом делителе 8 и деление полученной импульсной последовательности Fд на код N в управляемом делителе 9, а логическая 1, сформированная на третьем управляющем выходе П блока 1, поступает на вход ИЛИ 26 управления, при

712788ДАэтом на первый вход- блока 4 поступает код N, 0, а на второй вход - код N

I w J - lit Lj i v. ijj-vv |;j, -ffj O

Код суммы периодов, равный при этом

и ле пу

ния и

К„

поступает на входы управле- записывается в управляемом де- лителе 7. Кроме того, логическая 1 сформированная на выходе К блока 2, поступает на третий вход В блока 1 и при проходит на второй управляющий выход Д блока 1. При этом так же код N, с блока 2 поступает на входы управления делителей 8 и 9, а логическая 1, сформированная на третьем управляющем выходе П блока 2, поступает на вход ИЛИ 26 управле- ния, Аналогичным образом на первый вход блока 4 поступает код N, 0, а на второй вход - N. Код суммы периодов N Nj поступает на входы управления и записывается в управляемом делителе 7. Далее одновременно формируются две импульсные последо

вателыюсти

FAI

а затем и вына входы управления и в управляемых делителях

ходная импульсная последовательность аналогично описанному.

При F2 О аналогичным образом код N, поступает записывается 8 и 9, а код суммы периодов N N поступает на входы управления и записывается в управляемом делителе 7.

Если F, О, а через некоторое время и , то последний импульс им25

30

Устройство для алгебраического суммирования частот двух импульсны последовательностей, содержащее д генератора опорной частоты, счетчи импульсов, блок формирования кода суммы, два блока выделения период два управляемых делителя частоты, причем первые информационные входы блоков вьщеления периодов являются соответственно первым и вторым вх дами устройства, вторые информаци ные входы блока выделения периодо соединены с выходом первого генер тора опорной частоты, выход перво управляемого делителя частоты соед нен со счетным входом второго упр ляемого делителя частоты, отли чающееся тем, что, с целью увеличения надежности процесса сум рования, в него введены блок вания кода модуля пересчета, три у равляемых делителя частоты, десят групп элементов И, четыре группы ментов ИЛИ, два элемента И и два мента ИЛИ, причем каждый блок вьщ ния периода содержит 1К-триггер,

пульсной последовательности Fg, пос- элемент задержки, элемент НЕ, два

2

тупивший на вход А блока 2, обеспе- 35 чивает формирование на его управляющих выходах К и П логической 1, при этом код N2 поступает на входы управления и записывается в управляемые делители 8 и 9, а код суммы пе- 40 риодов N 2 поступает на входы управления и записывается в управляемом делителе 7. Поскольку по входу А блока 2 импульсы входной импульсной последовательности не поступают, 45 то на выходе управления П блок 2 дополнительно сформирует логическую 1,- при этом выходной регистр блока 2 установится в ноль N 0. Логическая 1, сформированная на управ- 50 ляющем выходе П блока 2, поступает на вход ИЛИ 26 управления, при этом на первый вход блока 4 поступает код N,/ 0, а на второй вход - . Код суммы периодов поступает 55 на входы управления и записывается в управляемом делителе 7. При этом Рд. 0, а следовательно и Рд, О, код N,, 0 поступает на входы управления

элемента И, счетчик импульсов, ре гистр, элемент 2И-2ИЛИ, два элеме та ИЛИ, при этом выход первого ген ратора опорной частоты соединен с счетным входом третьего управляем делителя частоты, управляющие вход которого соединены с выходами пер группы элементов И, первые входы торых соединены с выходом второго равляемого делителя частоты и вход обнуления счетчика импульсов, сче ный вход которого соединен с выход четвертого управляемого делителя

тоты, выходы счетчика импульсов с динены с вторыми входами первой г пы элементов И, выходы блока форм вания кода модуля пересчета соеди ны с входами управления четвертог управляемого делителя частоты,- сч ный вход которого соединен с выход пятого управляемого делителя част счетньй вход которого соединен с вы ходом второго генератора опорной частоты и счетным входом первого у

равляемого делителя частоты, входы

и записывается в управляемом делителе 5, при этом частота выходной импульсной последовательности равна

нулю F 0, ЬМУ

Формула изобретения

Устройство для алгебраического суммирования частот двух импульсных последовательностей, содержащее два генератора опорной частоты, счетчик импульсов, блок формирования кода суммы, два блока выделения периодов, два управляемых делителя частоты, причем первые информационные входы блоков вьщеления периодов являются соответственно первым и вторым входами устройства, вторые информационные входы блока выделения периодов соединены с выходом первого генератора опорной частоты, выход первого управляемого делителя частоты соединен со счетным входом второго управляемого делителя частоты, отличающееся тем, что, с целью увеличения надежности процесса суммирования, в него введены блок фop fflpo- вания кода модуля пересчета, три управляемых делителя частоты, десять групп элементов И, четыре группы эл-е- ментов ИЛИ, два элемента И и два элемента ИЛИ, причем каждый блок вьщеления периода содержит 1К-триггер,

элемент задержки, элемент НЕ, два

элемента И, счетчик импульсов, регистр, элемент 2И-2ИЛИ, два элемента ИЛИ, при этом выход первого генератора опорной частоты соединен со счетным входом третьего управляемого делителя частоты, управляющие входы которого соединены с выходами первой группы элементов И, первые входы которых соединены с выходом второго управляемого делителя частоты и входом обнуления счетчика импульсов, счетный вход которого соединен с выходом четвертого управляемого делителя час тоты, выходы счетчика импульсов сое- динены с вторыми входами первой группы элементов И, выходы блока формирования кода модуля пересчета соединены с входами управления четвертого управляемого делителя частоты,- счетный вход которого соединен с выходом пятого управляемого делителя частоты счетньй вход которого соединен с выходом второго генератора опорной частоты и счетным входом первого уп-

равляемого делителя частоты, входы

.управления которого соединены с выхо- дами первой группы элементов ЮТ1, .выход элемента первого блока вьщеления периода соединен с первьми входами элементов И второй группы, 5 вторые входы которых соединены с ррямыми выходами регистра второго - блока выделения периода, с первыми, входами элементов И третьей и четвертой групп, прямые выходы регистра 0 первого блока выделения периода соединены с первыми входами элементов И пятой, шестой и седьмой групп, выход первого элемента И первого блока вЫ деления периода соединен с- вторыми входами элементов И пятой группы и первым входом первой группы элемента 2И-2ИЛИ второго блока выделения периода, выход первого элемента И которого соединен с вторьми входами 20 элементов И четвертой группы и первым входом первой группы элемента 2И-2ИЛ11 первого блока выделения периода, инверсные выходы регистра второго блока выделения периода соедине-

5

ны с первыми входами элементов И восьмой группы, вторые входы элементов И седьмой группы соединены с выходом элемента 2И-2ИЛИ.второго блока вьщеления периода выходы элементов HJIIi первого и второго блоков вьщеления периода соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым входами управления ренсимом суммирования, вькод первого элемента И соединен с первым входом второго элемента ИЛИ, вторыми вxoдa ш элементов И третьей группы и первыми входами элементов И девятой rpynnjji, вторые входы которых, соединены с прямьми выходами

входами э.лементов И группы и входами первых элементов И и RlTIi, первые входы элемента задержки второго элемента И соответственно первым и вторым информационными входами блоков выделения периодов, выход переполнения счетчика соединен с К входом Ж-триггера и первым . и вторым входами соответственно вто- 35 рого и первого элементов ИЛИ, прямой выход 1К- Триггера соединен с вторыми входаш-г первого и второго элементов И, третий вход второго элемента И соединен с выходом элемента НЕ, выход второго элемента И соединен со счетным входом счетчика импульсов, выходы которого соединены с вторыми входаг-ш элементов И группы, выходы которых соединены с входаблока формирования кода суммы, инфор- 45 J,JH регистра, вход установки нуля комационные входы перво.й группы кото- рого соединены с выходами элементов И шестой группы, вторые входы которых соединены с выходом второго элеторого соединен с выходом второго - элемента ИЛИ, второй вход которого соединен с первым входом второй группы элемента 2И-2ИЛИ и входом злеменмента ИЛИ, второй вход которого сое- 50 та задержки, инёерсньй выход 1К-триг- Динен с выходом второго элемента И, гера соединен с вторыми входами пер- с вторыми входами элементов И вось- „ второй групп элемента 2И-2ШШ.

мой группы и первыми входами элементов И десятой , вторые входы которых соединены с инверсными выходами блока формирования кода суммы, информационные входы второй группы которого соединены с выходами элементов ИЛИ второй группы, входы которых соединены с выходами элементов И третьей и восьмой групп, выходы элементов И пятой группы соединены с входами элементов ИЛИ первой группы, выходы элементов И четвертой и седьмой I pyjin и девятой и десятой групп соединены соответственно с входами элементов ИЛИ третьей и четвертой групп, выходы которых соединены соответственно с входами управления второго и пятого управляемых делителей частоты, выход третьего управляемого д€;лителя частоты является выходом устройства, при этом выход элемента задержки блока вьщеления периода соединен с 1-входом 1К-триггера, входом элемента НЕ, вхо-. дом установки нул.я счетчика, первьп ш

30

входами э.лементов И группы и входами первых элементов И и RlTIi, первые входы элемента задержки второго элемента И соответственно первым и вторым информационными входами блоков выделения периодов выход переполнения счетчика соединен с К входом Ж-триггера и первым . и вторым входами соответственно вто- 35 рого и первого элементов ИЛИ, прямой выход 1К- Триггера соединен с вторыми входаш-г первого и второго элементов И, третий вход второго элемента И соединен с выходом элемента НЕ, выход второго элемента И соединен со счетным входом счетчика импульсов, выходы которого соединены с вторыми входаг-ш элементов И группы, выходы которых соединены с входа40

45 J,JH регистра, вход установки нуля которого соединен с выходом второго - элемента ИЛИ, второй вход которого соединен с первым входом второй группы элемента 2И-2ИЛИ и входом злеменФи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Преобразователь сдвига фаз в цифровой код | 1974 |

|

SU532059A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство для суммирования частотно-импульсных сигналов | 1977 |

|

SU708361A1 |

| Преобразователь сдвига фаз в цифровой код | 1978 |

|

SU781708A1 |

| Частотно-импульсный функциональный преобразователь | 1980 |

|

SU953640A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Частотно-импульсное делительное устройство | 1980 |

|

SU898429A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к способам и устройствам алгебраического суммирования частот частотно-импульсных сигналов, и предназначено для преимущественного применения в системах регулирования тягового асинхронного электропривода, содержащего статические преобразова тели частоты для формирования частотно-импульсного сигнала управления преобразователем. Целью изобретения является увеличение надежности мирования. Выходную импульсную последовательность формируют путем одновременного первого деления опорной частоты на 1 ;ифровые коды периодов входных частот и второго деления на цифровые коды суммы периодов и модуля пересчета с последующим кодированием и делением опорной частоты на полученный код, причем при равенстве нулю одной из входных частот первое деление производят на цифровой код во второй степени периода не равной нулю частоты, а код сытимы периодов, приравнивают к коду периода не равной нулю частоты. Вводятся новые операции: одновременное первое деление опорной частоты на цифровые коды периодов и второе деление опор™ ной частоты на цифровые коды периодов и модуля пересчета; кодирование периода импульсной последовательности от первого деления импульсами, от второго деления и деление опорной частоты на этот код. 2 ил. i ю 8 00

| Авторское свидетельство СССР № 758150, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Частотно-импульсное алгебраическое суммирующее устройство | 1975 |

|

SU575650A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1984-05-15—Подача