Изобретение относится к вычислительной и информационно-измерительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации, в частности специализированных внешних устройств (СВУ) для исследования речи и диагностики сложных механизмов по их акустическим шумам с блок- мультиплексным каналом ввода-вывода ЕС ЭВМ.

Целью изобретения является повышение быстродействия устройства.

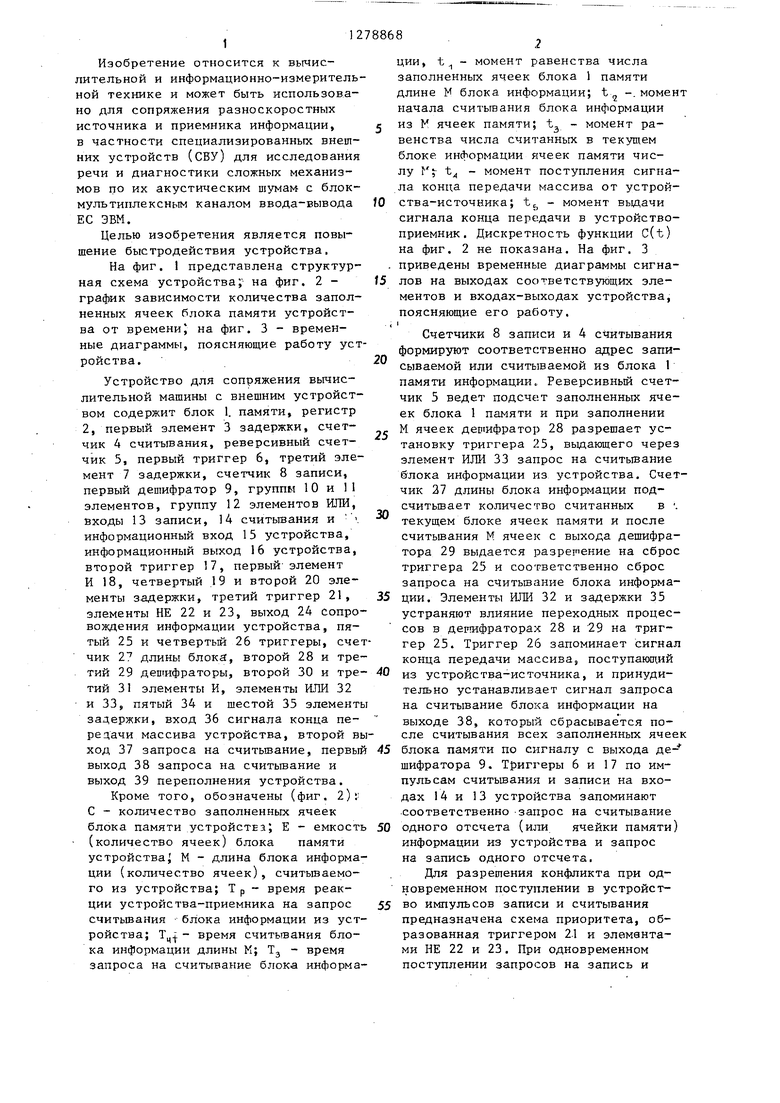

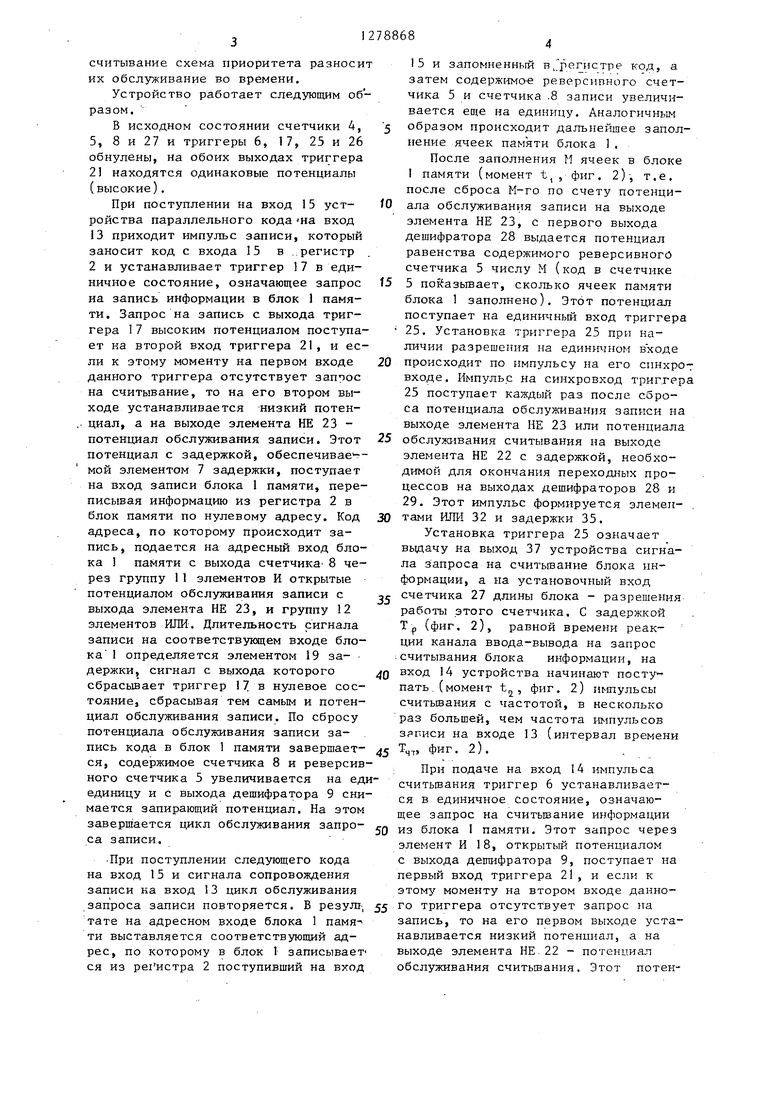

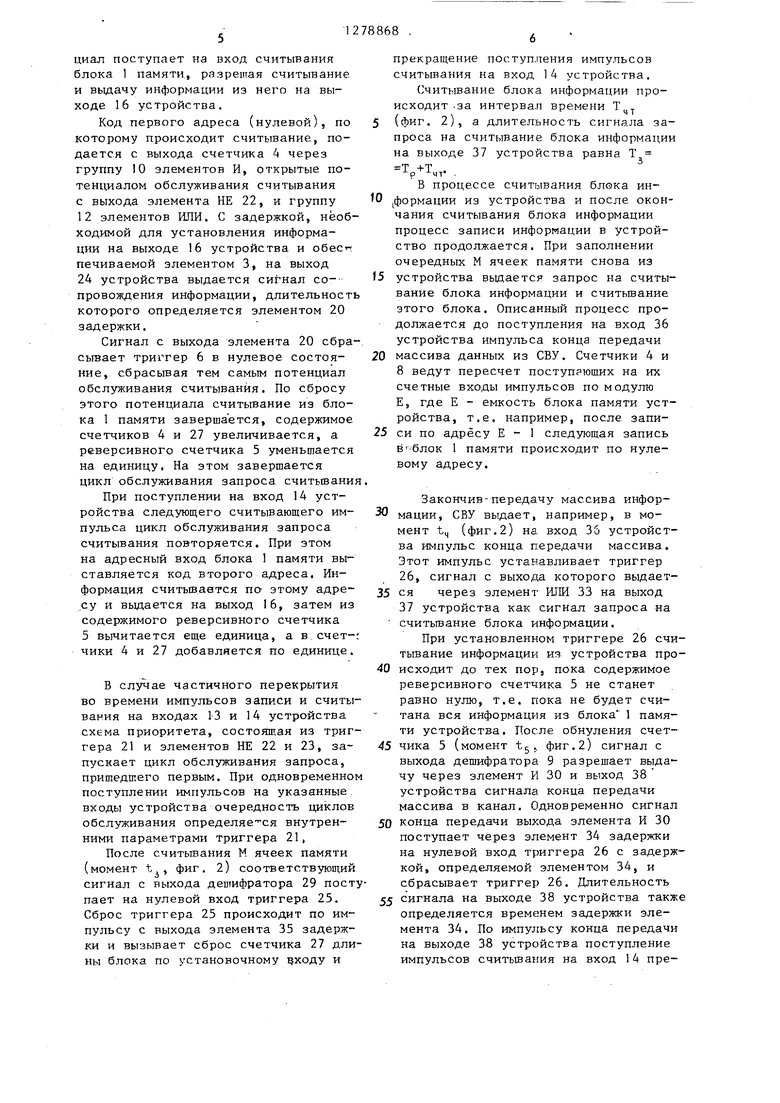

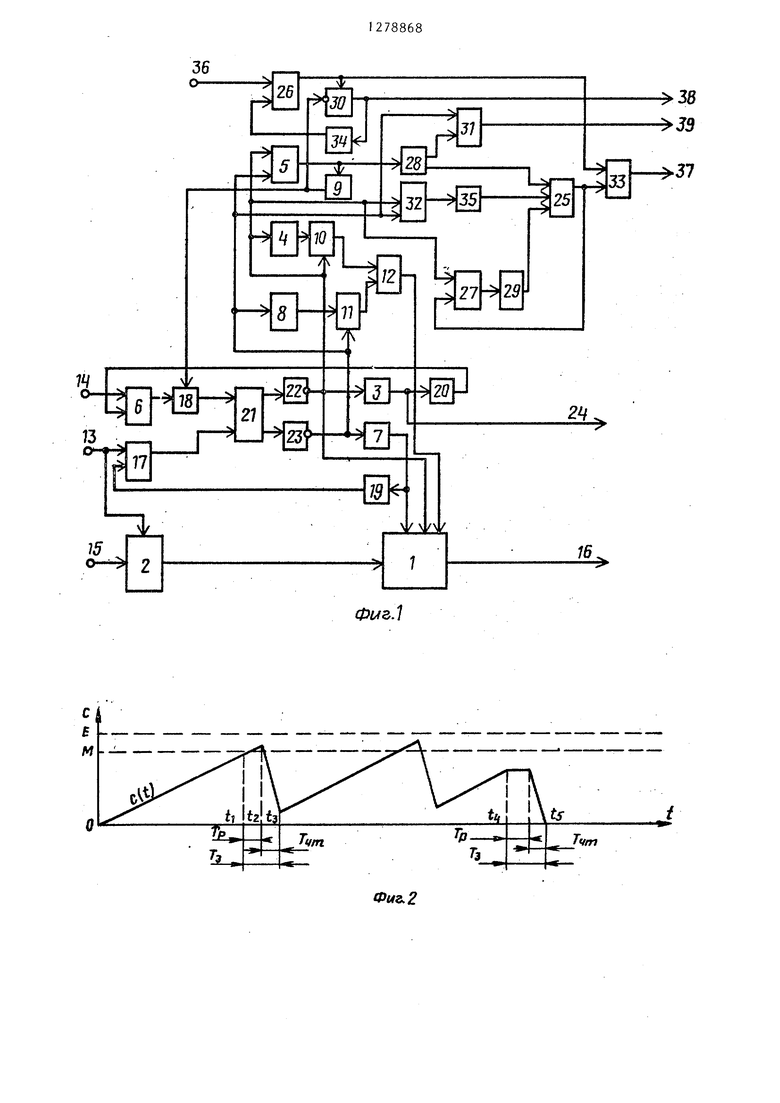

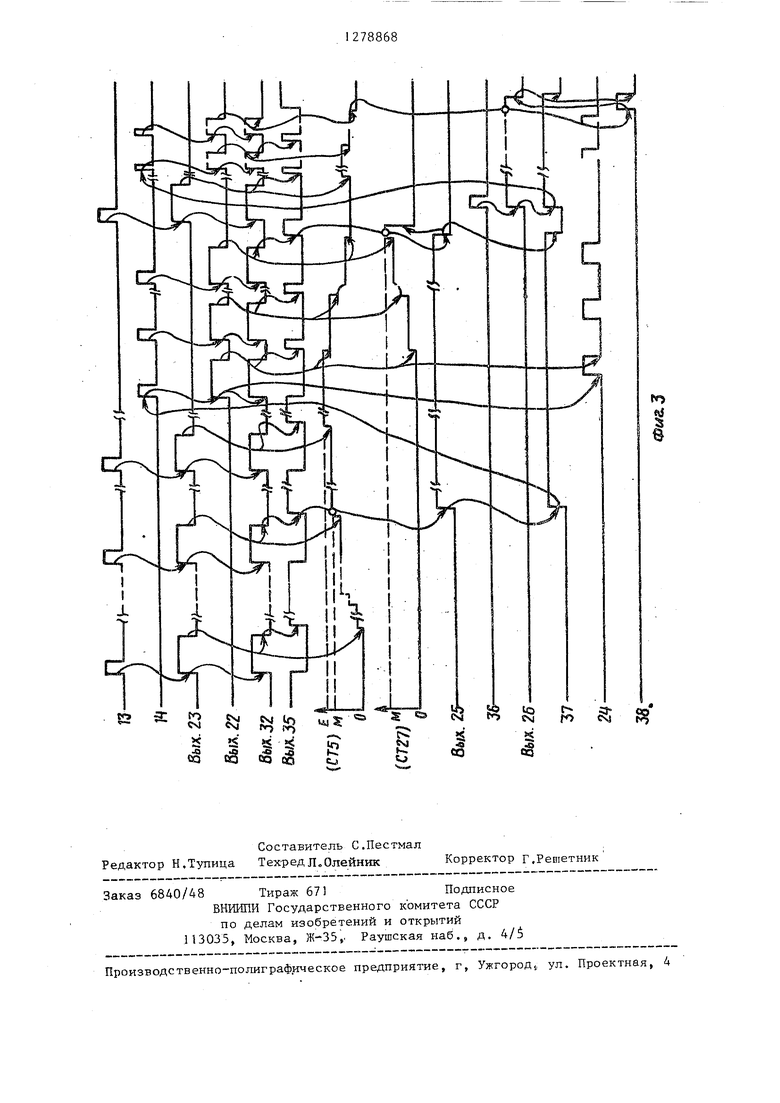

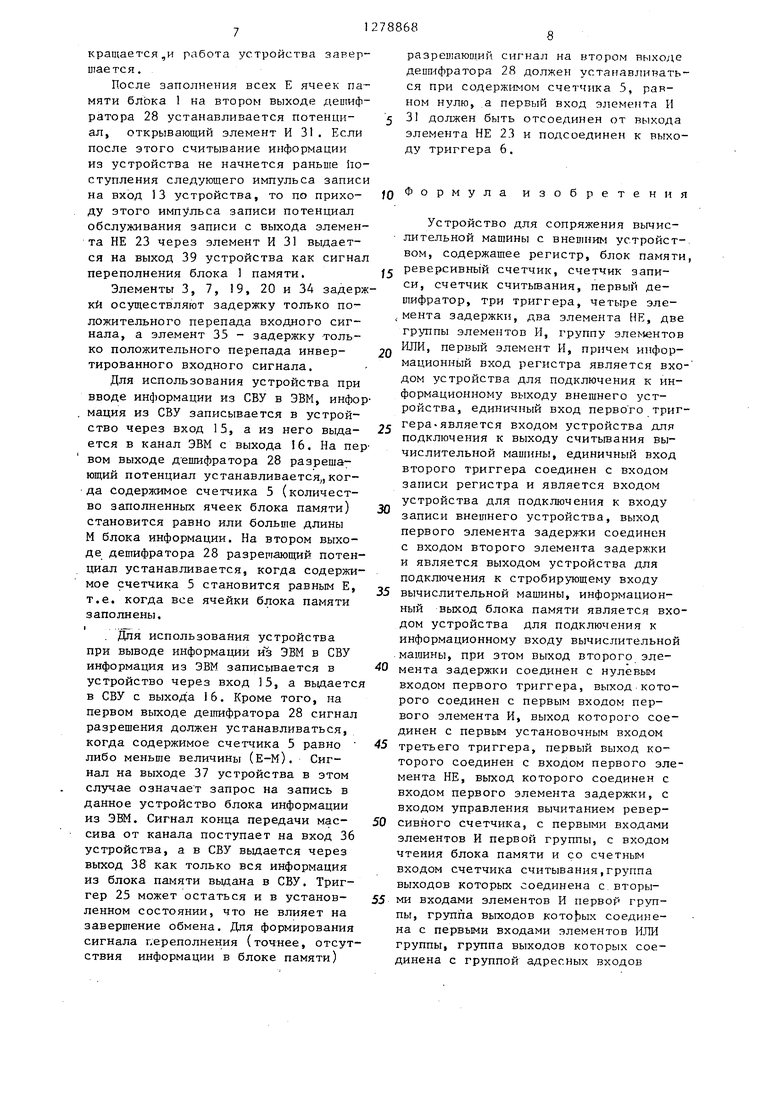

На фиг, 1 представлена структурная схема устройства; на фиг, 2 - график зависимости количества заполненных ячеек блока памяти устройства от времени) на фиг, 3 - временные диаграммы, поясняющие работу устройства.

Устройство для сопряжения вычислительной машины с внешним устройством содержит блок 1. памяти, регистр 2, первый элемент 3 задержки, счетчик 4 считывания, реверсивный счетчик 5, первый триггер 6, третий элемент 7 задержки, счетчик 8 записи, первый дешифратор 9, группы 10 и 11 элементов, группу 12 элементов ИЛИ, входы 13 записи, 14 считьшания и информационный вход 15 устройства, информационный выход 16 устройства, второй триггер 17, первый элемент И 18, четвертый 19 и второй 20 элементы задержки, третий триггер 21, элементы НЕ 22 и 23, выход 24 сопровождения информации устройства, пятый 25 и четвертый 26 триггеры, счетчик 27 длины блока, второй 28 и третий 29 деп ифраторы, второй 30 и тре- тий 31 элементы И, элементы ИЛИ 32 и 33, пятый 34 и шестой 35 элементы задержки, вход 36 сигнала конца пе- редачи массива устройства, второй вы

ход 37 запроса на считьшание, первый 45 блока памяти по сигналу с выхода девыход 38 запроса на считьгоание и выход 39 переполнения устройства,

Кроме того, обозначены (фиг, 2);: С - количество заполненных ячеек блока памяти устройства; Е - емкость (количество ячеек) блока памяти устройстваj М - длина блока информации (количество ячеек), считьшаемо- го из устройства; Т р - время реакции устройства-приемника на запрос считьюания блока информации из устройства; Тцф- время считьшания блока информации длины К; Т - время запроса на считывание блока информа

5

5 0

0

5

ции, t - момент равенства числа заполненных ячеек блока 1 памяти длине М блока информации; t -. момент начала считьгаания блока информации из V. ячеек памяти; t - момент равенства числа считанных в текущем блоке информации ячеек памяти числу f t - момент поступления сигнала конца передачи массива от устройства-источника; tj - момент выдачи сигнала конца передачи в устройство- приемник. Дискретность функции C(t) на фиг, 2 не показана. На фиг. 3 приведены временные диаграммы сигналов на выходах соответств ующих элементов и входах-выходах устройства, поясняющие его работу.

Счетчики 8 записи и 4 считывания формируют соответственно адрес записываемой или считываемой из блока 1 памяти информации. Реверсивный счетчик 5 ведет подсче Т заполненных ячеек блока 1 памяти и при заполнении М ячеек дешифратор 28 разрешает установку триггера 25, выдающего через элемент ИЛИ 33 запрос на считывание блока информации из устройства. Счетчик 27 длины блока информации под- считьтает количество считанных в . текущем блоке ячеек памяти и после считывания М ячеек с выхода дешифратора 29 выдается разрешение на сброс триггера 25 и соответственно сброс запроса на считьшание блока информации. Элементы ИЛИ 32 и задержки 35 устраняют влияние переходных процессов в дешифраторах 28 и 29 на триггер 25, Триггер 26 запоминает сигнал конца передачи массива, поступающий из устройства-источника, и принудительно устанавливает сигнал запроса на считывание блока информации на

выходе 38, который сбрасывается после считывания всех заполненных ячеек

шифратора 9. Триггеры 6 и 17 по импульсам считьшания и записи на входах 14 и 13 устройства запоминают .соответственно -запрос на считывание

одного отсчета (или ячейки памяти) информации из устройства и запрос на запись одного отсчета.

Для разрешения конфликта при одновременном поступлении в устройство импульсов записи и считьшания предназначена схема приоритета, образованная триггером 2.1 и эламанта- ми НЕ 22 и 23, При одновременном поступлении запросов на запись и

считывание схема приоритета разносит их обслуживание во времени.

Устройство работает следующим образом.

В исходном состоянии счетчики 4, 5 5, 8 и 27 и триггеры 6, 17, 25 и 26 обнулены, на обоих выходах триггера 21 находятся одинаковые потенциалы (высокие).

При поступлении на вход 15 уст- fO ройства параллельного кода на вход 13 приходит импульс записи, который заносит код с входа 15 в .: регистр . 2 и устанавливает триггер 17 в единичное состояние, означающее запрос 15 на запись информации в блок 1 памяти. Запрос на запись с выхода триггера 17 высоким потенциалом поступает на второй вход триггера 21, и если к этому моменту на первом входе 20 данного триггера отсутствует запрос на считывание, то на его втором выходе устанавливается низкий потен- циал, а на выходе элемента НЕ 23 - потенциал обслуживания записи. Этот 25 потенциал с задержкой, обеспечивае - - мой элементом 7 задержки, поступает на вход записи блока 1 памяти, переписывая информацию из регистра 2 в блок памяти по нулевому адресу. Код 30 адреса, по которому происходит запись, подается на адресный вход блока 1 памяти с выхода счетчикЭ 8 через группу 11 элементов И открытые потенциалом обслуживания записи с выхода элемента НЕ 23, и группу 12 элементов ИЛИ, Длительность сигнала записи на соответствующем входе блока определяется элементом 19 задержки, сигнал с выхода которого сбрасьшает триггер 17. в нулевое состояние, сбрасывая тем самым и потенциал обслуживания записи. По сбросу потенциала обслуживания записи запись кода в блок 1 памяти завершает- 5 ся, содержимое счетчика 8 и реверсивного счетчика 5 увеличивается на еди- единицу и с выхода дешифратора 9 снимается запирающий потенциал. На этом завершается цикл обслуживания запроса записи.

При поступлении следующего кода на вход 15 и сигнала сопровождения записи ка вход 13 цикл обслуживания запроса записи повторяется. В резул, 55 тате на адресном входе блока 1 памя ти выставляется соответствующий адрес, по которому в блок 1 записывает ся из ре1 истра 2 поступивший на вход

35

40

50

в л с сч вх п сч р зя ч

сч ся ще из эл с пе эт го за на вы об

15 и запомненный в,.регистре код, а затем содержимо-е реверсипного счетчика 5 и счетчика .8 записи увеличивается еще на единицу. Аналогичным образом происходит дальнейшее заполнение ячеек памяти блока 1.

После заполнения И ячеек в блоке

5

O 5 0 5 0 5

5

5

0

0

1 памяти (момент t,, фиг. 2), т.е. после сброса М-го по счету потенциала обслуживания записи на выходе элемента НЕ 23, с первого выхода дешифратора 28 выдается потенциал равенства содержимого реверсивного счетчика 5 числу М (код в счетчике 5 пойазьгоает, сколько ячеек памяти блока I заполнено). Этот потенциал поступает на единргчный вход триггера 25. Установка триггера 25 при нгг- личии разрешения на единжиюм входе происходит по импульсу на его спнхрот входе. Импульс на синхровход триг. 25 поступает каждый раз после сброса потенциала обслуживания записи на выходе элемента НЕ 23 или потенциала обслуживания считывания на выходе элемента НЕ 22 с задержкой, необходимой для окончания переход1«1х процессов на выходах дешифраторов 28 и 29. Этот импульс формируется элементами ИЛИ 32 и задержки 35.

Установка триггера 25 означает выдачу на выход 37 устройства сигнала запроса на считьюание блока информации, а на установочный вход счетчика 27 длины блока - разрешения работы этого счетчика, С задержкой Тр (фиг, 2), равной времени реакции канала ввода-вывода на запрос считывания блока информации, на вход 14 устройства начинают посту пать.(момент t, , фиг. 2) импульсы считьшання с частотой, в несколько раз большей, чем частота импульсов зяписи на входе 13 (интервал времени чт. фиг. 2)..

При подаче на вход 14 импульса считьшания триггер 6 устанавливается в единичное состояние, означающее запрос на считьшание ир;формации из блока I памяти. Этот запрос через элемент И 18, открытый потенциалом с выхода дешифратора 9, поступает на первый вход триггера 2, и если к этому моменту на втором входе данного триггера отсутствует запрос на запись, то на его первом выходе устанавливается низкий потенпнал, а на выходе элемента НЕ.22 - потенциал обслуживания счнтьшання. Этот потенциал поступает на вход считывания блока 1 памяти, разрешая считывание и выдачу информации из него на выходе 16 устройства.

Код первого адреса (нулевой), по которому происходит считывание, подается с выхода счетчика 4 через группу 10 элементов И, открытые потенциалом обслуживания считывания с выхода элемента НЕ 22, и группу 12 элементов ИЛИ. С задержкой, необходимой для установления информации на выходе 16 устройства и обесп печиваемой элементом 3, на выход 24 устройства выдается сигнал со-- провождения информации, длительност которого определяется элементом 20 задержки.

Сигнал с выхода элемента 20 сбра сьгеает триггер 6 в нулевое состояние, сбрасывая тем самым потенциал обслуживания считывания. По сбросу этого потенциала считывание из блока 1 памяти завершается, содержимое счетчиков 4 и 27 увеличивается, а реверсивного счетчика 5 уменьшается на единицу, На этом завершается цикл обслуживания запроса считьгоани

При поступлении на вход 14 устройства следующего считывающего импульса цикл обслуживания запроса считывания повторяется. При этом на адресный вход блока 1 памяти выставляется код второго адреса. Информация считьшавтся па этому адре- .су и выдается на выход 16, затем из содержимого реверсивного счетчика 5 вычитается еще единица, а в счетчики 4 и 27 добавляется по единице.

В случае частичного перекрытия во времени импульсов записи и считывания на входах 13 и 14 устройства схема приоритета, состоящая из триггера 21 и элементов НЕ 22 и 23, запускает цикл обслуживания запроса, пришедшего первым. При одновременно поступлении импульсов на указанные входы устройства очередность циклов обслуживания определяе- ся внутренними параметрами триггера 21,

После считывания М ячеек памяти (момент t , фиг. 2) соответствующий сигнал с выхода дешифратора 29 постпает на нулевой вход триггера 25. Сброс триггера 25 происходит по импульсу с выхода элемента 35 задержки и вызывает сброс счетчика 27 длины блока по установочному эходу и

прекращение поступления импульсов считывания на вход 14 устройства.

Считывание блока информации происходит .за интервал времени Т

(фиг. 2), а длительность сигнала запроса на считывание блока информации на выходе 37 устройства равна Т ,,. ,

В процессе считывания блока ин(формации из устройства и после окончания считывания блока информации процесс записи информации в устройство продолжается. При заполнении очередных М ячеек памяти снова из

устройства вьщается запрос на считывание блока информации и считьгоание этого блока. Описанный процесс продолжается до поступления на вход 36 устройства импульса конца передачи

массива данных из СВУ. Счетчики 4 и 8 ведут пересчет поступающих на их счетные входы импульсов по модулю Е, где Е - емкость блока памяти устройства, т.е. например, после записи по адресу Е - 1 следующая запись 1 памяти происходит по нулевому адресу.

Закончив-передачу массива информации, СВУ выдает, например, в момент t (фиг.2) на вход 3S устройства импульс конца передачи массива. Этот импульс устанавливает триггер 26, сигнал с выхода которого выдается через элемент ИЛИ 33 на выход

37 устройства как сигнал запроса на считьгоание блока информации.

При установленном триггере 26 считывание информации из устройства происходит до тех пор, пока содержимое реверсивного счетчика 5 не станет равно нулю, т.е. пока не будет считана вся информация из блока 1 памяти устройства. После обнуления счетчика 5 (момент t ., фиг. 2) сигнал с выхода дешифратора 9 разрешает выдачу через элемент И 30 и выход 38 устройства сигнала конца передачи массива в канал. Одновременно сигнал

конца передачи выхода элемента И 30 поступает через эхшмент 34 задержки на нулевой вход триггера 26 с задержкой, определяемой элементом 34, и сбрасывает триггер 26. Длительность

сигнала на выходе 38 устройства также определяется временем задержки элемента 34. По импульсу конца передачи на выходе 38 устройства поступление импульсов считьюания на вход I4 прекращается,и работа устройства завершается.

После заполнения всех Е ячеек памяти блока 1 на втором выходе дешифратора 28 устанавливается потенциал, открывающий элемент И 31. Если после этого считывание информации из устройства не начнется раньте lio- ступления следующего импульса записи на вход 13 устройства, то по приходу этого импульса записи потенциал обслуживания записи с выхода элемента НЕ 23 через элемент И 31 выдается на выход 39 устройства как сигнал переполнения блока 1 памяти.

Элементы 3, 7, 19, 20 и 34 задержки осуществляют задержку только положительного перепада входного сигнала, а элемент 35 - задержку только положительного перепада инвертированного входного сигнала.

Для использования устройства при вводе информации из СВУ в ЭВМ, информация из СВУ записывается в устройство через вход 15, а из него выдается в канал ЭВМ с выхода 16. На первом выходе дешифратора 28 разрешающий потенциал ycтaнaвливaeтcя, когда содерлсимое счетчика 5 (количество заполненных ячеек блока памяти) становится равно или больше длины М блока информации. На втором выходе дешифратора 28 разрешающий потенциал устанавливается, когда содержимое счетчика 5 становится равным Е, т.е. когда все ячейки блока памяти заполнены.

. Для использования устройства при выводе информации и з ЭВМ в СВУ информация из ЭВМ записывается в устройство через вход 15, а выдается в СВУ с выхода 16. Кроме того, на первом выходе дешифратора 28 сигнал разрешения должен устанавливаться, когда содержимое счетчика 5 равно либо меньше величины (В-М). Сигнал на выходе 37 устройства в этом случае означает запрос на запись в данное устройство блока информации из ЭВМ. Сигнал конца передачи массива от канала поступает на вход 36 устройства, а в СВУ выдается через выход 38 как только вся информация из блока памяти выдана в СВУ. Триггер 25 может остаться и в установленном состоянии, что не влияет на завершение обмена. Для формирования сигнала переполнения (точнее, отсутствия информации в блоке памяти)

разрешаюпшн сигнал на втором выходе дешифратора 28 должен устанавливаться при содержимом счетчика 5, равном нулю, ,а первый вход элемента И 31 должен быть отсоединен от выхода элемента НЕ 23 и подсоединен к выходу триггера 6.

Формула изобретения

Устройство для сопряжения вычис- лительной машины с внешним устройством, содержащее регистр, блок памяти, реверсивнь й счетчик, счетчик записи, счетчик считывания, первый дешифратор, три триггера, четыре эле- мента задержки, два элемента НЕ, две группы элементов И, группу элементов ИЛИ, первый элемент И, причем информационный вход регистра является вхо- дом устройства для подключения к информационному выходу внешнего устройства, единичный вход первого триггера-является входом устройства для подключения к выходу считьгоания вычислительной машины, единичный вход второго триггера соединен с входом записи регистра и является входом устройства для подключения к входу записи внешнего устройства, выход первого элемента задер 1 и соединен с входом второго элемента задержки и является выходом устройства для подключения к стробирующему входу

вычислительной машины, информационный выход блока памяти является входом устройства для подключения к информационному входу вычислительной -машины, при этом выход второго элемента задержки соединен с нулевым входом первого триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым установочным входом

третьего триггера, первый выход которого соединен с входом первого элемента НЕ, выход которого соединен с входом первого элемента задержки, с входом управления вычитанием реверсивного счетчика, с первыми входами элементов И первой группы, с входом чтения блока памяти и со счетным входом счетчика считывания,группа выходов которьк соединена с вторыми входами элементов И первой группы, группа выходов которых соединена с первыми входами элементов ИЛИ группы, группа выходов которых соединена с группой адресных входов

блока памяти, вход записи которого соединен с вькодом третьего элемента задержки и с входом четвертого N элемента задержки, выход которого соединен с нулевым входом второго Триггера, выход которого соединен с вторьм установочным входом третьего триггера, второй выход которого соединен с входом второго элемента НЕ, выход которого соединен с входом третьего элемента задержки, с входом управления сложением реверсивного счетчика, с первыми входами элементов И второй группы и со счетным входом счетчика записи, группа выходов которого соединена с вторыми входами элементов И второй группы,группа выходов которых соединена с вторыми входами элементов ИЛИ группы, выход реверсивного счетчика соединен с входом первого депшфратора,выход которого соединен с вторым входом первого элемента И, информационный выход регистра соединен с информационным входом блока памяти, отличающееся тем, что, с целью увеличения быстродействия, в Него введены счетчик длины блока, два дешифратора, два триггера, два элемента задержки, два элемента И, два элемента ИЛИ, причем единичный вход четвертого триггера является входам устройства подключения к выходу сигнала конца передачи массива внешнего устройства, выход второго элемента И соединен с входом пятого элемента задержки и является выходом устройства для подключения к первому входузапроса на считьшание вычислительной машины, выход первого элемента ИЛИ является выходом устройства для подключения к второму

входу запроса на считывание вычислительной машины, выход третьего элемента И является выходом устройства для подключения к входу запроса на прерывание вычислительной машины,

при этом выход пятого --элемента задержки соединен с нулевым входом четвертого триггера, выход которого соединен с первым входом первого элемента ИЛИ и с первым входом второго элемента И, второй вход которого соединен с выходом первого дешифратора, вход которого соединен с входом второго дешифратора, первьш выход которого соединен с единичным

входом пятосо триггера, выход которого соединен с вторым входом первого элемента ИЛИ и с нулевым входом счетчика длины блока,выход которого соединен с входом третьего дешифратора, выход .которого соединен с нулевым входом пятого триггера, синхро- вход которого соединен с выходом шестого элемента задержки, вход кото- рого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом второго элемента НЕ и с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго дешифратора, второй в.ход второго элемента ИЛИ соединен со счетным входом счетчика длины блока и с выводом первого элемента НЕ,

33

J5 57

2it

16

.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения разноскоростных вычислительных устройств | 1984 |

|

SU1183975A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для измерения плоских углов | 1988 |

|

SU1567885A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285474A1 |

| Устройство для измерения частот появления групп команд | 1986 |

|

SU1405062A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1383375A1 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1987 |

|

SU1444796A1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| Устройство для определения частот обращения к программам | 1985 |

|

SU1357963A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения специализированных внешних устройств (СВУ) с блок-мультиплексным каналом ввода- вывода ЭВМ. Целью изобретения является повьшение быстродействия. Устройство содержит регистр, блок памяти, счетчики записи и считывания, реверсивный счетчик, счетчик длины блока, пять триггеров, шесть элементов задержки, два элемента НЕ, три элемента И, два элемента ИЛИ, две группь элементов И, группу эле-- ментов ИЛИ, три дешифратора. 3 ил. с S (Я с ю ч1 00 00 а 00

Фиг. 2

I I

I.

ffl

S2

Ю

CM

Составитель С.Пестмал Редактор Н,Тупица Тех-редЛ.Олейник Корректор г.Решетник

Заказ 6840/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий .113035, Москва, Ж-35,. Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород ул. Проектная, 4

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1984 |

|

SU1183975A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-26—Подача