4 1

о:

Изобретение относится к области вычислительной техники и может быть использовано в многомашинных и многопроцессорных вычислительных системах с магистральной структурой.

Цель изобретения - расширение функциональных возможностей устройства.

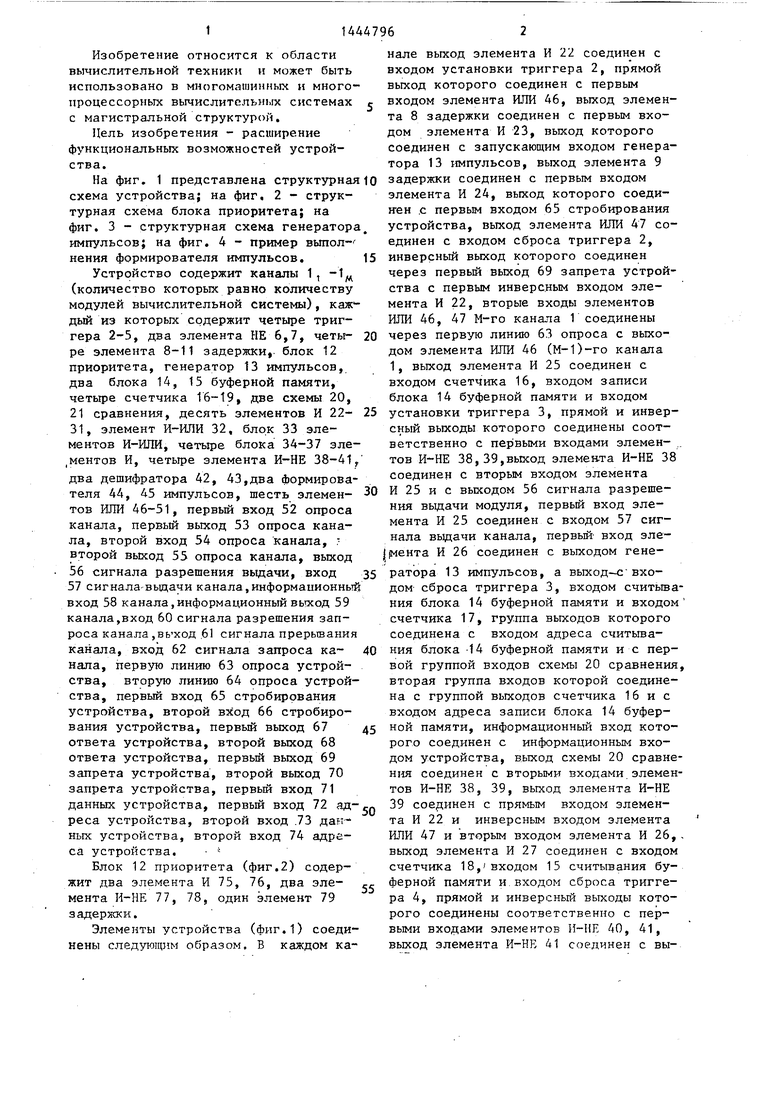

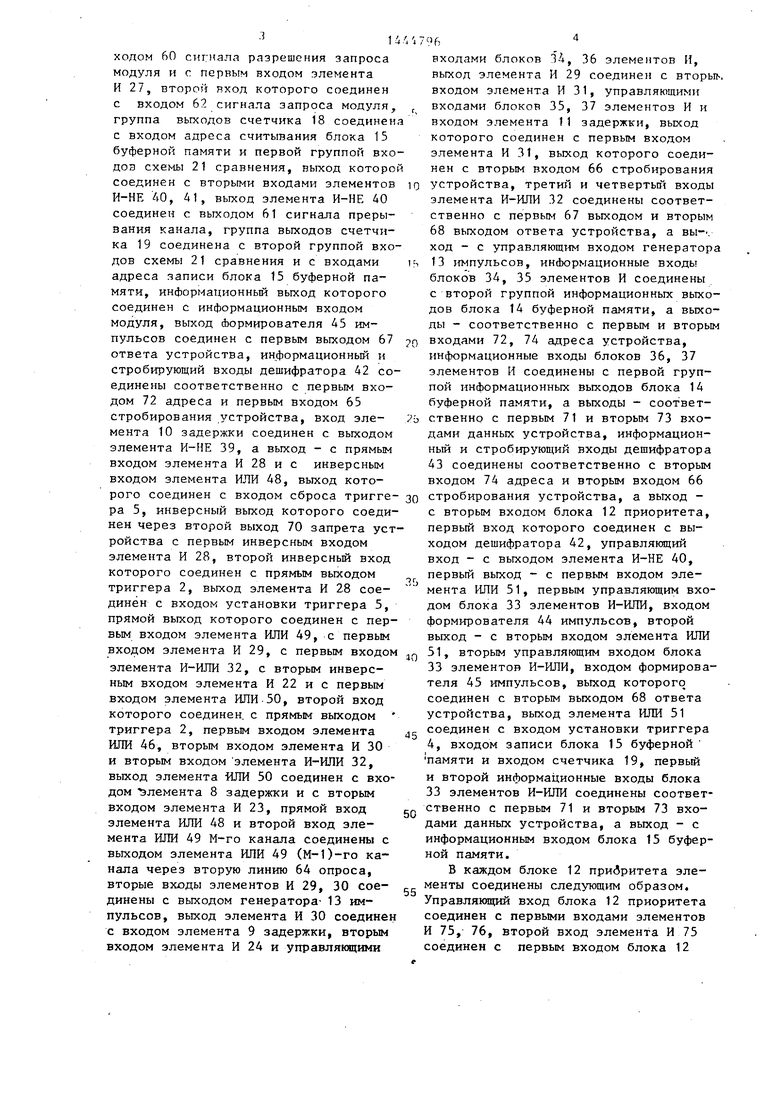

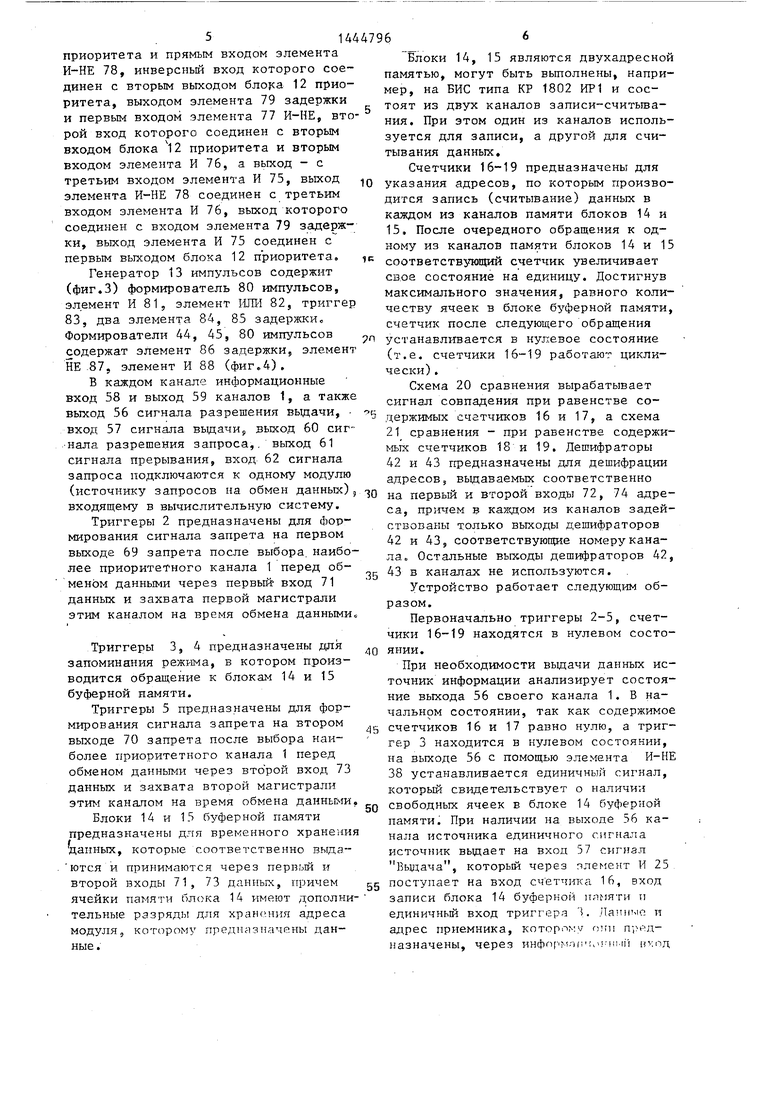

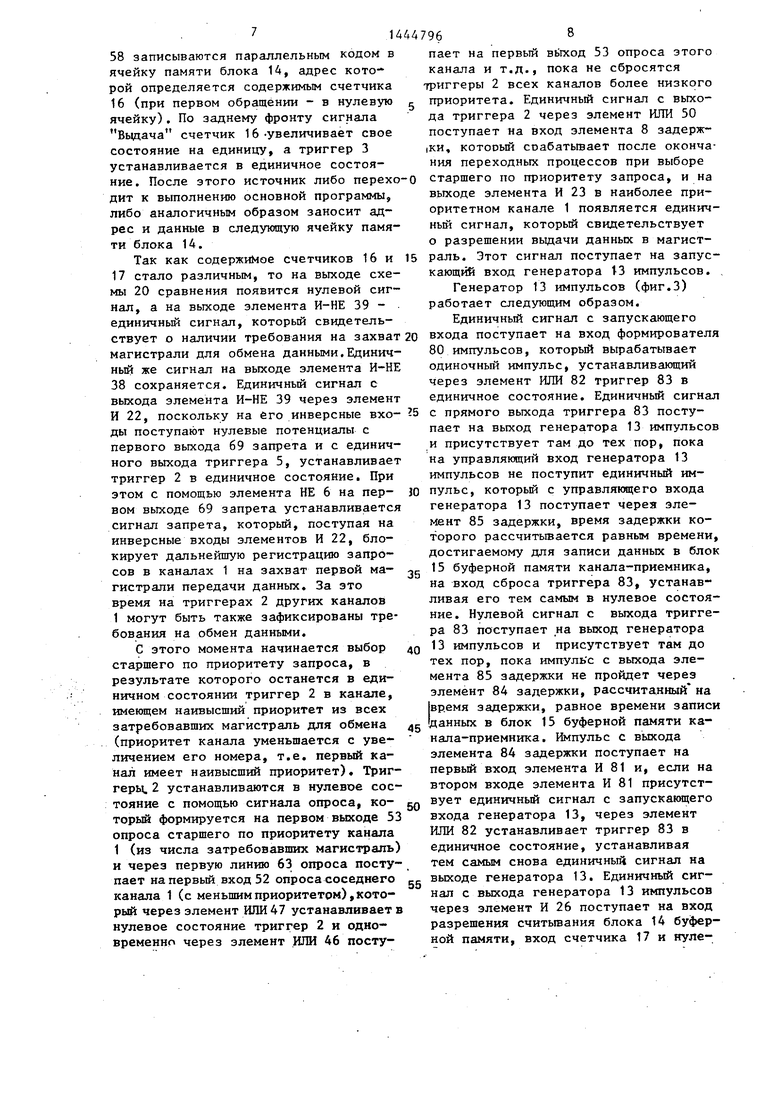

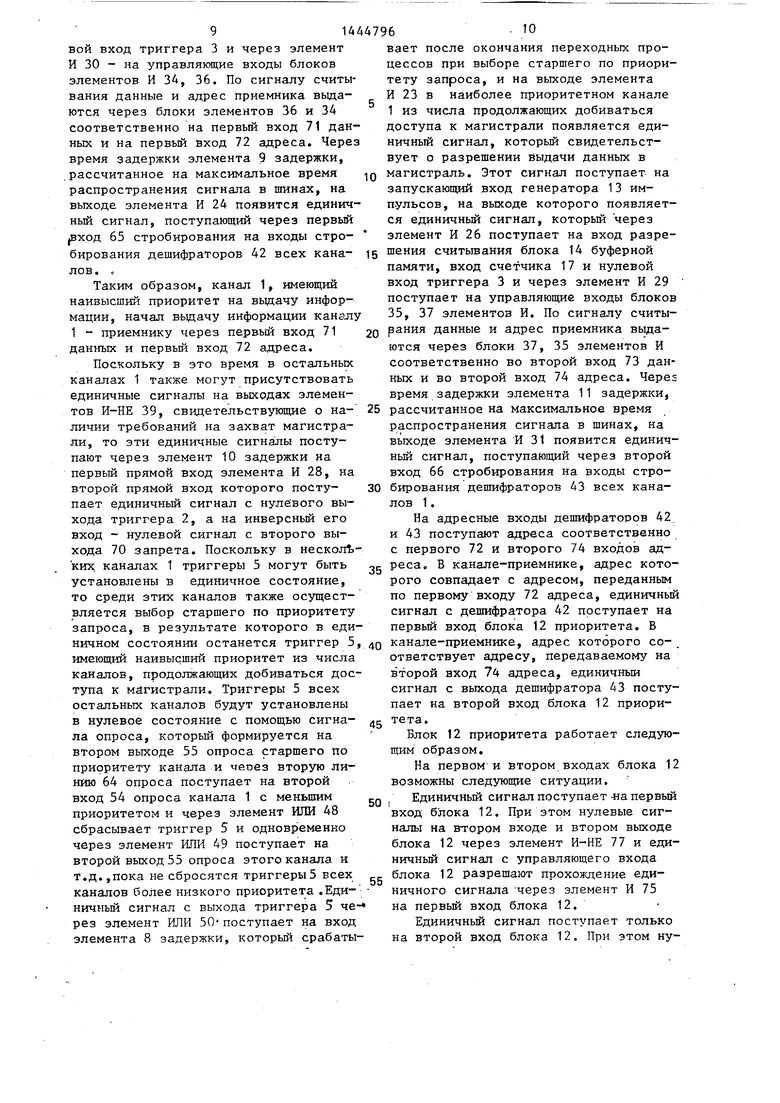

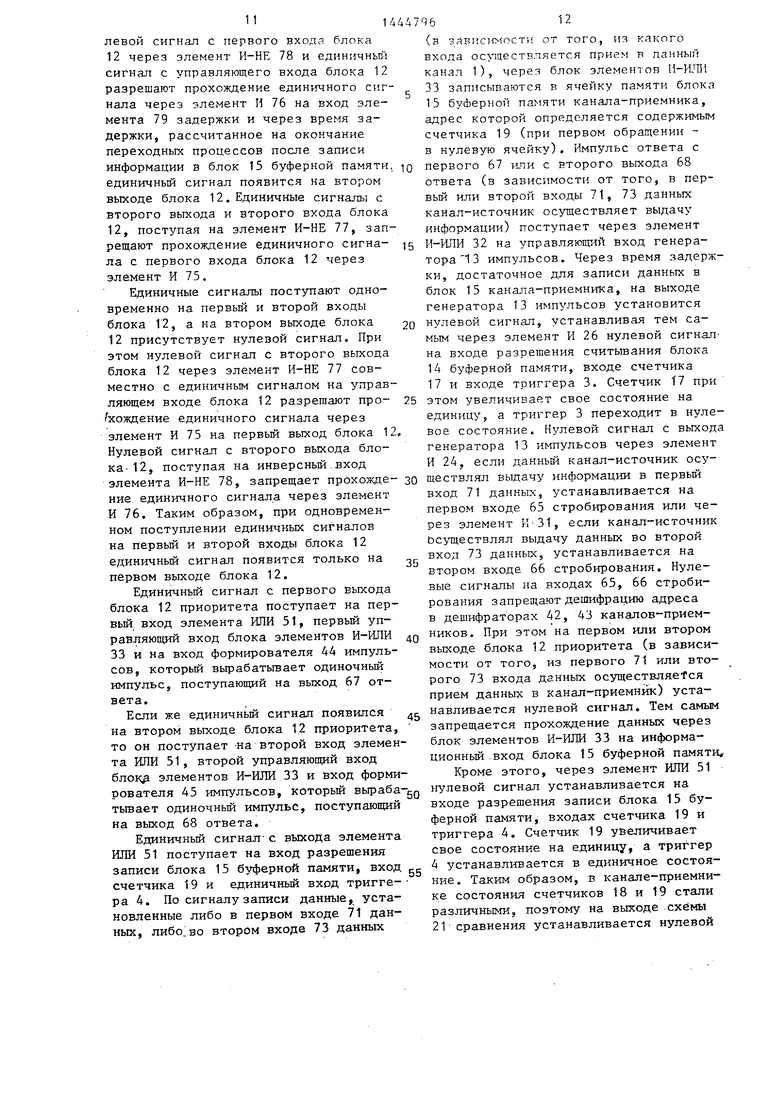

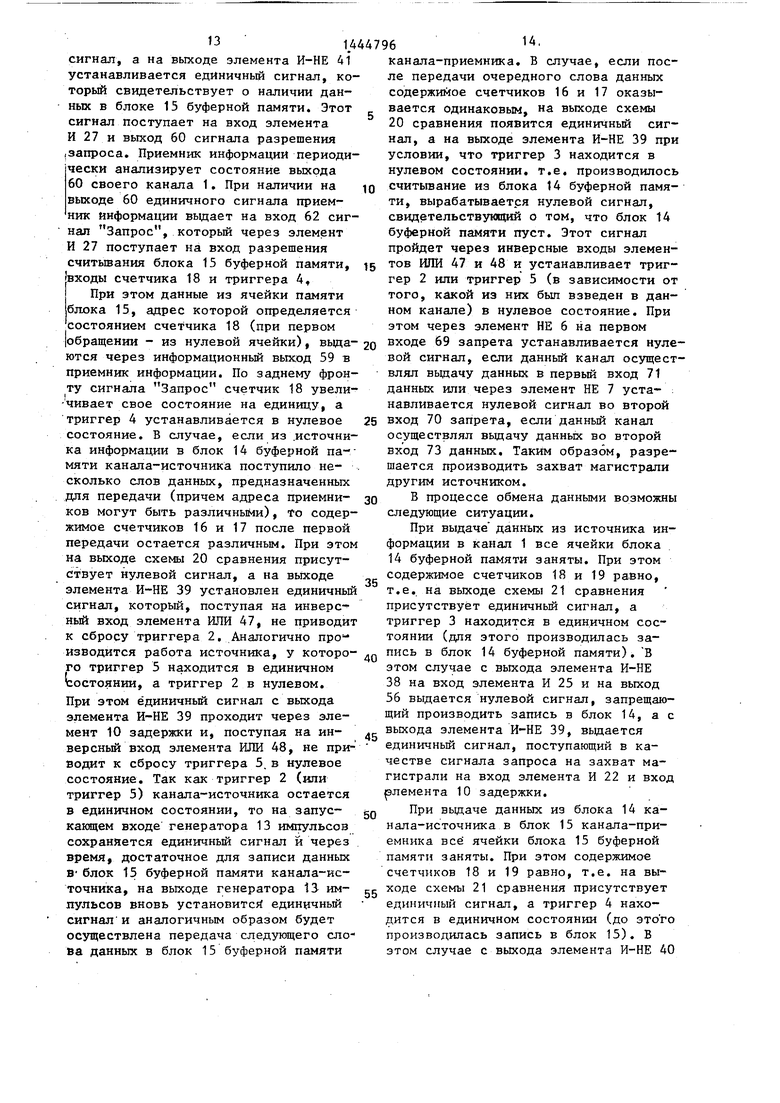

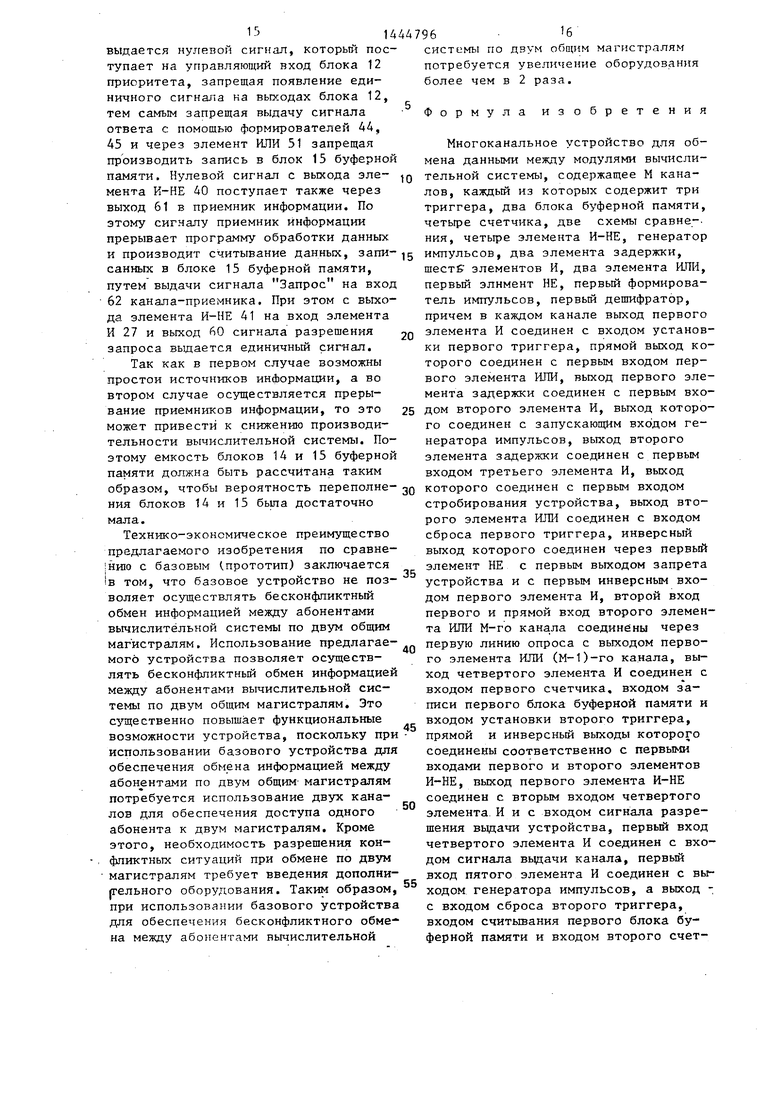

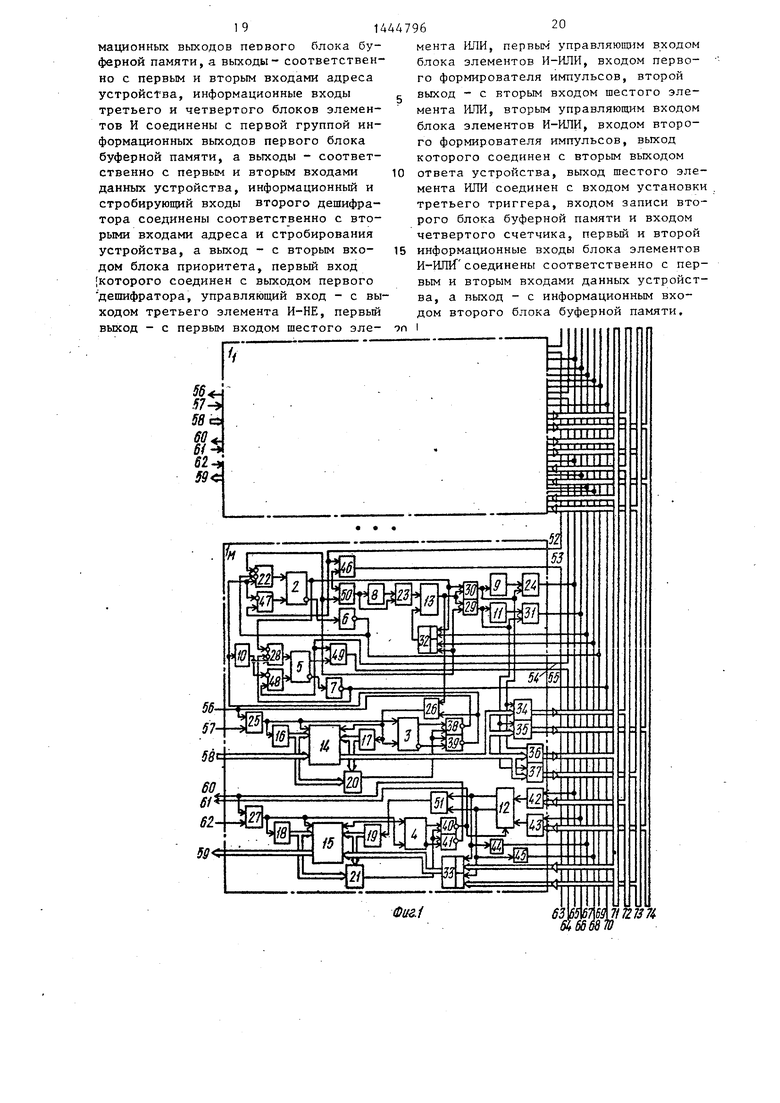

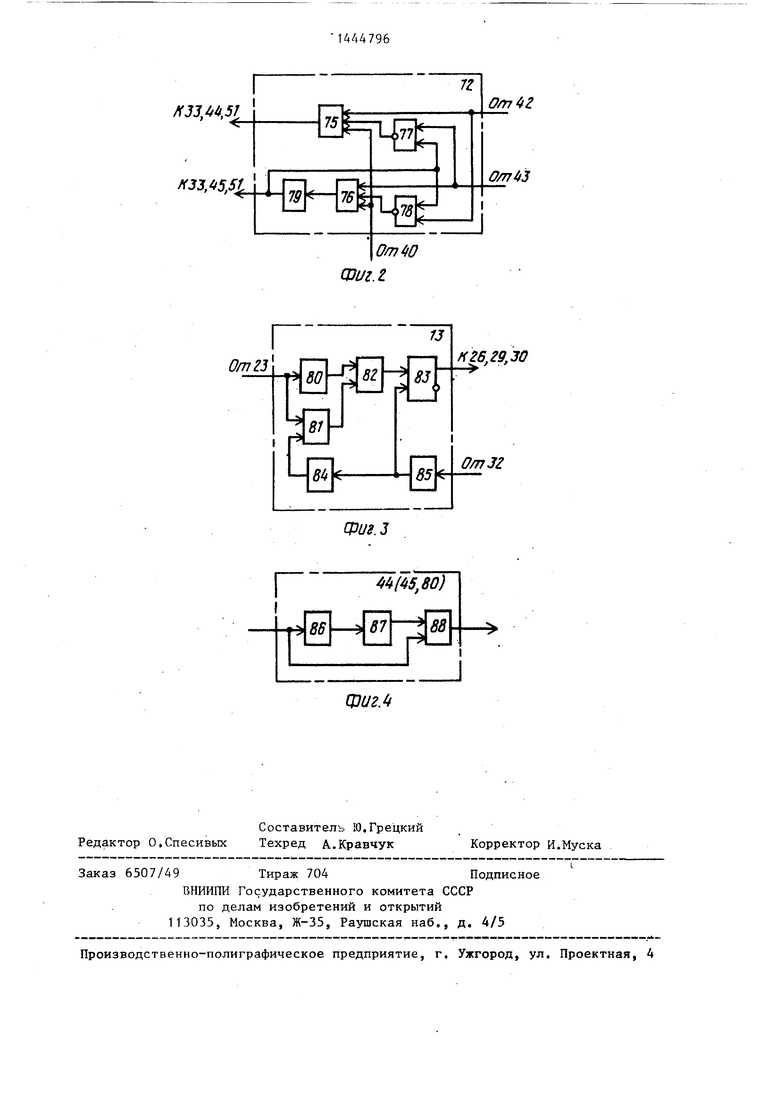

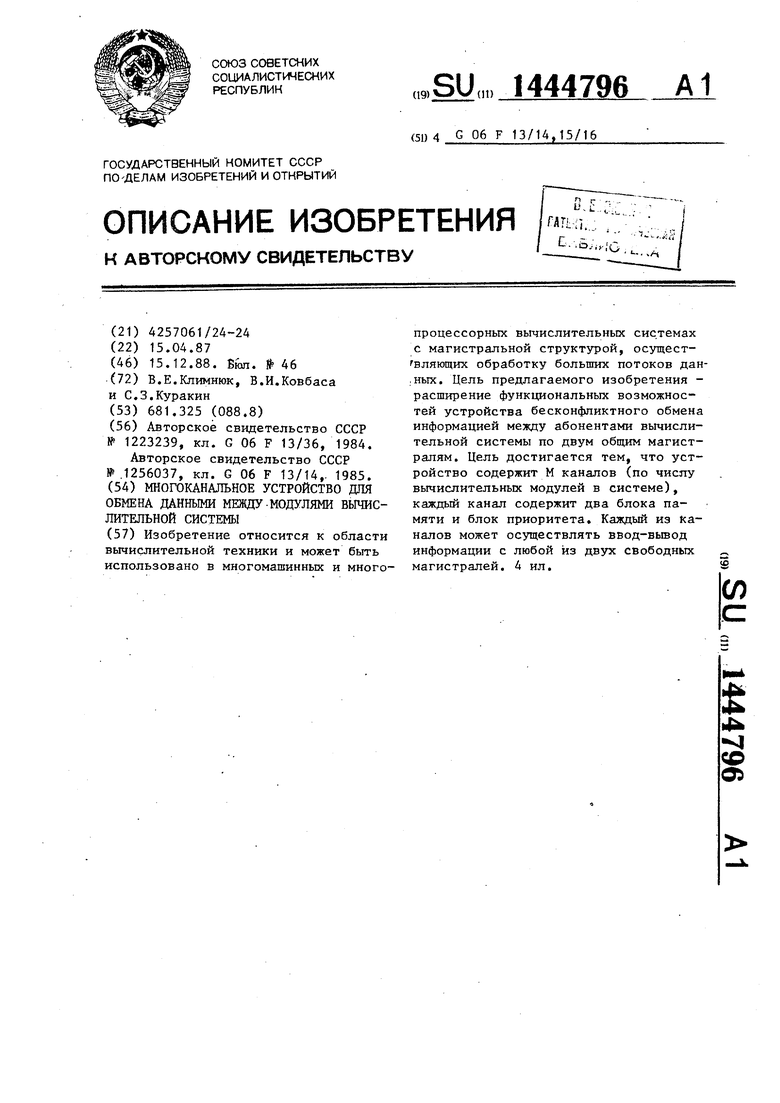

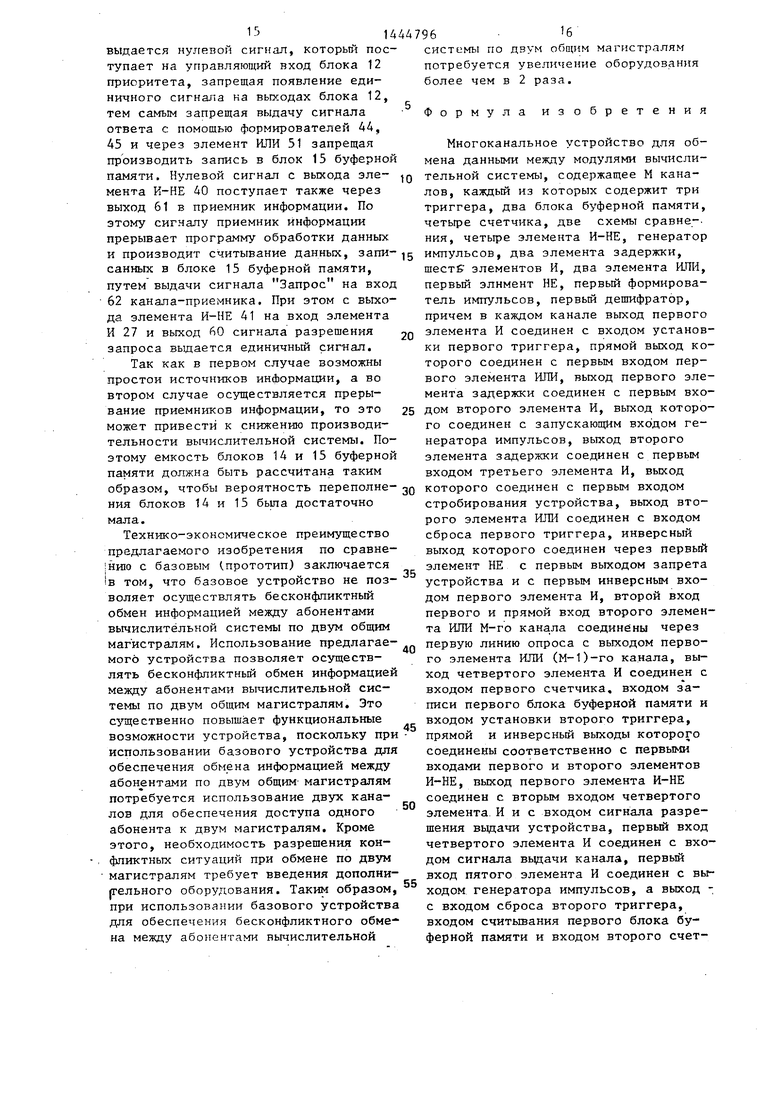

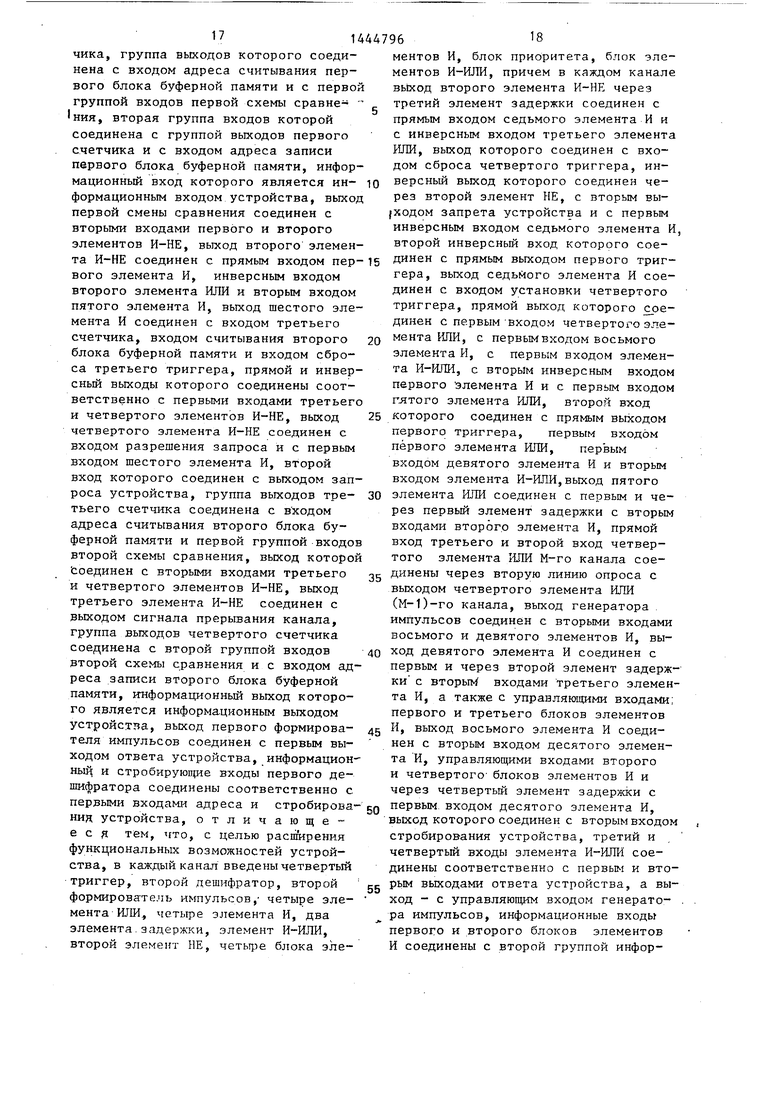

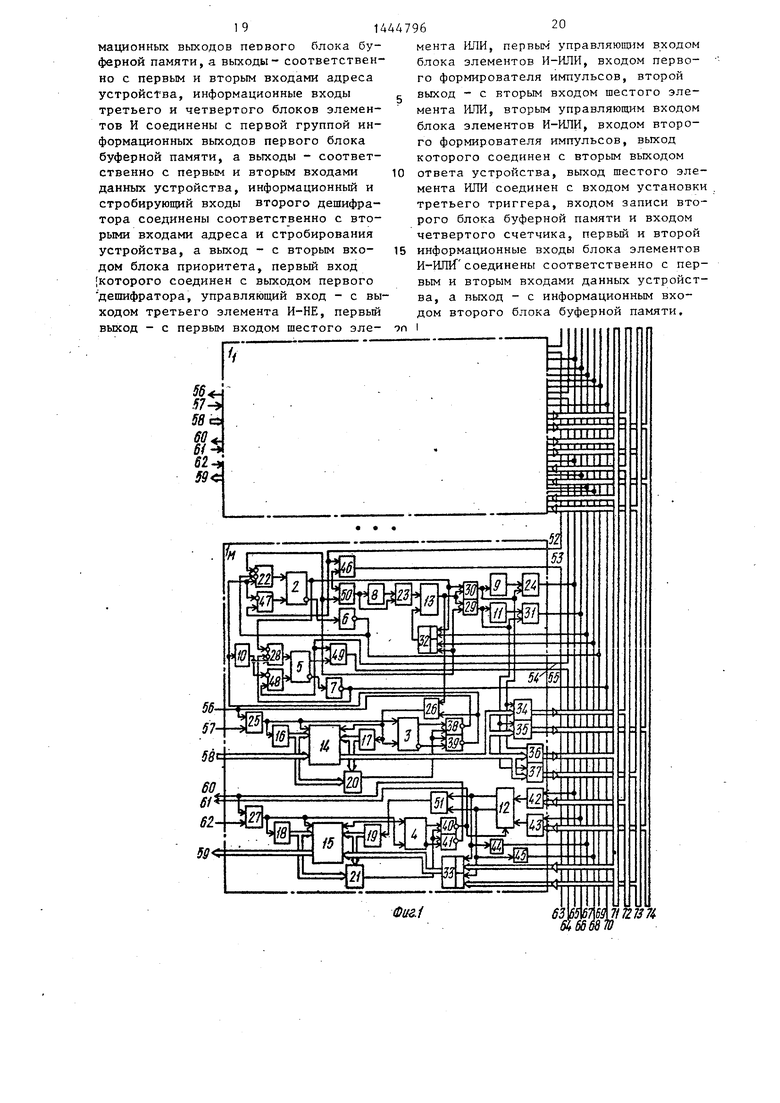

На фиг. 1 представлена структурная схема устройства; на фиг, 2 - структурная схема блока приоритета; на фиг. 3 - структурная схема генератора импульсов; на фиг. 4 - пример выпол- нения формирователя импульсов.

Устройство содержит каналы 1, -1 (количество которых равно количеству модулей вычислительной системы), дый из которых содержит четыре триггера 2-5, два элемента НЕ 6,7, четы- ре элемента 8-11 задержки,, блок 12 приоритета, генератор 13 импульсов, два блока 14, 15 буферной памяти, четыре счетчика 16-19, две схемы 20, 21 сравнения, десять элементов И 22- 31, элемент И-ИЛИ 32, блок 33 элементов , четьфе блока 34-37 эле- ,ментов И, четыре элемента И-НЕ 38-41,

два дешифратора 42, 43,два формирователя 44, 45 импульсов, шесть элемен- тов ИЛИ 46-51, первый вход 52 опроса канала, первый выход 53 опроса канала, второй вход 54 опроса канала, . второй выход 55 опроса канала, вьпсод

56сигнала разрешения вьщачи, вход

57сигнала-вьщачи канала,информапионньтй вход 58 канала,информационный выход 59 канала,вход 60 сигнала разрешения запроса канала ,выход ,61 сигнала прерьшания канала, вход 62 сигнала запроса ка- нала, первую линию 63 опроса устройства, вторую линию 64 опроса устройства, первый вход 65 стробирования устройства, второй вход 66 стробирования устройства, первьй выход 67 ответа устройства, второй выход 68 ответа устройства, первый выход 69 запрета устройства, второй выход 70 запрета устройства, первьш вход 71 данных устройства, первый вход 72 адреса устройства, второй вход .73 дан-- ньпс устройства, второй вход 74 адреса устройства.

Блок 12 приоритета (фиг.2) содержит два элемента И 75, 76, два эле- мента И-НЕ 77, 78, один элемент 79 задержки.

Элементы устройства (фиг.1) соединены следующим образом. В каждом канале выход элемента И 22 соединен с входом установки триггера 2, прямой выход которого соединен с первым входом элемента ИЛИ 46, выход элемента 8 задержки соединен с первым входом элемента И 23, выход которого соединен с запускающим входом генератора 13 импульсов, выход элемента 9 задержки соединен с первьм входом элемента И 24, выход которого соеди- н-ен .с первым входом 65 стробирования устройства, выход элемента ИЛИ 47 соединен с входом сброса триггера 2, инверсный выход которого соединен через первьй выход 69 запрета устройства с первым инверсным входом элемента И 22, вторые входы элементов ИЛИ 46, 47 М-го канала 1 соединены через первую линию 63 опроса с выходом элемента ИЛИ 46 (М-1)-го канала 1, выход элемента И 25 соединен с входом счетчика 16, входом записи блока 14 буферной памяти и входом установки триггера 3, прямой и инверсный выходы которого соединены соответственно с первыми входами элемен- тов И-НЕ 38,39,выход элемента И-НЕ 38 соединен с вторым входом элемента И 25 и с выходом 56 сигнала разрешения вьщачи модуля, первый вход элемента И 25 соединен с входом 57 сигнала выдачи канала, первьй вход эле- | 1ента И 26 соединен с выходом генератора 13 импульсов, а выход-с входом сброса триггера 3, входом считьгоа ния блока 14 буферной памяти и входом счетчика 17, группа выходов которого соединена с входом адреса считьгаа- ния блока -14 буферной памяти и с первой группой входов схемы 20 сравнения вторая группа входов которой соединена с группой выходов счетчика 16 и с входом адреса записи блока 14 буферной памяти, информационный вход которого соединен с информационным входом устройства, выход схемы 20 сравнения соединен с вторыми входами элементов И-НЕ 38, 39, выход элемента И-НЕ 39 соединен с прямым входом элемента И 22 и инверсным входом элемента ИЛИ 47 и вторым входом элемента И 26, выход элемента И 27 соединен с входом счетчика 18, входом 15 считывания буферной памяти и входом сброса триггера 4, прямой и инверсный выходы которого соединены соответственно с первыми входами элементов И-НЕ 40, 41, выход элемента И-НЕ 41 соединен с вы li

ХОДОМ 60 сигнала разрешения запроса модуля и с первым входом элемента И 27, второй вход которого соединен с входом 62 сигнала запроса модуля, группа выходов счетчика 18 соединен с входом адреса считывания блока 15 буферной памяти и первой группой входов схемы 21 сравнения, выход которо соединен с вторыми входами элементов И-НЕ АО, 41, выход элемента И-НЕ 40 соединен с выходом 61 сигнала прерывания канала, группа выходов счетчика 19 соединена с второй группой входов схемы 21 сравнения и с входами адреса записи блока 15 буферной памяти, информационньй выход которого соединен с информационным входом модуля, выход Формирователя 45 импульсов соединен с первым выходом 67 ответа устройства, информационный и стробирующий входы дешифратора 42 соединены соответственно с первым входом 72 адреса и первым входом 65 стробирования устройства, вход эле- мента 10 задержки соединен с выходом элемента И-НЕ 39, а выход - с прямым входом элемента И 28 и с инверсным входом элемента ИЛИ 48, выход которого соединен с входом сброса тригге- ра 5, инверсный выход которого соединен через второй выход 70 запрета устройства с первым инверсным входом элемента И 28, второй инверсньй вход которого соединен с прямым выходом триггера 2, выход элемента И 28 соединен с входом установки триггера 5, прямой выход которого соединен с первым входом элемента ИЛИ 49, с первым входом элемента И 29, с первым входом элемента И-ИЛИ 32, с вторым инверсным входом элемента И 22 и с первым входом элемента ИЛИ.50, второй вход которого соединен, с прямым выходом триггера 2, первым входом элемента ИЛИ 46, вторым входом элемента И 30 и вторым входом элемента И-ИЛИ 32, выход элемента ИЛИ 50 соединен с входом Элемента 8 задержки и с вторьм входом элемента И 23, прямой вход элемента ИЛИ 48 и второй вход элемента ИЛИ 49 М-го канала соединены с выходом элемента ИЛИ 49 (М-1)-го канала через вторую линию 64 опроса, вторые входы элементов И 29, 30 сое- динены с выходом генератора- 13 импульсов, выход элемента И 30 соединен с входом элемента 9 задержки, вторым входом элемента И 24 и управляющими

96

входтами блоков ЗД, 36 элементов И, выход элемента И 29 соединен с вторь входом элемента И 31, управляющими входами блоков 35, 37 элементов И и входом элемента 11 задержки, выход которого соединен с первым входом элемента И 31, выход которого соединен с вторым входом 66 стробирования устройства, третий и четвертьй входы элемента И-ИЛИ 32 соединены соответственно с первым 67 выходом и вторым 68 выходом ответа устройства, а вы- , ход - с управляющим входом генератор 13 гтмпульсов, информационные входы блоков 34, 35 элементов И соединены с второй группой информационных выходов блока 14 буферной памяти, а выходы - соответственно с первым и вторы входами 72, 74 адреса устройства, информационные входы блоков 36, 37 элементов И соединены с первой группой информационных выходов блока 14 буферной памяти, а вьгходы - соот-вет- ственно с первым 71 и вторым 73 входами данных устройства, информационный и стробирующий входы дещифратора 43 соединены соответственно с вторым входом 74 адреса и вторым входом 66 стробирования устройства, а выход - с вторым входом блока 12 приоритета, первый вход которого соединен с выходом дешифратора 42, управляющий вход - с выходом элемента И-НЕ 40, первый выход - с первым входом элемента ИЛИ 51, первым управляющим входом блока 33 элементов И-ИЛИ, входом формирователя 44 импульсов, второй выход - с вторым входом элемента ИЛИ 51, вторым управляющим входом блока 33 элементов И-ИЛИ, входом формирователя 45 импульсов, выход которого соединен с вторым выходом 68 ответа устройства, выход элемента ИЛИ 51 соединен с входом установки триггера 4, входом записи блока 15 буферной памяти и входом счетчика 19, первый и второй информационные входы блока 33 элементов И-ИЛИ соединены соответственно с первым 71 и вторым 73 входами данных устройства, а выход - с информационным входом блока 15 буферной памяти.

В каждом блоке 12 прибритета элементы соединены следующим образом. Управляющий вход блока 12 приоритета соединен с первыми входами элементов И 75, 76, второй вход элемента И 75 соединен с первым входом блока 12

514447966

приоритета и прямым входом элемента - , 5 являются двухадресной

памятью, могут быть вьтолнены, например, на БИС типа КР 1802 ИР1 и сосИ-НЕ 78, инверсньй вход которого соединен с вторым выходом 12 приоритета, выходом элемента 79 задержки

, .. - . .. - g тоят из двух каналов записи-считьгоаи первым входом элемента 77 И-НЕ, вто- „ „р каналов испольрой вход которого соединен с вторым входом блока 12 приоритета и вторым

входом элемента И 76, а выход - с третьим входом элемента И 75, выход элемента И-НЕ 78 соединен с третьим входом элемента И 76, выход которого соединен с входом элемента 79 задержки, выход элемента И 75 соединен с первым выходом блока 12 приоритета. Генератор 13 импульсов содержит (фиг.З) формирователь 80 импульсов, элемент И 81, элемент ИЛИ 82, триггер 83, два элемента 84, 85 задержки

зуется для записи, а другой для считывания данных.

Счетчики предназначены для

10 указания адресов, по которым производится запись (считывание) данных в каждом из каналов памяти блоков 14 и 15, После очередного обращения к одному из каналов памяти блоков 14 и 15

соответствующий счетчик увеличивает св.ое состояние на единицу. Достигнув максималтьного значения, равного количеству ячеек в блоке буферной памяти, счетчик после следующего обращения

Формирователи 44, 45, 80 импульсов у устанавливается в нулевое состояние содержат элемент 86 задержки, элемент (, счетчики 16-19 работаю- цикли- НЕ-87, элемент И 88 (фиг.4).

В каждом канапе информационные вход 58 и выход 59 каналов 1, а также выход 56 сигнала разрешения выдачи, вход 57 сигнала выдачи, выход 60 сиг- нала разрешения запроса, .выход 61

чески).

Схема 20 сравнения вырабатывает сигнал совпадения при равенстве со- J держимых счетчиков 16 и 17, а схема 21 сравнения - при равенстве содержимых счетчиков 18 и 19. Дешифраторы 42 и 43 предназначены для дешифрации адресов, вьщаваемых соответственно

мых счетчиков 18 и 19. Дешифраторы 42 и 43 предназначены для дешифрации адресов, вьщаваемых соответственно

сигнала прерывания, вход 62 сигнала

запроса подключаются к одному модулю

(источнику запросов на обмен данных), 0 на первый и второй входы 72, 74 адревходящему в вычислительную систему, причем в каждом из каналов задейТриггеры 2 предназначены для фор- ствованы только выходы дешифраторов мирования сигнала запрета на первом

выходе 69 запрета после выбора, наиболее приоритетного канала 1 перед об42 и 43, соответствующие номеру канала Остальные выходы дешифраторов 42,

35 43 в каналах не используются. .

меном данными через первый вход 71 данных и захвата первой магистрали этим каналом на время обмена данными

Триггеры 3, 4 предназначены для запоминания режима, в котором производится обращение к блокам 14 и 15 буферной памяти.

Триггеры 5 предназначены для формирования сигнала запрета на втором вькоде 70 запрета после выбора наиболее приоритетного канала 1 перед обменом данными через вто рой вход 73 данных и захвата второй магистрали

г)5 счетчиков 16 и 17 равно нулю, а триг гер 3 находится в нулевом состоянии, на выходе 56 с помощью элемента И-НЕ 38 устанавливается единичный сигнал, который свидетельствует о наличии

этим канапом на время обмена данньми, свободных ячеек в блоке 14 буферной

Блоки 14 и 15 буферной памяти памяти. При наличии на выходе 56 ка- предназначены для временного xpaHSiinH данных, которые соответственно вьгданала источника единичного сигнала источник выдает на вход 57 сигнал Выдача, который через ялемент И 25 55 поступает на вход счетчика 16, вход записи блока 14 буферной пямяти п единичньй вход триггера 1. Лапнма и адрес приемника, KOTOPOMV они п-,( назначены, через инфо млсч ч-имЛ пход

ются и принимаются через первый и второй нходы 71, 73 данных, причем ячейки памяти блока 14 имеют д ополни- тельные разряды для хранения адреса модуля, которому предназначены данные ,

зуется для записи, а другой для считывания данных.

Счетчики предназначены для

указания адресов, по которым производится запись (считывание) данных в каждом из каналов памяти блоков 14 и 15, После очередного обращения к одному из каналов памяти блоков 14 и 15

соответствующий счетчик увеличивает св.ое состояние на единицу. Достигнув максималтьного значения, равного количеству ячеек в блоке буферной памяти, счетчик после следующего обращения

устанавливается в нулевое состояние (, счетчики 16-19 работаю- цикли-

у устанавливается в нулевое состояние (, счетчики 16-19 работаю- цикли-

чески).

Схема 20 сравнения вырабатывает сигнал совпадения при равенстве со- J держимых счетчиков 16 и 17, а схема 21 сравнения - при равенстве содержимых счетчиков 18 и 19. Дешифраторы 42 и 43 предназначены для дешифрации адресов, вьщаваемых соответственно

на первый и второй входы 72, 74 адрествованы только выходы дешифраторов

42 и 43, соответствующие номеру канала Остальные выходы дешифраторов 42,

43 в каналах не используются. .

Устройство работает следующим образом.

Первоначально триггеры 2-5, счетчики 16-19 находятся в нулевом состоянии.

При необходимости вьщачи данных источник информации анализирует состояние выхода 56 своего канала 1. В начальном состоянии, так как содержимое

счетчиков 16 и 17 равно нулю, а триггер 3 находится в нулевом состоянии, на выходе 56 с помощью элемента И-НЕ 38 устанавливается единичный сигнал, который свидетельствует о наличии

свободных ячеек в блоке 14 буферной

памяти. При наличии на выходе 56 ка-

нала источника единичного сигнала источник выдает на вход 57 сигнал Выдача, который через ялемент И 25 поступает на вход счетчика 16, вход записи блока 14 буферной пямяти п единичньй вход триггера 1. Лапнма и адрес приемника, KOTOPOMV они п-,( назначены, через инфо млсч ч-имЛ пход

пает на первый вьпсод 53 опроса этого канала и т.д., пока не сбросятся триггеры 2 всех каналов более низкого приоритета. Единичный сигнал с выхода триггера 2 через элемент ШШ 50 поступает на вход элемента 8 задерж- |КИ, котооьй соабатьгоает после окончания переходных процессов при выборе старшего по приоритету запроса, и на вьгходе элемента И 23 в наиболее приоритетном канале 1 появляется единичный сигнал, который свидетельствует о разрешении вьщачи данных в магистраль. Этот сигнал поступает на запускающий вход генератора 13 импульсов.

Генератор 13 импульсов (фиг.З) работает следующим образом.

Единичный сигнал с запускающего

58 записываются параллельным кодом в ячейку памяти блока 14, адрес кото рой определяется содержимым счетчика

16(при первом обращении - в нулевую ячейку). По зaднe fy фронту сигнала Вьщача счетчик 16-увеличивает свое состояние на единицу, а триггер 3 устанавливается в единичное состояние. После этого источник либо перехо-о дит к выполнению основной программы, либо аналогичным образом заносит адрес и данные в следующую ячейку памяти блока 14.

Так как содержимое счетчиков 16 и 15

17стало различным, то на выходе схемы 20 сравнения появится нулевой сигнал, а на выходе элемента И-НЕ 39 - единичный сигнал, который свидетельствует о наличии требования на захват 20 входа поступает на вход формирователя магистрали для обмена данными,Единич- 80 импульсов, который вырабатывает ный же сигнал на выходе элемента И-НЕ

38 сохраняется. Единичный сигнал с

выхода элемента И-НЕ 39 через элемент

И 22, поскольку на его инверсные вхо- 5 с прямого выхода триггера 83 постуды поступают нулевые потенциалы с пает на выход генератора 13 импульсов

первого выхода 69 запрета и с единич- и присутствует там до тех пор, пока

кого выхода триггера 5, устанавливает на управляющий вход генератора 13

импульсов не поступит единичный импульс, который с управляющего входа генератора 13 поступает черея элемент 85 задержки, время задержки которого рассчитьгоается равным времени, достигаемому для записи данных в блок ,,(- 15 буферной памяти канала-приемника, на вход сброса триггера 83, устанавливая его тем самым в нулевое состояние. Нулевой сигнал с выхода триггера 83 поступает на выход генератора 40 13 импульсов и присутствует там до тех пор, пока импуль с с выхода элемента 85 задержки не пройдет через элемент 84 задержки, рассчитанный на время задержки, равное времени записи g данных в блок 15 буферной памяти каодиночный импульс, устанавливающий через элемент ИЛИ 82 триггер 83 в единичное состояние. Единичный сигнал

}0

триггер 2 в единичное состояние. При этом с помощью элемента НЕ 6 на первом выходе 69 запрета устанавливается сигнал запрета, который, поступая на инверсные входы элементов И 22, блокирует дальнейшую регистрацию запросов в каналах 1 на захват первой магистрали передачи данных. За это время на триггерах 2 других каналов 1 могут быть также зафиксированы требования на обмен данными.

С этого момента начинается выбор старшего по приоритету запроса, в результате которого останется в единичном состоянии триггер 2 в канале, имеющем наивысший приоритет из всех затребовавших магистраль для обмена (приоритет канала уменьшается с увеличением его номера, т.е. первый канал имеет наивысший приоритет). Триг- repbi. 2 устанавливаются в нулевое состояние с помощью сигнала опроса, ко- gg торый формируется на первом выходе 53 опроса старшего по приоритету канала 1 (из числа затребовавших магистраль) и через первую линию 63 опроса поступает на первый вход 52 опроса соседнего -д канала 1 (с меньшим приоритетом), который через элемент ШШ 47 устанавливает в нулевое состояние триггер 2 и одновременно через элемент ИЛИ 46 постунала-приемника. Импульс с выхода элемента 84 задержки поступает на первый вход элемента И 81 и, если на втором входе элемента И 81 присутствует единичный сигнал с запускающего входа генератора 13, через элемент ИЛИ 82 устанавливает триггер 83 в единичное состояние, устанавливая тем самым снова единичный сигнал на выходе генератора 13. Единичный сигнал с выхода генератора 13 импульсов через элемент И 26 поступает на вход разрешения считьшания блока 14 буферной памяти, вход счетчика 17 и нулепает на первый вьпсод 53 опроса этого канала и т.д., пока не сбросятся триггеры 2 всех каналов более низкого приоритета. Единичный сигнал с выхода триггера 2 через элемент ШШ 50 поступает на вход элемента 8 задерж- |КИ, котооьй соабатьгоает после окончания переходных процессов при выборе старшего по приоритету запроса, и на вьгходе элемента И 23 в наиболее приоритетном канале 1 появляется единичный сигнал, который свидетельствует о разрешении вьщачи данных в магистраль. Этот сигнал поступает на запускающий вход генератора 13 импульсов.

Генератор 13 импульсов (фиг.З) работает следующим образом.

Единичный сигнал с запускающего

входа поступает на вход формирователя 80 импульсов, который вырабатывает

входа поступает на вход формирователя 80 импульсов, который вырабатывает

одиночный импульс, устанавливающий через элемент ИЛИ 82 триггер 83 в единичное состояние. Единичный сигнал

,(- 0 g

}0

импульсов не поступит единичный импульс, который с управляющего входа генератора 13 поступает черея элемент 85 задержки, время задержки которого рассчитьгоается равным времени достигаемому для записи данных в бло 15 буферной памяти канала-приемника, на вход сброса триггера 83, устанавливая его тем самым в нулевое состояние. Нулевой сигнал с выхода триггера 83 поступает на выход генератора 13 импульсов и присутствует там до тех пор, пока импуль с с выхода элемента 85 задержки не пройдет через элемент 84 задержки, рассчитанный на время задержки, равное времени записи данных в блок 15 буферной памяти канала-приемника. Импульс с выхода элемента 84 задержки поступает на первый вход элемента И 81 и, если на втором входе элемента И 81 присутствует единичный сигнал с запускающего входа генератора 13, через элемент ИЛИ 82 устанавливает триггер 83 в единичное состояние, устанавливая тем самым снова единичный сигнал на выходе генератора 13. Единичный сигнал с выхода генератора 13 импульсов через элемент И 26 поступает на вход разрешения считьшания блока 14 буферной памяти, вход счетчика 17 и нулевой вход триггера 3 и через элемент И 30 - иа управляющие входы блоков элементов И ЗА, 36. По сигналу считывания данные и адрес приемника вьща- ются через блоки элементов 36 и 34 соответственно на первый вход 71 данных и на первый вход 72 адреса. Через время задержки элемента 9 задержки, рассчитанное на максимальное время распространения сигнала в шинах, на выходе элемента И 24 появится единичный сигнал, поступающий через первый |Вхрд 65 стробирования на входы стро- бирования дешифраторов 42 всех каналов, с

Таким образом, канал 1, имеющий наивысший приоритет на выдачу информации, начал въщачу информации каналу 1 - приемнику через первый вход 71 дан1гых и первый вход 72 адреса.

Поскольку в это время в остальных каналах 1 также могут присутствовать единичные сигналы на выходах элементов И-НЕ 39, свидетельствующие о на- личин требований на захват магистрали, то эти единичные сигналы поступают через элемент 10 задержки на первый прямой вход элемента И 28, на второй прямой вход которого поступает единичный сигнал с нулевого выхода триггера 2, а на инверсньй его вход - нулевой сигнал с второго выхода 70 запрета. Поскольку в нескольких, каналах 1 триггеры 5 могут быть установлены в единичное состояние, то среди этих каналов также осуществляется выбор старшего по приоритету запроса, в результате которого в единичном состоянии останется триггер 5 имеющий наивысший приоритет из числа каналов, продолжающих добиваться доступа к магистрали. Триггеры 5 всех остальных каналов будут установлены в нулевое состояние с помощью сигнала опроса, который формируется на втором выходе 55 опроса старшего по приоритету канала и чеоез вторую линию 64 опроса поступает на второй вход 54 опроса канала 1 с меньшим приоритетом и через элемент ИЛИ 48 сбрасывает триггер 5 и одновременно через элемент ИЛИ 49 поступает на второй выход 55 опроса этого канала и т.д.,пока не сбросятся триггеры5 всех каналов более низкого приоритета .Единичньй сигнал с выхода триггера 5 через элемент ИЛИ 50 поступает на вход элемента 8 задержки, который срабаты

0

5

вает после окончания переходных процессов при выборе старшего по приоритету запроса, и на выходе элемента И 23 в наиболее приоритетном канале 1 из числа продолжающих добиваться доступа к магистрали появляется единичный сигнал, который свидетельствует о разрешении выдачи данньк в магистраль. Этот сигнал поступает на запускающий вход генератора 13 импульсов, на выходе которого появляется единичный сигнал, который через элемент И 26 поступает на вход разре5 шения считьтания блока 14 буферной памяти, вход счетчика 17 и нулевой вход триггера 3 и через элемент И 29 поступает на управляющие входы блоков 35, 37 элементов И. По сигналу считы- рания данные и адрес приемника выдаются через блоки 37, 35 элементов И соответственно во второй вход 73 данных и во второй вход 74 адреса. Через время задержки элемента 11 задержки, рассчитанное на максимальное время распространения сигнала в щинах. На выходе элемента И 31 появится единич- ньй сигнал, поступающий через второй вход 66 стробирования на входы стро0 бирования дешифраторов 43 всех каналов 1.

На адресные входы дешифраторов 42 и 43 поступают адреса соответственно с первого 72 и второго 74 входов ад5 реса. В канале-приемнике, адрес которого совпадает с адресом, переданным по первому входу 72 адреса, единичный сигнал с дешифратора 42 поступает на первый вход блока 12 приоритета. В канале-приемнике, адрес которого соответствует адресу, передаваемому на второй вход 74 адреса, единичньш сигнал с выхода дешифратора 43 поступает на второй вход блока 12 приоритета.

Блок 12 приоритета работает следующим образом.

На первом и втором входах блока 12 возможны следующие ситуации.

Единичный сигнал поступает-на первьй вход блока 12. При этом нулевые сигналы на втором входе и втором выходе блока 12 через элемент И-НЕ 77 и еди- ничньй сигнал с управляющего входа блока 12 разрешают прохождение единичного сигнала через элемент И 75 на первьй вход блока 12.

Единичньй сигнал поступает только на второй вход блока 12, При этом ну0

5

0

5

11

левой сигнал с первого входа блока 12 через элемент И-НЕ 78 и единичны сигнал с управляющего входа блока 12 разрешают прохождение единичного сигнала через злемент И 76 на вход элемента 79 задержки и через время задержки, рассчитанное на окончание переходных процессов после записи информации в блок 15 буферной памяти, единичный сигнал появится на втором выходе блока 12. Единичные сигналь; с второго выхода и второго входа блока 12, поступая на элемент И-НЕ 77, запрещают прохождение единичного сигна- ла с первого входа блока 12 через элемент И 75.

Единичные сигналы поступают одновременно на первый и второй входы блока 12, а на втором выходе блока 12 присутствует нулевой сигнал. При этом нулевой сигнал с второго выхода блока 12 через элемент И-НЕ 77 совместно с единичным сигналом на управляющем входе блока 12 разрешают про- вхождение единичного сигнала через элемент И 75 на первый выход блока 12 Нулевой сигнал с второго выхода блока- 12, поступая на инверсньш .вход элемента И-НЕ 78, запрещает прохожд.е- ние единичного сигнала через элемент И 76. Таким образом, при одновременном поступлении единичных сигналов на первьй и второй входы блока 12 единичный сигнал появится только на первом выходе блока 12.

Единичный сигнал с первого выхода блока 12 приоритета поступает на первый вход элемента ИЛИ 51, первый управляющий вход блока элементов И-ИЛИ 33 и на вход формирователя 44 импульсов, который вырабатьгаает одиночный импульс, поступающий на выход 67 ответа.

Если же единичный сигнал появился на втором выходе блока 12 приоритета, то он поступает -на второй вход элемента ИЛИ 51, второй управляющий вход блокд элементов И-ИЛИ 33 и вход формирователя 45 импульсов, который вьфаба тьгаает одиночный импульс, поступающий на выход 68 ответа.

Единичный сигнал-с выхода элемента ИЛИ 51 поступает на вход разрешения записи блока 15 буферной памяти, вход счетчика 19 и единичный вход тригге- ра 4. По сигналу записи данные, установленные либо в первом входе 71 дан- Hbtx, либо;во втором входе 73 данных

612

(в зяв1 С мости ОТ ТОГО, ИЗ какого входа ос пцествляется прием в данный канал 1), через блок элементов И-ШШ 33 записываются в ячейку памяти блока 15 буферной памяти канала-приемника, адрес которой определяется содержимым счетчика 19 (при первом обращении - в нулевую ячейку). Импульс ответа с первого 67 с второго выхода 68 ответа (в зависимости от того, в первый или второй входы 71, 73 данных канал-источник осуществляет выдачу информации) поступает через элемент 32 на управляющий вход генератора 13 импульсов. Через время задержки, достаточное для записи данных в блок 15 канала-приемника, на выходе генератора 13 импульсов установится нулевой сигнал, устанавливая тем самым через элемент И 26 нулевой сигнал на входе разрешения считывания блока 14 буферной памяти, входе счетчика 17 и входе триггера 3. Счетчик t7 при этом увеличивает свое состояние на единицу, а триггер 3 переходит в нулевое состояние. Нулевой сигнал с выхода генератора 13 импульсов через элемент И 24, если данный канал-источник осуществлял выдачу информации в первьп вход 71 данных, устанавливается на первом входе 65 стробирования или через элемент И-31, если канал-источник Ьсуществлял выдачу данных во второй вход 73 данных, устанавливается на втором входе 66 стробирования. Нулевые сигналы на входах 65, 66 стробирования запрещают дешифрацию адреса в дешифраторах 42, 43 каналов-приемников. При этом на первом или втором выходе блока 12 приоритета (в зависимости от того, из первого 71 или второго 73 входа данных осуществляется прием данных в канал-приемник) устанавливается нулевой сигнал. Тем самым запрещается прохождение данных через блок элементов И-ИЛИ 33 на информационный вход блока 15 буферной памяти.

Кроме этого, через элемент ИЛИ 51 нулевой сигнал устанавливается на входе разрешения записи блока 15 буферной памяти, входах счетчика 19 и триггера 4. Счетчик 19 увеличивает свое состояние на единицу, а триггер 4 устанавливается в единичное состояние. Таким образом, в канале-приемнике состояния счетчиков 18 и 19 стали азличными, поэтому на выходе схемы 21 сравнения устанавливается нулевой

сигнал, а на выходе элемента И-НЕ 41 устанавливается единичный сигнал, который свидетельствует о наличии данных в блоке 15 буферной памяти. Этот сигнал поступает на вход элемента И 27 и выход 60 сигнала разрешения .запроса. Приемник информации периодически анализирует состояние выхода 60 своего канала 1. При наличии на выходе 60 единичного сигнала приемник информации вьщает на вход 62 сигнал Запрос, который через элемент И 27 поступает на вход разрешения считьшания блока 15 буферной памяти, входы счетчика 18 и триггера 4

При этом данные из ячейки памяти блока 15, адрес которой определяется состоянием счетчика 18 (при первом

канала-приемника. В случае, если после передачи очередного слова данных содержимое счетчиков 16 и 17 оказывается одинаковым, на выходе схемы 20 сравнения появится единичный сигнал, а на выходе элемента И-НЕ 39 при условии, что триггер 3 находится в нулевом состоянии, т.е. производилось

считьгаание из блока 14 буферной памяти, вырабатывается нулевой сигнал, свидетельствующий о том, что блок 14 буферной памяти пуст. Этот сигнал пройдет через инверсные входы элементов ИЛИ 47 и 48 и устанавливает триггер 2 или триггер 5 (в зависимости от того, какой из них был взведен в данном канале) в нулевое состояние. При этом через элемент НЕ 6 на первом

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного подключения источников информации к общей магистрали | 1989 |

|

SU1612303A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для прерывания программ | 1985 |

|

SU1256029A1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

Изобретение относится к области вычислительной техники и может быть использовано в многомашинных и многопроцессорных вычислительных системах с магистральной структурой, осущест- вляющих обработку болыпих потоков дан- .ных. Цель предлагаемого изобретения - расширение функциональных возможностей устройства бесконфликтного обмена информацией между абонентами вычислительной системы по двум общим магистралям. Цель достигается тем, что устройство содержит М каналов (по числу вычислительных модулей в системе), каждый канал содержит два блока памяти и блок приоритета. Каждый из каналов может осуществлять ввод-вьшод информации с любой из двух свободных магистралей. 4 ил.

25

30

35

обращении - из нулевой ячейки), вьща- 2о входе 69 запрета устанавливается нуле- ются через информационный выход 59 в приемник информации. По заднему фронту сигнала Запрос счетчик 18 увели- -чивает свое состояние на единицу, а триггер 4 устанавливается в нулевое состояние. В случае, если из .источника информации в блок 14 буферной па-- мяти канала-источника поступило не- . сколько слов данных, предназначенных для передачи (причем адреса приемников могут быть различными), то содержимое счетчиков 16 и 17 после первой передачи остается различным. При этом на выходе схемы 20 сравнения присутствует нулевой сигнал, а на выходе элемента И-НЕ 39 установлен единичный сигнал, который, поступая на инверс- ньй вход элемента ИЛИ 47, не приводит к сбросу триггера 2, Аналогично изводится работа источника, у которого триггер 5 находится в единичном состоянии, а триггер 2 в нулевом. При этом единичный сигнал с выхода элемента И-НЕ 39 проходит через элемент 10 задержки и, поступая на инверсный вход элемента ИЛИ 48, не приводит к сбросу триггера 5. в нулевое состояние. Так как триггер 2 (или триггер 5) канала-источника остается в единичном состоянии, то на запускающем входе генератора 13 импульсов сохраняется единичньй сигнал и через времЯу достаточное для записи данных в- блок 15 буферной памяти канала-источника, на выходе генератора 13- импульсов вновь установите единичный сигнал и аналогичным образом будет осуществлена передача следующего слова данных в блок 15 буферной памяти

40

45

50

55

вой сигнал, если данный канал осуществлял выдачу данных в первый вход 71 данных или через элемент НЕ 7 уста- ; навливается нулевой сигнал во второй вход 70 запрета, если данный канал осуществлял вьщачу данных во второй вход 73 данных. Таким образом, разрешается производить захват магистрали другим источником.

В процессе обмена данными возможны следующие ситуации.

При выдаче данных из источника информации в канал 1 все ячейки блока 14 буферной памяти заняты. При этом содержимое счетчиков 18 и 19 равно, т.е. на выходе схемы 21 сравнения присутствует единичный сигнал, а триггер 3 находится в единичном состоянии (для этого производилась запись в блок 14 буферной памяти). В этом случае с выхода элемента И-НЕ 38 на вход элемента И 25 и на выход 56 выдается нулевой сигнал, запрещающий производить запись в блок 14, ас выхода элемента И-НЕ 39, вьщается единичный сигнал, поступающий в качестве сигнала запроса на захват магистрали на вход элемента И 22 к вход рлемента 10 задержки.

При выдаче данных из блока 14 канала-источника в блок 15 канала-приемника всё ячейки блока 15 буферной памяти заняты. При этом содержимое счетчиков 18 и 19 равно, т.е. на выходе схемы 21 сравнения присутствует едииичньй сигнал, а триггер 4 находится в единичном состоянии (до этого производилась запись в блок 15). В этом случае с выхода элемента И-НЕ 40

5

0

5

о входе 69 запрета устанавливается нуле-

0

5

0

5

вой сигнал, если данный канал осуществлял выдачу данных в первый вход 71 данных или через элемент НЕ 7 уста- ; навливается нулевой сигнал во второй вход 70 запрета, если данный канал осуществлял вьщачу данных во второй вход 73 данных. Таким образом, разрешается производить захват магистрали другим источником.

В процессе обмена данными возможны следующие ситуации.

При выдаче данных из источника информации в канал 1 все ячейки блока 14 буферной памяти заняты. При этом содержимое счетчиков 18 и 19 равно, т.е. на выходе схемы 21 сравнения присутствует единичный сигнал, а триггер 3 находится в единичном состоянии (для этого производилась запись в блок 14 буферной памяти). В этом случае с выхода элемента И-НЕ 38 на вход элемента И 25 и на выход 56 выдается нулевой сигнал, запрещающий производить запись в блок 14, ас выхода элемента И-НЕ 39, вьщается единичный сигнал, поступающий в качестве сигнала запроса на захват магистрали на вход элемента И 22 к вход рлемента 10 задержки.

При выдаче данных из блока 14 канала-источника в блок 15 канала-приемника всё ячейки блока 15 буферной памяти заняты. При этом содержимое счетчиков 18 и 19 равно, т.е. на выходе схемы 21 сравнения присутствует едииичньй сигнал, а триггер 4 находится в единичном состоянии (до этого производилась запись в блок 15). В этом случае с выхода элемента И-НЕ 40

выдается нулевой сигнал, который поступает на управляющий вход блока 12 приоритета, запрещая появление единичного сигнала на выходах блока 12, тем самым запрещая выдачу сигнала ответа с помощью формирователей 4А, 45 и через элемент ИЛИ 51 запрещая производить запись в блок 15 буферной памяти. Нулевой сигнал с выхода эле- мента К-НЕ 40 поступает также через выход 61 в приемник информации. По этому сигналу приемник информации прерывает программу обработки данных и производит считывание данных, записанных в блоке 15 буферной памяти, путем выдачи сигнала Запрос на вход 62 канала-приемника. При этом с выхода элемента И-НЕ 41 на вход элемента И 27 и выход 60 сигнала разрешения запроса вьщается единичный сигнал.

Так как в первом случае возможны простои источников информации, а во втором случае осуществляется прерывание приемников информации, то это может привести к снижению производительности вычислительной системы. Поэтому емкость блоков 14 и 15 буферной памяти должна быть рассчитана таким образом, чтобы вероятность переполне- ния блоков 14 и 15 бьта достаточно мала.

Технико-экономическое преимущество предлагаемого изобретения по сравне- 1НИЮ с базовым (.прототип) заключается IB том, что базовое устройство не поз- воляет осуществлять бесконфликтный обмен информацией между абонентами вычислительной системы по двум общим магистралям. Использование предлагаемого устройства позволяет осуществлять бесконфликтньй обмен информацией между абонентами вычислительной системы по двум общим магистралям. Это существенно повышает функциональные возможности устройства, поскольку при использовании базового устройства для обеспечения обмена информацией между абонентами по двум общим магистралям потребуется использование двух кана лов для обеспечения доступа одного абонента к двум магистралям. Кроме этого, необходимость разращения конфликтных ситуаций при обмене по двум магистралям требует введения дополни- рельного оборудования. Таким образом, при использовании базового устройства для обеспечения бесконфликтного обме- на между абонентами вычислительной

д g JQ

25 Q

-

0

5

0

796 6 системы по двум магистралям потребуется увеличение оборудования более чем в 2 раза.

Формула изобретения

Многоканальное устройство для обмена данными между модулями вычислительной системы, содержащее М каналов, каждый из которых содержит три триггера, два блока буферной памяти, четыре счетчика, две схемы сравне-. ния, четыре элемента И-НЕ, генератор импульсов, два элемента задержки, шесте элементов И, два элемента ИЛИ, первый элнмент НЕ, первый формирователь импульсов, первый дещифратор, причем в каждом канале выход первого элемента И соединен с входом установки первого триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ, выход первого элемента задержки соединен с первым входом второго элемента И, выход которого соединен с запускающим входом генератора импульсов, выход второго элемента задержки соединен с первым входом третьего элемента И, выход которого соединен с первым входом стробирования устройства, выход второго элемента ИЛИ соединен с входом сброса первого триггера, инверсный выход которого соединен через первый элемент НЕ с первым выходом запрета устройства и с первым инверсным входом первого элемента И, второй вход первого и прямой вход второго элемента ИЛИ М-го канала соединены через первую линию опроса с выходом первого элемента ИЛИ (М-1)-го канала, выход четвертого элемента И соединен с входом первого счетчика, входом писи первого блока буферной памяти и входом установки второго триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами первого и второго элементов И-НЕ, выход первого элемента И-НЕ соединен с вторым входом четвертого элемента. И и с входом сигнала разрешения выдачи устройства, первый вход четвертого элемента И соединен с входом сигнала вьдачи канала, первый вход пятого элемента И соединен с выходом генератора импульсов, а выход - с входом сброса второго триггера, входом считывания первого блока буферной памяти и входом второго счетчика, группа выходов которого соединена с входом адреса считывания первого блока буферной памяти и с первой группой входов первой схемы сравне- ния, вторая группа входов которой соединена с группой выходов первого счетчика и с входом адреса записи первого блока буферной памяти, информационный вход которого является ин- ю вареный выход которого соединен через второй элемент НЕ, с вторым вы- {ходом запрета устройства и с первым инверсным входом седьмого элемента И второй инверсный вход которого соединен с прямым выходом первого триггера, выход седьмого элемента И соединен с входом установки четвертого триггера, прямой выход которого соединен с первым ВХОДОМ четвертогоэлерез второй элемент НЕ, с вторым вы- {ходом запрета устройства и с первым инверсным входом седьмого элемента И второй инверсный вход которого соединен с прямым выходом первого триггера, выход седьмого элемента И соединен с входом установки четвертого триггера, прямой выход которого соединен с первым ВХОДОМ четвертогоэлеформационным входом устройства, выход первой смены сравнения соединен с вторыми входами первого и второго элементов И-НЕ, выход второго элемента И-НЕ соединен с прямым входом пер- 15 вого элемента И, инверсным входом второго элемента ИЛИ и вторым входом пятого элемента И, выход шестого элемента И соединен с входом третьего счетчика, входом считывания второго 20 мента fflИ, с первым входом восьмого блока буферной памяти и входом сбро- элемента И, с первым входом элемен- са третьего триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И-НЕ, вькод четвертого элемента И-НЕ соединен с входом разрешения запроса и с первым входом шестого элемента И, второй вход которого соединен с выходом запроса устройства, группа выходов тре- 30 элемента ИЛИ соединен с первым и четьего счетчика соединена с входом рез первьй элемент задержки с вторым адреса считывания второго блока бу- входами второго элемента И, прямой ферной памяти и первой группой входов второй схемы сравнения, выход которой соединен с вторыми входами третьего и четвертого элементов И-НЕ, выход

та И-ИЛИ, с вторым инверсным входом первого Элемента Икс первым входом глтого элемента ИЛИ, второй вход 25 которого соединен с прямым выходом первого триггера, первым входом первого элемента ИЛИ, первым входом девятого элемента И и вторым входом элемента И-ИПИ,выход пятого

вход третьего и второй вход четвертого элемента 1ШИ М-го канала соедс динены через вторую линию опроса с выходом четвертого элемента ИЛИ (М-1)-го канала, выход генератора импульсов соединен с вторыми входами восьмого и девятого элементов И, вытретьего элемента И-НЕ соединен с выходом сигнала прерывания канала, группа выходов четвертого счетчика соединена с второй группой входов второй схемы сравнения и с входом адреса записи второго блока буферной памяти, информационный выход которого является информационным выходом

устройстз а, выход первого формирова- 45 выход восьмого элемента И соеди- теля импульсов соединен с первым вы- иен с вторым входом десятого элемен- хоДом ответа устройства, информацион- та И, управляющими входами второго ньщ и стробируюпще входы первого дешифратора соединены соответственно с

и четвертого блоков элементов И и через четвертый элемент задержки с

первыми входами адреса и стробирова- gg первым входом десятого элемента И,

нид устройства, отличающе е с д тем, что, с целью расширения функциональных возможностей устройства, в каждый канал введены четвертый триггер, второй дешифратор, второй формирователь импульсов,- четыре элемента ИТШ., четыре элемента И, два элемента.задержки, элемент И-ИЛИ, второй элемент НЕ, четьфе блока элевыход которого соединен с вторым вход стробирования устройства, третий и четвертый входы элемента И-ИЛИ соединены соответственно с первым и вт сс выходами ответа устройства, а в ход - с управляющим входом генерато ра импульсов, информационные входы первого и второго блоков элементов И соединены с второй группой информентов И, блок приоритета, блок элементов И-ИЛИ, причем в каждом канале вьЬсод второго элемента И-НЕ через третий элемент задержки соединен с прямым входом седьмого элемента И и с инверсным входом третьего элемента ИЛИ, выход которого соединен с входом сброса четвертого триггера, инвареный выход которого соединен через второй элемент НЕ, с вторым вы- {ходом запрета устройства и с первым инверсным входом седьмого элемента И второй инверсный вход которого соединен с прямым выходом первого триггера, выход седьмого элемента И соединен с входом установки четвертого триггера, прямой выход которого соединен с первым ВХОДОМ четвертогоэлемента fflИ, с первым входом восьмого элемента И, с первым входом элемен- элемента ИЛИ соединен с первым и через первьй элемент задержки с вторым входами второго элемента И, прямой

мента fflИ, с первым входом восьмого элемента И, с первым входом элемен- элемента ИЛИ соединен с первым и через первьй элемент задержки с вторым входами второго элемента И, прямой

та И-ИЛИ, с вторым инверсным входом первого Элемента Икс первым входом глтого элемента ИЛИ, второй вход которого соединен с прямым выходом первого триггера, первым входом первого элемента ИЛИ, первым входом девятого элемента И и вторым входом элемента И-ИПИ,выход пятого

мента fflИ, с первым входом восьмого элемента И, с первым входом элемен- элемента ИЛИ соединен с первым и через первьй элемент задержки с вторым входами второго элемента И, прямой

вход третьего и второй вход четвертого элемента 1ШИ М-го канала соединены через вторую линию опроса с выходом четвертого элемента ИЛИ (М-1)-го канала, выход генератора импульсов соединен с вторыми входами восьмого и девятого элементов И, выход девятого элемента И соединен с первым и через второй элемент задержки с вторьп входами третьего элемента И, а также с управляющими входами; первого и третьего блоков элементов

выход восьмого элемента И соеди- иен с вторым входом десятого элемен та И, управляющими входами второго

и четвертого блоков элементов И и через четвертый элемент задержки с

первым входом десятого элемента И,

выход которого соединен с вторым входом стробирования устройства, третий и , четвертый входы элемента И-ИЛИ соединены соответственно с первым и вто- выходами ответа устройства, а выход - с управляющим входом генерато- . ра импульсов, информационные входы первого и второго блоков элементов И соединены с второй группой информационных вькодов первого блока буферной памяти,а выходы- соответственно с первым и вторым входами адреса устройства, информационные входы третьего и четвертого блоков элементов И соединены с первой группой информационных выходов первого блока буферной памяти, а выходы - соответственно с первым и вторым входами данньк устройства, информационный и стробирующий входы второго дешифратора соединены соответственно с вторыми входами адреса и стробирования устройства, а выход - с вторым входом блока приоритета, первый вход которого соединен с выходом первого дешифратора, управляющий вход - с выходом третьего элемента И-НЕ, первый выход - с первым входом шестого элемента ИЛИ, первым управляющим входом блока элементов И-ИЛИ, входом первого формирователя импульсов, второй

выход - с вторым входом шестого элемента ПНИ, вторым управляюгдим входом блока элементов И-ИЛИ, входом второго формирователя импульсов, выход которого соединен с вторым вькодом

ответа устройства, выход шестого элемента ИЛИ соединен с входом установки третьего триггера, входом записи второго блока буферной памяти и входом четвертого счетчика, первый и второй

информационные входы блока элементов И-ИЛРГ соединены соответственно с первым и вторым входами данных устройства, а пыход - с информационным входом второго блока буферной памяти,

I П

Ш37

Отгз

Фиг.з

Г

86

HZ6,Z9.30

отзг

4(45,80)

Г

| Устройство для сопряжения абонентов с общей магистралью вычислительной системы | 1984 |

|

SU1223239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-15—Подача