триггера является входом останова устройства, установочный вход второго триггера соединен с выходом второго элемента ИЛИ, первый вход которого является входом пуска устройства, первый выход третьего триггера соединен с вторыми входам первого и третьего элементов И и с первыми управляющими входами перво второго,третьего и четвертого комм торов, второй выход третьего триггера соединен с вторыми вхбдами .второго и четвертого элементов И и вторьми управляю цими входами первого, второго, третьего и четверто го коммутаторов, выход четвертого триггера соединен с вторым входом третьего формирователя импульсов, первый выход которого соединен с первьм информационным входом второго коммутатора и вторым информационным входом третьего коммутато8ра, второй информационный вход второго коммутатора и первый информационный вход третьего коммутатора соединены между собой и с первым выходом первого формирователя импульсов, второй выход третьего формирователя импульсов является выходом синхроимпульсов устройства и соединен с управляющим входом выходного регистра, выход которого является информационным выходом устройства, выходы третьего и четвертого блоков стековой памяти соединены с информационными входами четвертого коммутатора, выход которого соединен со сбрасывающим выходом четвертого триггера и вторым входом второго элемента ИЛИ, выход второго коммутатора соединен с запускающим входом первого счетчика, выход третьего коммутатора соединен с запускающим входом второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения | 1979 |

|

SU857967A1 |

| Устройство для селекции изображений объектов | 1988 |

|

SU1608711A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Устройство для обмена информацией | 1979 |

|

SU826328A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ, содер,жа1цее первый и второй блоки стековой памяти, два счетчика, коммутатор , выходной регистр, выход первого счетчика соединен с адресным входом первого блока стековой памяти, выход второго счетчика - с адресным . входом второго блока стековой памяти, выход первого блока стековой памяти соединен с первым информационным входом коммутатора, а выход второго блока стековой памяти - с вторым информационным входом коммутатора, выход которого соединен с информационным входом выходного регистра, о т л и ч а ю щ е е с я тем,что, с целью расширения его функциональных возможностей путем совместной работы разноскоростных устройств, в него введены третий и четвертый блоки стековой памяти, два элемента ИЛИ, пять элементов И, четыре триггера, элемент задержки. Три коммутатора и три формирователя импульсов , первые входы каждого из которых являются соответственно входами синхронизации, признака окончания массива и запроса информации устройства, информационные входы первого и второго блоков стековой памяти соединены между собой и являются информационным входом устрой- ства, информационные входы третьего и четвертого блоков стековой памяти соединены меящу собой и с первым выходом второго формирователя импульсов, второй выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с дторым выходом первого формирователя импульсов и с первг,1ми входами первого и .второго элементов И, выход первого элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И, выходы первого, второго, третьего и четвертого элементов И соединены с входами управления записью соответственно первого, второiro, третьего и четвертого блоков стековой памяти, адресные входы первого и третьего блоков стековой памяти соединены между собой и с выходом первого счетчика, адресные входы второго и четвертого блоков стековой памяти соединены между со бой и с выходом второго счетчика, выСО 00 ходы первого и второго триггеров соединены с входами пятого элемента И, выход которого соединен с входом элемента задержки, выход которого является выходом начала обмена устройства и соединен со сбрасывающими входами первого и второго триггеров, со счетным входом третьего триггера, с установочным входом четвертого триггера и со сбрасьгеаюо{ими входами первого и второго счетчиков, установочный вход первого

Изобретение относится к автоматик и вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации, в частности для свя зи устройства управления накопителем на магнитной ленте с электростатическим печатающим устройством.

Известно устройство для сопряжения, содержащее буферную память с входным и выходным коммутаторами, с которыми соединены выходы счетчиков записи и считывания, вход каждого из которых соединен с одним из входов реверсивного счетчика с присоединенными к его выходам дешифраторами для блокировки записи и считывания l .

Недостатком этого устройства является невозможность сопряжения при помощи него накопителя на магнитной ленте с выводным устройством в связи с тем, что при поступлении информации в известное устройство со скоростью, превышающей скорость вьщачи, имеют место случаи блокировки записи в буферную память. Это привело бы к потере части информации, так как накопитель на магнитной ленте формирует информационные потоки, непрерывные в пределах считываемой с магнитной ленты зоны.

Наиболее близким к изобретению по технической сущности является устройство сопряжения, которое содержит два входных регистра, два блока стековой памяти, счетчик записи и счетчи к считывания, два выходных регистра, коммутатор, четыре элемента И, индикатор состояния памяти, распределитель импульсов записи, распределитель импульсов считывания, блок асинхронной записи, схему сравнения, регистр начального адреса и блок формирования начала сообщения.Распределитель импульсов записи управляет процессом записи входной информации во входные регистры. Распределитель импульсов считьшания управляет поочередным считыванием из блоков стековой памяти в выходные регистры. Блок асинхронной записи управляет очередностью перезаписи из входных регистров в блоки стековой памяти и считыванием, отдавая приоритет процессу считьшания перед записью. На выход устройства информация подается с выходных регистров через коммутатор. Блоками

стековой памяти управляют счетчики записи и считывания через схему .сранения при помощи индикатора состояния памяти, регистра начального адреса и блока формирования наяала Соэбщения 2j .

Недостатком известного устройства является также невозможность использования накопителя на магнитной ленте в качестве источника ийформации, так как возможны случаи, блокировки записи в память, приводящие в потере части информации,которая поступает непрерывно в пределах считьшаемой зоны со скоростью, превьшающей скорость вьщачи.

Целью изобретения является расширение функциональных возможностей за счет совместной работы разноскоростных устройств.

Поставленная цель достигается тем, что в устройство для сопряжения, содержащее первый и второй блоки стековой памяти, два счетчика, коммутатор, выходной регистр, выход первого счечика соединен с адресным входом первого блока стековой памяти, выход второго счетчика - с адресным входом второго блока стековой памяти, выход первого блока стековой памяти соединен с первым информационным входом коммутатора, а выход второго блока стековой памяти - с вторым информационным входом коммутатора, выход Которого соединен с информационным входом выходного регистра, введены третий и четвертый блоки стековой памяти, два элемента ИЛИ, пять элементов И, четьфе триггера, элемент задержки, три коммутатора и-три формирователя импульсон,первые входы каждого из которых являются соответственно входами синхронизации, признака окончания массива и запроса инфбрмации устройства, информационные входы первого и второго блоков стековой памяти соединены между собой и являются информационным входом устройства, информационные входы третьего и четвертого блоков стековой памяти соединены между собой и с первым выходом второго формирователя импульсов, второй выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом первого формирователя импульсов и с первыми входами первого и второго элементов И, выход первого элемента ИЛИ соединен с первыми входами

третьего и четвертого элементов И выходы первого, второго третьего и четвёртого элементов И соединены с входами управления записью соответственно : первого, второго, третьего

и четвертого блоков стековой памяти, адресные входы первого и третьего блоков стековой памяти соединены между собой,и с выходом первого счетчика, адресные входы второго и четвертого блоков стековой памяти соединены между собой и с выходом второго счетчика, выходы первого и второго триггеров соединены с входами пятого элемента И, выход которого

соединен с входом элемента задержки, выход которого является выходом начала обмена устройств и соединен со . сбрасывающими входами первого и второго триггеров, со счетным входом

третьего триггера, с установочным

входом четвертого триггера и со сбрасывающими входами первого и второго счетчиков, установочный вход первого триггера является входом останова устройства, установочный вход второго триггера соединен с выходом второго элемента ИЛИ, первый вход которого является входом пуска устройства, первый выход третьего триггера

соединен с вторыми входами первого и третьего элементов И и с первыми

управляющими входами первого, второго, третьего и четвертого комму- . таторов, второй выход .третьего триггера соединен с вторыми входами второго и четвертого элементов И и вторыми управляющими входами первого, второго, третьего и четвертого коммутаторов , выход четвертого триггера

соединен с вторым входом третьего формирователя импульсов, первый выход которого соединен с первым информационным входом второго коммутатора и вторым информационным входом третьего коммутатора, второй информационный вход второго коммутатора и первый информационный вход третьего коммутатора соединены между собой и с первым выходом первого формирователя импульсов, второй выход

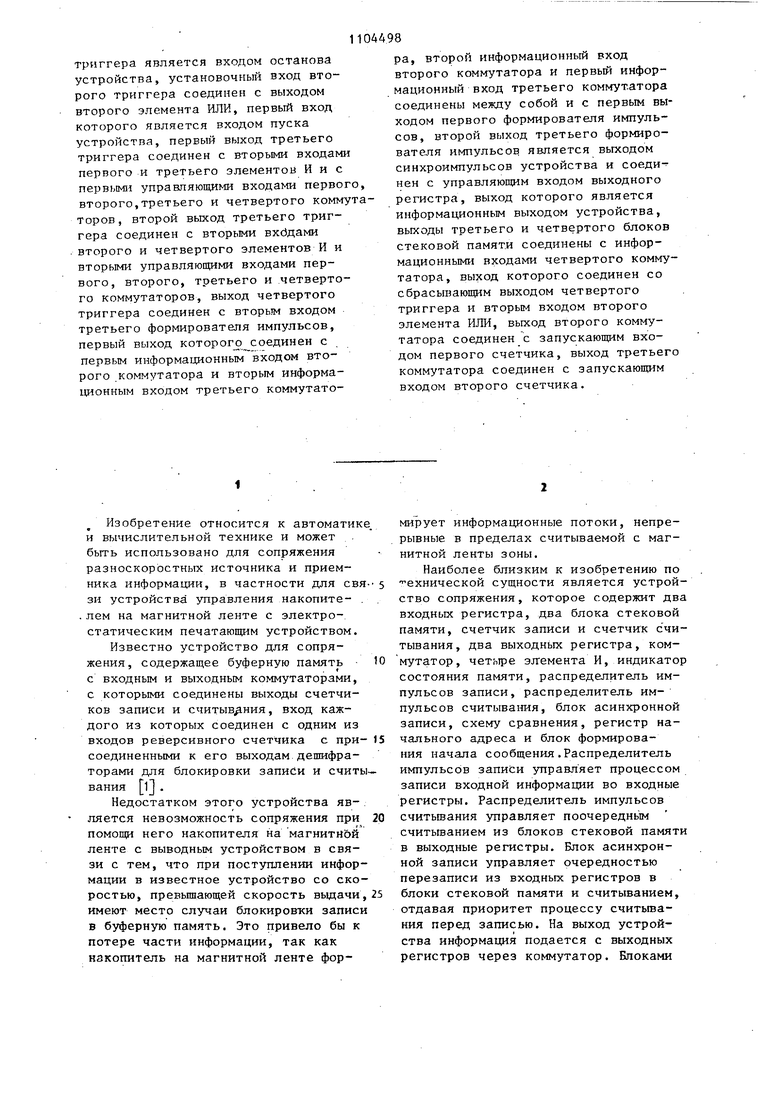

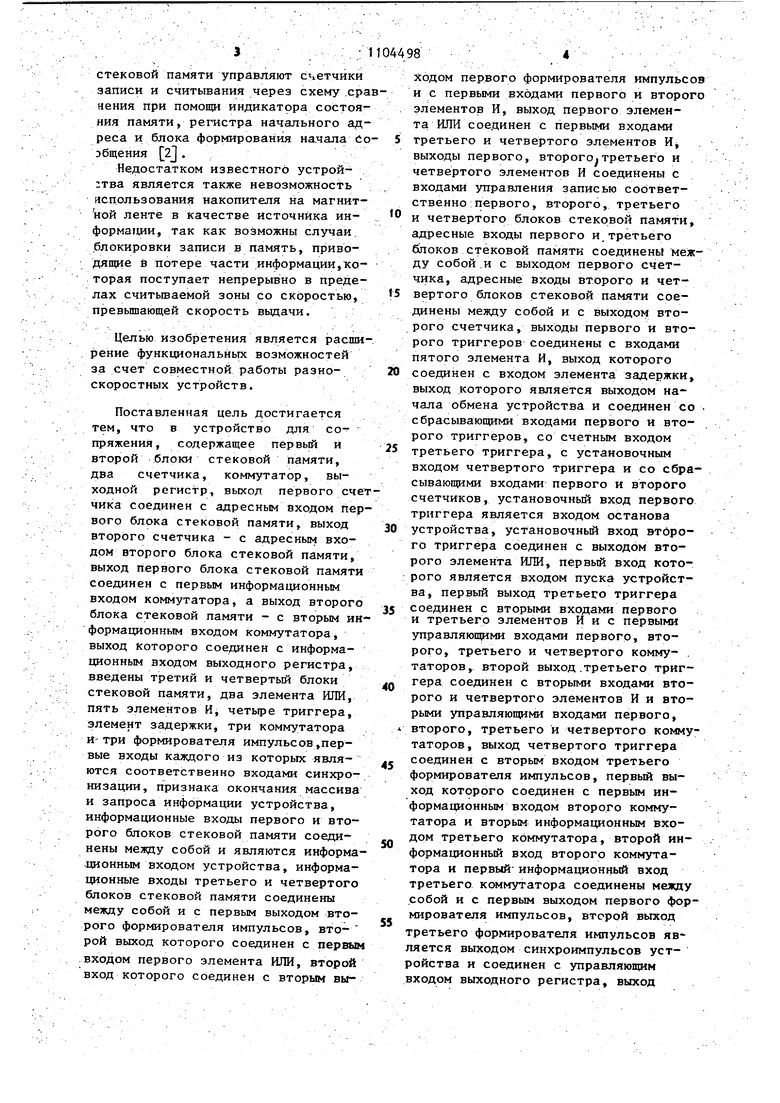

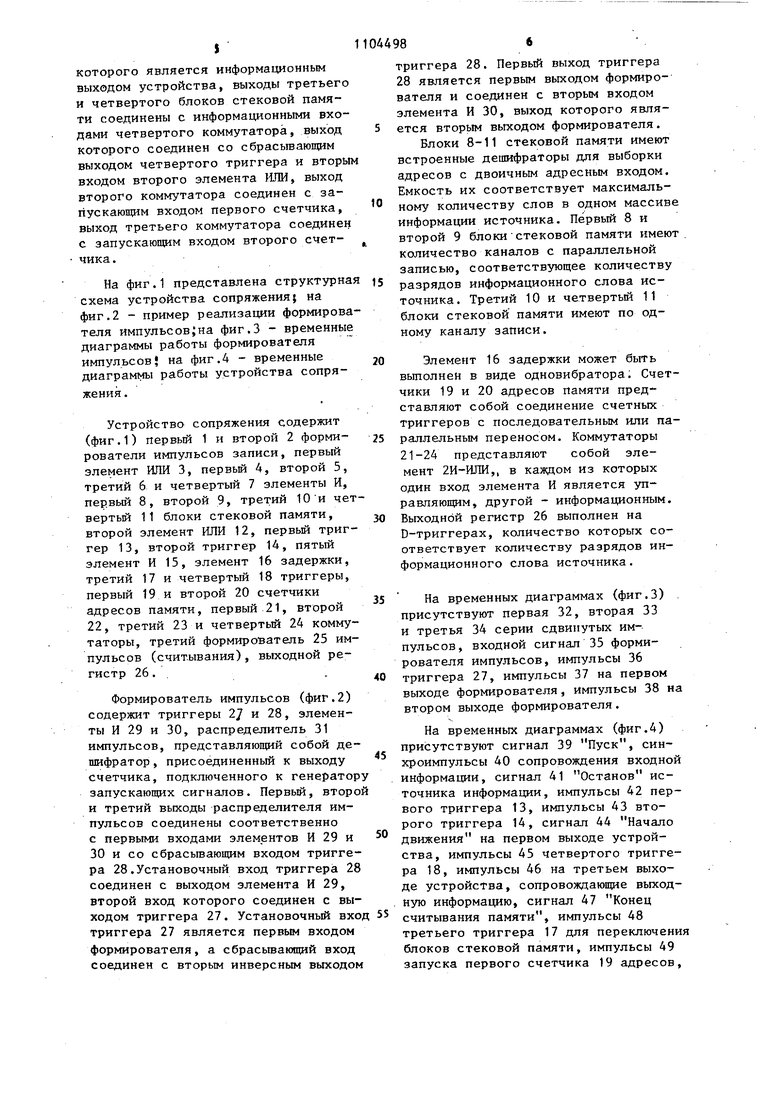

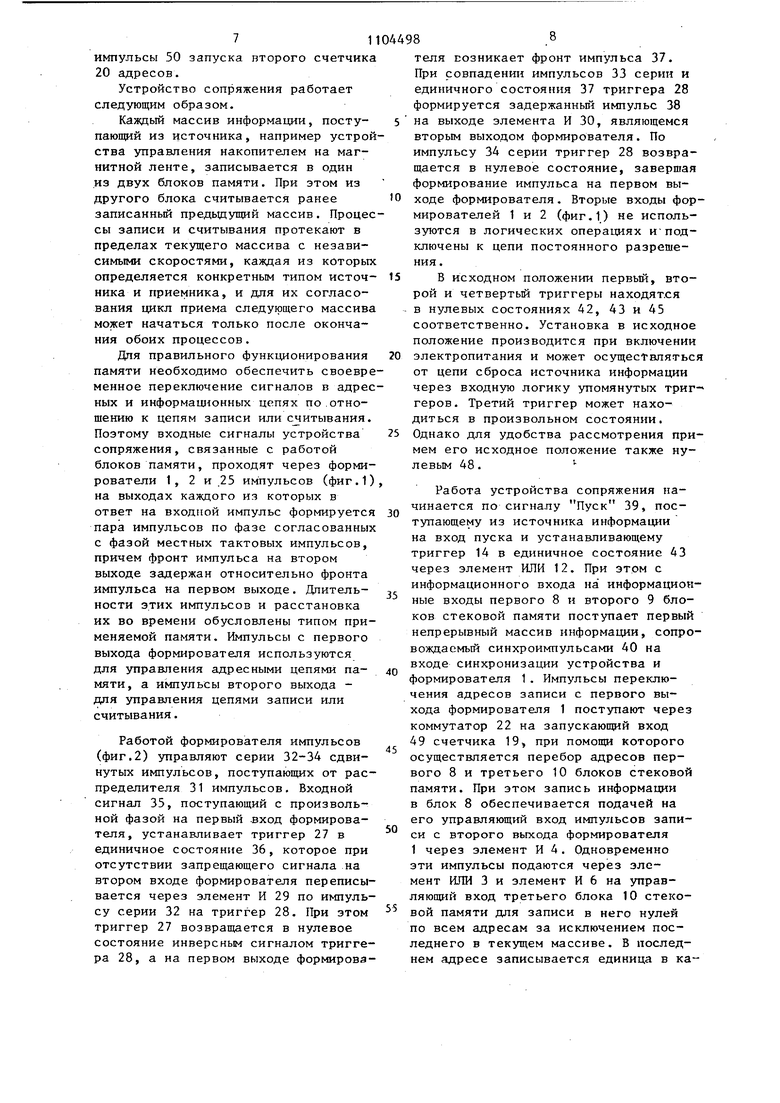

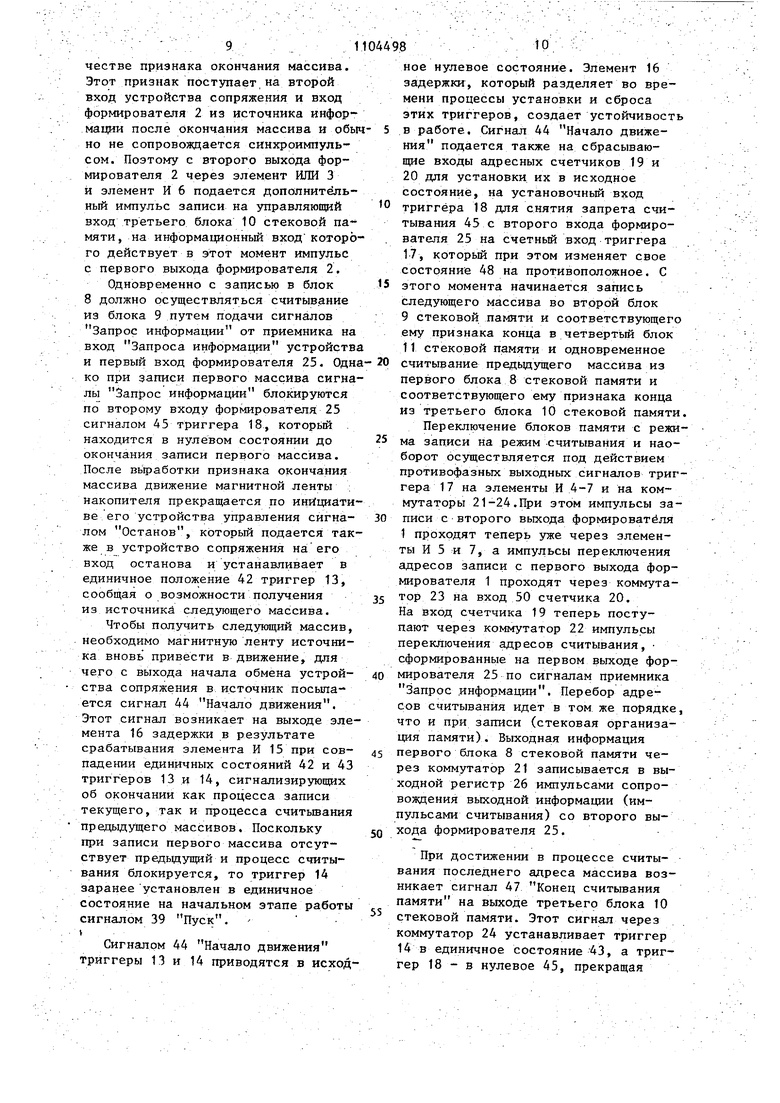

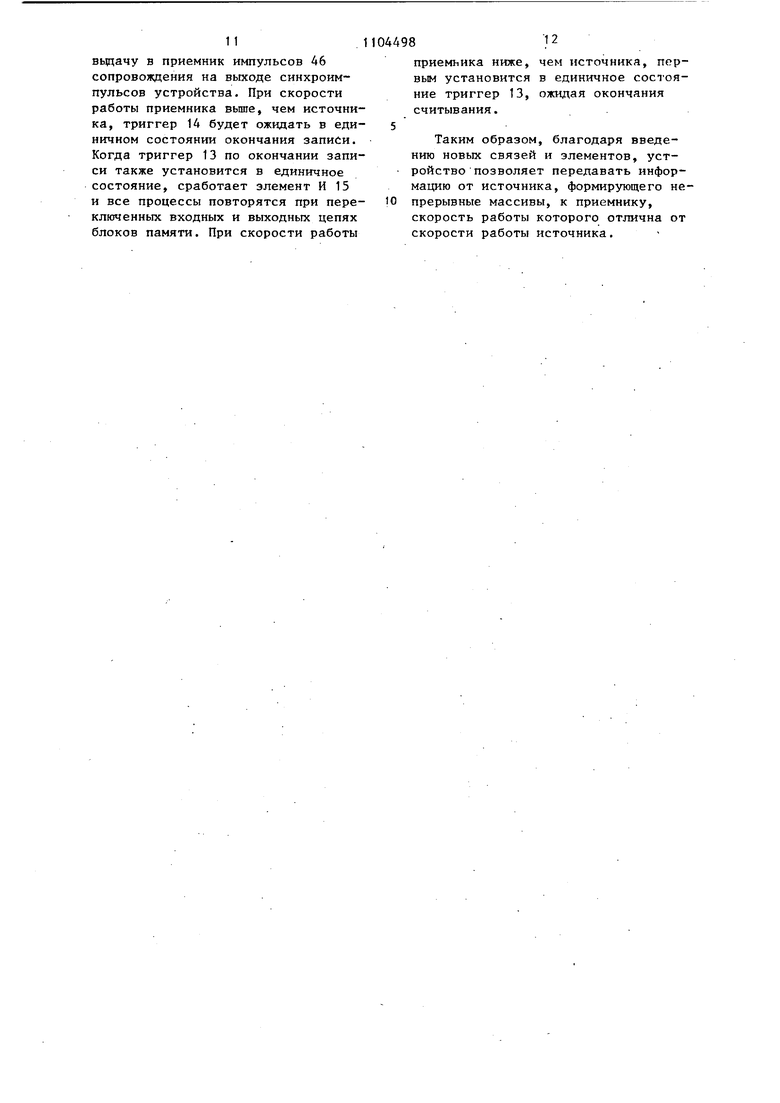

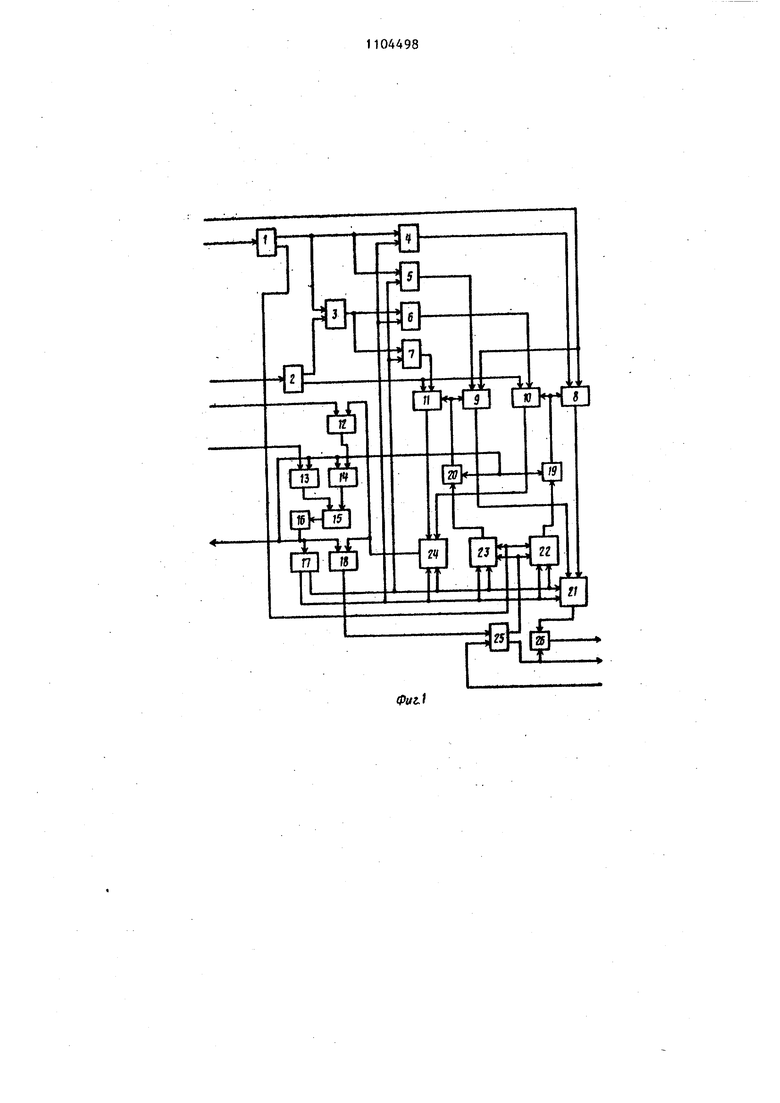

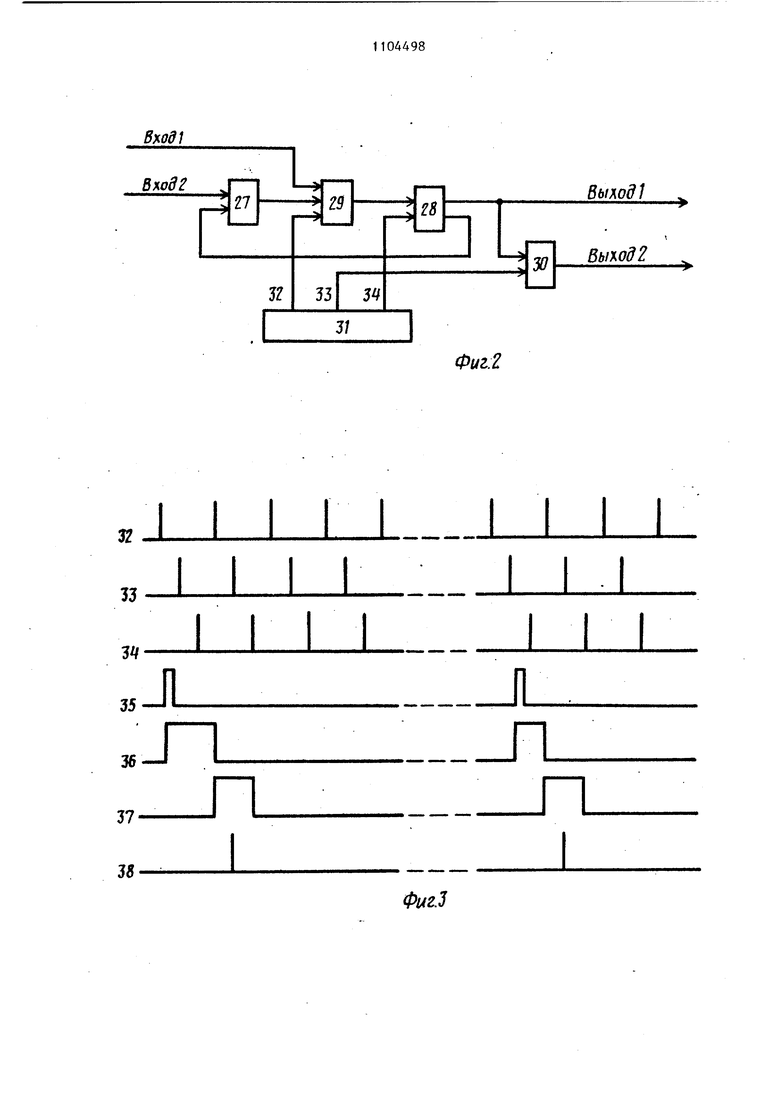

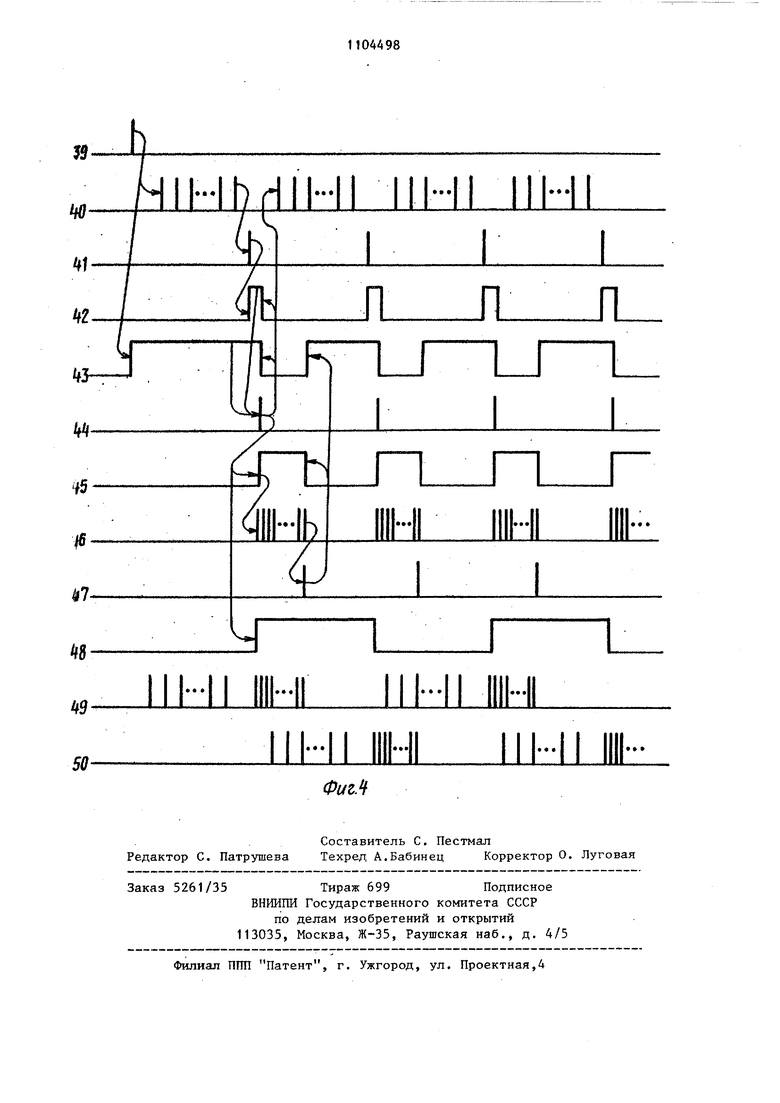

третьего формирователя импульсов является выходом синхроимпульсов устройства и соединен с управляющим входом выходного регистра, выход которого является информационным выходом устройства, выходы третьего и четвертого блоков стековой памяти соединены с информационными входами четвертого коммутатора, выход которого соединен со сбрасывающим выходом четвертого триггера и вторы входом второго элемента ИЛИ, выход второго коммутатора соединен с запускающим входом первого счетчика, выход третьего коммутатора соединен с запускаюпщм входом второго счетчика. На фиг . 1 представлена структурна схема устройства сопряжения; на фиг,2 - пример реализации формирова теля импульсов;на фиг.З - временные диаграммы работы формирователя импульсов на фиг.4 - временные диаграммы работы устройства сопряжения . Устройство сопряжения содержит (фиг.1) первый 1 и второй 2 формирователи импульсов записи, первый элемент ИЛИ 3, первьй 4, второй 5, третий 6 и четвертый 7 элементы И, первый 8, второй 9, третий 10и чет вертьй 11 блоки стековой памяти, второй элемент ИЛИ 12, первый триггер 13, второй триггер 14, пятый элемент И 15, элемент 16 задержки, третий 17 и четвертый 18 триггеры, первый 19 и второй 20 счетчики адресов памяти, первый 21, второй 22, третий 23 и четвертый 24 коммутаторы, третий формирователь 25 импульсов (считывания), выходной регистр 26.. Формирователь импульсов (фиг.2) содержит триггеры 2/ и 28, элементы И 29 и 30, распределитель 31 импульсов, представляющий собой дешифратор , присоединенный к выходу счетчика, подключенного к генератор запускающих сигналов. Первый, второ и третий выходы распределителя импульсов соединены соответственно с первыми входами элементов И 29 и 30 и со сбрасьшающим входом триггера 28.Установочный вход триггера 28 соединен с выходом элемента И 29, второй вход которого соединен с выходом триггера 27. Установочный вхо триггера 27 является первым входом формирователя, а сбрасьгеающий вход соединен с вторым инверсным выходом триггера 28. Первый выход триггера 28 является первым выходом формирователя и соединен с вторым входом элемента И 30, выход которого является вторым выходом формирователя. Блоки 8-11 стековой памяти имеют встроенные дешифраторы для выборки адресов с двоичным адресным входом. Емкость их соответствует максимальному количеству слов в одном массиве информации источника. Первый 8 и второй 9 блокистековой памяти имеют количество каналов с параллельной записью, соответствующее количеству разрядов информационного слова источника. Третий 10 и четвертьй 11 блоки стековой памяти имеют по одному каналу записи. Элемент 16 задержки может быть выполнен в виде одновибратора. Счетчики 19 и 20 адресов памяти представляют собой соединение счетных триггеров с последовательным или параллельным переносом. Коммутаторы 21-24 представляют собой элемент 2И-ИЛИ,, в каждом из которых один вход элемента И является управляющим, другой - информационным. Выходной регистр 26 выполнен на D-триггерах, количество которых соответствует количеству разрядов информационного слова источника. На временных диаграммах (фиг.З) . присутствуют первая 32, вторая 33 и третья 34 серии сдвинутых импульсов, входной сигнал 33 формирователя импульсов, импульсы 36 триггера 27, импульсы 37 на первом выходе формирователя, импульсы 38 на втором выходе формирователя. На временных диаграммах (фиг.4) присутствуют сигнал 39 Пуск, синхроимпульсы 40 сопровождения входной информации, сигнал 41 Останов источника информации, импульсы 42 первого триггера 13, импульсы 43 второго триггера 14, сигнал 44 Начало вижения на первом выходе устройства, импульсы 45 Четвертого триггера 18, импульсы 46 на третьем выхое устройства, сопровождающие выходную информацию, сигнал 47 Конец считывания памяти, импульсы 48 ретьего триггера 17 для переключения блоков стековой памяти, импульсы 49 запуска первого счетчика 19 адресов. импульсы 50 запуска второго счетчика 20 адресов. Устройство сопряжения работает следующим образом. Каждый массив информации, поступающий из источника, например устрой ства управления накопителем на магнитной ленте, записывается в один из двух блоков памяти. При этом из другого блока считывается ранее записанньй предыдущий массив. Процес сы записи и считывания протекают в пределах текущего массива с независимыми скоростями, каждая из которых определяется конкретным типом источника и приемника, и для их согласования цикл приема следующего массива может начаться только после окончания обоих процессов. Дпя правильного функционирования памяти необходимо обеспечить своевре менное переключение сигналов в адрес ных и информационных цепях по .отношению к цепям записи или с читывания. Поэтому входные сигналы устройства сопряжения, связанные с работой блоков памяти, проходят через формирователи 1, 2 и 25 импульсов (фиг.1) на выходах каждого из которых в ответ на входной импульс формируется пара импульсов по фазе согласованных с фазой местных тактовых импульсов, причем фронт импульса на втором выходе задержан относительно фронта импульса на первом выходе. Длительности этих импульсов и расстановка их во времени обусловлены типом применяемой памяти. Импульсы с первого выхода формирователя используются для управления адресными цепями памяти, а импульсы второго выхода для управления цепями записи или считывания. Работой формирователя импульсов (фиг.2) управляют серии 32-34 сдвинутых импульсов, поступающих от распределителя 31 импульсов. Входной сигнал 35, поступающий с произвольной фазой на первый -вход формирователя, устанавливает триггер 27 в единичное состояние 36, которое при отсутствии запрещающего сигнала на втором входе формирователя переписывается через элемент И 29 по импульсу серии 32 на триггер 28. При этом триггер 27 возвращается в нулевое состояние инверсным сигналом триггера 28, а на первом выходе формирователя возникает фронт импульса 37. При совпадении импульсов 33 серии и единичного состояния 37 триггера 28 формируется задержанньй импульс 38 на выходе элемента И 30, являющемся вторым выходом формирователя. По импульсу 34 серии триггер 28 возвращается в нулевое состояние, завершая формирование импульса на первом выходе формирователя. Вторые входы формирователей 1 и 2 (фиг.1) не используются в логических операциях иподключены к цепи постоянного разрешения. В исходном положении первый, второй и четвертьй триггеры находятся в нулевых состояниях 42, 43 и 45 соответственно. Установка в исходное положение производится при включении электропитания и может осуществляться от цепи сброса источника информации через входную логику упомянутых триг- геров. Третий триггер может находиться в произвольном состоянии. Однако для удобства рассмотрения примем его исходное положение также нулевьм 48. Работа устройства сопряжения начинается по сигналу Пуск 39, поступающему из источника информации на вход пуска и устанавливающему триггер 14 в единичное состояние 43 через элемент ИЛИ 12. При этом с информационного входа на информационные входы первого 8 и второго 9 блоков стековой памяти поступает первый непрерывный массив информации, сопровождаемый синхроимпульсами 40 на входе синхронизации устройства и формирователя 1. Импульсы переключения адресов записи с первого выхода формирователя 1 поступают через коммутатор 22 на запускающий вход 49 счетчика 19, при помощи которого осуществляется перебор адресов первого 8 и третьего 10 блоков стековой памяти. При этом запись информации в блок 8 обеспечивается подачей на его управляющий вход импульсов записи с второго выхода формирователя 1 через элемент И 4. Одновременно эти импульсы подаются через элемент ИЛИ 3 и элемент И 6 на управляюЕций вход третьего блока 10 стековой памяти для записи в него нулей по всем адресам за исключением последнего в текущем массиве. В последнем адресе записывается единица в качестве признака окончания массива. Этот признак поступает,на второй вход устройства сопряжения и вход формирователя 2 из источника информации после окончания массива и обы но не сопровождается синхроимпульсом. Поэтому с второго выхода формирователя 2 через элемент ИЛИ 3 и элемент И 6 подается дополнительный импульс записи на управляющий вход третьего блока 10 стековой па- мяти, на информационньй вход которо го действует в этот момент импульс с первого выхода формирователя 2. Одновременно с записью в блок 8 должно осуществляться считывание из блока 9 путем подачи сигналов Запрос информации от приемника на вход Запроса информации устройств и первый вход формирователя 25. Одн

ко при записи первого массива сигналы Запрос информации блокируются по второму входу формирователя 25 сигналом 45 триггера 18, который . находится в нулевом состоянии до окончания записи первого массива. После выработки признака окончания массива движение магнитной ленты ; накопителя прекращается по инициативе его устройства управления сигналом Останов, который подается также в устройство сопряжения наего вход останова и устанавливает в единичное положение 42 триггер 13, сообщая о возможности полз чения из источника следующего массива.

Чтобы получить следующий массив, необходимо магнитную ленту источника вновь привести в движение, для чего с выхода начала обмена устройства сопряжения в источник посылается сигнал 44 Начало движения. Этот сигнал возникает на выходе элемента 16 задержки в результате срабатывания элемента И 15 при совпадении единичных состояний 42 и 43 триггеров 13 и 14, сигнализирующих об окончании как процесса записи текущего, так и процесса считьюания предыдущего массивов. Поскольку при записи первого массива отсутствует предыдущий и процесс считывания блокируется, то триггер 14 заранее установлен в единичное состояние на начальном этапе работы сигналом 39 Пуск.

Сигналом 44 Начало движения триггеры 13 и 14 приводятся в исход1

первого блока 8 стековой памяти и соответствующего ему признака конца из третьего блока 10 стековой памяти Переключение блоков памяти с режима записи на режим считывания и наоборот осуществляется под действием противофазных выходных сигналов триггера 1 7 на элементы И 4-7 и на коммутаторы 21-24.При этом импульсы записи с второго выхода формирователя 1 проходят теперь уже через элементы И 5 и 7, а импульсы переключения адресов записи с первого выхода формирователя 1 проходят через коммутатор 23 на вход 50 счетчика 20. На вход счетчика 19 теперь поступают через коммутатор 22 импульсы переключения адресов считывания, сформированные на первом выходе формирователя 25 по сигналам приемника Запрос .информации. Перебор адресов считывания идет в том же порядке что и при записи (стековая организация памяти). Выходная информация первого блока 8 стековой памяти через коммутатор 21 записывается в выходной регистр 26 импульсами сопровождения выходной информации (импульсами считывания) со второго выхода формирователя 25.

При достижении в процессе считывания последнего адреса массива возникает сигнал 47 Конец считывания памяти на выходе третьего блока 10 стековой памяти. Этот сигнал через коммутатор 24 устанавливает триггер 14 в единичное состояние 43, а триггер 18 - в нулевое 45, прекращая . iP. , ное нулевое состояние. Элемент 16 задержки, который разделяет во времени процессы установки и сброса этих триггеров, создает устойчивость в работе. Сигнал 44 Начало движения подается также на сбрасывающие входы адресных счетчиков 19 и 20 для установки их в исходное состояние, на установочньй вход триггера 18 для снятия запрета считывания 45 с второго входа формирователя 25 на счетный вход триггера 17, который при этом изменяет свое состояние 48 на противоположное. С этого момента начинается запись следующего массива во второй блок 9 стековой памяти и соответствующего ему признака конца в четвертый блок 11 стековой памяти и одновременное считывание предьщущего массива из вьщачу в приемник импульсов А6 сопровождения на выходе синхроимпульсов устройства. При скорости работы приемника вьппе, чем источника, триггер 14 будет ожидать в единичном состоянии окончания записи. Когда триггер 13 по окончании записи также установится в единичное состояние, сработает элемент И 15 и все процессы повторятся при переключенных входных и выходных цепях блоков памяти. При скорости работы 8 приемьика ниже, чем источника, первым установится в единичное состояние триггер 13, ожидая окончания считывания. Таким образом, благодаря введению новых связей и элементов, устройство позволяет передавать информацию от источника, формирующего непрерывные массивы, к приемнику, скорость работы которого отлична от скорости работы источника.

Вмдг

T-TfL

гд

JZ

53

35

Г1

36

Вымд

Bbiwd2

30

0(/г.

(I

:П

A/2.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство сопряжения | 1979 |

|

SU857967A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-03-21—Подача