Изобретение относится к управлению электрическими машинами и может быть использовано для многорежимного управления шаговыми двигателями (ШД).

Цель изобретения - расширение фун- 5 кциональных возможностей путем увеличения числа режимов коммутации и повышения точности отработки заданного перемещения.

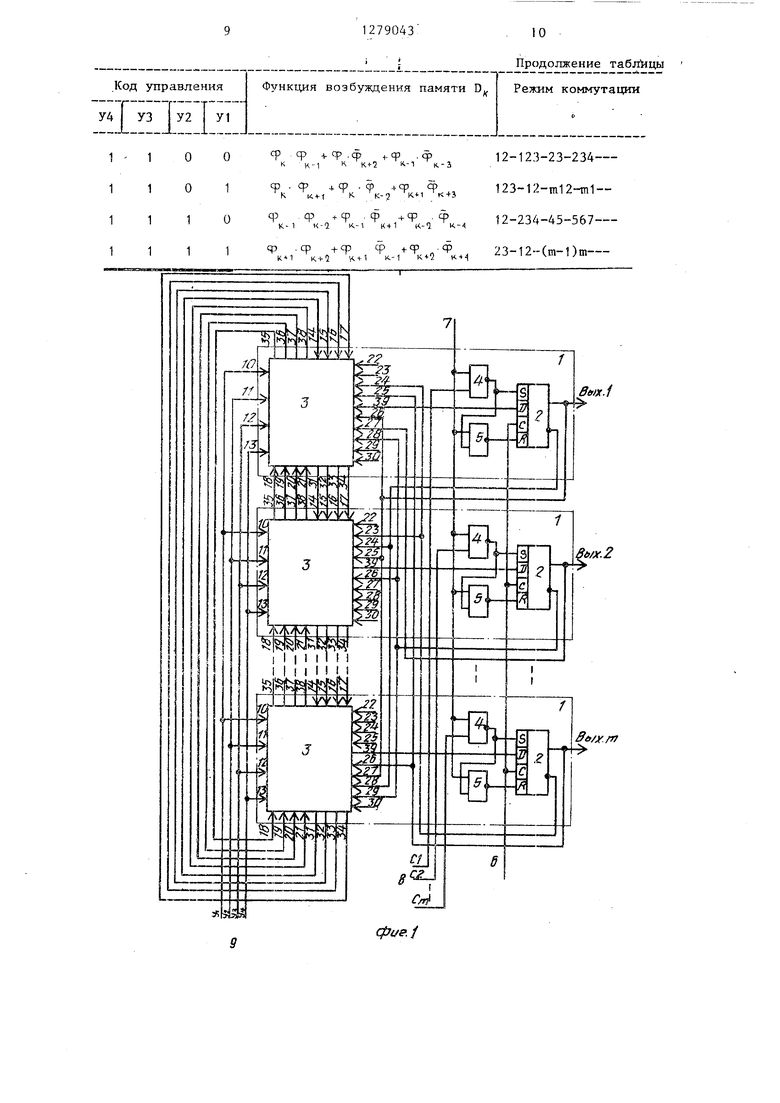

На фиг. 1 представлена функцио- О нальная схема многорежимного распределителя импульсов для управления га- фазным шаговым двигателем, реализующего предлагаемьй способ; на фиг.2(k+S,-1)-я фазы, то при oL, 21Т/га, в (i+1)-M такте k-я фаза будет отключена, (k+1) (k+2)-я (k + S,-1)-я фазы останутся включенными и дополнительно включится (k+S)-я фаза, что обеспечивает шаг коммутации d. 2ir/m и заданное направление переключений. При этом же режиме и t О в (i+1)-M такте отключаются k-я, (k+1)-я и (k+t,)-я фазы; (k + + t + 1), () ,,... ,(k+S,-1) фазы остаются включенными и дополнительно включатся (k-S )-я, (k+S +1)-я,,.. и ()-я фазы,, что обеспечивает

функциональная схема блока формирова- 5 шаг коммутации ;, (t +1) 21Г/т, А

если задано направление Назад, то при соответственно в (1+1)-м такте отключится ()-я фаза, остаются включенными остальные вклю- 20 ченные фазы и дополнительно включится (k-1)-я фаза. При t, 0 отключатся (k+S.-1)-я, ()-я,,.. и ( -1)-я фазы и включатся (k -1)-я (k-2)-я,... и ()-я фа- Числа S, q, OL и направление пере- 25 бы. Если заданы несимметричньш режим

кия функций возбуждения памяти.

Способ осуществляют следующим образом.

В процессе работы ШД изменяют режим коммутации, выбирая очередной режим из множества предусмотренных заданием по числу поочередно включенных фаз S и q и шагу коммутации . .

ключений могут быть заданы в виде кодов управления и определяют состояние Т, i+lj каждой k-й фазы в очередном (i+1)-M такте коммутации в зависимости от заданного направления переключений и состояний (k-1), (k-t-1), (k+q-t-1), (k-S-t-1),(kH-t), (k+t+1), (k-q+t+1), (k+S+t+1) фаз в предыдущем i-м такте коммутации в соответствии с логической функцией перехода

я ,С1-и1 Ф..,1П -(ф,.., ,.-,-1 +

i K-s-bifi -t-iril) Ct)

при направлении переключений Вперед и

9jiH-1 cp, (9,.i4ib--V ttib

+ Ф, .t

MS+ttt 1

45 ..., (k+t 2)-я фазы и включатся (k+S, + 1)-я,.. . , ()-я фазы При t., О и направлении Назад

при направлении Назад, где t с т/2П-1 - целое неотрицательное число; q S 1 - при симметричном .и q S+1 . 1 при несимметричном ре- 50 (k+S,J-1)-я и дополнительно включав соответствии с выражением (2) в (i+1)-M такте отключаются (k+S-t )жимах коммутации, t т/2 при четном m и 1(т+1)/2 при нечетном т, эл. град.

Например, если заданы симметрич- ньй режим коммутации с параметрами

,q S,p(. и направление переключений Вперед и в i-м такте коммута,ции были включены k-я, (k+1)тя,..,,

ются (k-t,.,-1)-я,.. . , (k-1)-я фазы, а в (i+2)-M такте отключаются (k+S,j- -2t,-1)-я, (,J)-я,..., ( -t-1)-я фазы и дополнительно вклю- 55 чаются (k-2t2-1)-я, (k-2t )-я,.,., (k-t,J-2)-я фазы.

Таким образом, обеспечиваются за данное число поочередно включенных

(k+S,-1)-я фазы, то при oL, 21Т/га, в (i+1)-M такте k-я фаза будет отключена, (k+1) (k+2)-я (k + S,-1)-я фазы останутся включенными и дополнительно включится (k+S)-я фаза, что обеспечивает шаг коммутации d. 2ir/m и заданное направление переключений. При этом же режиме и t О в (i+1)-M такте отключаются k-я, (k+1)-я и (k+t,)-я фазы; (k + + t + 1), () ,,... ,(k+S,-1) фазы остаются включенными и дополнительно включатся (k-S )-я, (k+S +1)-я,,. и ()-я фазы,, что обеспечивает

шаг коммутации ;, (t +1) 21Г/т, А

коммутации с параметрами S

г

Ч,

32+1,оС5И п i-M такте бьти включены S фаз с номерами k, (k+1),.,., (), то при направлении переключения Вперед в соответствии с выражениями (1), при t,j О в (i+1)-M такте коммутаций все S фазы останутся включенными и дополнительно ключится (k+S,J)-я фаза, в (1+2)-м

такте отключится k-я фаза, а при наравлении переключений Назад в (i+1)-M такте дополнительно включится (k-1)-я фаза, а в (1+2)-м такте отлючится (k+S2-1)-я фаза. При tj О

направлении Вперед в (1+1)-м так- те отключаются k-я, (k+1)-я,... и (k+t,J-1)-я фазы и включ аются (k+S-)-я, ..., ( )-я фазы, в (i-2)-M такте отключатся (k+t )-я,, (k+t,J+f)-я,

..., (k+t 2)-я фазы и включатся (k+S, + 1)-я,.. . , ()-я фазы. При t., О и направлении Назад

(k+S,J-1)-я и дополнительно включа(k+S,J-1)-я и дополнительно включав соответствии с выражением (2) в (i+1)-M такте отключаются (k+S-t )я.

50 (k+S,J-1)-я и дополнительно включаются (k-t,.,-1)-я,.. . , (k-1)-я фазы, а в (i+2)-M такте отключаются (k+S,j- -2t,-1)-я, (,J)-я,..., ( -t-1)-я фазы и дополнительно вклю- 55 чаются (k-2t2-1)-я, (k-2t )-я,.,., (k-t,J-2)-я фазы.

Таким образом, обеспечиваются заданное число поочередно включенных

фаз, шаг коммутации и направление переключений.

Если в момент начала перехода с одного режима на другой были включены г фаз с номерами k, (k+1),.., (k+r-1) и требуется переход на режим коммутации с параметрами S , q и oLj , то при приходе очередного тактового импульса число включенных фаз при БЗ г увеличивается на единицу и будут включены фазы с номерами (k+t р , (k+tj + 1) ,.. . ,(k+t.j+r) при направлении Вперед и .с номерами (k-t -1) ,.,. , (k-t -ьг-) при направлении Назад, а при q г чис- ло включенных фаз уменьшается на единицу и в соответствии с вьфажени- ями (1) и (2) будут включены (k+t+-1 (k+tJ+2),...,(k+t3+r+1) фазы при направлении Вперед и (k-t ,) , (k - -t3+1),,..,(k-t +Г-2) при направлении Назад.

Таким образом, за такты перехода с одного режима на другой шаг коммутации ()7r/m переключения фаз производятся по заданному направлению и происходит с каждым тактом коммутации изменение числа включенных фаз. .

При достижении заданного числа S 3 или q J распределение тактовых импульсов начинает производиться по описанному режиму, соответствующему заданным S , q и (t +1) 21Г/т.

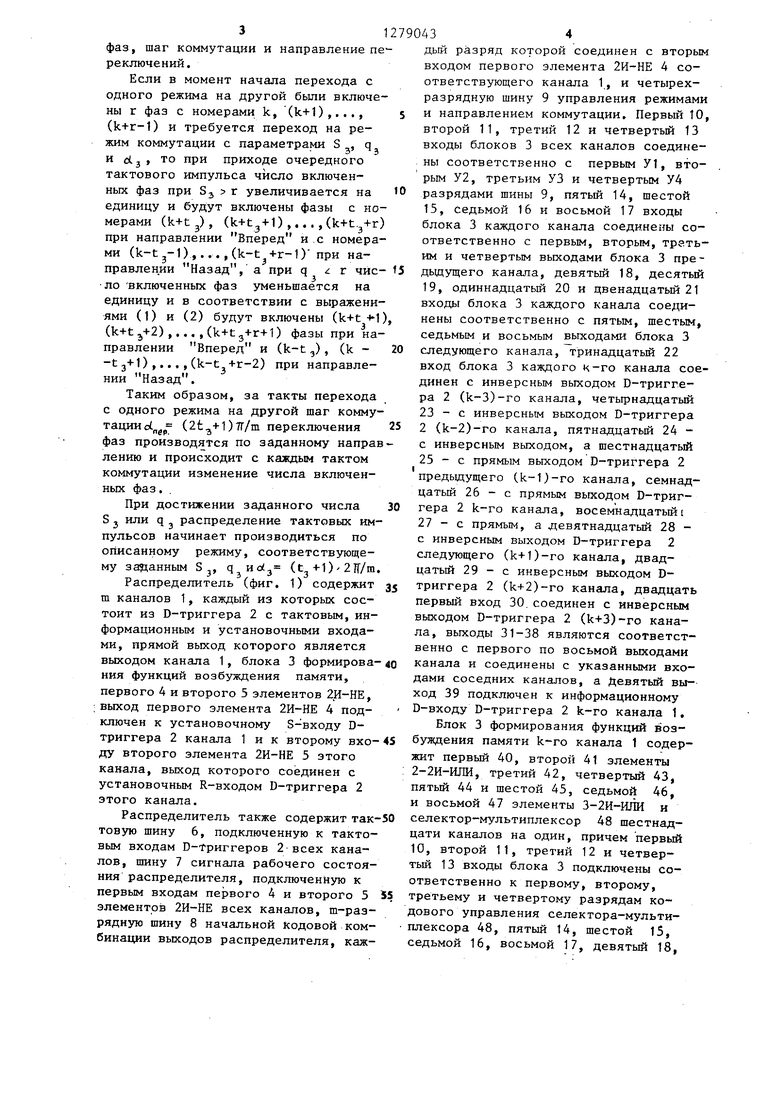

Распределитель (фиг. 1) содержит m каналов 1, каждый из которых состоит из D-триггера 2 с тактовым, информационным и установочными входами, прямой выход которого является выходом канала 1, блока 3 формирова- ния функций возбуждения памяти, первого 4 и второго 5 элементов 2И-НЕ, ; выход первого элемента 2И-НЕ 4 подключен к установочному S-входу D- триггера 2 канала 1 и к второму вхо- ду второго элемента 2И-НЕ 5 этого канала, выход которого соединен с установочным R-входом D-триггера 2 этого канала.

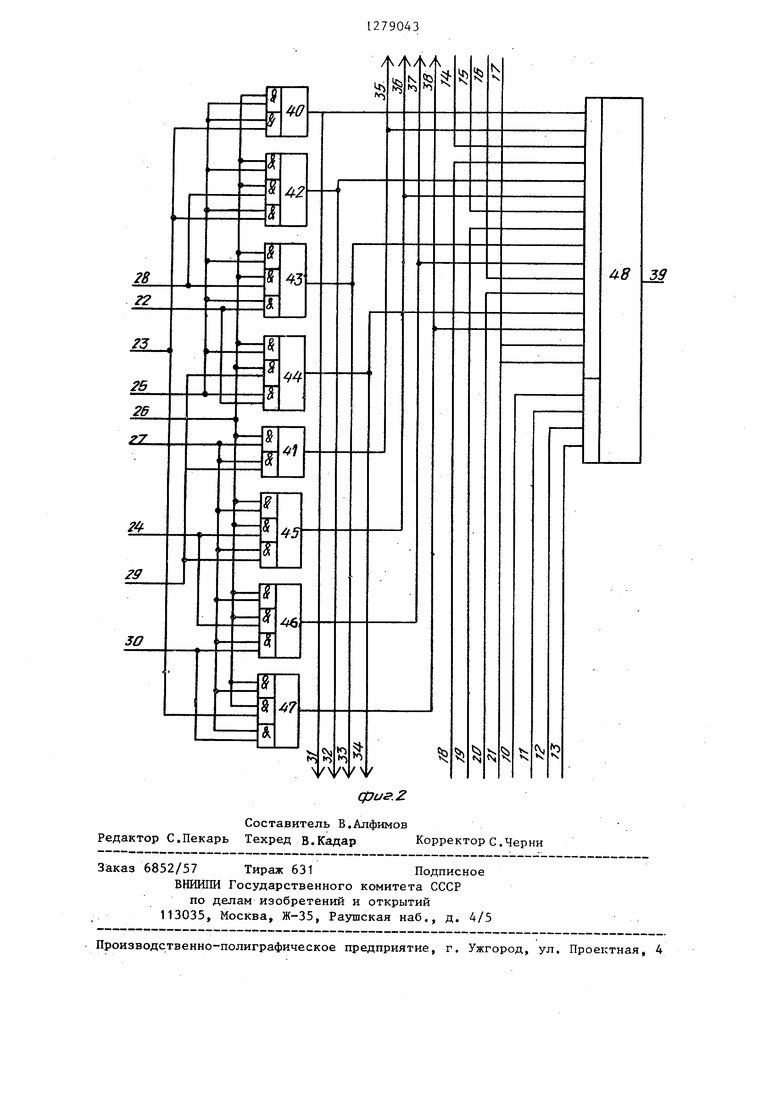

Распределитель также содержит тактовую шину 6, подключенную к тактовым входам D-Триггеров 2-всех каналов, шину 7 сигнала рабочего состояния распределителя, подключенную к первым входам первого 4 и второго 5 элементов 2И-НЕ всех каналов, т-раз- рядную шину 8 начальной Кодовой комбинации выходов распределителя, каждый разряд которой соединен с вторым входом первого элемента 2И-НЕ 4 соответствующего канала 1, и четырехразрядную шину 9 управления режимами и направлением коммутации. Первый 10 второй 11, третий 12 и четвертый 13 входы блоков 3 всех каналов соединены соответственно с первым У1, вторым У2, третьим УЗ и четвертым У4 разрядами шины 9, пятый 14, шестой 15, седьмой 16 и восьмой 17 входы блока 3 каждого канала соединены соответственно с первым, вторым, третьим и четвертым выходами блока 3 пре- дьщущего канала, девятый 18, десятый 19, одиннадцатый 20 и двенадцатый 21 входы блока 3 каждого канала соединены соответственно с пятым, шестым, седьмым и восьмым выходами блока 3 следующего канала, тринадцатьш 22 вход блока 3 каждого к-го канала соединен с инверсным выходом D-триггера 2 (k-3)-ro канала, четырнадцатый 23 - с инверсным выходом D-триггера 2 (k-2)-ro канала, пятнадцатьш 24 - с инверсным выходом, а шестнадцатый 25 - с прямым выходом D-триггера 2 предьщущего Ck-1)-ro канала, семнадцатый 26 - с прямым выходом D-триггера 2 k-ro канала, восемнадцатый 27 - с прямым, а девятнадцатый 28 - с инверсным выходом D-триггера 2 следующего (k+1)-го канала, двадцатый 29 - с инверсным выходом D- триггера 2 (k+2)-ro канала, двадцать первый вход 30.соединен с инверсным выходом D-триггера 2 (k+3)-ro канала, выходы 31-38 являются соответственно с первого по восьмой выходами канала и соединены с указанными входами соседних каналов, а Девятый вы- ход 39 подключен к информационному D-входу D-триггера 2 k-ro канала 1, Блок 3 формирования функций возбуждения памяти k-ro канала 1 содержит первый 40, второй 41 элементы 2-2И-ИЛИ, третий 42, четвертый 43, пятый 44 и шестой 45, седьмой 46, и восьмой 47 элементы 3-2И-ИЛИ и селектор-мультиплексор 48 шестнадцати каналов на один, причем первый 10, второй 11, третий 12 и четвертый 13 входы блока 3 подключены соответственно к первому, второму, третьему и четвертому разрядам кодового управления селектора-мультиплексора 48, пятый 14, шестой 15, седьмой 16, восьмой 17, девятый 18,

десятый 19, одиннадцатый 20 и двенадцатый 21 входы блока 3 подключены соответственно к третьему, седьмому, одиннадцатому, пятнадцатому, четвертому, восьмбму, двенадцатому и шестнадцатому входам селектора- мультиплексора 48, тринадцатый 22 вход блока 3 соединен с четвертыми входами третьего 42 и четвертого 43 элементов 2-2И-ИЛИ, четырнадцатый 23 вход блока 3, - с четвертыми входами первого 40 и второго 41 и с вторым входом восьмого 47 элементов 2-2И-ИЛИ, пятнадцатый 24 вход блока 3-е вторыми входами шестого 45 и седьмого 46 элементов 3-2И-ИЛИ, шестнадцатый 25 вход блока 3-е третьими входами первого 40, второго 41, третьего 42 и четвертого 43 и с вторым входом первого 40 элементов, семнадцатый 26 вход блока 3-е первыми входами всех элементов 2-2И-ИЛИ и 3-2И-ИЛИ, восемнадцатый 27 вход блока 3 - с третьими входами пятого 44, шестого 45, седьмого 46 и восьмого 47 и с вторым входом пятого 44 элементов 3-2И-ИЛИ, девятнадцатый 28 вход блока 3-е вторыми входами второго 41 и третьего 42 элементов ИЛИ, двадцатый 29 вход блока 3-е вторым входом четвертого 43 и с четвертыми входами пятого 44 и шестого 45 элементов 3-2И-ИЛИ, а двадцать первьй 30 вход блока.3 подключен к четвертым входам седьмого 46 и воеьмого 47 элементов 3-2И-ИЛИ, выход первого 40 элементов 2-2И-И11И подключен к первому входу селектора-мультиплексора 48 и к первому 31 выходу блока 3, выход второго 41 - к пятому входу селектора-мультиплексора 48 и к второму 32 выходу блока 3, выход третьего 42 - к девятому входу селектора- мyльтиплieкcopa 48 и к третьему 33 выходу блока 3, выход четвертого 43 - к тринадцатому входу селектора-мультиплексора 48 и к четвертому 34 выходу блока 3, выход пятого 44 - к второму входу селектора-мультиплексора 48 и к пятому 35 выходу блока

3, выход шестого 45 - к -шестому вхо- ду селектора-мультиплексора 48 и к шестому 36 выходу блока 3, выход седьмого 46 - к десятому входу селектора-мультиплексора 48 и к седьмому 37 выходу блока 3, выход восьмого 47 - к четырнадцатому входу се o

лектора-мультиплексора 48 к к восьмому 38 выходу блока 3, а выход селектора-мультиплексора 48 подключен к девятому 39 выходу блока 3,

Раепределитель работает следующим образом.

В начальном состоянии на т-раз- рядную шину 8 начальной кодовой комбинации выходов распределителя (С1,

С2 С

С) подается код.

5

0

5

0

5

5

5

каждый k-й из т-разряДов которого идентичен требуемому исходному еос- тоянию выхода k-ro канала распределителя. После включения питания на шине 7 сигнала рабочего состояния распределителя имеется уровень логической 1, на выходе первого 4 элемента 2И-НЕ каждого k-ro канала 1 - инверсия сигнала С исходного состояния выхода k-ro канала 1, на выходе второго 5 элемента 2И-НЕ k-ro канала 1 - сигнал, идентичньм С, следовательно, состояние выхода D- триггера 2 k-ro канала 1 идентично сигналу С и кодовая комбинация на выходах распределителя идентична заданной на разрядах шины 8 начальной кодовой комбинации выходов распределителя ,

Коммутация выходов распределителя осуществляется после переключения сигнала, рабочего состояния на шине 7 в логический О тактовыми импульсами, поступающими по тактовой шине 6.

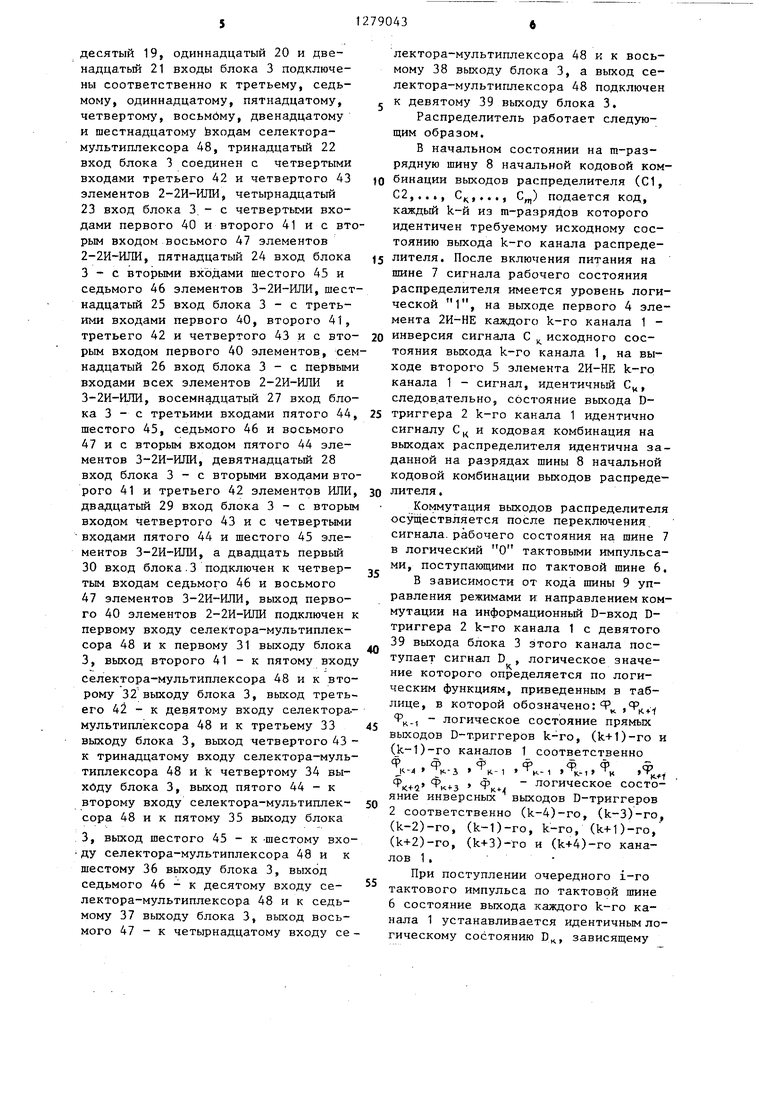

В зависимости от кода шины 9 управления ре.жимами и направлением коммутации на информационньй D-вход D- триггера 2 k-ro канала 1 с девятого 39 выхода блока 3 этого канала поступает сигнал D , логическое значение которого определяется по логическим функциям, приведенным в таблице, в которой обозначено: Ф , Ф., - логическое еостояние прямых выходов D-т.риггеров k-ro, (k+1)-ro и (k-1)-ro каналов 1 соотв етственно Ф Ф Ф Ф Ф Ф й

l.-i K-l К- 1 Vl К H.f.y

Ф Ф i, « Ф логическое состо +Ч к-1-3

яние инверсных выходов D-триггеров 2 соответственно (k-4)-ro, (k-3)-ro, (k-2)-ro, (k-l)-ro, k-ro, (k+1)-ro, (k+2)-ro, (k+3)-ro и (k+4)-ro каналов 1 .

При поступлении очередного i-го тактового импульса по тактовой шине 6 состояние выхода каждого k-ro канала 1 устанавливается идентичным логическому состоянию D, зависящему

от кодовой комбинации выходов распределителя в (i-l)-M такте,

Предлагаемое выполнение распределителя обеспечивает многорежимное управление т-фазным шаговьм двигателем и возможность перехода из любого режима коммутации к другим в процессе работы шагового двигателя без потери информации и без отработки ложных шагов.

Формула изобретения

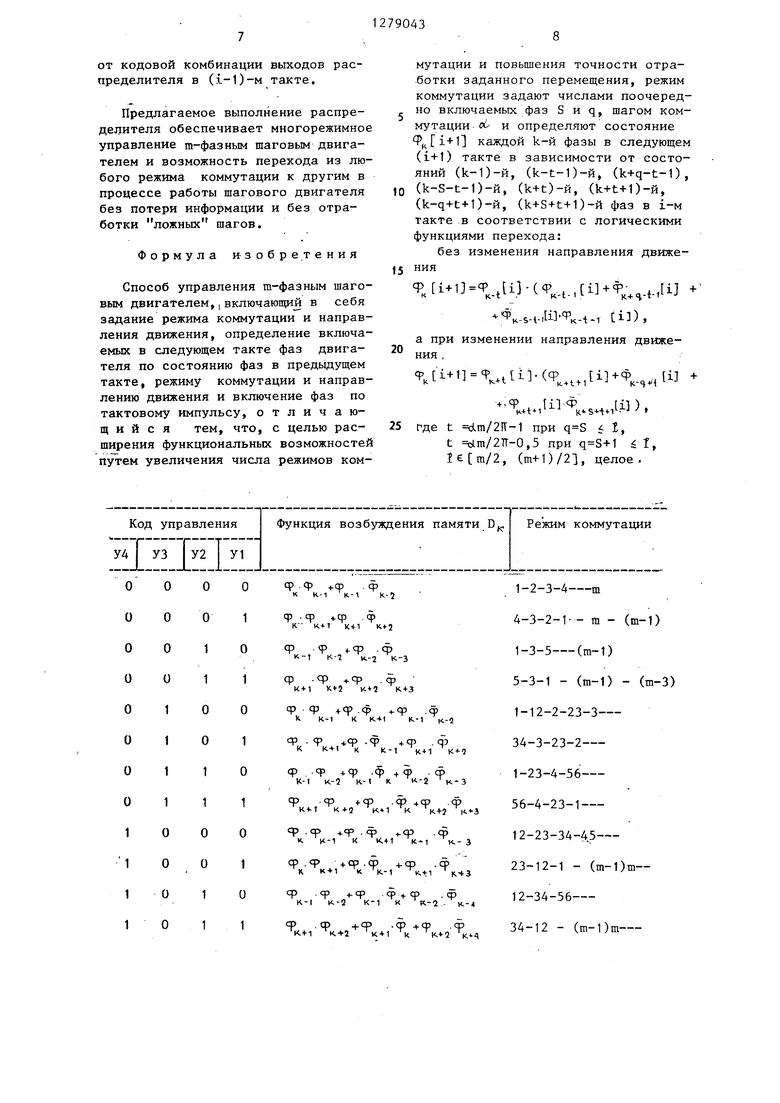

Способ управления т-фазным шаговым двигателем,,включающий в себя задание режима коммутации и направления движения, определение включаемых в следующем такте фаз двигателя по состоянию фаз в предыдущем такте, режиму коммутации и направлению движения и включение фаз по тактовому импульсу, отличающийся тем, что, с целью расширения функциональных возможностей путем увеличения числа режимов коммутации и повьшения точности отра- .ботки заданного перемещения, режим коммутации задают числами поочеред- но включаемых фаз S и q, шагом коммутации ос- и определяют состояние KCi+ll каждой k-й фазы в следующем (i+1) такте в зависимости от состояний (k-1)-й, (k-t-1)-й, (k+q-t-1),

(k-S-t-1)-й, (k+t)-й, ()-й, (k-q+t+1)-й, (k+S+t+1)-й фаз в i-м такте в соответствии с логическими функциями перехода:

без изменения направления движения

.дд-(Ф.,.,.,.д1 V

K-s-t-. ti),

20

а при изменении направления движения ,

VJil-(..,.,,-,.Hi .tMtil- K sW-i. Где t при I,

t Ыт/2Я-0,5 при i Г, , (m+1)/2l, целое .

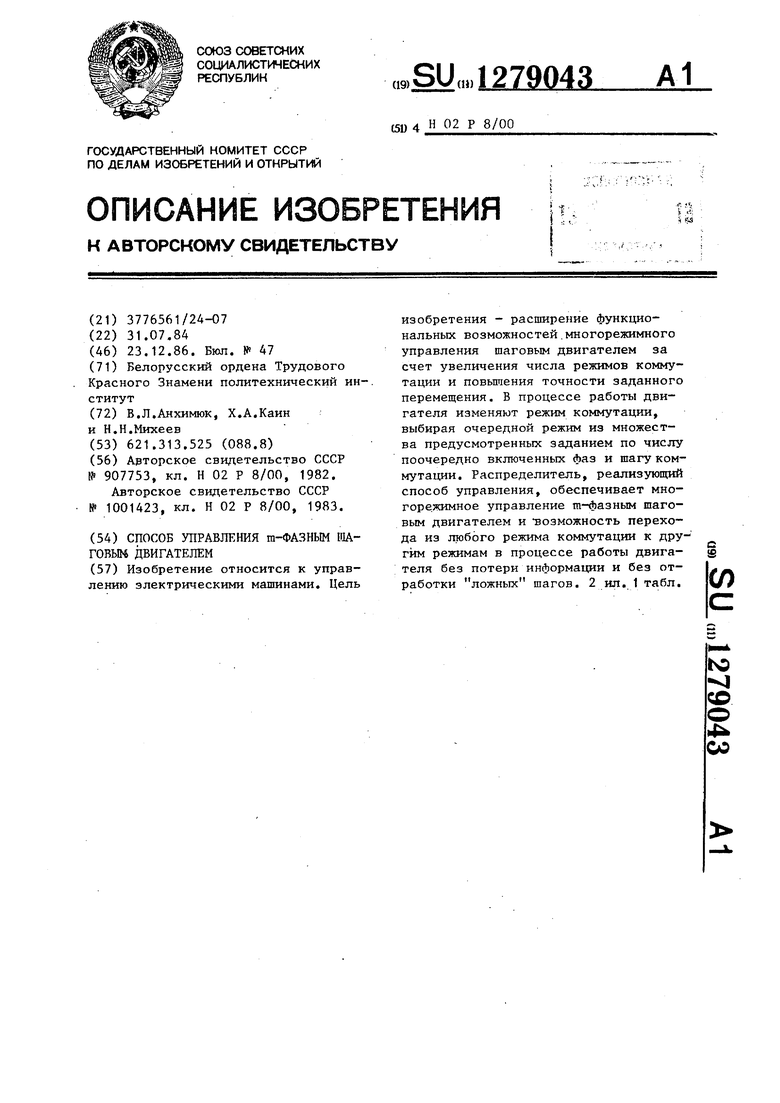

Код управления

Функция возбуждения памяти D.

У4 УЗ У2

У1

ОО

О1

1О

11

Ср , СП ч- Ср . ф1. ф . ф

к к-1 К - I--ф.ф +ф.ф +ф q Ч к V2

Ср . ф + ф . ф + ф . ф к-1 к-2 к-1 к+1 «-1 к-4

ф .ф +ф ф 1-ф.ф К.+ 5 х

1279043

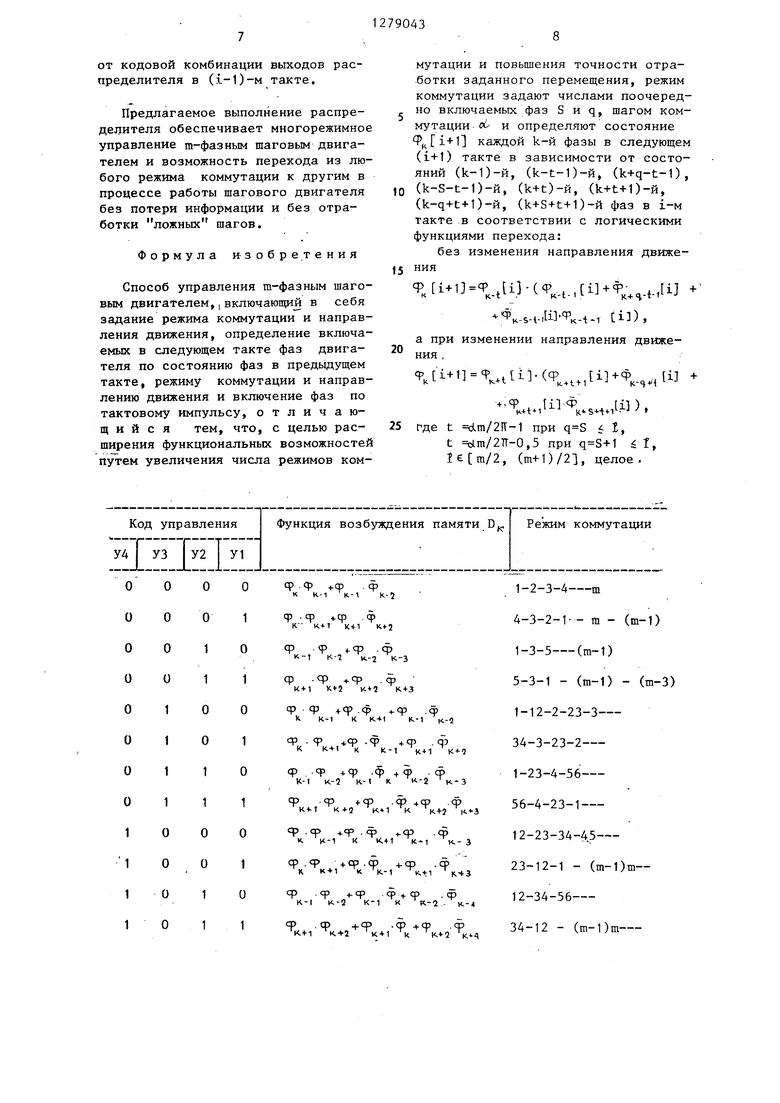

10 Продолжение таблицы

Режим коммутации

12-123-23-234- 123-12-ra12 m1- 12-234-45-567- 23-12--(m-1)m-

fTf

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальный трехрежимный распределитель импульсов для управления шаговым двигателем | 1984 |

|

SU1275734A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1109735A1 |

| Преобразователь постоянного напряжения в квазисинусоидальное с промежуточным высокочастотным преобразованием | 1986 |

|

SU1417144A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

Изобретение относится к управлению электрическими машинами. Цель изобретения - расширение функциональных возможностей.многорежимного управления шаговым двигателем за счет увеличения числа режимов коммутации и повьшгения точности заданного перемещения. В процессе работы двигателя изменяют режим коммутации, выбирая очередной режим из множества предусмотренных заданием по числу поочередно включенных фаз и шагу коммутации. Распределитель, реализующий способ управления, обеспечивает мно- горе.жимное управление т-фазным шаговым двигателем и возможность перехода из любого режима коммутации к другим режимам в процессе работы двигателя без потери информации и без отработки ложных шагов. 2 ил. 1 табл. с (Л ю sj СО о 4 00

| Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем | 1980 |

|

SU907753A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1981 |

|

SU1001423A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-12-23—Публикация

1984-07-31—Подача