Поставленная цель достигается тем, что процессор содержит первьй блок оповещения 1, первый регистр 2, второй блок оповещения 3, второй регистр 4j третий блок оповещания 5, третий регистр 6, четвертый блок оповещания 7, четвертый регистр 8, два решающих блока 9 и 10, блок 11 памяти данных, пятый и шестой регист

1

Изобретение относится к вычислительной технике и предназначено для построения матричных вычислительных структур, ориентированных на решение дифференциальных уравнений в частных производных.

Цель изобретения - расширение функциональных возможностей путем выполнения различных типов итерационных процедур численного решения дифференциальных уравнений .в частных производных.

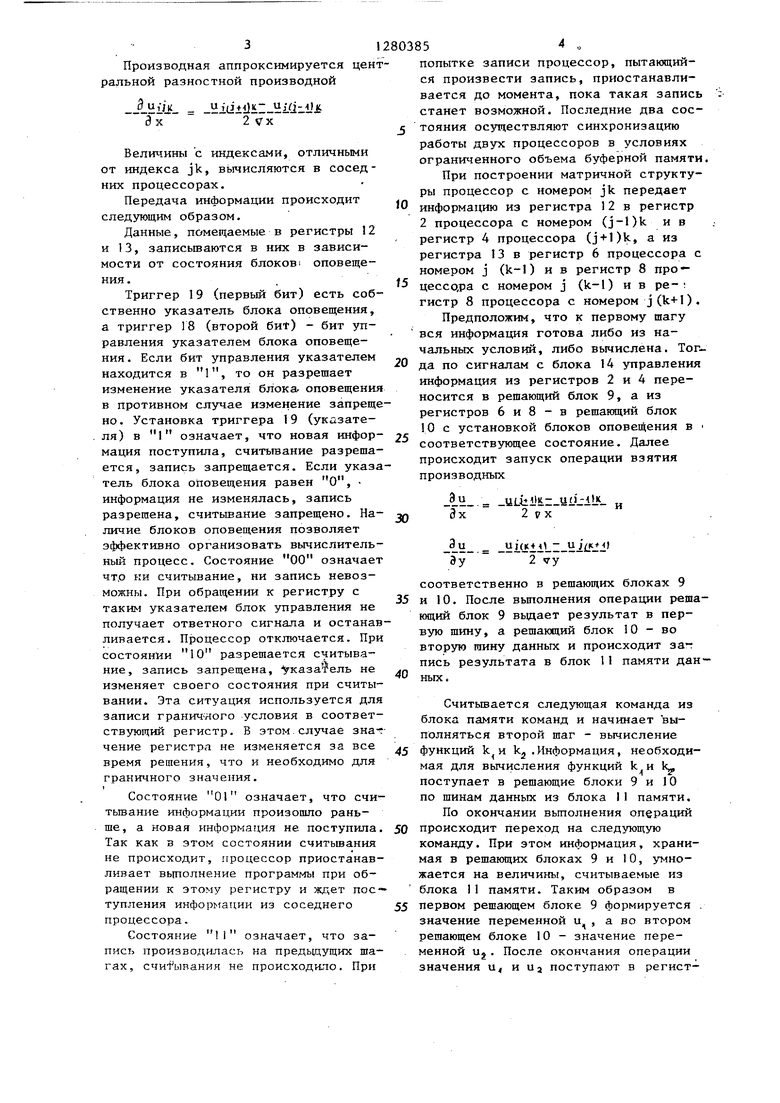

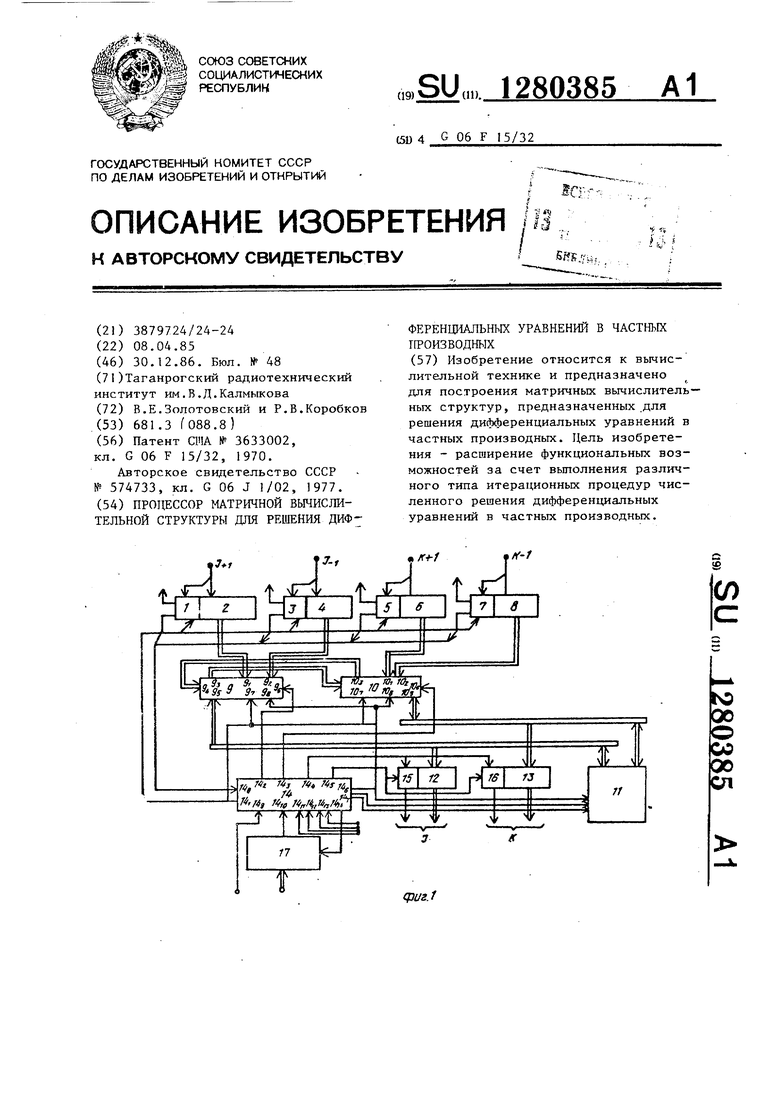

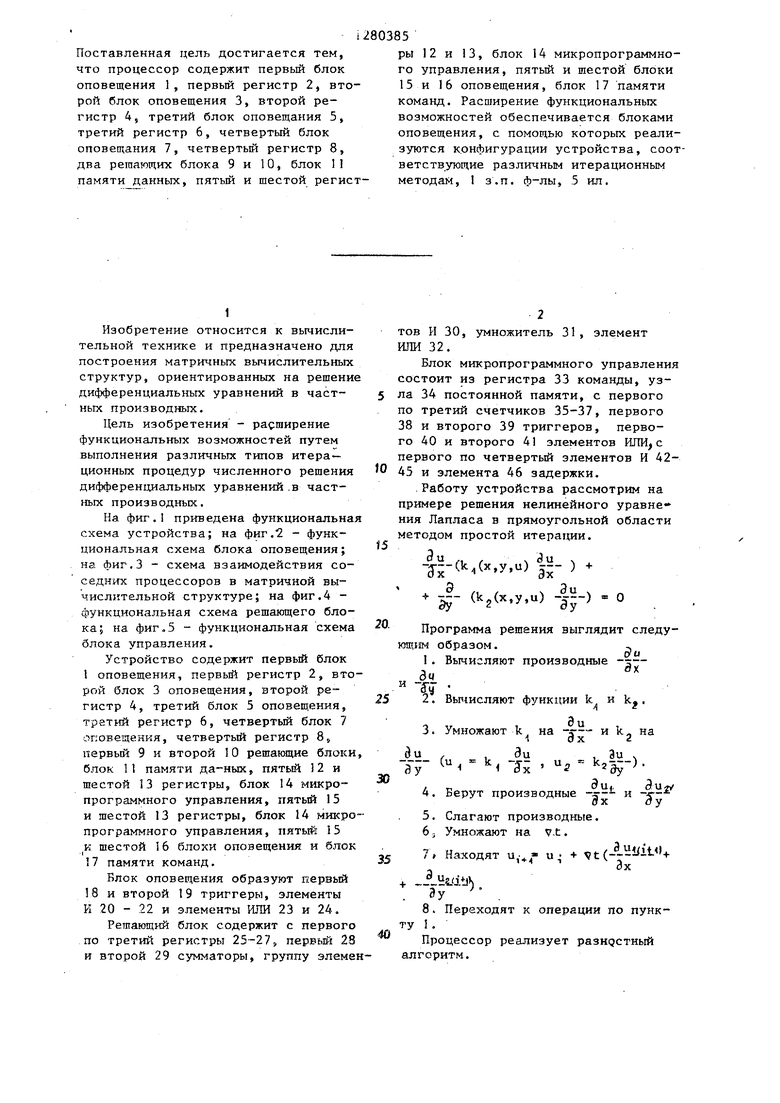

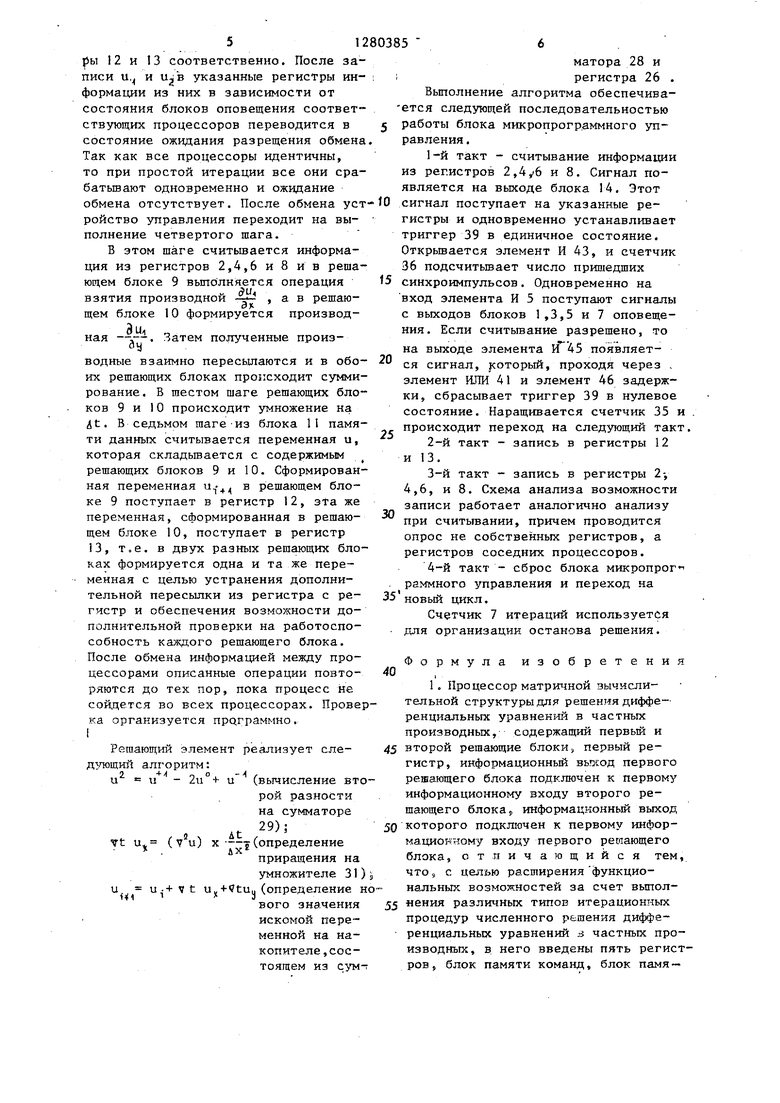

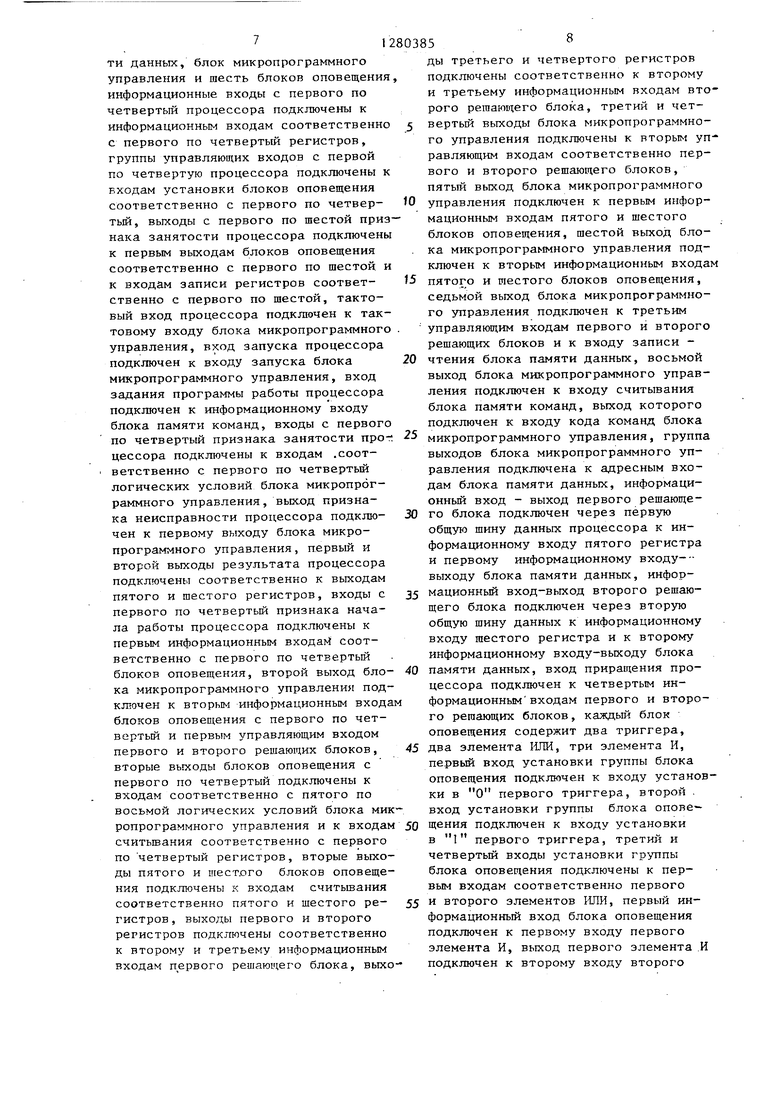

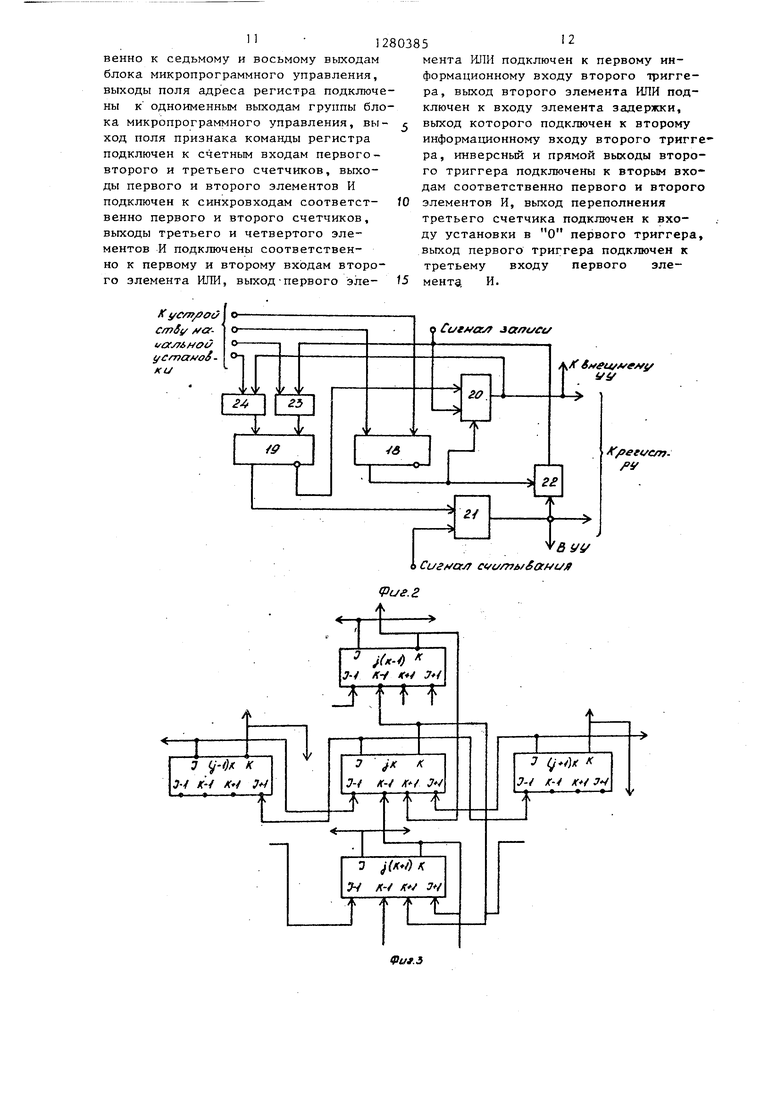

На фиг. приведена функциональная схема устройства; на фиг.2 - функциональная схема блока оповещения; на фиг.3 - схема взаимодействия соседних процессоров в матричной вычислительной структуре; на фиг.4 - функциональная схема решающего блока ; на фиг.5 - функциональная схема блока управления.

Устройство содержит первый блок I оповещения, первый регистр 2, второй блок 3 оповещения, второй регистр 4, третий блок 5 оповещения, третий регистр 6, четвертьй блок 7 оповещения, четвертый регистр 8, первый 9 и второй 10 решающие блоки блок 11 памяти да-ных, пятьй 12 и шестой 13 регистры, блок 14 микропрограммного управления, пятый 15 и шестой 13 регистры, блок 14 микропрограммного управления, пятьш 15 к шестой 16 блоки оповещения и блок 17 памяти команд.

Блок оповещения образуют первый 8 и второй 19 триггеры, элементы К 20 - 22 и элементы ИЛИ 23 и 24.

Решающий блок содержит с первого по третий регистры 25-27, первьш 28 и второй 29 сумматоры, группу элеме80385

ры 12 и 13, блок 14 микропрограммного управления, пятый и шестой блоки 15 и 16 оповещения, блок 17 памяти команд. Расширение функциональных возможностей обеспечивается блоками оповещения, с помощью которых реализуются конфигурации устройства, соответствующие различным итерационным методам, 1 з.п. ф-лы, 5 ил.

5

тов и 30, умножитель 31, элемент ИЛИ 32.

Блок микропрограммного управления состоит из регистра 33 команды, узла 34 постоянной памяти, с первого по третий счетчиков 35-37, первого 38 и второго 39 триггеров, первого 40 и второго 41 элементов первого по четвертый элементов И 42- 45 и элемента 46 задержки.

Работу устройства рассмотрим на примере решения нелинейного уравнения Лапласа в прямоугольной области методом простой итерации.

Эй., ., , (3 U ч . -g---(k,(x,y,u) -- )

.5,. , .Эи«

(k,,(x,y,u) -j--) « о

ay

Эу

20.

25

Программа решения выглядит следующим образом.д

1.Вычисляют производные -ч-

-|.

2,Вьтисляют функции k, и k,,

Умножают k

Эй

на -5-- и k, Эх;

на

0

. Зи k -тU,

du ,

-;;(и J к . -jЗУ ОХ

4. Берут производные

Эй W

и ---

2 а,. )

t

Эх

5. Слагают производные. 6 3 Умножают на 7,t.

Эу

7 Находят и,- u; t(

us- iti)). ЗУ

JLyifit i+ Эх

8. Переходят к операции по пункту 1 .

Процессор реализует разидстный

алгоритм.

Производная аппроксимируется центральной разностной производной

ui(jiilil Hi(i::.l l

Э х 2 сх

Величины с индексами, отличными от индекса jk, вьиисляются в соседних процессорах.

Передача информации происходит следующим образом.

Данные, помещаемые в регистры 12 и 13, записьгоаются в них в зависимости от состояния блоков оповещения.

Триггер 19 (первый бит) есть собственно указатель блока оповещения, а триггер 18 (второй бит) - бит управления указателем блока оповещения. Если бит управления указателем находится в 1, то он разрешает изменение указателя блока оповещения в противном случае изменение запрещено. Установка триггера 19 (указателя) в 1 означает, что новая инфор- мация поступила, считывание разрешается, запись запрещается. Если указатель блока оповещения равен О, информация не изменялась, запись разрешена, считывание запрещено. На- личие блоков оповещения позволяет эффективно организовать вычислительный процесс. Состояние 00 означает чтр ки считывание, ни запись невозможны. При обращении к регистру с таким указателем блок управления не получает ответного сигнала и останавливается. П зоцессор отключается. При состоянии 10 разрешается считывание, запись запрещена, Указатель не изменяет своего состояния при считывании. Эта ситуация используется для записи граниЧ Лого условия в соответствующий регистр. В этом, случае зна-г чение регистра не изменяется за все время решения, что и необходимо для

граничного значения. I

Состояние 01 означает, что счи- тьтание информации произошло раньше, а новая информация не поступила. Так как в этом состоянии считывания не происходит, .процессор приостанавливает вьшолнение программы при обращении к этому регистру и ждет поступления информации из соседнего процессора.

Состояние М означает, что запись производилась на предьщущих шагах, c4HfbiBaHHH не происходило. При

попытке записи процессор, пытающийся произвести запись, приостанавливается до момента, пока такая запись станет возможной. Последние два состояния осуществляют синхронизацию работы двух процессоров в условиях ограниченного объема буферной памяти

При построении матричной структуры процессор с номером jk передает информацию из регистра 12 в регистр 2 процессора с номером (j-l)k ив регистр 4 процессора (j + Ok, а из регистра 13 в регистр 6 процессора с номером j (k-1) и в регистр 8 про - цессо,ра с номером j (k-1) и в ре-; гистр 8 процессора с номером j(k+1).

Предположим, что к первому шагу вся информация готова либо из начальных условий, либо вычислена. Тогда по сигналам с блока 14 управления информация из регистров 2 и 4 переносится в решающий блок 9, а из регистров 6 и 8 - в решанлдий блок 10 с установкой блоков оповещения в соответствующее состояние. Далее происходит запуск операции взятия производных

uLiiii i.r Ul :l JL Эх 2 V X

и

9и ) Эу 2 vy

соответственно в решающих блоках 9 и 10. После выполнения операции решающий блок 9 выдает результат в первую шину, а решающий блок 10 - во вторую шину данных и происходит запись результата в блок 11 памяти дан ных.

Считывается следующая команда из блока памяти команд и начинает выполняться второй шаг - вычисление функций kj .Информация, необходимая для вычисления функций k и k, поступает в решающие блоки 9 и 10 по шинам данных из блока I1 памяти.

По окончании вьтолнения операций происходит переход на следующую команду. При этом информация, хранимая в решающих блоках 9 и 10, умножается на величины, считываемые из блока 11 памяти. Таким образом в первом решающем блоке 9 формируется . значение переменной и, а во втором решающем блоке 10 - значение переменной Uj. После окончания операции значения и и Uj поступают в регист51280385

|5ы 12 и 13 соответственно. После записи и, и Uj в указанные регистры ин- ; i

формации из них в зависимости от состояния блоков оповещения соответ™ ствующих процессоров переводится в состояние ожидания разрещения обмена. Так как все процессоры идентичны, то при простой итерации все они сра- батьюают одновременно и ожидание

матора 28 и

iрегистра 26

Выполнение алгоритма обеспечива бтся следующей последовательностью работы блока микропрограммного управления .

1-й такт - считывание информаци из регистров 2, и 8. Сигнал появляется на выходе блока 14. Этот

обмена отсутствует. После обмена уст-10 сигнал поступает на указанные реройство управления переходит на вы- полнение четвертого шага.

В этом шаге считывается информация из регистров 2,4,6 и 8 ив решающем блоке 9 выполняется операция взятия производной , а в решающем блоке 10 формируется производная --,--. Затем полученные производные взаимно пересылаются и в обоих решающих блоках происходит суммирование. Б шестом шаге решающих блоков 9 и 10 происходит умножение на At. В седьмом шаге-из блока 11 памяти данных считывается переменная и, которая складьюается с содержимым решающих блоков 9 и 10. Сформированная переменная в решающем блоке 9 поступает в регистр 12, зТа же переменная, сформированная в решающем блоке 10, поступает в регистр 13, т.е. в двух разных решающих блоках формируется одна и та же переменная с целью устранения дополнительной пересылки из регистра с регистр и обеспечения возможности дополнительной проверки на работоспособность каждого решающего блока. После обмена информацией между процессорами описанные операции повторяются до тех пор, пока процесс не сой,цется во всех процессорах. Проверка организуется праграммно. I

Решающий элемент реализует следующий алгоритм:

„г+- п .0

гистры и одновременно устанавливает триггер 39 в единичное состояние. Открьшается элемент И 43, и счетчик 36 подсчитьтает число пришедших t5 синхроимпульсов. Одновременно на вход элемента И 5 поступают сигналы с выходов блоков 1,3,5 и 7 оповещения. Если считьгаание разрешено, то на выходе элемента И 45 появляется сигнал, {который, проходя через . элемент ИЖ 41 и элемент 46 задержки, сбрасывает триггер 39 в нулевое состояние. Наращивается счетчик 35 и . происходит переход на следующий такт.

2-й такт - запись в регистры 12 и 13.

3-й такт - запись в регистры 2-, 4,6, и 8. Схема анализа возможности записи работает аналогично анализу при считьгеании, причем проводится опрос не собственных регистров, а регистров соседних процессоров.

4-й такт - сброс блока микропрог . раммного управления и переход на 35 новый цикл.

Счетчик 7 итераций используется для организации останова решения.

20

25

30

40

Формула изобретения

- 2и% U

--(

7t u

(вычисление второй разности на сумматоре

. At (У u) X -f(определение

U X

u

1. Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных, содержащий первый и

45 второй решающие блоки, первый регистр, информационньй вьжод первого решающего блока подключен к первому информационному входу второго решающего блока,, информационный выход,

50 которого подключен к первому информационному входу первого решающего блока, отличающийся тем, что, с целью расширения функциональных возможностей за счет выполприращения на умножителе 31)э (определение нового значения 55 «бния различньк типов итерационных искомой пере- процедур численного решения диффе- менной на на- ренциальных уравнений л частных про- копителе,сос- изводньгх, в него введены пять регист- тоящем из сум- РОВ, блок памяти команд, блок памя-

i

матора 28 и

iрегистра 26 .

Выполнение алгоритма обеспечива- бтся следующей последовательностью работы блока микропрограммного управления .

1-й такт - считывание информации из регистров 2, и 8. Сигнал появляется на выходе блока 14. Этот

гистры и одновременно устанавливает триггер 39 в единичное состояние. Открьшается элемент И 43, и счетчик 36 подсчитьтает число пришедших 5 синхроимпульсов. Одновременно на вход элемента И 5 поступают сигналы с выходов блоков 1,3,5 и 7 оповещения. Если считьгаание разрешено, то на выходе элемента И 45 появляется сигнал, {который, проходя через . элемент ИЖ 41 и элемент 46 задержки, сбрасывает триггер 39 в нулевое состояние. Наращивается счетчик 35 и . происходит переход на следующий такт.

2-й такт - запись в регистры 12 и 13.

3-й такт - запись в регистры 2-, 4,6, и 8. Схема анализа возможности записи работает аналогично анализу при считьгеании, причем проводится опрос не собственных регистров, а регистров соседних процессоров.

4-й такт - сброс блока микропрог . раммного управления и переход на 5 новый цикл.

Счетчик 7 итераций используется для организации останова решения.

0

5

0

40

Формула изобретения

1. Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных, содержащий первый и

45 второй решающие блоки, первый регистр, информационньй вьжод первого решающего блока подключен к первому информационному входу второго решающего блока,, информационный выход,

50 которого подключен к первому информационному входу первого решающего блока, отличающийся тем что, с целью расширения функциональных возможностей за счет выпол

ти данных, блок микропрограммного управления и шесть блоков оповещения информационные входы с первого по четвертый процессора подключены к информационным входам соответственно с первого по четвертый регистров, группы управляющих входов с первой по четвертую процессора подключены к входам установки блоков оповещения соответственно с первого по четвер- тый, выходы с первого по шестой признака занятости процессора подключены к первым выходам блоков оповещения соответственно с первого по шестой и к входам записи регистров соответ- ственно с первого по шестой, тактовый вход процессора подключен к тактовому входу блока микропрограммного управления, вход запуска процессора подключен к входу запуска блока микропрограммного управления, вход задания программы работы процессора подключен к информационному входу блока памяти команд, входы с первого по четвертый признака занятости npo-t цессора подключены к входам .соответственно с первого по четвертый логических условий блока микропрограммного управления, вых.од признака неисправности процессора подклю- чен к первому выходу блока микропрограммного управления, первый и второй выходы результата процессора подключены соответственно к выходам пятого и шестого регистров, входы с первого по четвертьй признака начала работы процессора подключены к первым информационным входат соответственно с первого по четвертьй блоков оповещения, второй выход бло- ка микропрограммного управления под- к вторым информационным входа блоков оповещения с первого по четвертый и первым управляющим входом первого и второго решающих блоков, вторые выходы блоков оповещения с первого по четвертый подключены к входам соответственно с пятого по восьмой логических условий блока микропрограммного управления и к входам считывания соответственно с первого по четвертый регистров, вторые выходы пятого и шестлго блоков оповещения подключены к входам считьшания соответственно пятого и шестого ре- гистров, выходы первого и второго регистров подключены соответственно к второму и третьему информационным входам п ервого решающего блока, выхо5

О -5 0 0 5 0 5

ды третьего и четвертого регистров подключены соответственно к второму и третьему информационным входам второго решающего блока, третий и четвертый выходы блока микропрограммного управления подключены к вторым уп равляющим входам соответственно первого и второго решающего блоков, пятый выход блока микропрограммного управления подключен к первым информационным входам пятого и шестого блоков оповещения, шестой выход блока микропрограммного управления подключен к вторым информационным входам пятого и шестого блоков оповещения, седьмой выход блока микропрограммного управления подключен к третьим управляющим входам первого и второго решающих блоков и к входу записи - чтения блока памяти данных, восьмой выход блока микропрограммного управления подключен к входу считывания блока памяти команд, выход которого подключен к входу кода команд блока микропрограммного управления, группа выходов блока микропрограммного управления подключена к адресным входам блока памяти данных, информационный вход - выход первого решающего блока подключен через первую общую шину данных процессора к информационному входу пятого регистра и первому информационному входу- выходу блока памяти данных, инфор- мационньй вход-выход второго решающего блока подключен через вторую общую шину данных к информационному входу шестого регистра и к второму информационному входу-выходу блока памяти данных, вход приращения процессора подключен к четвертым информационным входам первого и второго решающих блоков, каждьй блок оповещения содержит два триггера, два злемента ИЛИ, три элемента И, первый вход установки группы блока оповещения подключен к входу установки в О первого триггера, второй . вход установки группы блока опове щения подключен к входу установки в 1 первого триггера, третий и четвертый входы установки группы блока оповещения подключены к первым входам соответственно первого и второго элементов ИЛИ, первый ин- формационньй вход блока оповещения подключен к первому входу первого элемента И, выход первого элемента И подключен к второму входу второго

to

15

91280385

элемента ИЛИ и к первому выходу блока оповещения, выходы первого и второго элементов ИЛИ подключены соответственно к входу установки и к входу установки в 1 второго триггера, прямой и инверсньй выходы второго триггера подключены соответственно к первому входу третьего элемента И и второму входу первого элемента И, выход первого триггера подключен к третьему входу первого элемента И и первому входу второго элег мента И, второй информационный вход блока оповещения подключен к второму входу третьего элемента И, выход третьего элемента И подключен к второму входу второго элемента И и второму выходу блока оповещения, выход второго элемента И подключен к вто- рому входу первого элемента ИЛИ, при этом каждый решающий блок содержит два сумматора, умножитель, три регистра, элемент РШИ, группу из п (где fi - разрядность переменной/ элементов И, первый, второй, третий, 25 четвертьй информационные входы решающего блока подключены соответствен-, но к первому информационному входу первого сумматора, первому информационному входу второго сумматора, второму информационному входу второго сумматора и информационному входу первого регистра решакщего блока, первый управляющий вход решающего блока подключен к входу считывания второго регистра решающего блока, второй управляющий вход решающего блока подключен к первым входам элементов И группы и первому входу элемента ИЛИ решающего блока, третий управляющий вход решающего блока подключен к второму входу элемента ИЛИ решающего блока, выходы и второго сумматора и первого регистра решающего блока подключены соот- 45 ветственно к первому и второму входам умножителя, выход которого подк- лючен к второму информационному входу первого сумматора,- выход которого подключен к информационному входу второго регистра решающего блока, выход второго регистра решающего блока подключен к вторым входам элементов И группы решающего блока, к третьему информационному входу первого сумматора и к информационному выходу решающего блока, выход элементов И группы решающего блока подключен к информационному входу треть30

ег го ще чт щ ч

те и т ч т эл

20 к н п л п в г п м л р

40 п

35

50

55

5

10

его регистра решающего блока и к информационному входу-выходу решающего блока, выход элемента ИЛИ решающего блока подключен к входу записи- чтения третьего регистра решающего блока, выход третьего регистра решающего блока подключен к третьему и четвертому информационным входам второго сумматора.

5

5 5

0

2. Процессор матричной вычислительной структуры для решения дифференциальных уравнений в частных производных, отличающийся тем, что блок микропрограммного управления содержит регистр, три счетчика, узел постоянной памяти, два триггера, элемент задержки, четыре элемента И, два элемента ИЛИ, вход

0 кода команды блока микропрограммного управления подключен к информационному входу первого счетчика, вход запуска блока микропрограммного управления подключен к входу установки в 1 первого .триггера, тактовый вход блока микропрограммного управления подключен к первым входам первого и второго элементов И, входы с первого по четвертый логических условий блока микропрограммного управления подключены к входам соответственно с первого по четвертый третьего элемента И, входы с пятого по восьмой логических условий блока микропрог- раммного управления подключены к входам соответственно с первого по четвертый четвертого элемента И, выход первого счетчика подключен к адресному входу узла постоянной

0 памяти, выход узла постоянной памяти подключён к информационному входу регистра, первый выход блока микропрограммного управления подключен к выходу переноса второго счетчика, выход первого разряда поля команды регистра подключен к первому входу первого элемента ИЛИ и второму выходу блока микропрограммного управления, выходы разрядов с второго по четвертый поля команды регистра подключены к выходам соответственно с третьего по пятый блока микропрограммного управления, выход пятого разряда поля команды регистра подключен к второму входу первого элемента ИЛИ и к шестому выходу блока микропрограммного управления, выходы седьмого и восьмого разрядов поля ко- манД1 1 регистра подключены соответст5

0

5

венно к седьмому и восьмому выходам блока микропрограммного управления, выходы поля адреса регистра подключены к одноименным выходам группы блока микропрограммного управления, выход поля признака команды регистра подключен к счетным входам первого- второго и третьего счетчиков, выходы первого и второго элементов И подключен к синхровходам соответственно первого и второго счетчиков, выходы третьего и четвертого элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход-первого эле

мента ИЛИ подключен к первому информационному входу второго триггера, выход второго элемента ИЛИ подключен к входу элемента задержки, выход которого подключен к второму информационному входу второго тригге ра, инверсный и прямой выходы второго триггера подключены к вторым входам соответственно первого и второго элементов И, выход переполнения третьего счетчика подключен к входу установки в О первого триггера, выход первого триггера подключен к третьему входу первого элемента. И.

I cvi//m f af ujf

(Pus. г

t t t

I / I /«5 I 7 /«. 1

Jj

iL

j-i

35

1

/.

v

Hf-O C«s)/

r tivao f/tf/t/e en iofft/f tA,ffufi ia/rvettft.fAt.e /refero

Составитель В,Смирнов Редактор Л.Пчелинская Техред Л.Олейник Корректор В.Бутяга

-Заказ 7051/42 Тираж 671Подписное

ВНИШИ Государственного Комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская. йа5., д.4/5

Проиэводственио-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

Изобретение относится к вычислительной технике и предназначено для построения матричных вычислительных структур, предназначенных для решения дифференциальных уравнений в частных производных. Цель изобретения - расширение функциональных возможностей за счет выполнения различного типа итерационных процедур численного решения дифференциальных уравнений в частных производных. /r-1-f К-1 с t ю X) :с 00 СП

| Патент США № 3633002, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ячейка интегрирующей структуры для решения уравнения лапласа | 1975 |

|

SU574733A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-30—Публикация

1985-04-08—Подача