fO

11293737

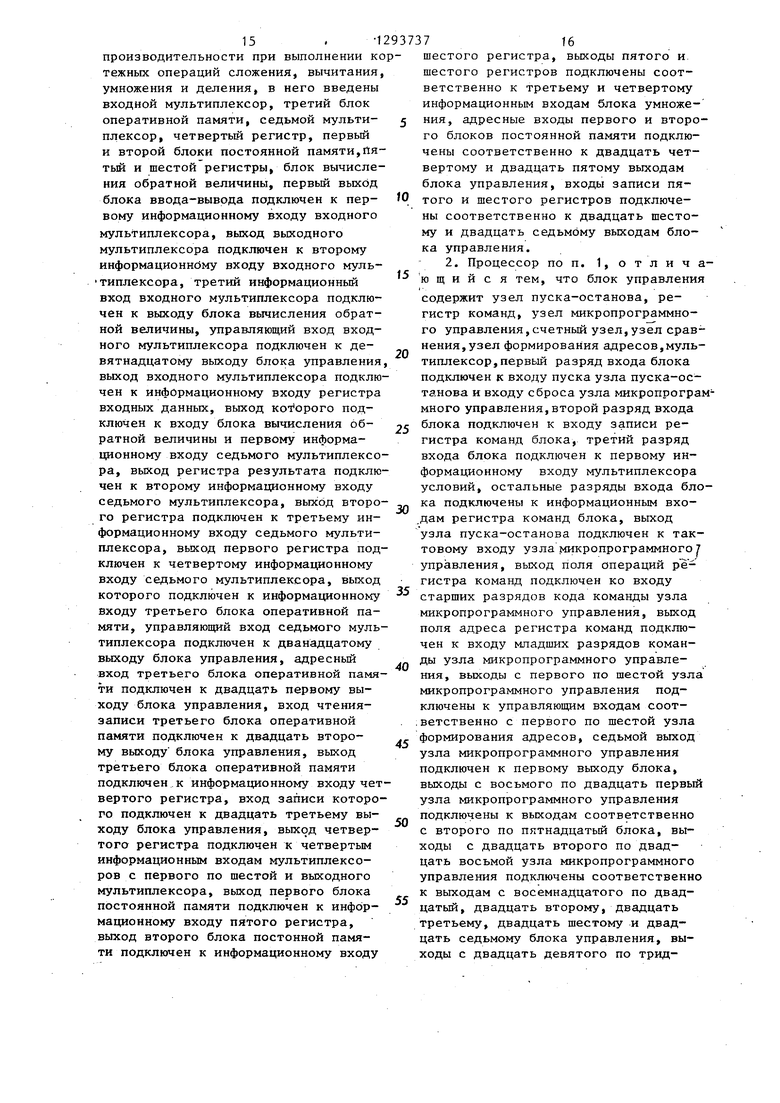

Изобретение относится к вычислиельной технике и может быть испольовано при построении вычислительных истем для решения различных задач, частности для решения дифференцильных уравнений в частных производных.

В прикладной математике существует класс задач, в которых возникает необходимость обрабатывать массивы, особого вида, так называемые диффе- енциальные кортежи. Этот класс заач включает в себя решение дифференциальных уравнений в частных производных, описьшающих физико-механические поля (тепловые, деформационные, электродинамические и др.), где применяется стратегия дифференцирования сложных аналитических вьфажений с использованием понятия дифференциаль ного кортежа и кортежных операций над ним, которые подчиняются законам кортежной алгебры.

Определение понятия дифференциального кортежа.

Пусть функция U(x)eC (S), (с (2) - пространство непрерывных в ЭеК функций) задана вместе с частными производными до п-го порядка включительно. Вектор-функция U(x)(U,Uj,

iS

-20

25

30

и(„, ) назьтается дифференциальным кортежем п-го порядка функции U(x) если она является образом отображения

ко

на фе У

су

ни ма чи

(a))3

К(1,о)

LC

Х...Х C°(SJ)

«Cm.Mj

I

a ее компоненты определяются формулами:

,

и f V ,

rwi

0 +S-1),

m-K+1

где X - знак прямого произведения,

, ., (m+t-1)

k(m,t) показатели степени

(.m-t; t

пространств с Чй) (,1, ... ,п);

.dL (ot , - мультиндекс,

.х(х;, X,,..., xJeR ; D , ,....

Размещение компонентов дифференциального кортежа осуществля ется группами в порядке возрастания производных ( loL| 0,1J... . ,п) , а в каждой из групп приоритет имеют производные по аргументам с меньшим индексом, т.е. дифференциальньй кортеж имеет следующую структуру:

/ , (-дх)

2

ду дх,

.5-Р дх.

l)(««).

fO

iS

20

25

30

35

40

45

50

Определение кортежных операций.

Операцией над дифференциальным кортежом U- (x)eD функций U;(х),

,2п, порождаемой функцией,

называется закон формирования дифференциального кортежа W:R -R, , (n() соответствующего

w(u,, и,UJ.

S

суперпозиции ..i, , u,,..,,.

Согласно приведенным определе- - ниям дифференциальный кортеж есть массив, операции над которыми подчиняются законам кортежной алгебры, отличающимися от законов обычной алгебры, и компоненты которого формируются особым образом.

Цель изобретения - повышение производительности устройства при выполнении кортежных операций.

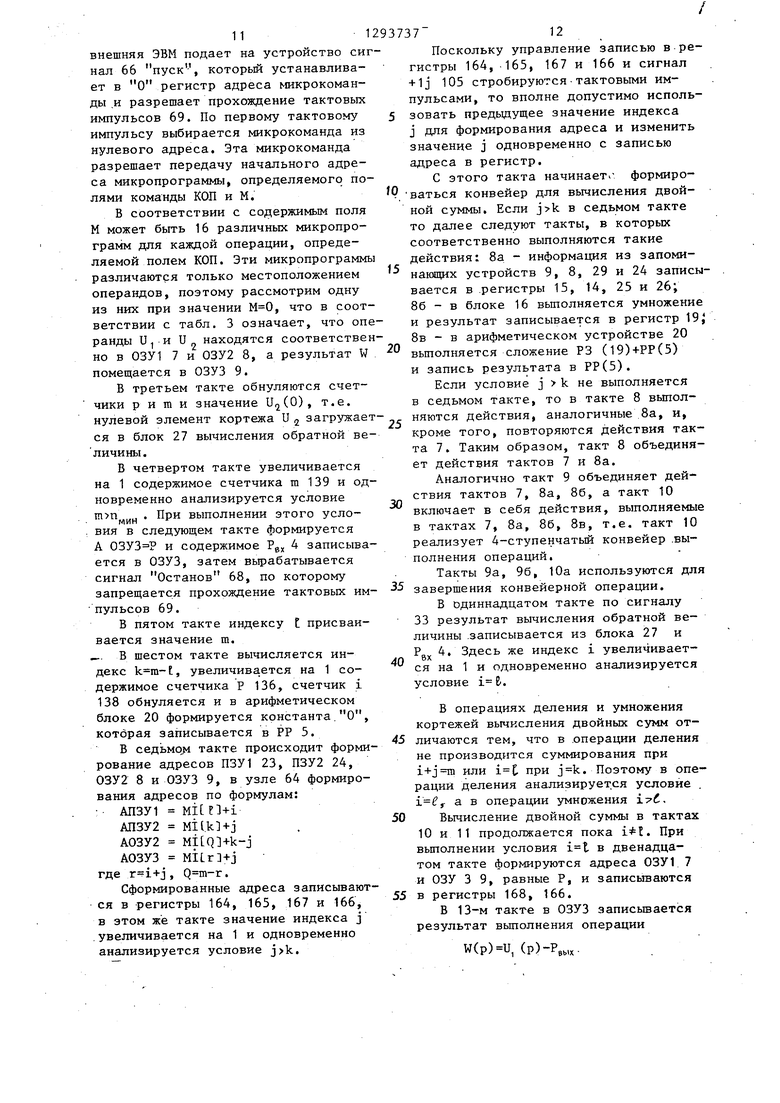

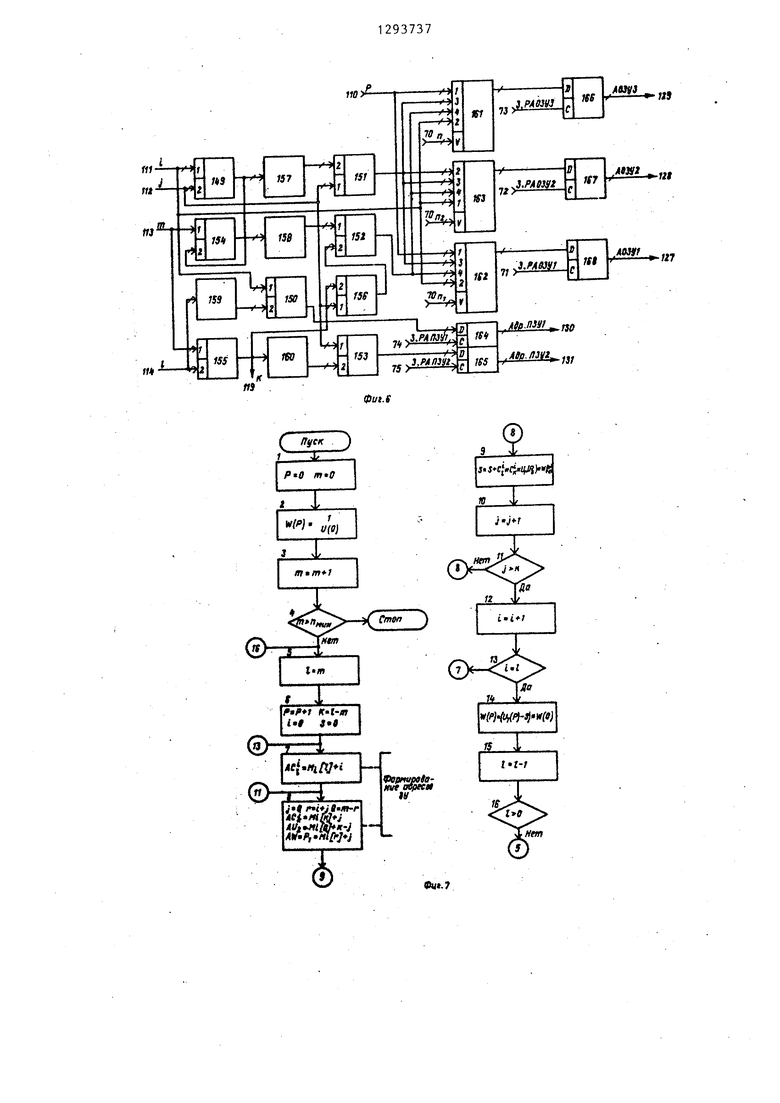

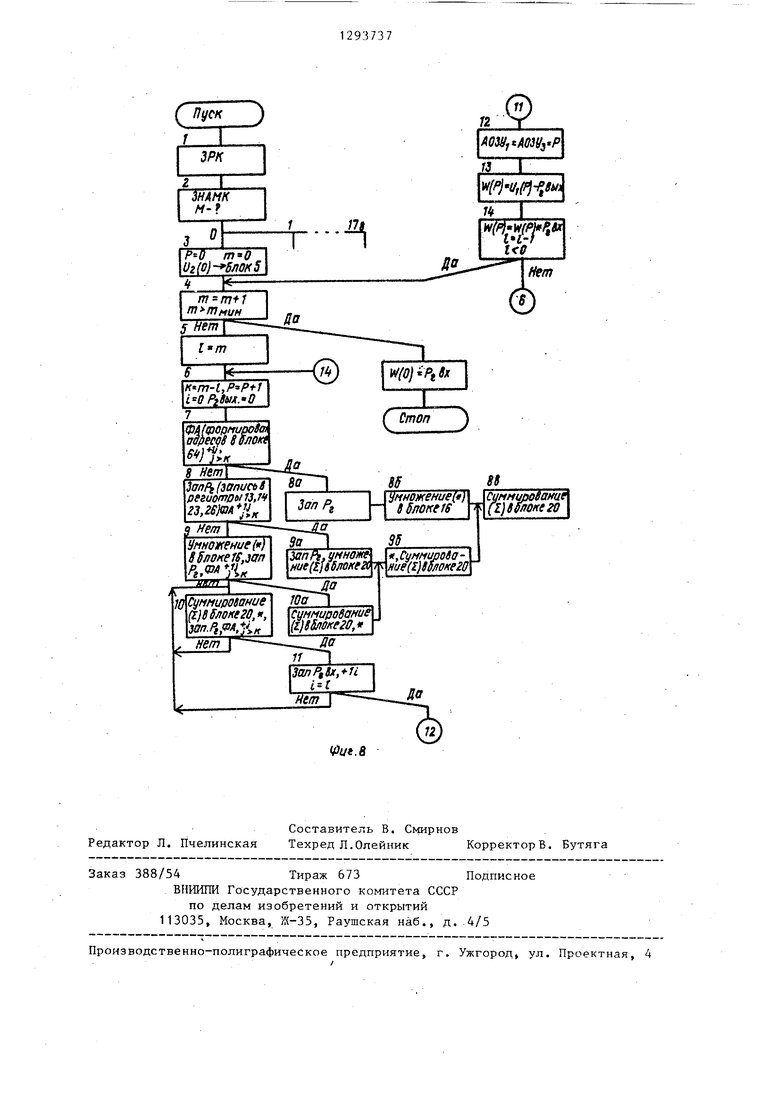

На фиг. 1 представлена функциональная схема матричного процессора на фиг. 2 - схема блока управления, на фиг. 3 - схема узла пуска-останова; на фиг.4 - схема счетного узла на фиг.5 - схема узла сравнения; на фиг. 6 - схема узла формирования адресов; на фиг. 7 - алгоритм операции деления кортежей, на фиг. 8 - микропрограмма деления кортежей.

Матричньй процессор для обработки массивов содержит блок 1 ввода- вывода, блок 2 управления, мультиплексор 3 входных данных, регистр 4 входных данных, регистр 5 результата, выходной мультиплексор 6, три блока 7-9 оперативной па мяти, три входных мультиплексора 10-12 блоков оперативной памяти, три выходных регистра 13-15 блоков оперативной памяти, блок 16 умножения, два входных мультиплексора 17 и 18 блока умножения, выходной регистр 19 блока умножения, арифметический блок 20, два входных мультиплексора 20 и 21 арифметического блока, два блока 23 и 24 постоянной памяти, два выходных регистра 25 и 26 блоков постоянной памяти, блок 27 вычисления обратной величины.

Первьй информационный вход блока 1 ввода-вывода подключен к выходу выкодного мультиплексора 6, второй

28 и третий 29 информационные входы блока ввода-вывода соединены с внешней ЭВМ, первый выход 30 блока ввода-вывода подключен к входу блока

.управления к первому информационно- му входу входного мультиплексора 3 Второй выход 31 блока управления подключен к внешней ЭВМ. Управляющий вход блока ввода-вывода подключен к выходу 32 блока управления, выходы 33-40 блока управления подключены к

I входам записи соответственно регистра 4 входных данных, регистров 13, 14 и 19, регистра 5 результата, регистров 15, 25 и 26, выходы 41-49 блока управления подключены к управляющим входам соответственно мультиплексора 6, мультиплексоров 22, 10,

11,17, 18 и 21, мультиплексора 3 и мультиплексора 12, выходы 50-52 блока управления подключены к входам записи-считывания блоков 7-9 оперативной памяти соответственно, выходы

53-57 блока управления - к адресным входам блоков 7-9 оперативной памяти и блоков 23 и 24 постоянной памяти, выход 58 блока управления - к входу кода операции арифметического блока, второй информационньй вход входного мультиплексора 3 - к выходу выходного мультиплексора 6, третий информационный вход входного мультиплексора 3 - к выходу блока 27 вычисления обратной величины, чет вертьй информационный вход входного мультиплексора 3 - к уровню логической 1 устройства, выход входного мультиплексора 3 - к информационному входу регистра 4 входных данных,вход которого подсоединен к входу блока 27 вычисления обратной величины,третьим информационным входам мультиплексоров 10, 11, 17 и 18 и первому информационному входу мультиплексора

12,информационный вход регистра результата 5 подключен к выходу арифметического блока 20, выход регистра результата 5 - к- первым информационным входам выходного мультиплек- сора 6 и мультиплексора 22, информационный вход блока 7 оперативной памяти - к выходу мультиплексора 10, выход блока 7 оперативной памяти к информационному входу регистра 13, .выход которого соединен с первыми информационными входами мультиплексоро 17, 18 и 21, вторыми информационными входами мультиплексоров 22 и 11 и выQ

5

0

5 О 0 5

ходного мультиплексора 6, и четвертым информационным входом мультиплексора 12, информационный вход блока 8 оперативной памяти подключен к выходу мультиплексора 11, выход блока 8 оперативной памяти - к информационному входу регистра 14, выход которого связан с вторыми информационными входами мультиплексоров 17, 18, 21 и 10 и третьими информационными входами мультиплексоров 22 и 12 и выходного мультиплексора 6, информационный вход блока 9 оперативной памяти подключен к выходу мультиплексора 12, выход блока 9 оперативной памяти - к информационному входу регистра 15, выход которого подсоединен к четвертым информационным входам мультиплексоров 17, 18, 21, 22, 10 и 11 и выходного мультиплексора 6, выходы мультиплексоров 17 и 18 под-, ключены соответственно к первому и второму информационным входам блока 16 умножения, выход блока 23 постоянной памяти подсоединен к информационному входу регистра 25, выход которого связан с третьим информационным входом блока 16 умножения, выход блока 24 постоянной памяти подключен к информационному входу регистра 26, выход которого соединен с четвертым информационным входом блока 16 умножения, выход которого подключен к информационному входу регистра 19, выход которого связан с третьим информационным входом мультиплексора 21, выходы мультиплексоров 21 и 22 подключены соответственно к первому и второму информационным входам арифметического блока 20.

Структура блока ввода-вывода 1 зависит от интерфейса внешней ЭВМ. В качестве элементной базы для блока ввода-вывода можно использовать микропроцессорные комплекты с наращиваемой разрядностью, например, микропроцессоры серии 585/589,1802, 1804.

Вьшолнение блока 2 управления зависит от типа конкретной ЗВМ и типа обмена между матричным процессором и ЭВМ.

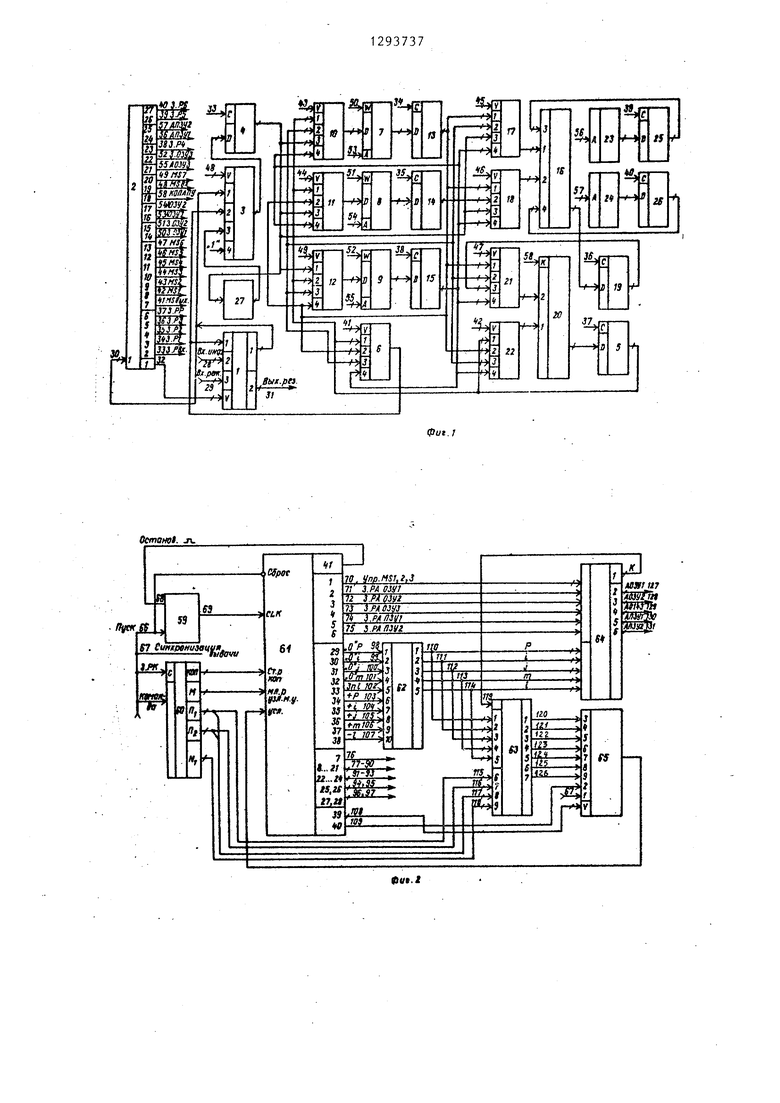

На фиг, 2 приведена структурная схема блока управления, реализующего программный обмен с внешней ЭВМ. Он содержит узел пуска-останова 59, регистр 60 команд, узел 61 микропрограммного управления, счетный узел 62, узел 63 сравнения, узел

JO

f5

512937376

64 формирования адресов и мультиплек- соответствующему выходу узла 64 фор- сор 65. мирования адресов, выходы 120-126 узг

Первый разряд 66 входа блока уп- ла 63 сравнения подсоединены к соответравления подключен к входу пуска узла ствуклцим информационным входам муль- пуска-останова 59 и входу сброса узла 5 типлексора 65 условий, выход которо- микропрограммного управления 61, второй разряд входа блока подсоединен к входу записи регистра команд 60, третий разряд 67 входа блока - к пер- Botty информационному входу мульти-« плексора условий 65, остальные раз ряды входа блока - к информационным входам регистра команд 60, вход 68 узла пуска-останова 59 подключен к выходу узла 61 микропрограммного управления, выход 69 узла пуска-останова 59 - к тактовому входу узла 61 микропрограммного управления, выход поля операций (КОП) регистра 60 команд соединена с входом старших разрядов кода команды узда 61 микропрограммного управления, выход поля адреса (М) регистра 60 команд - с входом младших разрядов кода команды узла 61 микропрограммного управления, выходы 70-75 узла микропрограммного управления - с соответствующими управляющими входами узла 64 формирования адресов, выход микро-. ,, . программного управления - с выходом ки 136-140, входы 98-101 счетного 32, выходы 77-97 узла 61 микропро- узла 62 подключены к входам установ. граммного управления - соответственно ки в ноль соответственно счетчиков с выходами 33-52, 58 блока 2 управ(ления, выходы 98-107 узла 61 микропрограммного управления - с соответствующими входами счетного узла 62, выход 108 узла 61 микропрограммного

20

25

го подключен к входу условий узла 61 микропрограммного управления, выходы 127-131 узла 64 формирования адресов соединены соответственно с выходами 53, 54, 52, 56, 57 блока 2 управления.

Структурная схема узла 59 пуска- останова приведена на фиг. 3. Узел 59 содержит генератор 132 тактовых импульсов, J-гК-триггер 133, элемент И 134 и одновибратор 135, вход 66 узла 59 пуска-останова подключен к входу одновибратора 135, выход которого подсоединен к входу J триггера 133, вход 68 узла пуска-останова 59 - ко входу К триггера 133, выход генератора 132 тактовых импульсов подключен к первому входу элемента И и тактовому входу триггера 133, прямой выход которого соединен с вторым входом элемента И 134, выход которого подключен к выходу 69 узла 59 пуска- останова .

Счетный узел 62 содержит счетчи136-139, вход 102 счетного узла 62 соединен с входом записи начального

35 значения счетчика 140, входы 103-107 счетного узла 62 - с счетными входами соответственно счетчиков 136-140, выходы счетчиков 136-140 подключены соответственно к выходам 110-114

управления - с управляющим входом мультиплексора 65 условий, выход 109 узла 61 микропрограммного управления - с вторым информационным входом мультиплексора 65 условий, выходы 110-114 счетного узла 62 подключены к соответствующей группе информаци35 значения счетчика 140, входы 103-107 счетного узла 62 - с счетными входами соответственно счетчиков 136-140, выходы счетчиков 136-140 подключены соответственно к выходам 110-114

40 счетного узла 62, выход счетчика 139 подсоединен к информационному входу счетчика 140.

Узел 63 сравнения содержит элементы 141-147 сравнения и мультионных входов узла 63 сравнения и уз- плексор 148, вход 110 узла сравне- ла 64 формирования адресов, выход первого поля условий (п) регистра 60 команд подсоединен к входу 115 узла 63 сравнения, выход второго поля условий (п,) регистра 60 команд - 50 та 143 сравнения, вход 112 узла срав- к входу 116 узла 63 сравнения, выходы нения - к первому входу элемента 144 первого (п) и второго (п ) полей условий регистра 60 команд объединены

ния подключен к первому входу элемента 141 сравнения, вход 111 узла сравнения - к первому входу элемента сравнения 142 и первому входу элеменсравнения, вход 113 узла сравнения - к первому входу элемента 145 сравнеи подключены к входу 117 узла 63

сравнения, выход третьего поля уело- 55 первому входу элемента 146 сравнения ВИЙ (N,) регистра 60 команд соединен и второму входу элемента 143 сравнес входом 118 узла 63 сравнения, вход 119 узла 63 сравнения подключен к

ния, вход 115 узла сравнения - к первому входу элемента 147 сравнения

ствуклцим информационным входам муль- типлексора 65 условий, выход которо-

. ,, . ки 136-140, входы 98-101 счетного узла 62 подключены к входам установ

го подключен к входу условий узла 61 микропрограммного управления, выходы 127-131 узла 64 формирования адресов соединены соответственно с выходами 53, 54, 52, 56, 57 блока 2 управления.

Структурная схема узла 59 пуска- останова приведена на фиг. 3. Узел 59 содержит генератор 132 тактовых импульсов, J-гК-триггер 133, элемент И 134 и одновибратор 135, вход 66 узла 59 пуска-останова подключен к входу одновибратора 135, выход которого подсоединен к входу J триггера 133, вход 68 узла пуска-останова 59 - ко входу К триггера 133, выход генератора 132 тактовых импульсов подключен к первому входу элемента И и тактовому входу триггера 133, прямой выход которого соединен с вторым входом элемента И 134, выход которого подключен к выходу 69 узла 59 пуска- останова .

Счетный узел 62 содержит счетчи ки в ноль соответственно счетчиков

136-139, вход 102 счетного узла 62 соединен с входом записи начального

35 значения счетчика 140, входы 103-107 счетного узла 62 - с счетными входами соответственно счетчиков 136-140, выходы счетчиков 136-140 подключены соответственно к выходам 110-114

40 счетного узла 62, выход счетчика 139 подсоединен к информационному входу счетчика 140.

Узел 63 сравнения содержит элементы 141-147 сравнения и мульти- 5 плексор 148, вход 110 узла сравне- 50 та 143 сравнения, вход 112 узла срав- нения - к первому входу элемента 144

плексор 148, вход 110 узла сравне- та 143 сравнения, вход 112 узла срав- нения - к первому входу элемента 144

ния подключен к первому входу элемента 141 сравнения, вход 111 узла сравнения - к первому входу элемента сравнения 142 и первому входу элеменплексор 148, вход 110 узла сравне- та 143 сравнения, вход 112 узла срав- нения - к первому входу элемента 144

сравнения, вход 113 узла сравнения - к первому входу элемента 145 сравнения, вход 114 узла сравнения - к

ния, вход 115 узла сравнения - к первому входу элемента 147 сравнения

и первому информационному входу мультиплексора 148, вход 116 узла сравнения - к второму входу элемента 147 сравнения и второму информационному входу мультиплексора 148, вход 117 узла сравнения - к второму входу элемента 141 сравнения, вход 118 узла сравнения - к второму входу элемента 142 сравнения, вход 119 узла сравнения - к второму входу элемента 144 сравнения, второй вход элемента 146 сравнения подсоединен к входу нуле- вого потенциала устройства, выход элемента 147 сравнения - к управляющему входу мультиплексора 148, выход которого соединен с вторым входом элемента 145 сравнения, выходы элементов 141, 142, 145, 144 и 146 сравнения, подключены соответственно к выходам 120, 121, 122, 124 и 125 узла сравнения, первый и второй выходы элемента сравнения подключены соответственно к выходам 123 и 126

узла сравнения.

I

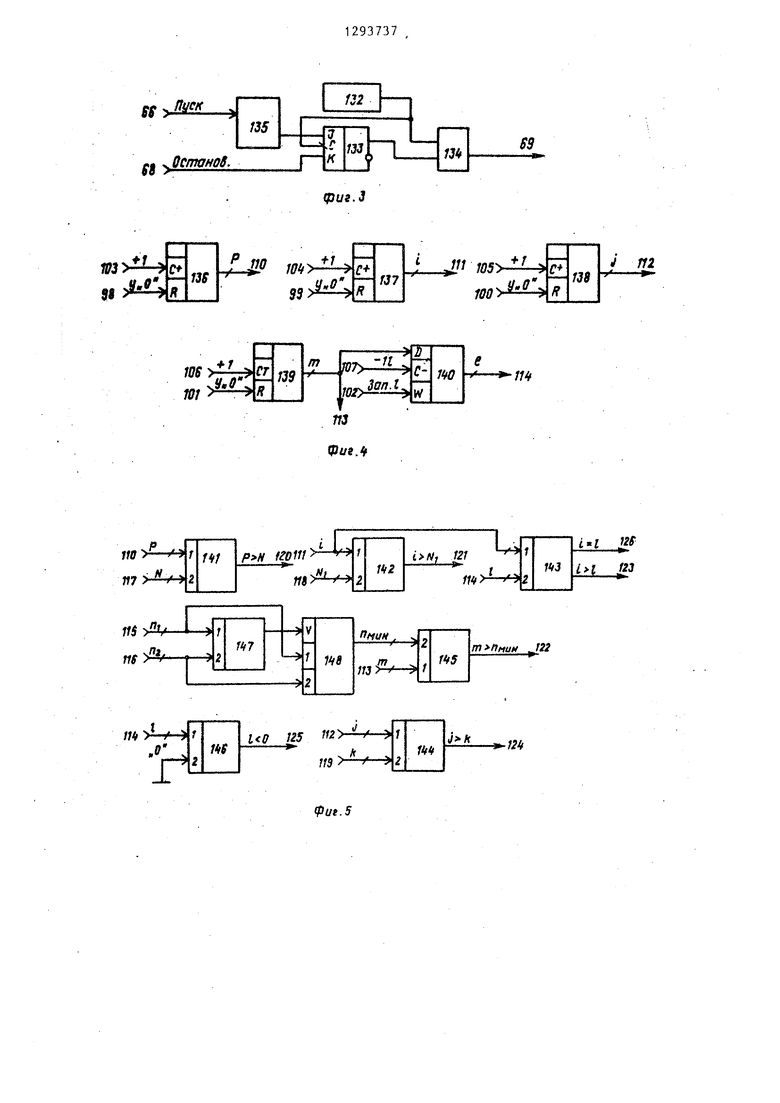

Узел формирования адресов содержит сумматоры 149-153, вычитате- ли 154-156, блоки 157-160 постоянной памяти, мультиплексоры 161-63, регистры. 164- 168 адреса, вход 110 узла . 64 формирования адресов подключен к первым информационным входам мультиплексоров 161 и 162, вход 111 узла 64 формирования адресов - к первым входам сумматоров 149 и 150 мультиплексора 163 и вторым входам мультиплексоров 161 и 162, вход 112 узла 64 формирования адресов - к второму входу сумматора 149, первым входам сумматоров 151 и 153, вход 114 узла 64 формирования адресов - к второму входу вычитателя 155 и адресному входу блока 159 постоянной памяти, управляющие входы 70 узла формирования адресов подключены к управляю- щим входам мультиплексоров 161-163, управляющие входы 71-75 узла формирования адресов - к входам записи соответственно регистров 168, 167, 164 и 165 адреса, выход сумматора 149 соединен с вторым входом вычита- теля 154 и адресным входом постоянной памяти 157, выход вычитателя 154 подключен к адресному входу постоянной памяти 158, выход постоянной па- мяти 159.связан с вторым входом сумматора 150, выход вычитателя 155 подключен к второму входу вычитателя 156 адресному входу постоянной памяти 160

v i

5

Q 0 5

5

и выходу 119 узла 64 формирования, адресов, выход постоянной памяти 157 подключен к второму входу сумматора

151,выход постоянной памяти 158 - к первому входу сумматора 152, выход сумматора 150 - к информационному входу регистра адреса 164, выход постоянной памяти 160 - к второму входу сумматора 153, выход которого подключен к информационному входу регистра 165 адреса, выход вычитателя .156 - соединен с вторым входом сумматора

152,выход сумматора 151 подключен к третьим информационным входам мультиплексоров 161 и 162 и второму и третьему информационным входам мультиплексора 163, выход сумматора 152 к четвертым информационным входам мультиплексоров 161-163, выходы которых соединены соответственно с информационными входами регистров 166- 167 адреса, выходы регистров 168, 167, 166, 164 и 165 адреса подключены соответственно к выходам 127-131 узла формирования адресов.

В блоке управления матричного процессора реализован аппаратно-микро- программный принцип управления. Наличие независимых счетчиков р, i, j, m, 1, k, аппаратных схем сравнения и отдельных схем формирования адресов ОЗУ1, ОЗУ2, ОЗУЗ, ПЗУ1, ПЗУ2 позволяет организовать конвейерное выпол- нение операций, что существенно увеличивает производительность матричного процессора.

Матричный процессор для обработки массивов выполняет следующие операции :

1.Пересылка данных

2.Y(p)A(p)X(p)+B(p), ,...,N

3.Y(p)A(p)X(p),

4.Y(p)x (p),

5.Y(p)X (p)-fB(p),

. N, „

6.Y i:X4i), , ,-;

--0

ч ,

7. (I)+B i-o „

8. Y(p) CA(i)X (p), ,1,

Ь I

j 111 l. у « % 14

9.Y(p)nA(p,i)X(i)+B(p)

10.Y(p) i:; A(p, i) X(i),

:O

(Y, A, X, в - массивы).

if

9 1293737

Кроме перечисленных операций мат- ричньй процессор для обработки массивов вьтолняет кортежные операции:

11. Сложение W(p)U, (p)+U5(p);

12. Вычитание W(p)U, (p)-U(p);

13. Умножение

fO

о дл в

f к , ,

w(p)CCCfC,u,(p,).U2(p,),

j o 14. 7 Деление

E к

WCP)---V u,(f bIIIIc iw(P.) U,CP,)

- U,U I ;-n bo

i +j fTi

Индексы p и i в операциях 1-12 изменяются линейно. В операциях 13 и 14 индексы р, Р,,Р, вычисляются по формулам: /

p(t+k)(t+k+1)/2+k; р,-(i+j)(i+j+1)/2+j; P,(in-i-j)(m-i-j + 1)/2+k-j-

n

Индекс m изменяется от нуля до где n - порядок кортежа. Индекс Е изменяется от m до нуля для каждого ш. Индекс k вычисляется .

Матричный процессор использует 3 формата команды.

1-й формат

В этом формате реализованы следующие операции:

1)пересьшка даннык;

2)векторные операции 2-5;

3)кортежные операции сложения и вь1читания.

Тип операции определяется содержанием поля КОП.

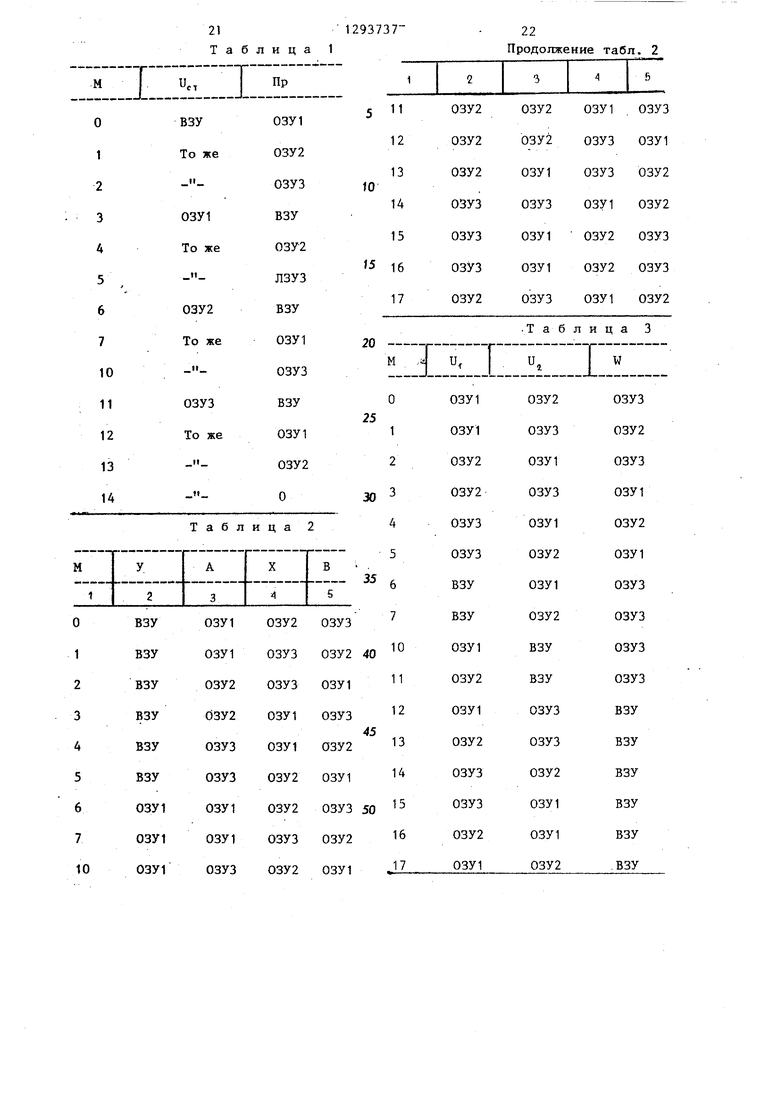

Поле М - модификация команды,

определяющая местонахождения операндов. Функциональное назначение поля М приведено в табп. 1.для команды Пересылка, в табл. 2 - для векторных операции, тежных операций.

табл. 3 - для корПоле N определяет количество передаваемых данных в команде Пересыпка, длину вектора и длину кортежа в векторных и кортежных операциях соответственно.

10 2-й формат

Поле КОП определяет векторные операции 6-8 и матричные операции 9 и 10.

Функциональное назначение поля М определяется по табл. 2. Поле для векторных операций 6 и 7. Для векторной операции 8 поля N и N определяют длину векторов, для матричных операций 9 и 10 поля N и N определяют размер матрицы 1.

3-й формат

В этом формате реализованы кортежные операции умножения и деления. Тип операции определяется содержимым поля КОП. Функциональное назначение поля М определяется по табл.3. Поля п, и п Q определяют порядок кор- тежей и и и соответственно.

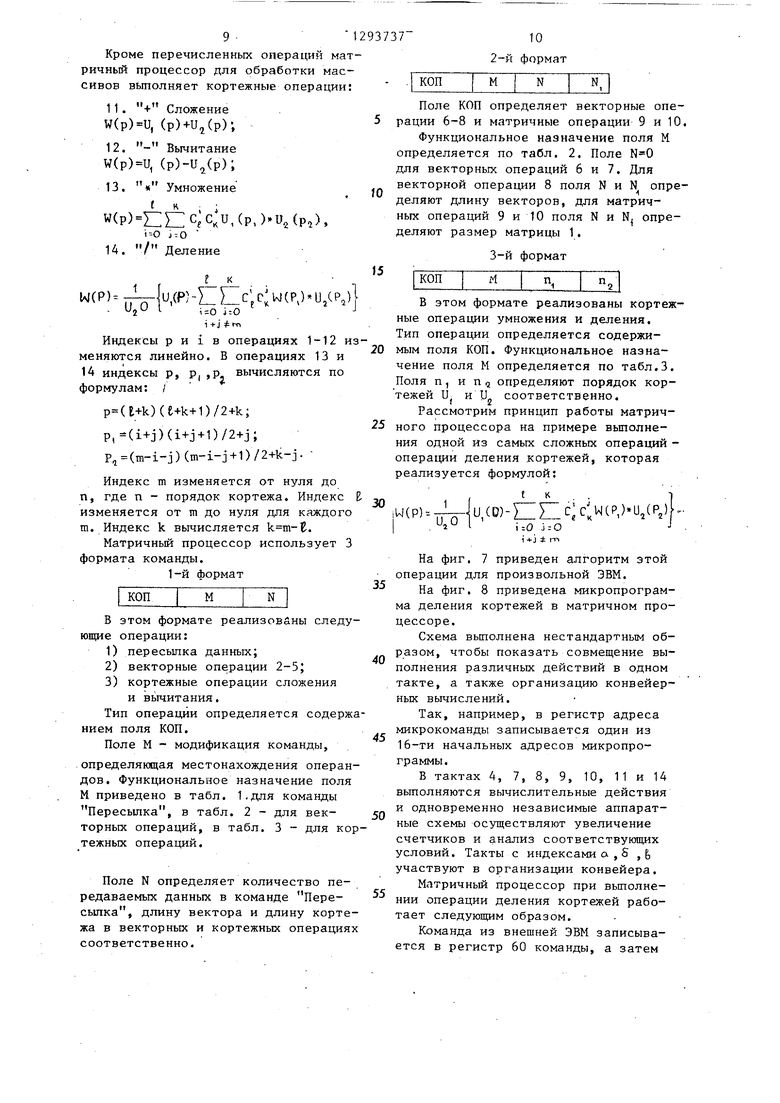

Рассмотрим принцип работы матричного процессора на примере вьшолне- ния одной Из самых сложных операций - операции деления кортежей, которая реализуется формулой:

iW(P)-1

U,(D)-nCc;C(P,)U,(P,

i:0

1 -v j m

Ha фиг. 7 приведен алгоритм этой операции для произвольной ЭВМ.

На фиг. 8 приведена микропрограмма деления кортежей в матричном процессоре.

Схема выполнена нестандартным образом, чтобы показать совмещение выполнения различных действий в одном такте, а также организацию конвейерных вычислений.

Так, например, в регистр адреса микрокоманды записывается один из 16-ти начальных адресов микропрограммы.

В тактах 4, 7, 8, 9, 10, 11 и 14 вьшолняются вычислительные действия и одновременно независимые аппаратные схемы осуществляют увеличение счетчиков и анализ соответствующих условий. Такты с индексами а,S , участвуют в организации конвейера.

Млтричньй процессор при выполнении операции деления кортежей работает следующим образом.

Команда из внешней ЭВМ записывается в регистр 60 команды, а затем

fO

111293737

внешняя ЭВМ подает на устройство сигнал 66 пуск, который устанавливает в О регистр адреса микрокоманды .и разрешает прохождение тактовых импульсов 69. По первому тактовому импульсу выбирается микрокоманда из нулевого адреса. Эта микрокоманда разрешает передачу начального адреса микропрограммы, определяемого полями команды КОП и М.

В соответствии с содержимым поля М может быть 16 различных микропрограмм для каждой операции, определяемой полем КОП. Эти микропрограммы различаются только местоположением операндов, поэтому рассмотрим одну из них при значении , что в соответствии с табл. 3 означает, что операнды и, и U- находятся соответствен но в ОЗУ1 7 и ОЗУ2 8, а результат W помещается в ОЗУЗ 9.

В третьем такте обнуляются счетчики р и m и значение ), т.е

12

Поскольку управление записью в гистры 164, 165, 167 и 166 и сигна +1J 105 стробируютсятактовыми импульсами, то вполне допустимо испо зовать предыдущее значение индекса j для формирования адреса и измени значение j одновременно с записью адреса в регистр.

С этого такта начинает - формир ваться конвейер для вычисления дво ной суммы. Если в седьмом такт то далее следуют такты, в которых соответственно выполняются такие действия: 8а - информация из запом нающих устройств 9, 8, 29 и 24 запи вается в .регистры 15, 14, 25 и 26 86 - в блоке 16 выполняется умноже и результат записывается в регистр 8в - в арифметическом устройстве 2 вьшолняется сложение РЗ (19)+РР(5) и запись результата в РР(5).

Если условие j k не выполняется в седьмом такте, то в такте 8 вьтол

20

нулевой элемент кортежа Uj загружает- няются действия, аналогичные 8а, и

ся в блок 27 вычисления обратной ве- личины.

В четвертом такте увеличивается на 1 содержимое счетчика m 139 и одновременно анализируется условие

30

кроме того, повторяются действия та та 7. Таким образом, такт 8 объеди ет действия тактов 7 и 8а.

Аналогично такт 9 объединяет дей ствия тактов 7, 8а, 86, а такт 10 включает в себя действия, выполняем в тактах 7, 8а, 86, 8в, т.е. такт реализует 4-ступенчатый конвейер .вы полнения операций.

мин

При выполнении этого условия в следующем такте формируется А и содержимое Pg 4 записывается в ОЗУЗ, затем вырабатывается сигнал Останов 68, по которому запрещается прохождение тактовых импульсов 69.

В пятом такте индексу t присваивается значение т. -. В шестом такте вычисляется индекс , увеличивается на 1 содержимое счетчика Р 136, счетчик i 138 обнуляется и в арифметическом блоке 20 формируется константа.О, которая записывается в РР 5.

В седьмо,м такте происходит формирование адресов ПЗУ1 23, ПЗУ2 24, ОЗУ2 8 и ОЗУЗ 9, в узле 64 формирования адресов по формулам: АПЗУ1 Mltn+i

АПЗУ2

АОЗУ2

ЛОЗУЗ MlLrD+j где , .

Сформированные адреса записываются в регистры 164, 165, 167 и 166, в этом же такте значение индекса j ,увеличивается на 1 и одновременно анализируется условие .

12

O

Поскольку управление записью в регистры 164, 165, 167 и 166 и сигнал +1J 105 стробируютсятактовыми импульсами, то вполне допустимо использовать предыдущее значение индекса j для формирования адреса и изменить значение j одновременно с записью адреса в регистр.

С этого такта начинает - формироваться конвейер для вычисления двойной суммы. Если в седьмом такте то далее следуют такты, в которых соответственно выполняются такие действия: 8а - информация из запоми- нающих устройств 9, 8, 29 и 24 записывается в .регистры 15, 14, 25 и 26 86 - в блоке 16 выполняется умножение и результат записывается в регистр 19J 8в - в арифметическом устройстве 20 вьшолняется сложение РЗ (19)+РР(5) и запись результата в РР(5).

Если условие j k не выполняется в седьмом такте, то в такте 8 вьтол0

0

кроме того, повторяются действия такта 7. Таким образом, такт 8 объединяет действия тактов 7 и 8а.

Аналогично такт 9 объединяет действия тактов 7, 8а, 86, а такт 10 включает в себя действия, выполняемые в тактах 7, 8а, 86, 8в, т.е. такт 10 реализует 4-ступенчатый конвейер .выполнения операций.

Такты 9а, 96, 10а используются для -5 завершения конвейерной операции.

В одиннадцатом такте по сигналу 33 результат вычисления обратной величины .записывается из блока 27 и РО 4. Здесь же индекс i увеличиваетОА

СЯ на 1 И одновременно анализируется условие .

0

В операциях деления и умножения кортежей вычисления двойных сумм отличаются тем, что в .операции деления не производится суммирования при или при . Поэтому в операции деления анализирует.ся условие i.Cf а в операции умножения 1:,

Вьиисление двойной суммы в тактах 10 и 11 продолжается пока i. При выполнении условия в двенадцатом такте формируются адреса ОЗУ1 7 и ОЗУ 3 9, равные Р, и записываются

в регистры 168, 166.

В 13-м такте в ОЗУЗ записывается результат выполнения операции

W(p)U, (р)-Р,

вых

В 14-м такте содержимое ОЗУЗ 9

по адресу Р умножается на содержимое

,Р..„ 4 и результат записывается в ,

J

ОЗУ. в этом же такте индекс уменьшается на 1 и анализируется условие tfO. При невыполнении этого условия прЬцесс вычислений продолжается с такта 6, а при выполнении с такта 4

Конвейерный принцип вычислений, реализованный для кортежных опера-. ций умножения и деления для матрич- ных и некоторых векторных операций, повышает быстродействие матричного процессора. Формула изобретения

1,Процессор для обработки массивов данных, содержащий блок ввода-вывода.

Ю

)5 мультиплексоров подключены соответственно к первому и второму информационным входам умножителя, выход шестого мультиплексора подключен к второму информационному входу арифметического блока, выход второго .блока оперативной памяти подключен к

I.. ,информационному входу второго регистра, выход которого подключен к вторым информационным входам второго, четвертого и пятого мультиплексоров, третьему информационному входу выходного мультиплексора, второму информационному входу шестого мультиплексора и третьему информационному входу первого мультиплексора,выход блока умножения подключен к информационному входу третьего регистра,выход коблок управления, регистр входных дан-2о торого подключен к третьему информационному входу шестого мультиплексора, первый выход блока ввода-вывода подклю- чен к входу блока управления,второй выход блока ввода-вывода подключен к 25 выходу резуль ата устройства, второй информационньй вход блока ввода,-вы- вода подключен к информационному входу устройства, третий информационный вход блока ввода-вывода подключен к входу задания режимов работы устройства, выход регистра входных данных подключен к третьим информационным входам второго, третьего, четвертого и пятого мультиплексоров, первый выход блока управления подключен к входу задания режима работы блока ввода- вывода, выходы с второго по шестой блока управления подключены к входам записи соответственно регистра входных данных, первого регистра, второго регистра, третьего регистра, регистра результата, выходы с седьмого по тринадцатый блока управления подключены к управляющим входам соответственно выходного мультиплексора, первого, второго, третьего, четвертого, пятого шестого мультиплексоров, четырнадцатый и пятнадцатый выходы блока управления подключены к входам записи - считывания соответственно первого и второго блоков оперативной памяти, шестнадцатый и семнадцатьй выходы блока управления подключены к адресным входам соответственно первого и второго блоков оперативной памяти, восемнадцатьй выход блока управления подключен к входу,кода операции арифметического блока, О т л и ч а ю- щ и и с я тем, что, с Целью повышения

ых, регистр результата, выходной ультиплексор, первый и второй блои оперативной памяти, первый и втоой мультиплексоры, первый и второй егистры, блок умножения, третий и етвертый мультиплексоры, третий регистр, пятый и шестой мультиплексоры, арифметический блок, выход которого подключен к информационному входу регистра результата, выход которого подключен к первому информационному входу первого мультиплексора, первому информационному входу выходного мультиплексора и первым информационным входам второго и третьего мультиплексоров, выход первого мультиплексора подключен к первому информационному входу арифметического блока, вькод выходного мультиплексора подключен к первому информационному входу блока ввода-вывода, выход второго мультиплексора подключен к информационному входу первого блока оперативной памяти, выход третьего мультиплексора подключен к информационному входу второго блока оперативной памяти, выход первого блока оперативной памяти подключен к информационному входу первого ре- гистра, выход которого подключен к первым информационным входам четвертого и пятого мультиплексоров, второму информационному входу третьего мультиплексора, второму информационному входу выходного мультиплексора, первому информационному входу шестого мультиплексора, и второму информационному входу первого мультиплексора, выходы четвертого и пятого

5 мультиплексоров подключены соответственно к первому и второму информационным входам умножителя, выход шестого мультиплексора подключен к второму информационному входу арифметического блока, выход второго .блока оперативной памяти подключен к

I.. ,информационному входу второго регистра, выход которого подключен к вторым информационным входам второго, четвертого и пятого мультиплексоров, третьему информационному входу выходного мультиплексора, второму информационному входу шестого мультиплексора и третьему информационному входу первого мультиплексора,выход блока умножения подключен к информационному входу третьего регистра,выход коо торого подключен к третьему информаци0

онному входу шестого мультиплексора, первый выход блока ввода-вывода подклю- чен к входу блока управления,второй выход блока ввода-вывода подключен к 5 выходу резуль ата устройства, второй информационньй вход блока ввода,-вы- вода подключен к информационному входу устройства, третий информационный вход блока ввода-вывода подключен к входу задания режимов работы устройства, выход регистра входных данных подключен к третьим информационным входам второго, третьего, четвертого и пятого мультиплексоров, первый выход блока управления подключен к входу задания режима работы блока ввода- вывода, выходы с второго по шестой блока управления подключены к входам записи соответственно регистра входных данных, первого регистра, второго регистра, третьего регистра, регистра результата, выходы с седьмого по тринадцатый блока управления подключены к управляющим входам соответственно выходного мультиплексора, первого, второго, третьего, четвертого, пятого, шестого мультиплексоров, четырнадцатый и пятнадцатый выходы блока управления подключены к входам записи - считывания соответственно первого и второго блоков оперативной памяти, шестнадцатый и семнадцатьй выходы блока управления подключены к адресным входам соответственно первого и второго блоков оперативной памяти, восемнадцатьй выход блока управления подключен к входу,кода операции арифметического блока, О т л и ч а ю- щ и и с я тем, что, с Целью повышения ;

5

0

5

0

5

производительности при выполнении котежных операций сложения, вычитания, умножения и деления, в него введены входной мультиплексор, третий блок оперативной памяти, седьмой мульти- плексор, четвертый регистр, первый и второй блоки постоянной памяти,йя- тый и шестой регистры, блок вычисления обратной величины, первый выход блока ввода-вывода подключен к первому информационному входу входного мультиплексора, выход выходного мультиплексора подключен к второму информационному входу входного муль- типлексора, третий информационный вход входного мультиплексора подключен к выходу блока вычисления обратной величины, управляющий вход входного мультиплексора подключен к девятнадцатому выходу блока управления выход входного мультиплексора подключен к информационному входу регистра входных данных, выход кот орого подключен к входу блока вычисления обратной величины и первому информационному входу седьмого мультиплексора, выход регистра результата подключен к второму информационному входу седьмого мультиплексора, выход второго регистра подключен к третьему информационному входу седьмого мультиплексора, выход первого регистра подключен к четвертому информационному входу седьмого мультиплексора, выход которого подключен к информационному входу третьего блока оперативной памяти, управляющий вход седьмого мультиплексора подключен к дванадцатому выходу блока управления, адресный вход третьего блока оперативной памяти подключен к двадцать первому выходу блока управления, вход чтения- записи третьего блока оперативной памяти подключен к двадцать второму выходу блока управления, выход третьего блока оперативной памяти подключен к информационному входу четвертого регистра, вход записи которого подключен к двадцать третьему выходу блока управления, выход четвертого регистра подключен к четвертым информационным входам мультиплексоров с первого по шестой и выходного мультиплексора, выход первого блока постоянной памяти подключен к информационному входу пятого регистра, выход второго блока постонной памяти подключен к информационному входу

5

0

5

0

5

0

5

0

5

шестого регистра, выходы пятого и шестого регистров подключены соответственно к третьему и четвертому информационным входам блока умножения, адресные входы первого и второго блоков постоянной памяти подключены соответственно к двадцать четвертому и двадцать пятому выходам блока управления, входы записи пятого и шестого регистров подключены соответственно к двадцать шестому и двадцать седьмому выходам блока управле ния.

2. Процессор по п. 1, о т л и ч а- ю щ и и с я тем, что блок управления содержит узел пуска-останова, регистр команд, узел микропрограммного управления, счетный узел, узел сравнения, узел формирования адресов,мультиплексор, первый разряд входа блока подключен к входу пуска узла пуска-останова и входу сброса узла микропрограммного управления, второй разряд входа блока подключен к входу записи регистра команд блока, третий разряд входа блока подключен к первому информационному входу мультиплексора условий, остальные разряды входа блока подключены к информационным входам регистра команд блока, выход узла пуска-останова подключен к тактовому входу узла микропрограммного 7 управления, выход поля операций ре- гистра команд подключен ко входу старших разрядов кода команды узла микропрограммного управления, выход поля адреса регистра команд подключен к входу младших разрядов команды узла микропрограммного управления, выходы с первого по шестой узла микропрограммного управления подключены к управляющим входам соот- ;ветственно с первого по шестой узла формирования адресов, седьмой выход узла микропрограммного управления подключен к первому выходу блока, выходы с восьмого по двадцать первый узла микропрограммного управления подключены к выходам соответственно с второго по пятнадцатый блока, выходы с двадцать второго по двадцать восьмой узла микропрограммного управления подключены соответственно к выходам с восемнадцатого по двадцатый, двадцать второму, двадцать третьему, двадцать шестому и двадцать седьмому блока управления, выходы с двадцать девятого по тридцать восьмой узла микропрограммного управления подключены к группе вхо- дов счетного узла. Тридцать девятьй выход узла микропрограммного управления подключен к управляклцему входу мультиплексора условий, сороковой выход узла микропрограммного управления подключен к первому информационному входу мультиплексора условий, сорок первый выход узла микропрограм много управления подключен к входу

останова узла пуска-останова, первый выход счетного узла подключен к первому входу узла сравнения и первому информационному входу узла формирования адресов, выходы с второго по пятый счетного узла подключены к входам с второго по пятьй соответственно узла сравнения и информационным входам с второго по пятый соответственно узла формирования адресов, выход первого поля условий регистра команд подключен к шестому входу узла сравнения, выход второго поля условий регистра команд подключен к седьмому входу узла сравнения, выходы первого и второго полей условий регистра команд объединены и подключены к восьмому входу , узла сравнения, выход четвертого поля условий регистра команд подключен к девятому входу узла формирования адресов, выходы с первого по седьмой узла сравнения подключены к информационным входам соответственно с третьего по девятый мультиплексора условий, выход которого подключен ко входу условий узла микропрограммного управления, выходы с второго по шестой узла формирования адресов подключены соответственно к шестнадцатому, семнадцатому, двадцать второму, двадцать четвертому и двадцать пятому выходам блока уп- равления, при этом узел пуска-останова содержит генератор тактовых импульсов, J-К-триггер, и элемент И и одновибратор, вход пуска узла пуска-останова подключен к входу одно- вибратора, выход которого подключен ко входу J триггера, вход останова узла пуска-останова подключен к входу К триггера, выход генератора тактовых импульсов подключен к первому входу элемента И узла пуска-останова и тактовому входу триггера, прямей выход триггера подключен к второму входу элемента И узла пуска10

15

20

25

30

35

40

45

50

55

останова, выход элемента И узла пуска-останова подключен к выходу узла пуска-останова, при этом счетный узел содержит пять счетчиков, с первого по четвертый входы счетного узла подключены к входам установки в нрль соотйетственно с первого по четвертый счетчиков, пятьй вход счетного узла подключен к входу записи начального значения пятого счетчика, входы с шестого по десятый счетного узла подключены к счетным входам соответственно с первого по пятьй счетчиков, выходы с первого по пятьй счетного узла подключены к выходам соответственно с первого по пятьй счетчиков, выход четвертого счетчика подключен к информационному входу пятого счетчика, при этом узел сравнения содержит с первого по седьмой элементы сравнения и мультиплексор, первый вход узла сравнения подключен к первому входу первого элемента сравнения, второй вход узла сравнения подключен к первому входу .второго элемента сравнения ,и первому входу третьего элемента сравнения, третий вход узла сравнения подключен к первому входу четвертого элемента сравнения, четвертый вход узла сравнения подключен к первому входу пятого элемента сравнения, пятый вход узла сравнения подключен к первому входу шестого элемента сравнения и второму входу третьего элемента сравнения, шестой вход узла сравнения подключен к первому входу седьмого элемента сравнения и первому информационному входу мультиплексора блока сравнения, седьмой вход узла сравнения подключен к второму входу седьмого элемента сравнения и второму информационному входу мультиплексора блока сравнения, восьмой вход узла сравнения подключен к второму входу первого элемента сравнения, девятый вход узла сравнения подключен к второму входу второго элемента сравнения, десятьш вход узла сравнения подключен к второму входу четвертого элемента сравнения, второй вход шестого элемента сравнения подключен к входу нулевого потенциала устройства, выход седьмого элемента сравнения подключен к управляющему входу мультиплексора узла сравнения, вьпсод которого подключен к второму входу пятого элемента сравнения, выход пер-

вого элемента сравнения подключен к первому выходу узла сравнения, выход второго элемента сравнения подключен к второму выходу узла сравнения, выход пятого элемента сравнения подключен к третьему выходу узла сравнения, первый выход третьего элемента сравнения подключен к четвертому выходу узла сравнения, выход четвертого элемента сравнения подключен к пятому выходу узла сравнения, выход шестеро элемента сравнения подключен к шестому выходу узла сравнения, второй выход третьего элемента сравнения подключен к седьмому выход узла сравнения, при этом узел формирования адресов содержит пять сумматоров, три вычитателя, с первой по четвертую постоянные памяти, три мультиплексора, пять регистров адреса, первый информационный вход узла формирования адресов подключен к первым информационным входам первого и второго мультиплексоров.узла формирования адресов, второй информа- ционньш вход узла формирования адресов подключен к первым входам первого сумматора, второго сумматора, вторым информационным входам первого и второго мультиплексоров узла формирования адресов и первому информационному входу третьего мультиплексора узла формирования адресов, третий информационный вход узла формирования адресов подключен к второму входу первого сумма тора, первым входам третьего сумматора, третьего вычитателя и пятого сумматора, четвертый информационный вход узла формирования адресов подключен к первым входам первого и второго вы- читателей, пятьй информационный вход узла формирования адресов подключен к второму входу второго вычитателя и адресн ому входу третьей постоянной памяти, первый управляющий вход узла формирования адресов подключен к управляющим входам мультиплексора с первого по третий узла формирования адресов, второй, третий, четвертьй управляющие входы узла формирования адресов подключены к синхровходам соответственно пятого, четвертого и третьего регистров адреса узла формирования адресов, пятый, шестой управляющие входы узла формирования

o

5

0

5

0

5

0

5

0

5

адресов подключены к входам записи соответственно первого и второго регистров адреса узла формирования адресов, выход .первого сумматора подключен к второму входу первого вычитателя и адресному входу первой постоянной памяти, выход первого вычитателя подключен к адресному входу второй постоянной памяти, выход третьей постоянной памяти подключен к второму входу второго сумматора, выход второго вычитателя подключен к второму входу третьего вычитателя, адресному входу четвертой постоянной памяти и первому выходу узла формирования адресов, выход первой постоянной памяти подключен к второму входу третьего сумматора, выход второй постоянной памяти подключен к первому входу четвертого сумматора, выход второго сумматора подключен к информационному входу первого регистра адреса узла формирования адресов, выход четвертой постоянной памяти подключен к второму входу пятого сумматора, выход которого подключен к информационному входу второго регистра .адреса узла формирования адресов, выход третьего вычитателя подключен к второму входу четвертого сумматора, выход третьего сумматора подключен к третьим информационным входам первого и второго мультиплексоров и второму и третьему информационным входам третьего мультиплексора узла формирования адресов, выход четвертого сумматора подключен к четвертым информационным входам с первого по третий мультиплексоров узла формирования адресов, выходы первого, второго и третьего мультиплексоров узла формирования адресов подключены к информационным входам соответственно третьего, четвертого, пятого регистров адреса узла формирования адресов, выходы пятого, четвертого и третьего регистров адреса узла формирования адресов подключены соответственно к второму, третьему и четвертому выходам узла формирования адресов, выходы первого и второго регистров адреса узла формирования адресов подключены к пятому шестому выходам узла формирования адре - сов.

Ocmomi. л.

Щ/ага

фиг.З

&-Ш

., J5

т

117

т

.0

Г

9u.7

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

Изобретение относится к области вычислительной техники и может использоваться при построении вычислительных систем для реализации операций над дифференциальными кортежами, в частности при решении дифференциальных уравнений в частных производных. Цель изобретения - повьш1е- ние производительности при выполнении кортежных операций сложения, вычитания, умножения и деления. Поставленная цель достигается тем, что процессор содержит блок ввода-вывода, блок управления, регистр входных данных, регистр результата, входной и выходной мультиплексоры, с первого по третий блоки оперативной памяти, с первого по седьмой мультиплексоры, с первого по шестой регистры, блок умножения, арифметический блок,первый и второй блоки постоянной памяти, блок вычисления обратной величины. Повьш1ение производительности достигается за счет организации конвейерных вычислений для кортежных операций. 1 з.п. ф-лы, 8 ил. с б (Л ISD 00 а

| Семерджан М.А., Налбандян Ж.С | |||

| Пластинчатый предохранитель для трубопроводов высокого давления | 1925 |

|

SU2345A1 |

| -Изд-вс Финансы и статистика, 1984 | |||

| Патент США № 4150434, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-28—Публикация

1985-04-30—Подача