Изобретение относится-к вычисли- тельной технике и может быть использовано для построения быстродействующих микропрограммных процессоров с 5 динамическим микропрограммированием. Целью изобретения является расширение области применения микропрограммного процессора за счет возможности комплексирования его с другими ЭВМ. fO

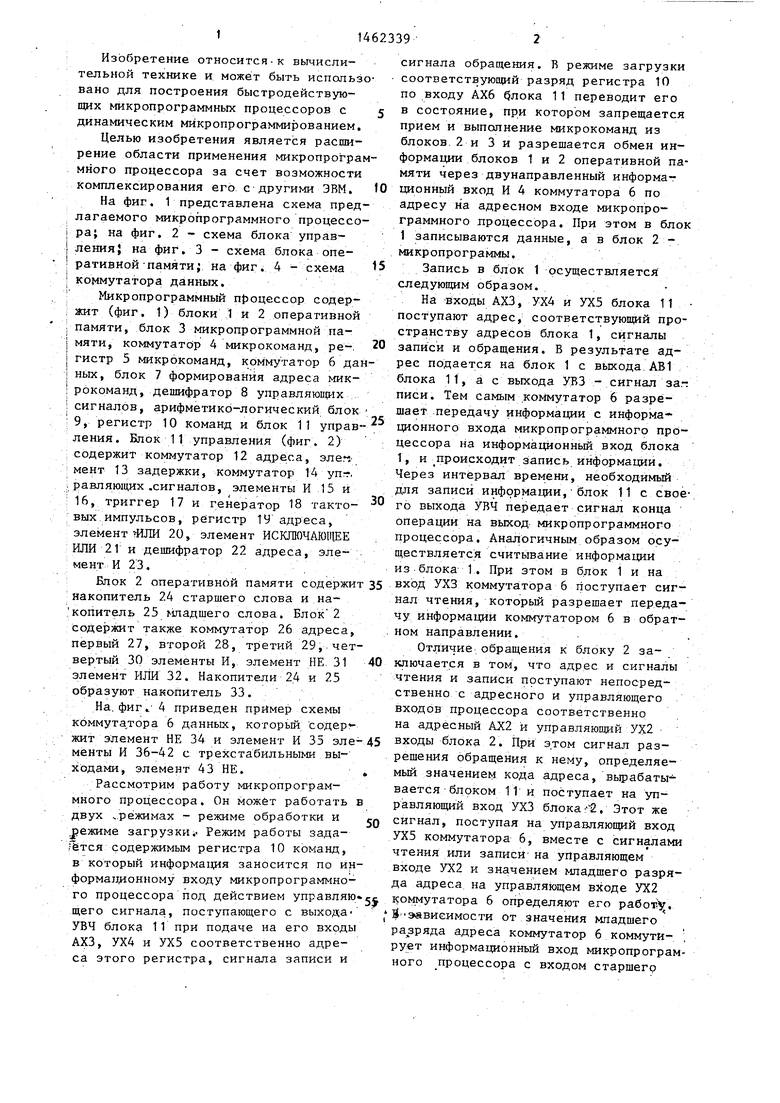

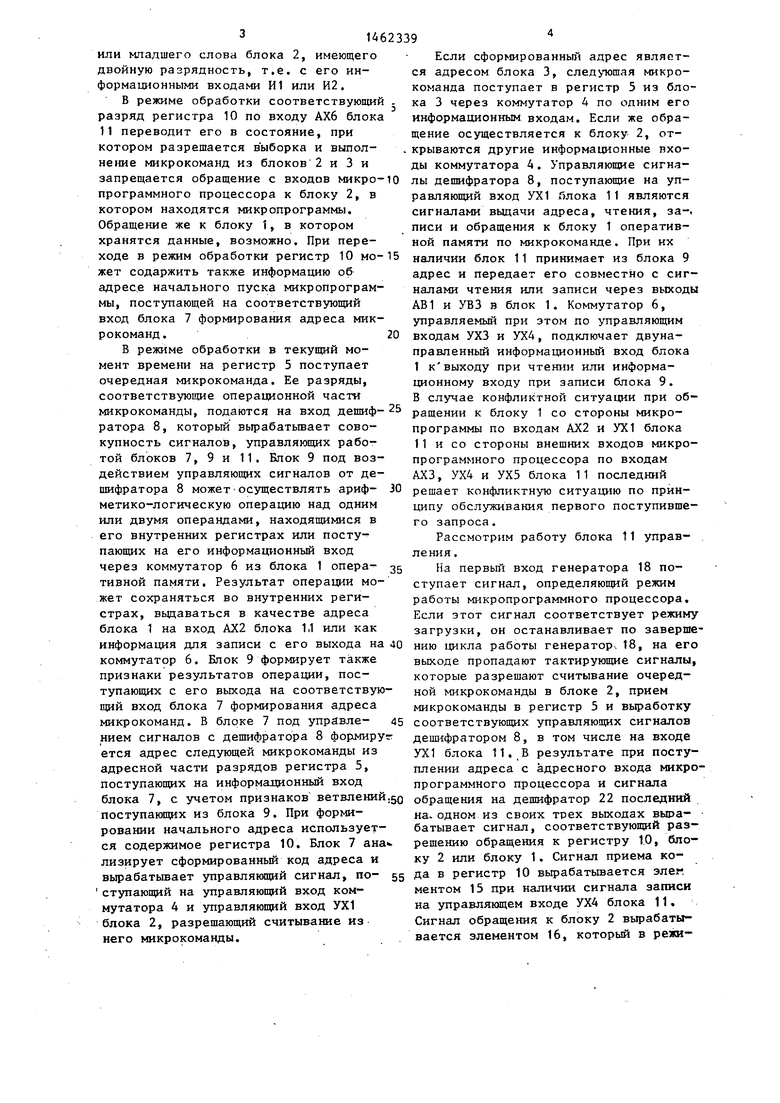

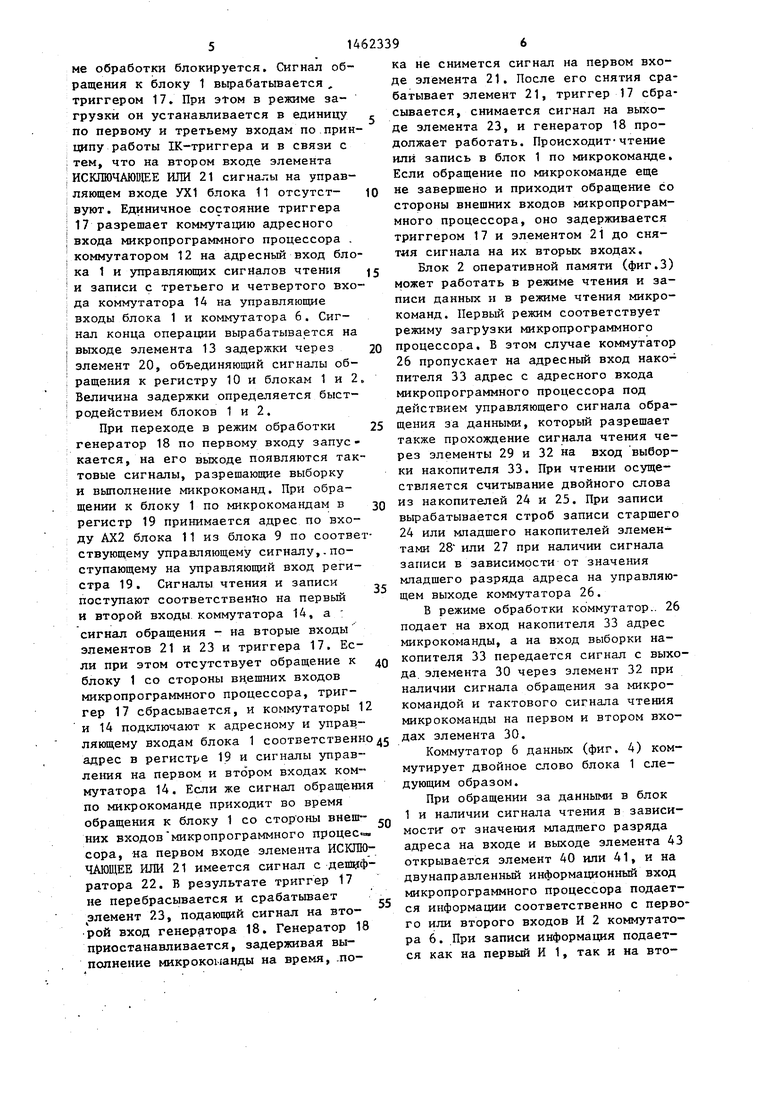

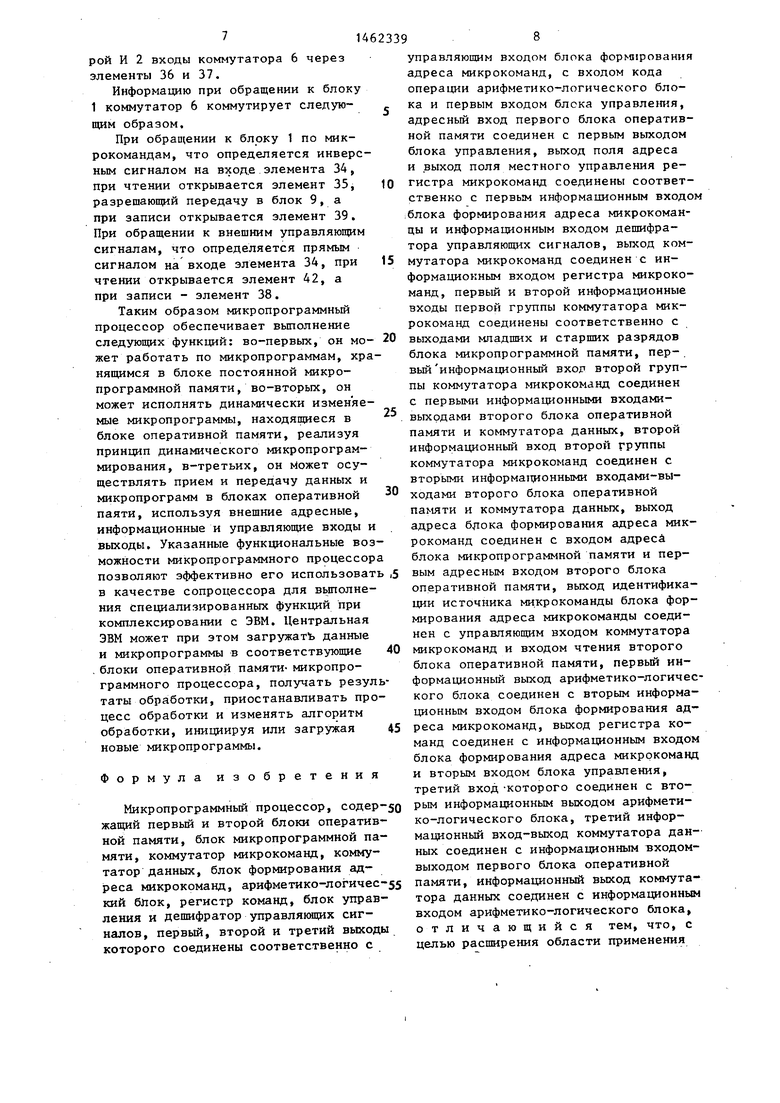

На фиг. Г представлена схема пред- лагаемого микропрограммного процессо- ра; на фиг. 2 - схема блока управ- ления на фиг. 3 - схема блока опе- ративной-памяти; на фиг. 4 - схема 15 коммутатора данных.

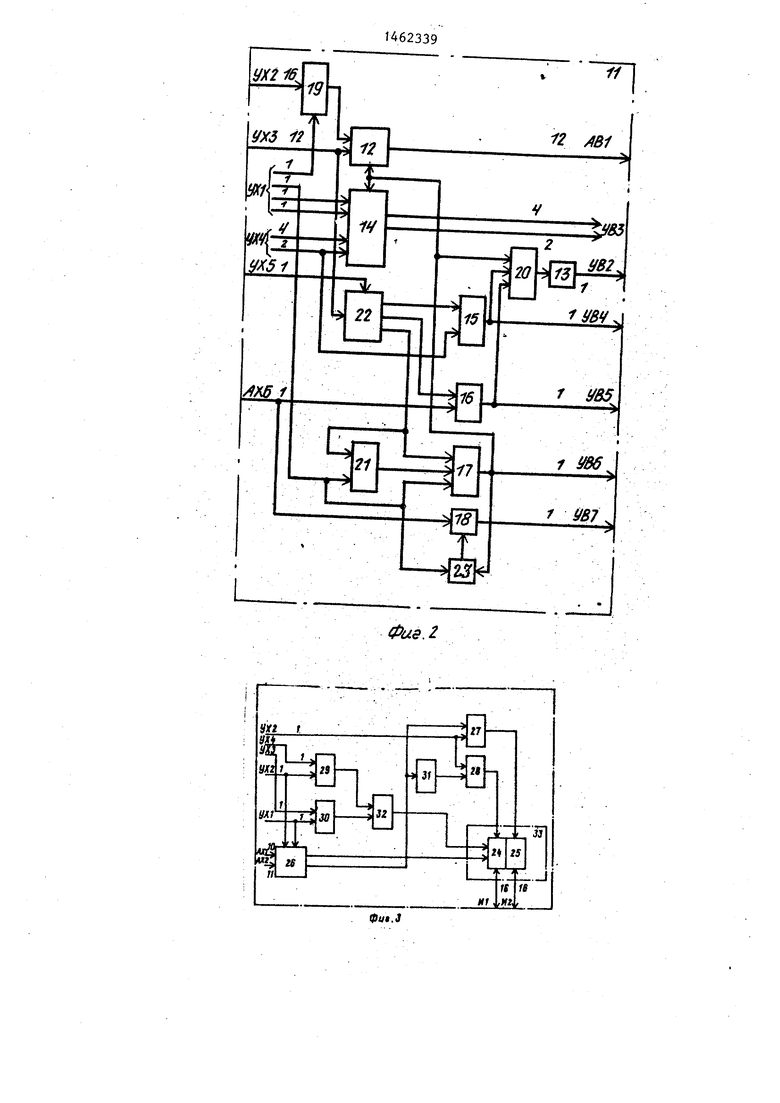

Микропрограммный п зоцессор содер- жит (фиг. 1) блоки 1 И 2 оперативной памяти, блок 3 микропрограммной памяти, коммутатор 4 микрокоманд, ре-. 20 гистр 5 микрокоманд, коммутатор 6 данных, блок 7 формирования адреса микрокоманд, дешифратор 8 управляюпц.1х сигналов, арифметико-логический блок 9, регистр 10 команд и блок 11 управ- 5 ления. Блок 11 управления (фиг. 2) содержит коммутатор 12 адреса, эле.,- мент 13 задержки, коммутатор 14 упгг, равляющих .сигналов, элементы И 15 и 16, триггер 17 и генератор 18 такто- О вых импульсов, регистр ty адреса, элемент 41ЛИ 20, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 21 и дешифратор 22 адреса, эле- . мент И 23.

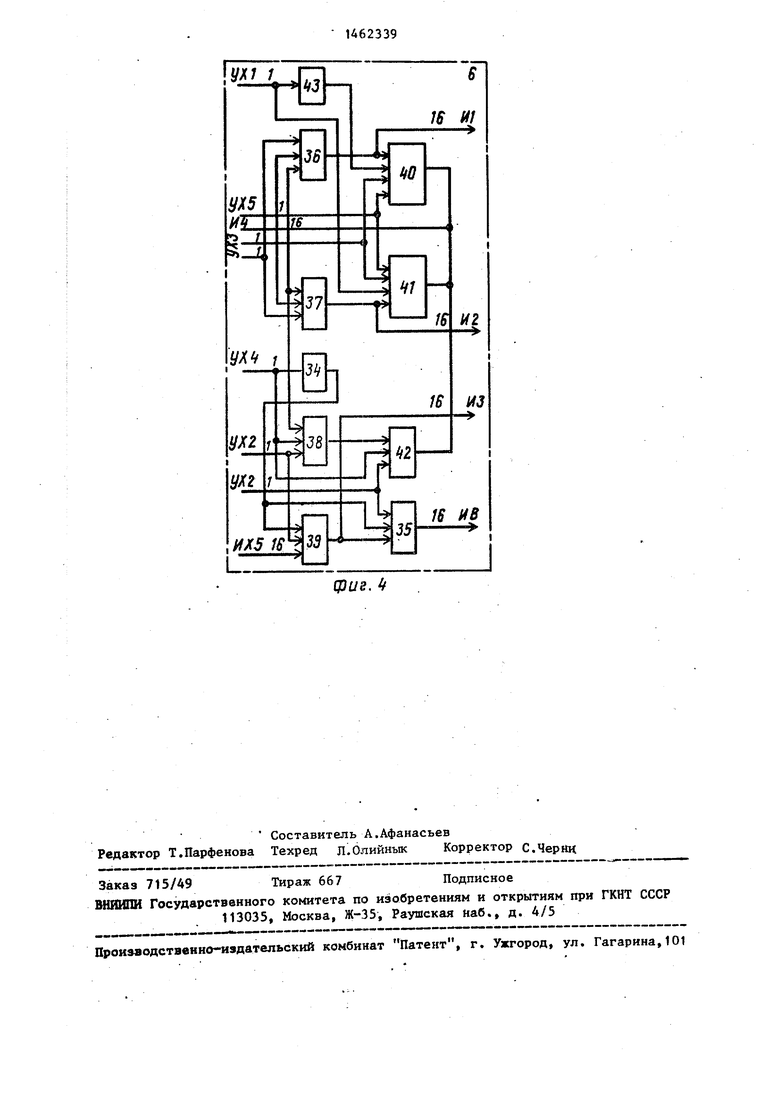

Клок 2 оперативной памяти содержит 35 накопитель 24 старшего слова и на- копитель 25 шaдшeгo слова. Блок 2 Содержит также коммутатор 26 адреса, первый 27, второй 28, 29,. четвертый 30 элементы И, элемент НЕ 31 40 элемент ИЛИ 32. Накопители 24 и 25 образуют накопитель 33.

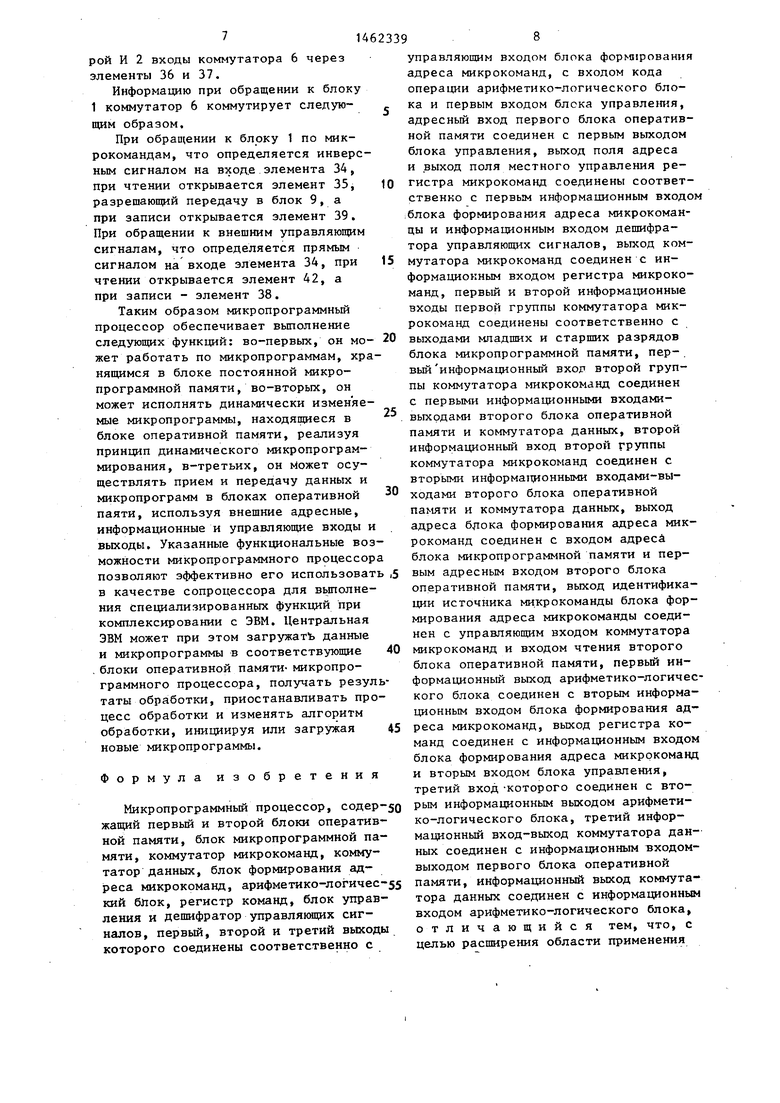

На. фиг..- 4 приведен пример схемы к6ммута,тора 6 данных, который содер - жит элемент НЕ 34 и элемент И 35 эле-45 менты И 36-42 с трехстабильными выходами, элемент 43 НЕ.,

Рассмотрим работу микропрограммного процессора. Он может работать в двух ..режимах - режиме обработки и ,. Jpeжимe загрузкиi- Режим работы зада- .ется содержимым регистра 10 команд, в который информа1 ия заносится по ин- форма11ионному входу микропрограммного процессора под действием управляющее щего сигнала, поступающего с выхода- УВЧ блока 11 при подаче на его входы АХЗ, УХ4 и УХ5 соответственно адреса этого регистра, сигнала записи и

сигнала обращения. В режиме загрузки соответствующий разряд регистра 10 по входу АХ6 блока 11 переводит его в состояние, при котором запрещается прием и выполнение микрокоманд из блоков. 2 и 3 и разрешается обмен информации блоков 1 и 2 оперативной памяти через двунаправленный информационный вход И 4 коммутатора 6 по адресу н а адресном входе микропрограммного процессора. При этом в блок 1 записываются данные, а в блок 2 - микропрограммы.

Запись в блок 1 осуществляется следующим образом..

На входы АХЗ, УХ4 и УХ5 блока 11 - поступают адрес, соответствующий пространству адресов блока 1, сигналы записи и обращения. В результате адрес подается на блок 1 с вькода АЫ блока 11, а с выхода УВЗ - сигнал за.г писи. Тем самым коммутатор 6 разрешает .передачу информации с информационного входа микропрограммного процессора на информационный вход блока 1, и происходит запись информации. Через интервал времени, необходимый для записи информащи, блок 11 с своего выхода УВЧ передает сигнал конца операции на выход микропрограммного процессора. Аналогичным образом осуществляется считывание информации из.блока 1. При этом в блок 1 и на ; вход УХЗ коммутатора 6 поступает сигнал чтения, который разрешает передачу информации коммутатором 6 в обрат- ном направлении. .

Отличие-обращения к блоку 2 заключается в том, что адрес и сигналы чтения и записи поступают непосредственно с адресного и управляющего входов процессора соответственно на адресный АХ2 и управляющий УХ2 - входы блока 2. При этом сигнал разрешения обращения к нему, определяемый значением кода адреса, вырабаты вается блоком 11 и поступает на управляющий вход УХЗ блока :-2. Этот же сигнал, поступая на управляющий вход УХ5 коммутатора 6, вместе с сигналами чтения или записи на управляющем входе УХ2 и значением младшего разряда адреса на управляющем входе УХ2 коммутатора 6 определяют его работу. S зависимости от значения младшего разряда адреса коммутатор 6 коммути- рует информационный вход микропрограм- ного процессора с входом старшего

31462339

или младшего слова блока 2, имеющего

к л

двойную разрядность, т.е. с его информационными входами И1 или И2.

В режиме обработки соответствующий разряд регистра 10 по входу АХб блока 11 переводит его в состояние, при котором разрешается выборка и вьтол- нение микрокоманд из блоков 2 и 3 и запрещается обращение с входов микропрограммного процессора к блоку 2, в котором находятся микропрограммы. Обращение же к блоку 1, в котором хранятся данные, возможно. При переходе в режим обработки регистр 10 ножет содаржить также информацию о& адресе начального пуска микропрограммы, поступающей на соответствующий вход блока 7 формирования адреса микрокоманд .

В режиме обработки в текущий момент времени на регистр 5 поступает очередная микрокоманда. Ее разряды, соответствующие операционной части микрокоманды, подаются на вход дешиф- ратора 8, который вырабатьтает совокупность сигналов, управляющих работой блоков 7, 9 и 11. Блок 9 под воздействием управляющих сигналов от дешифратора 8 можетосуществлять ариф- метико-логическую операцию над одним или двумя операндами, находящимися в его внутренних регистрах или поступающих на его информационный вход через коммутатор 6 из блока 1 оперативной памяти. Результат операции может сохраняться во внутренних регистрах, вьщаваться в качестве адреса блока 1 на вход АХ2 блока 1,1 или как

информация для записи с его выхода на 40 нию цикла работы генератор-. 18, на его коммутатор 6. Блок 9 формирует также

выходе пропадают тактирующие сигналы, которые разрешают считывание очередной микрокоманды в блоке 2, прием микрокоманды в регистр 5 и вьтработку соответствующих управляющих сигналов дешифратором 8, в том числе на входе УХ1 блока 11. В результате при поступлении адреса с адресного входа микропрограммного процессора и сигнала

признаки результатов операции, поступающих с его выхода на соответствующий вход блока 7 формирования адреса микрокоманд. В блоке 7 под упрявле- 45 нием сигналов с дешифратора 8 фор1мируг ется адрес следующей микрокоманды из адресной части разрядов регистра 5, поступающих на информадионный вход блока 7, с учетом признаков ветвлений.5о обращения на дешифратор 22 последний

выходе пропадают тактирующие сигналы которые разрешают считывание очередной микрокоманды в блоке 2, прием микрокоманды в регистр 5 и вьтработку соответствующих управляющих сигналов дешифратором 8, в том числе на входе УХ1 блока 11. В результате при поступлении адреса с адресного входа микро программного процессора и сигнала

поступающих из блока 9. При формировании начального адреса используется содержимое регистра 10. Блок 7 ана. лизирует сформированный код адреса и вырабатьшает управляющий сигнал, по- 55 ступаюш й на управляющий вход коммутатора 4 и управляющий вход УХ1 блока 2, разрешающий считывание из него микрокоманды.

на- одном из своих трех выходах выра- батывает сигнал, соответствующий разрешению обращения к регистру 1.0, блоку 2 или блоку 1. Сигнал приема кода в регистр 10 вырабатывается элег. ментом 15 при наличии сигнала записи на управляющем входе УХ4 блока 11. Сигнал обращения к блоку 2 вырабатывается элементом 16, который в ражи

5 0

5

Если сформированньт адрес является адресом блока 3, следующая микрокоманда поступает в регистр 5 из блока 3 через коммутатор 4 по одним его информационным входам. Если же обращение осуществляется к блоку 2, открываются другие информационные входы коммутатора 4. Управляющие сигналы дешифратора 8, поступающие на управляющий вход УХ1 Г)лока 11 являются сигналами выдачи адреса, чтения, за-, писи и обращения к блоку 1 оперативной памяти по микрокоманде. При их наличии блок 11 принимает из блока 9 адрес и передает его совместно с СИ1- налами чтения или записи через выходы АВ1 и УВЗ в блок 1. Коммутатор 6, управляемый при этом по управляющим входам УХЗ и УХ4, подключает двунаправленный информационный вход блока

Iк выходу при чтении или информационному входу при записи блока 9.

В случае конфликтной ситуации при обращении к блоку 1 со стороны микропрограммы по входам АХ2 и УХ1 блока

I1и со стороны внешних входов микропрограммного процессора по входам АХЗ, УХ4 и УХЗ блока 11 последний решает конфликтную ситуацию по принципу обслуживания первого поступившего запроса.

Рассмотрим работу блока 11 управления .

На первый вход генератора 18 поступает сигнал, определяющий режим работы микропрограммного процессора. Если этот сигнал соответствует режиму загрузки, он останавливает по завершению цикла работы генератор-. 18, на его

обращения на дешифратор 22 последний

выходе пропадают тактирующие сигналы, которые разрешают считывание очередной микрокоманды в блоке 2, прием микрокоманды в регистр 5 и вьтработку соответствующих управляющих сигналов дешифратором 8, в том числе на входе УХ1 блока 11. В результате при поступлении адреса с адресного входа микропрограммного процессора и сигнала

на- одном из своих трех выходах выра- батывает сигнал, соответствующий разрешению обращения к регистру 1.0, блоку 2 или блоку 1. Сигнал приема кода в регистр 10 вырабатывается элег. ментом 15 при наличии сигнала записи на управляющем входе УХ4 блока 11. Сигнал обращения к блоку 2 вырабатывается элементом 16, который в ражи51462339

е обработки блокируется. Сигнал обащения к блоку 1 вырабатывается , триггером 17. При этом в режиме загрузки он устанавливается в единицу по первому и третьему входам по принципу работы 1К-триггера и в связи с тем, что на втором входе элемента СКЛЮЧАЮПСЕЕ ИЛИ 21 сигналы на управ- ляющем входе УХ1 блока 11 отсутст- Ю БУЮТ. Единичное состояние триггера 17 разрешает коммутацию адресного входа микропрограммного процессора . коммутатором 12 на адресный вход бло- ка 1 и управляющих сигналов чтения 15 записи с третьего и четвертого входа коммутатора 14 на управляющие входы блока 1 и коммутатора 6. Сигнал конца операции вырабатывается на выходе элемента 13 задержки через элемент 20, объединяющий сигналы обращения к регистру 10 и блокам 1 и 2,, Величина задержки определяется быстродействием блоков 1 и 2.

При переходе в режим обработки генератор 18 по первому входу запус- кается, на его выходе появляются тактовые сигналы, разрешающие выборку и выполнение микрокоманд. При обращении к блоку 1 по микрокомандам в регистр 19 принимается адрес по входу АХ2 блока 11 из блока 9 по соответ ствующему управляющему сигналу,-поступающему на управляющий вход регистра 19. Сигналы чтения и записи поступают соответственно на первый и второй входы, коммутатора 14, а : сигнал обращения - на вторые входы элементов 21 и 23 и триггера 17. Если при этом отсутствует обращение к блоку 1 со стороны внешних входов микропрограммного процессора, триггер 17 сбрасывается, и коммутаторы 12 и 14 подключают к адресному и управ20

25

30

35

40

Х Н llU ruJijv - ci. L х t(f - J -- . ОА

ляющему входам блока 1 соответственно45 дах элемента 30.

ка не снимется сиг де элемента 21. По батывает элемент сывается, снимает де элемента 23, и должает работать. или запись в блок Если обращение по не завершено и пр стороны внешних в много процессора, триггером 17 и эл тия сигнала на их

Блок 2 операти может работать в писи данных и в р команд. Первый ре режиму загрузки м процессора. В это 26 пропускает на пителя 33 адрес с микропрограммного действием управля щения за данными, также прохождение рез элементы 29 и ки накопителя 33 ствляется считыва из накопителей 24 вьфабатывается ст 24 или младшего н тами 28 или 27 пр записи в зависим младшего разряда щем выходе комму

В режиме обра подает на вход н микрокоманды, а копителя 33 пере да, элемента 30 ч наличии сигнала командой и такто микрокоманды на

адрес в регистре 19 и сигналы управления на первом и втором входах коммутатора 14. Если же сигнал обращения по микрокоманде приходит во время обращения к блоку 1 со стороны внеш-- р них входов микропрограммного процес™ сора, на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21 имеется сигнал с дешифратора 22. В результате триггер 17 не перебрасывается и срабатывает элемент 23, подающий сигнал на вто- .рой вход генератора 18. Генератор 18 приостанавливается, задерживая выполнение микрокоманды на время, -поКоммутатор 6 мутирует двойное дующим образом.

При обращении 1 и наличии сигн мости- от значени адреса на входе открывается элем двунаправленный микропрограммног ся информации со го или второго в ра 6. .При записи ся как на первый

0

5

0

5

40

ОА

ка не снимется сигнал на первом входе элемента 21. После его снятия срабатывает элемент 21, триггер 17 сбрасывается, снимается сигнал на выходе элемента 23, и генератор 18 продолжает работать. Происходит-чтение или запись в блок 1 по микрокоманде. Если обращение по микрокоманде еще не завершено и приходит обращение со стороны внешних входов микропрограммного процессора, оно задерживается триггером 17 и элементом 21 до снятия сигнала на их вторых входах.

Блок 2 оперативной памяти (фиг.З) может работать в режиме чтения и записи данных и в режиме чтения микрокоманд. Первый режим соответствует режиму загрузки микропрограммного процессора. В этом случае коммутатор 26 пропускает на адресный вход накопителя 33 адрес с адресного входа микропрограммного процессора под действием управляющего сигнала обращения за данными, который разрешает также прохождение сигнала чтения через элементы 29 и 32 на вход выборки накопителя 33. При чтении осуществляется считывание двойного слова из накопителей 24 и 25. При записи вьфабатывается строб записи старшего 24 или младшего накопителей элементами 28 или 27 при наличии сигнала записи в зависимости от значения младшего разряда адреса на управляющем выходе коммутатора 26.

В режиме обработки коммутатор.. 26 подает на вход накопителя 33 адрес микрокоманды, а на вход выборки накопителя 33 передается сигнал с выхода, элемента 30 через элемент 32 при наличии сигнала обращения за микрокомандой и тактового сигнала чтения микрокоманды на первом и втором входах элемента 30.

Коммутатор 6 данных (фиг. 4) коммутирует двойное слово блока 1 следующим образом.

При обращении за данными в блок 1 и наличии сигнала чтения в зависимости- от значения младшего разряда адреса на входе и выходе элемента 43 открывается элемент 40 или 41, и на двунаправленный информационный вход микропрограммного процессора подается информации соответственно с первого или второго входов И 2 коммутатора 6. .При записи информация подается как на первый И 1, так и на вто

рой И 2 входы коммутатора 6 через элементы 36 и 37.

Информацию при обращении к блоку 1 коммутатор 6 коммутирует следую-

щим образом.

При обращении к блоку 1 по микрокомандам, что определяется инверсным сигналом на входе элемента 34, при чтении открывается элемент 35, 1 разрешающий передачу в блок 9, а при записи открывается элемент 39. При обращении к внешним управляющим сигналам, что определяется прямым сигналом на входе элемента 34, при 1 чтении открывается элемент 42, а при записи - элемент 38,

Таким образом микропрограммный процессор обеспечивает выполнение следующих функций: во-первых, он мо- жет работать по микропрограммам, хранящимся в блоке постоянной микропрограммной памяти, во-вторых, он может исполнять динамически изменяемые микропрограммы, находящиеся в блоке оперативной памяти, реализуя принцип динамического микропрограммирования, в-третьих, он Может осуществлять прием и передачу данных и микропрограмм в блоках оперативной паяти, используя внещние адресные, информационные и управляющие входы и выходы. Указанные функциональные возможности микропрограммного процессора позволяют эффективно его использовать в качестве сопроцессора для выполнения специализированных функций при комплекскровании с ЭВМ. Центральная ЭВМ может при этом загружать данные и микропрограммы в соответствующие .блоки оперативной памяти- микропрограммного процессора, получать результаты обработки, приостанавливать процесс обработки и изменять алгоритм обработки, инициируя или загружая новые микропрограммы.

Формула изобретения

Микропрограммный процессор, содержащий первый и второй блоки оперативной памяти, блок микропрограммной памяти, коммутатор микрокоманд, коммутатор данных, блок формирования адреса микрокоманд, арифметико-логический блок, регистр команд, блок управления и дешифратор управляющих сигналов, первый, второй и третий выходы которого соединены соответственно с

5

0 5

0 . ,5 40 45

50 55

управляющим входом блока форьшрования адреса микрокоманд, с входом кода операции арифметико-логического блока и первым входом блока управления, адресный вход первого блока оперативной памяти соединен с первым выходом блока управления, выход поля адреса и выход поля местного управления регистра микрокоманд соединены соответственно с первым информационным входом )блока формирования адреса микрокоманды и информационным входом дешифратора управляющих сигналов, выход коммутатора микрокоманд соединен с информационным входом регистра микрокоманд, первый и второй информационные входы первой группы коммутатора микрокоманд соединены соответственно с выходами младших и старших разрядов блока микропрограммной памяти, пер-. вый информационный вход второй группы коммутатора микрокоманд соединен с первыми информационными входами- выходами второго блока оперативной памяти и коммутатора данных, второй информационный вход второй группы коммутатора микрокоманд соединен с вторыми информационными входами-выходами второго блока оперативной памяти и коммутатора данных, выход адреса блока формирования адреса микрокоманд соединен с входом адресА блока микропрограммной памяти и первым адресным входом второго блока оперативной памяти, выход идентификации источника микрокоманды блока формирования адреса микрокоманды соединен с управляющим входом коммутатора микрокоманд и входом чтения второго блока оперативной памяти, первый информационный выход арифметико-логического блока соединен с вторым информационным входом блока формирования адреса микрокоманд, выход регистра команд соединен с информационным входом блока формирования адреса микрокоманд и вторым входом блока управления, третий вход -которого соединен с вторым информационным выходом арифметико-логического блока, третий информационный вход-выход коммутатора данных соединен с информационным входом- выходом первого блока оперативной памяти, информационный выход коммутатора данных соединен с информационным входом арифметико-логического блока, отличающийся тем, что, с целью расширения области применения

за счет возможности его комнлексиро- вания с другими ЭВМ, информационный вход-выход микропрограммного процессора соединен с информационным входом регистра команд и четвертьш информационным входом-выходом коммутатора данных, информационный вход микропрограммного процессора соединен с четвертым входом блока управления, первым управляющим входом коммутатора данных и с вторым адресным входом второго блока оперативной памяти, вход признака ввода информации микропрограммного процессора соединен с входом записи второго блока оперативной памяти с вторым управляющим входом KOMisiyTaTopa данных и пятьм входом блока уцравления, вход признака вывода информации микропрограммного процессора соединен с шестьп входом блока управления, выход признака окончания операции микропрограммного процессора соединен с вторым выходом блока управления, пятый информацион- ный выход коммутатора данных соединен с третьим информационным выходом арифметико-логического блока, третий выход блока управления соединен с

входом управления режимом первого

блока оперативной памяти и третьим управляющим входом коммутатора данных, четвертьй выход блока управления соединен с входом записи регистра команд, пятый выход блока управ- ления соединен с четвертым управляющим входом коммутатора данных, шесто выход блока управления соединен с пятым управляющим входом коммутатора данных и первым входом выборки вто- рого блока оперативной памяти, седьмой выход блока управления соединен со стробирующим входом шифратора управляющих сигналов, синхровходом регстра микрокоманд и вторым входом вы- борки второго блока оперативной памяти, причем блок управления содержит коммутатор адреса, первый, второй -и третий элементы И, триггер, элемент задержки, коммутатор управ- ляющих сигналов, генератор тактовых импульсов, регистр адреса, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, дещифpatop адреса, вход выборки которого соединен с шестым входом блока уп- равления, второй вход которого сое5 0 5

0

.5 0 5Q 5

динен с входом запуска генератора и с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ и с пятым выходом блока управления, третий вход которого Соединен с информационным входом регистра . адреса, выход которого соединен с первым информационным входом коммутатора адреса, выход которого соединен с первым выходом блока управления, четвертый вход которого соединен с вторым информационным входом коммутатора адреса и информационным входом дещифратора адреса, первый и второй выходы которого соединены соответственно с вторым входом первого и первым входом второго элементов И, выход которого соединен с вторым входом элемента ИЛИ и четвертым вьрсодом блока управления, первый разряд первого входа которого соединен с входом записи регистра адресаj второй разряд первого входа блока управления соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первым информационным входом триггера и первым входом третьего элемента И, выход которого соединен с входом блокировки генератора тактовых импульсов, выход которого соединен с седьмым входом блока управления, остальные разряды первого входа которого соединены с первым информационным входом коммутатора управляющих сигналов, выход которого соединен с третьим выходом блока управления, пятьй вход которого соединен с вторьм входом коммутатора управляющих сигналов, причем мпадший разряд этого входа соединен с вторым входом второго элемента И, третий выход дешифратора адреса соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым информационным входом триггера, выход которого соединен с управляющими входами коммутаторов адреса и управляющих сигналов, вторым входом третьего элемента И, шестым выходом блока управления и третьим входом элемента Ш1И, выход которого соединен с входом элемента задержки, выход которого соединен с вторым выходом блока управления, выход элемента ИСКгаОЧАЮиЩЕ ИЛИ соединен с синхро- входом триггера.

//

/ т

УВ7

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих микропрограммных процессоров с динамическим микропрограммированием. Цель изобретения - расширение области нрименения микропрограммного процессора за счет комплексирования его с другим ЭВМ. Ыкропрограммш 1й процессор содержит блоки 1 и 2 оперативной памяти, блок 3 микропрограммной памяти, коммутатор 4 микрокоманд, регистр 5 микрокоманд, коммутатор 6 данных, блок 7 формирования адреса микрокоманд, дешифратор 8 управляющих сигналов, арифметико-логический блок 9, регистр 10 команд и блок 11 управле . кия. 4 ил.

Фаз. 2.

физ.

| Патент США № 3859636, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1986-06-09—Подача