Изобретение относится к вычислительной технике и может быть использовано в процессорах, архитектура которых предполагает использование буферной памяти, конвейерного выполнения команд.

Целью изобретения является повышение быстродействия устройства.

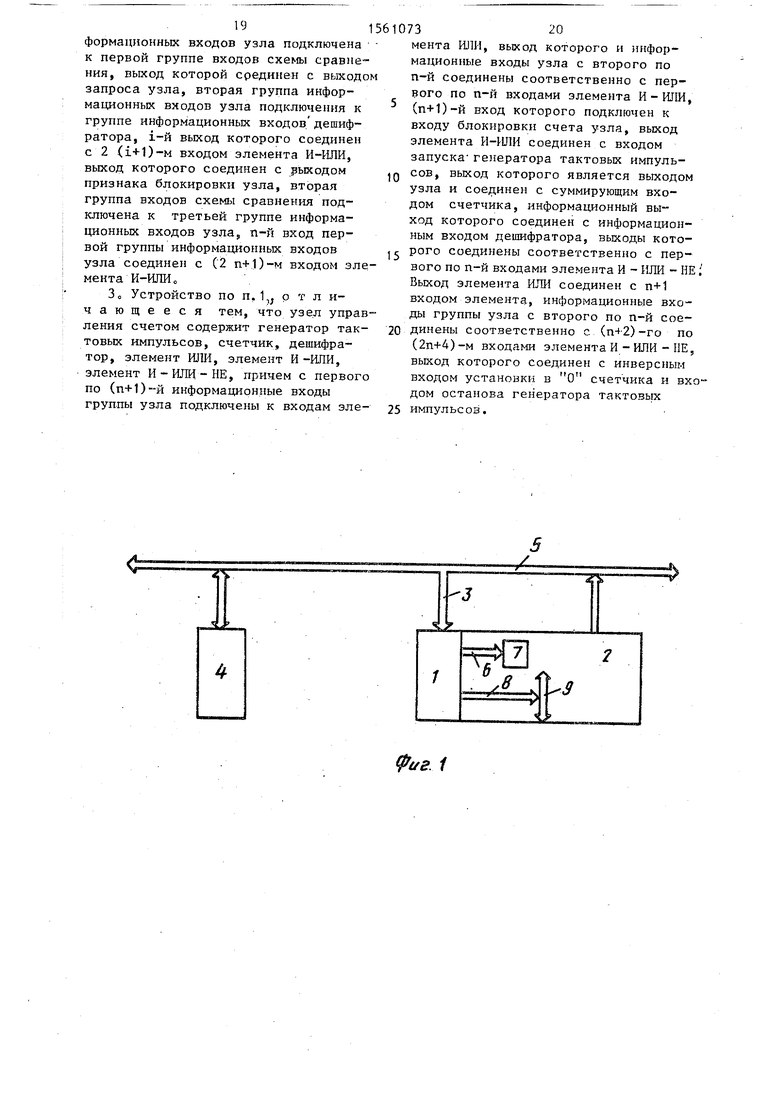

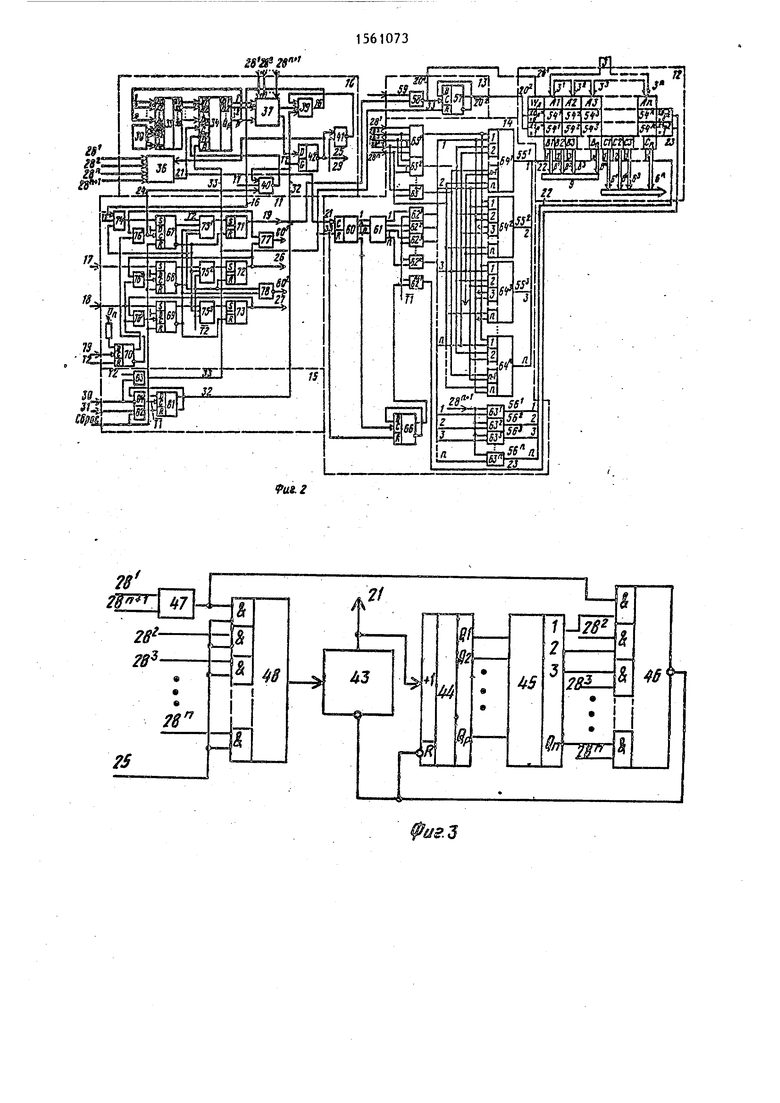

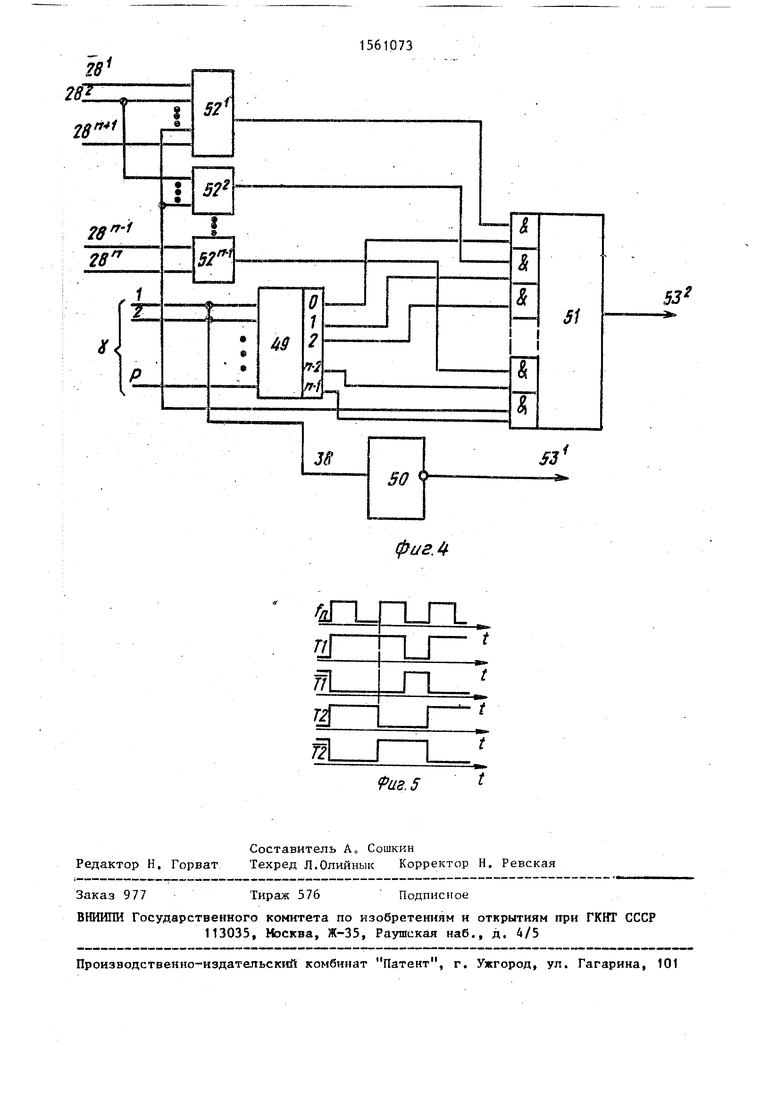

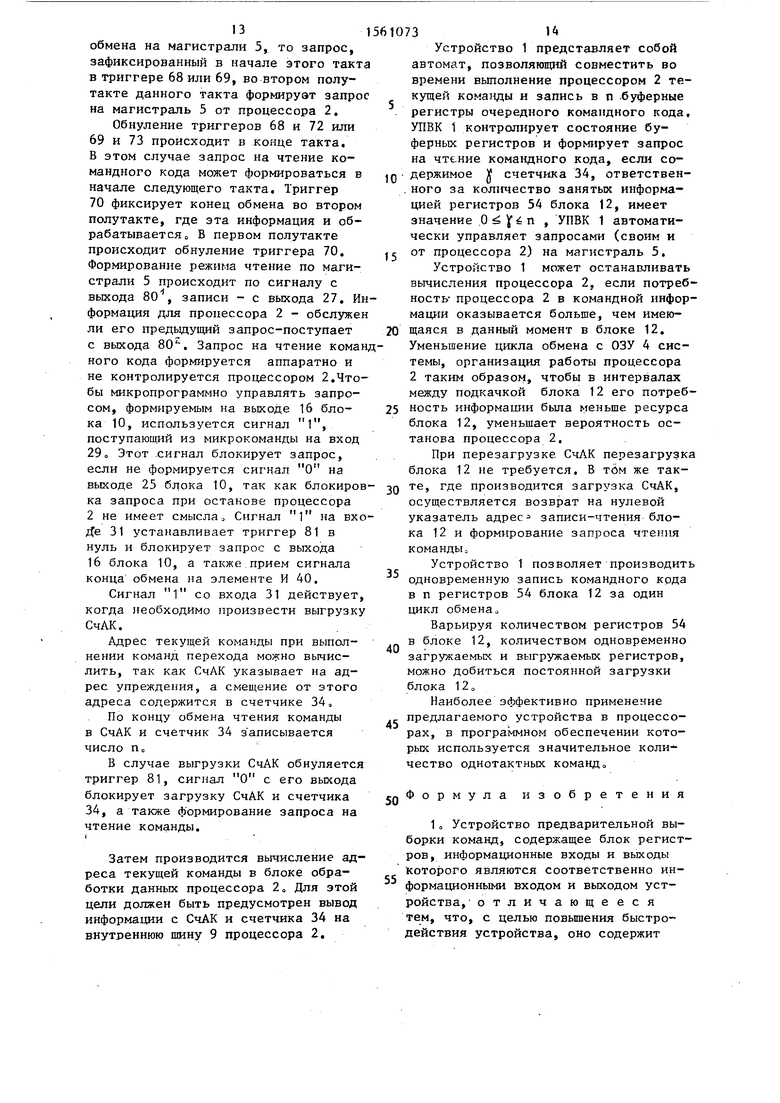

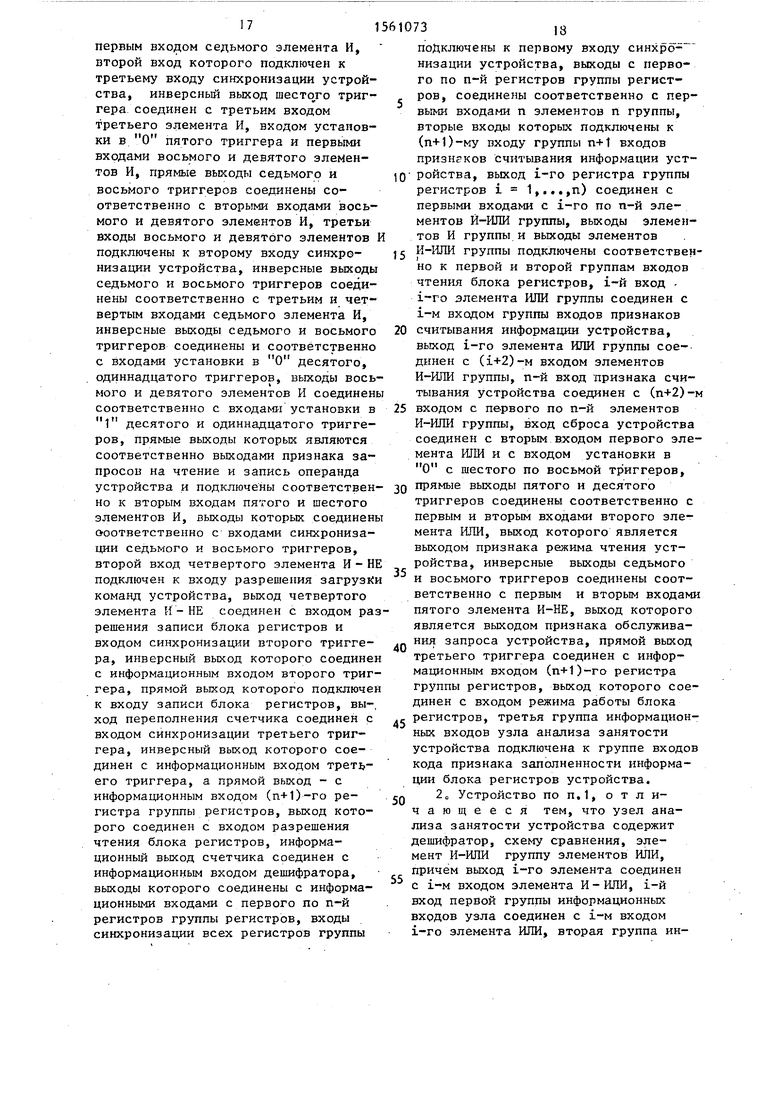

На фиг.1 представлен пример реализации электронной вычислительной машины, включающий данное устройство; на фиг.2 - функциональная схема устройства предварительной выборки команд- на фиг„3 - функциональная схема узла управления счетом; на фиг.4 - функциональная схема узла анализа занятости устройства на фиг„5 - временная диаграмма тактовой последовательности импульсов процессора.

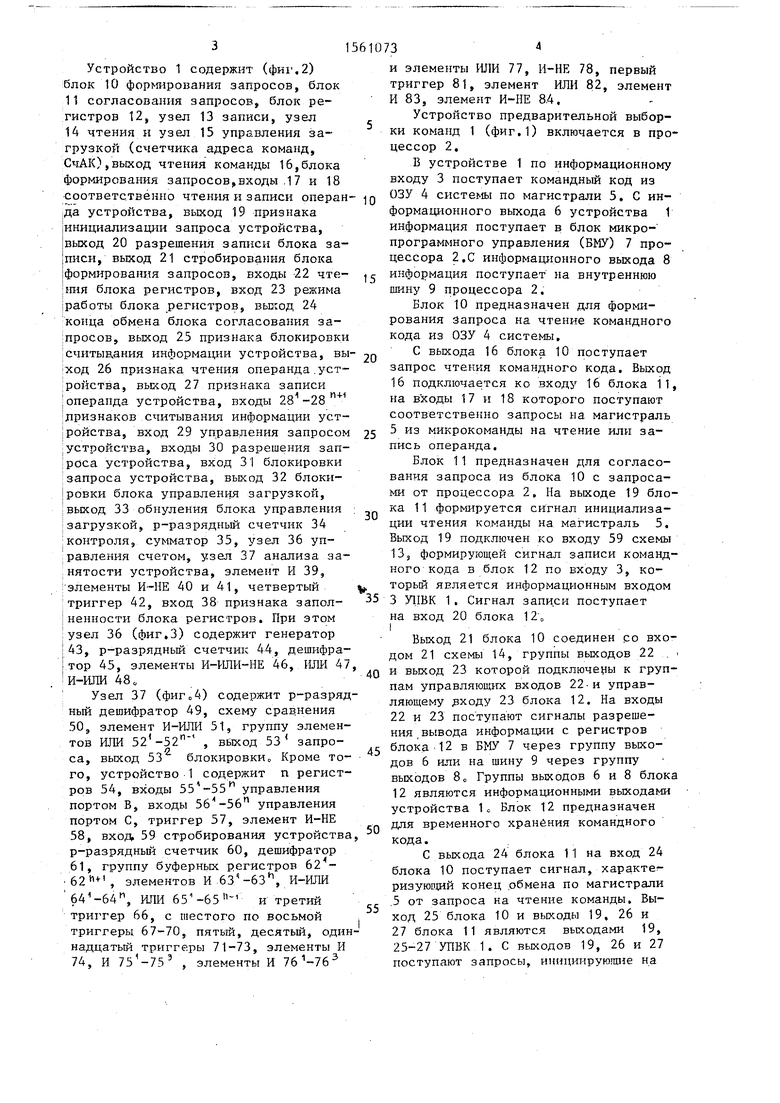

Электронная вычислительная машина, поясняющая область применения устройства (фиг.1), содержит устройство предварительной выборки команд 1, процессор 2, информационный вход 3, оперативное запоминающее устройство 4, системную магистраль 5, второй информационный выход блока буферной памяти команд 6, блок микропрограммного управления 7, первый информационный выход блока буферной памяти команд 8, внутреннюю магистраль процессора 9.

2Л

Э

1

го

3

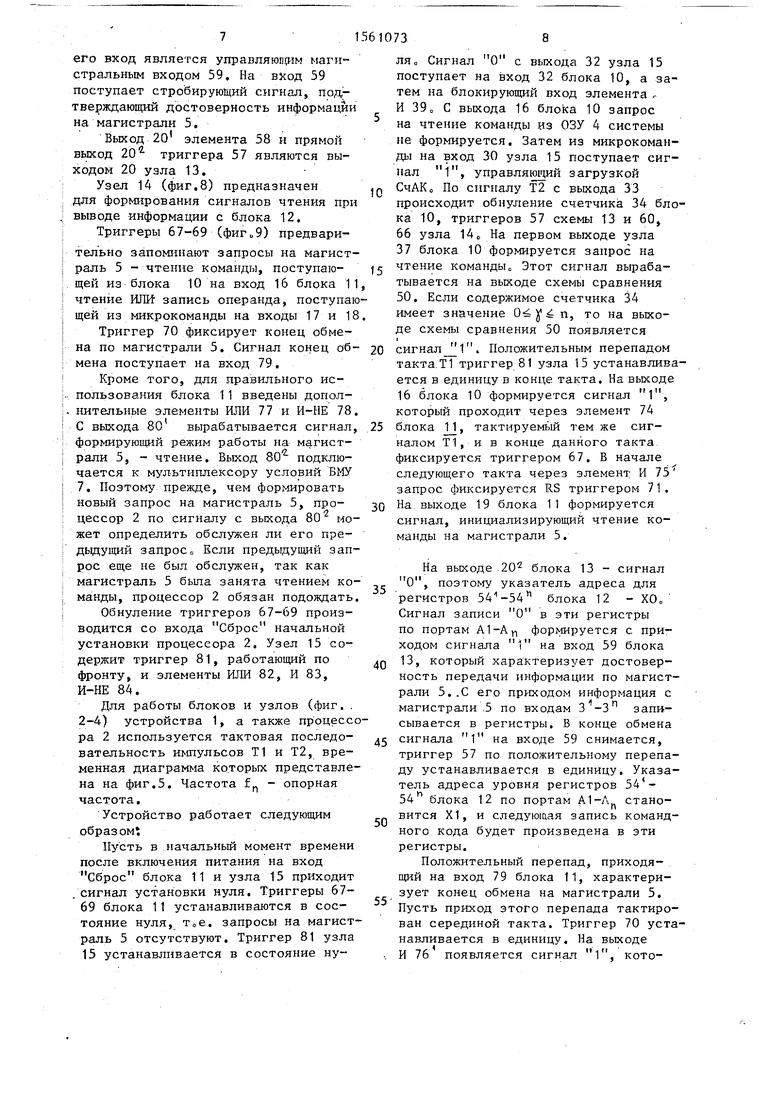

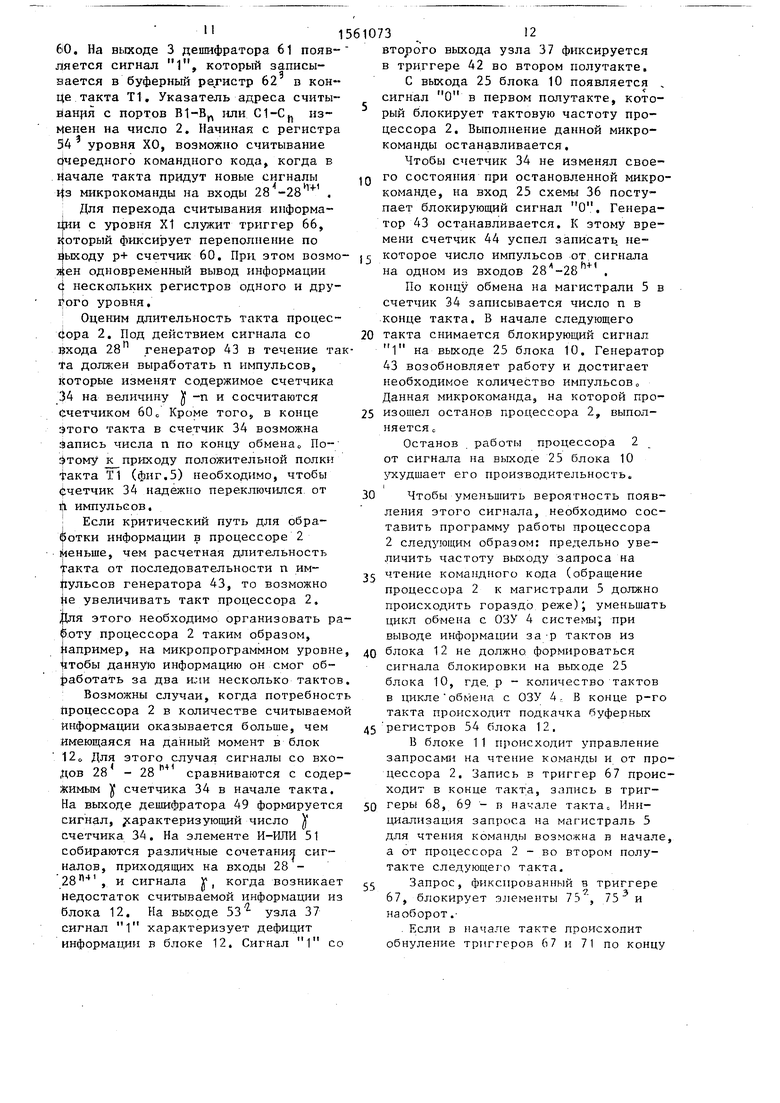

Устройство 1 содержит (фиг.2) блок 10 формирования запросов, блок 11 согласования запросов, блок регистров 12, узел 13 записи, узел 14 чтения и узел 15 управления загрузкой (счетчика адреса команд, СпАК),выход чтения команды 16,блока формирования запросов„входы 17 и 18 соответственно чтения и записи операда устройства, выход 19 признака инициализации запроса устройства, выход 20 разрешения записи блока за писи, выход 21 стробирования блока формирования запросов, входы 22 чтения блока регистров, вход 23 режима работы блока регистров, выход 24 конца обмена блока согласования запросов, выход 25 признака блокировк считывания информации устройства, вход 26 признака чтения операнда устройства, выход 27 признака записи операнда устройства, входы 281-28 n+ лризнаков считывания информации устройства, вход 29 управления запросо устройства, входы 30 разрешения запроса устройства, вход 3I блокировки запроса устройства, выход 32 блокировки блока управления загрузкой, выход 33 обнуления блока управления загрузкой, р-разрядный счетчик 34 контроля, сумматор 35, узел 36 управления счетом, узел 37 анализа занятости устройства, элемент И 39, элементы И-НЕ 40 и 41, четвертый триггер 42, вход 38 признака заполненности блока регистров. При этом узел 36 (фиг.З) содержит генератор 43, р-разрядный счетчик 44, дешифра ,тор 45, элементы И-ИЛИ-НЕ 46, ИЛИ 4 и-ИЛИ 48 о

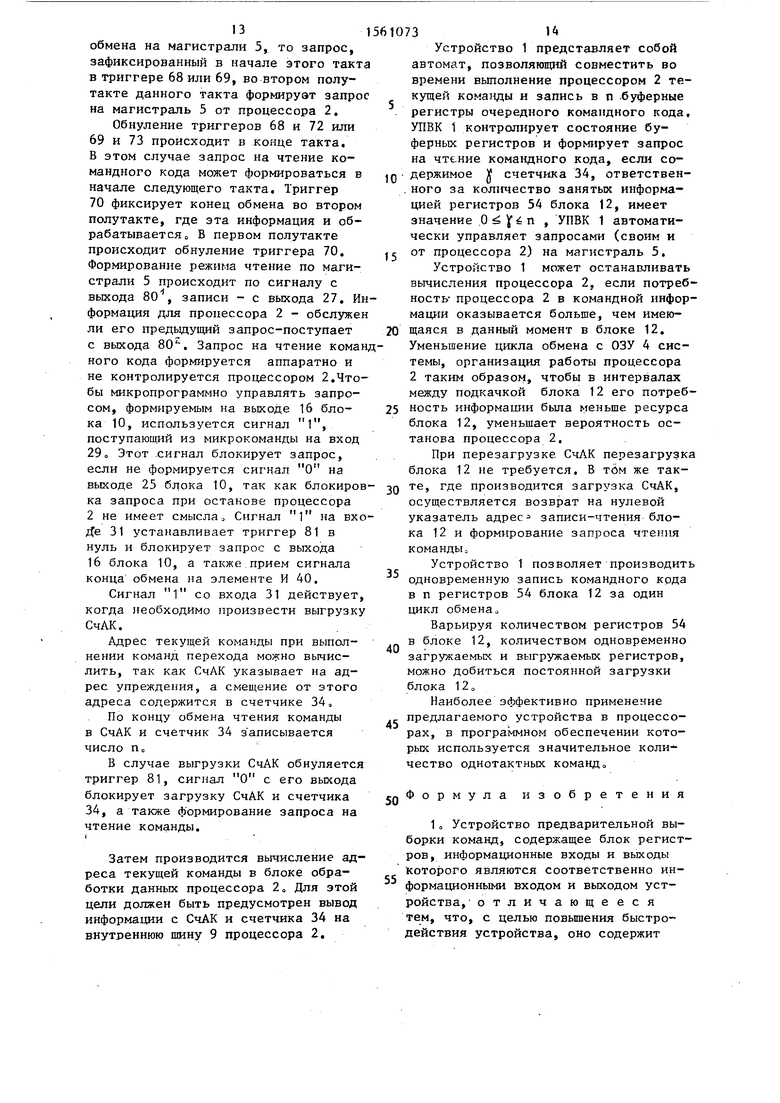

Узел 37 (фиг04) содержит р-разряный дешифратор 49, схему сравнения 50, элемент И-ИЛИ 51, группу элемен ИЛИ , выход 53( запро- выход 53 блокировки Кроме то устройство 1 содержит п регистров 54, входы управления портом В, входы управления портом С, триггер 57, элемент И-НЕ 58, вход. 59 стробирования устройств р-разрядный счетчик 60, дешифратор 61, группу буферных регистров 62 - 62ии, элементов И , И-ИЛИ

б41-64п, ИЛИ 651-65п 1 и третий

9

тов са, го,

триггер 66, с шестого по восьмой

триггеры 67-70, пятый, десятый, одиннадцатый триггеры 71-73, элементы И

74, И 75-75

элементы

И 761-76э

0

5

0

5

0

5

0

5

0

5

и элементы ИЛИ 77, И-НЕ 78, первый триггер 81, элемент ИЛИ 82, элемент И 83, элемент И-НЕ 84.

Устройство предварительной выборки команд 1 (фиг.1) включается в процессор 2.

В устройстве 1 по информационному входу 3 поступает командный код из ОЗУ 4 системы по магистрали 5. С информационного выхода 6 устройства 1 информация поступает в блок микропрограммного управления (БМУ) 7 процессора 2.С информационного выхода 8 информация поступает на внутреннюю шину 9 процессора 2.

Блок 10 предназначен для формирования Запроса на чтение командного кода из ОЗУ 4 системы.

С выхода 16 блока 10 поступает запрос чтения командного кода. Вькод 16 подключается ко входу 16 блока 11, на входы 17 и 18 которого поступают соответственно запросы на магистраль 5 из микрокоманды на чтение или запись операнда.

Блок 11 предназначен для согласования запроса из блока 10 с запросами от процессора 2. На выходе 19 блока 11 формируется сигнал инициализации чтения команды на магистраль 5. Выход 19 подключен ко входу 59 схемы 133 формирующей сигнал записи командного кода в блок 12 по входу 3, который является информационным входом 3 У11ВК 1 . Сигнал записи поступает

на вход 20 блока 120 I

Выход 21 блока 10 соединен со входом 21 схемы 14, группы выходов 22 и выход 23 которой подключены к группам управляющих входов 22 и управляющему входу 23 блока 12. На входы 22 и 23 поступают сигналы разрешения вывода информации с регистров блока 12 в БМУ 7 через группу выходов 6 или на шину 9 через группу выходов 8о Группы выходов 6 и 8 блока 12 являются информационными выходами устройства Ь Блок 12 предназначен для временного хранения командного кода.

С выхода 24 блока 1I на вход 24 блока 10 поступает сигнал, характеризующий конец обмена по магистрали 5 от запроса на чтение команды. Выход 25 блока 10 и выходы 19, 26 и 27 блока 11 являются выходами 19, 25-27 УПВК 1. С выходов 19, 26 и 27 поступают запросы, инициирующие на

магистраль 5 соответственно чтение команды и операнда, запись операнда. С выхода 25 поступает блокирующий сигнал для тактовой частоты процессора 2.

На группу управляющих входов 28 28блока 10 и схемы 14, на вход

29блока 10 и входы 30 и 31 узла 15 поступают управляющие сигналы с поля микрокоманды, на управляющий вход

28 - сигнал с БМУ 7. Узел 15 предназначен для формирования сигналов управления работой блока 10 и узлов 14 и 13 в случае перезагрузки СчАК процессора 2„ С выхода 32 узла 15 на вход 32 блока 10 поступает сигнал блокировки, С выхода 33 узла 15 поступает сигнал обнуления на входы 33 блока 10 и узлов 13 и 14.

Узел 36 имеет группу входов 28 -28 и + , являющихся входами блока 10. Выход узла 36 соединен со счетным входом счетчика 34, работающего на вычитание, и является выходом 21 блока 10. Входы Д1-ДР счетчика 34 подключены к выходам сумматора 35, входы А1-АР которого соединены с выходами Q1-QP счетчика 34, а входы В1-ВР соединены со схемой 38. Схема 38 устанавливает постоянное число, например число п, разрядность которого в двоичном коде меньше р. Установленное число п складывается в сумматоре 35 с содержимым Y счетчика 34.

Разрядность р счетчика 34 определяется максимальным числом 2 п. Это утверждение будет пояснено далее.

Вход 24 блока 10 через элемент И-НЕ 40 соединен со входом разрешения записи счетчика 34.

Таким образом, изменение содержимого счетчика 34 происходит под действием сигнала на входе 24. Обнуление счетчика 34 происходит по входу R сигналом, поступающим с узла 15 на вход 33.

Узел 37 производит анализ информации на выходах Q1-QP счетчика 34. От результата анализа на первом выходе узла 37 вырабатывается запрос на чтение команды из ОЗУ 4 системы, который через элемент И 39 поступает на выход 16 блока 100 На втором выходе узла 37 появляется сигнал, фиксируемый триггером 42„

Содержимое счетчика 34 поступает на р входов дешифратора 49 и на р

входов схемы сравнения 5(J, на другой вход которого узла 38 поступает установленное число п в двоичном коде разрядностью р„ Инверсный выход схемы сравнения 50, являющийся первым выходом 53 узла 37, соединяется со входом элемента И 39 блока 10. На выходе схемы сравнения 50 появляется

3 сигнал 1, если значение у со счетчика 34 в двоичном коде не превышает заданного узлом 38 порога п. Блок 12 (фиг.6) предназначен для временного хранения командного кода. Блок 12

5 содержит 2 п К-разрядных буферных регистров 54, Запись с магистрали 5 производится одновременно в п регистров 54 по портам AI-Ап. Информация в регистры 54-54 поступает с ннфор0 мационного входа 3. Так как nq каждому порту А поступает К бит информации, то разрядность магистрали 5 должна быть не меньше Km.

Управление записью производится

5 по входу 20 . Управление уровнями регистров 54 -5411 по адресу ХО или Х1 производится сигналом со входа 20г. Входы 20 и 202 являются управляющим входом 20 блока 12, подо ключенным к выходу схемы 13.

Вывод информации производится с портов В1-ВП на внутреннюю шину 9 процессора 2. Вывод информации возможен как с одного порта В, так одновременно со всех В1-ВП. Поэтому разрядность шины 9 должна быть не меньше К-п0 Вывод информации с портов С1-СП производится в БМУ 7 и возможен только с одного порта С. ВыQ ходы 6 -6 объединены монтажным ИЛИ и являются информационным выходом 6 УПВК 1. При считывании информации выбор номера порта производится для портов В1-В„ по входам 55 -55 , для

с портов С1-СП - по входам 56 -56 . Входы 551-55п и 5б -56п являются группами управляющих входов 22 блока 12, подключенными к выходам узла 14. Указатель считывания с регистров

0 О или 1 уровня по портам В1-ВП, С1-С соединен с управляющим входом 23 блока 12, подключенным к выходу 23 узла 14.

Узел 13 (фиг.7) содержит триггер 57, работающий по фронту, элемент И-НЕ 58. Обнуление триггера 57 осуществляется по R-входу с выхода 33 узла 15, Первый вход И-НЕ 58 соединен с выходом 19 блока 11, а второй

его вход является управляющим маги™ стралышм входом 59. На вход 59 поступает стробирующий сигнал, подверждающий достоверность информации на магистрали 5.

Выход 201 элемента 58 и прямой выход 20а триггера 57 являются выодом 20 узла 13.

Узел 14 (фиг.8) предназначен ля формирования сигналов чтения при выводе информации с блока 12.

Триггеры 67-69 (фиг„9) предварительно запоминают запросы на магистраль 5 - чтение команды, поступающей из блока 10 на вход 16 блока 11, чтение ИЛИ запись операнда, поступающей из микрокоманды на входы 17 и 18.

Триггер 70 фиксирует конец обмена по магистрали 5. Сигнал конец обмена поступает на вход 79.

Кроме того, для правильного использования блока 11 введены допол- нительные элементы ИЛИ 77 и И-НЕ 78. С выхода 80 вырабатывается сигнал, формирующий режим работы на магистрали 5, - чтение. Выход подключается к мультиплексору условий ЕМУ 7. Поэтому прежде, чем формировать новый запрос на магистраль 5, процессор 2 по сигналу с выхода 80 может определить обслужен ли его предыдущий запрос о Если предыдущий запрос еще не был обслужен, так как магистраль 5 была занята чтением команды, процессор 2 обязан подождать. Обнуление триггеров 67-69 производится со входа Сброс начальной установки процессора 2. Узел 15 содержит триггер 81, работающий по фронту, и элементы ИЛИ 82, И 83, И-НЕ 84.

Для работы блоков и узлов (фиг. . 2-4) устройства 1, а также процессора 2 используется тактовая последовательность импульсов Т1 и Т2, временная диаграмма которых представлена на фиг.5. Частота fn - опорная частота.

Устройство работает следующим образом

Пусть в начальный момент времени после включения питания на вход Сброс блока 11 и узла 15 приходит . сигнал установки нуля. Триггеры 67- 69 блока 11 устанавливаются в состояние нуля, т0е. запросы на магистраль 5 отсутствуют. Триггер 81 узла 15 устанавливается в состояние ну

0

5

0

5

0

5

0

5

ля„ Сигнал О с выхода 32 узла 15 поступает на вход 32 блока 10, а затем на блокирующий вход элемента ,- И 39„ С выхода 16 блока 10 запрос на чтение команды из ОЗУ 4 системы не формируется. Затем из микрокоманды на вход 30 узла 15 поступает сигнал 1, управляющий загрузкой СчАК0 По сигналу Т2 с выхода 33 происходит обнуление счетчика 34 блока 10, триггеров 57 схемы 13 и 60, 66 узла 14 о На первом выходе узла 37 блока 10 формируется запрос на чтение команды. Этот сигнал вырабатывается на выходе схемы сравнения 50. Если содержимое счетчика 34 имеет значение Oi у п, то на выходе схемы сравнения 50 появляется сигнал 1. Положительным перепадом такта Т1 триггер 81 узла 15 устанавливается в единицу в конце такта. На выходе 16 блока 10 формируется сигнал 1, который проходит через элемент 74 блока 11, тактируемый тем же сигналом Т1, ив конце данного такта фиксируется триггером 67. В начале следующего такта через элемент И 75 запрос фиксируется RS триггером 71. На выходе 19 блока 11 формируется сигнал, инициализирующий чтение команды на магистрали 5.

На выходе 202 блока 13 - сигнал О, поэтому указатель адреса для регистров 54/|-54п блока 12 - Х0„ Сигнал записи О в эти регистры по портам А1-АП формируется с приходом сигнала 1 на вход 59 блока 13, который характеризует достоверность передачи информации по магистрали 5..С его приходом информация с магистрали 5 по входам 3 -3п записывается в регистры. В конце обмена сигнала 1 на входе 59 снимается, триггер 57 по положительному перепаду устанавливается в единицу. Указатель адреса уровня регистров 54 блока 12 по портам А1-ЛП становится XI, и следующая запись командного кода будет произведена в эти регистры.

Положительный перепад, приходящий на вход 79 блока 11, характеризует конец обмена на магистрали 5. Пусть приход этого перепада тактирован серединой такта. Триггер 70 устанавливается в единицу. На выходе И 76 появляется сигнал 1, кото9рый в конце данного такта сигналом О поступает на W-вход счетчика 34.

Под действием этого сигнала содер жимое сумматора 35 записывается в счетчик 34, в данном случае У 0, тогда в счетчик 34 записывается число п„ Узел 37 производит анализ содержимого счетчика 34, На выходе схемы сравнения 50 вновь появляется сигнал 1, который поступает на вход 16 блока 11 „ Запись числа п в счетчик 34 производится в течение времени Т1, поэтому первым полутактом следующего такта триггер 70 устанавливается в нуль. Положительным перепадом по С-входу триггер 67, а затем и триггер 71 по R-вхо- ду обнуляются. Блокировка на входе И 74 снимается. В конце данного такта по сигналу триггер 67 снова устанавливается в единицу, а в начале следующего такта инициализируется запрос на магистраль 5 для чтения командного кода0 Максимальное число, записанное в счетчик 34, равно 2п, разрядность которого в двоичной системе р.

Если при загрузке СчАК под действием управляющего сигнала из микро команды (сигнал 1 на входе 30) его содержимое было А, то по концу обмена с выхода 24 блока 11 появляется сигнал, который изменяет содержимое СчАК на А+п, Таким образом при чтении командного кода в п регистров 54 ВК 12 наращивание СчАК происходит автоматически на число пс Под действием сигналов, поступающим на входы устройства 1, производится считывание с регистров блока 12. Под действием сигналов со входов 28 -2811 из микрокоманды происходит вывод информации на шину 9, со входа 28ГН1 (управляющий сигнал из БМУ 7) - в БМУ 7.

При этом сигналы со входов 28 - 28h характеризуют количество регистров 54 БК 12 одновременно считываемых по портам В1-БП. Под действием сигнала со входа 28 считывается один регистр 54, под действием 28 - одновременно два регистра 54 и т «д., под действием 28 - п регистров 54. Под действием сигнала со входа 28 считывается всегда один регистр 54 с портов С1-СП

С помощью сигнала на входе 28 процессор 2 читает код операции оче10

61073Ю

редкой команды в БМУ 7, где формируется начальный адрес микрокоманды обработки данной команды. В большинстве случаев команда выполняется

5 за один такт процессора 2, т.е. за одну микрокоманду. В выбранной микрокоманде может быть указано количество регистров 54 по сигналам на входах 28 -28п, которые необходимо считать на шину 9 (чтение остатка команды, например непосредственного операнда), чтобы выполнить команду заданного формата. После загрузки

jtj СчКА триггер 60 обнулен. На выходе 1 дешифратора 61 - сигнал 1. Запись сигналов в регистры 62 -62 происхо- . дит по концу такта Т1. В данном случае указатель адреса считывания с

20 портов В1-В|, или С1-СП поступает с регистра 621„

Сигнал с выхода триггера 66 указывает с какого уровня регистров производить считывание, В данном

25 случае считывание по портам В1-Вп или С1-СП производится с уровня ХО Пусть, например, в начале такта пришел сигнал 1 на вход 28. В этом случае на выходе элементов ИЛИ

2Q 65, 65г - сигналы 1, отсюда на выходе И-ИЛИ 64,64 - тоже сигналы 1, На управляющие входы 55 , 55 блока 12 поступают сигналы 1, которые разрешают вывод информации по портам В1, В2 с регистров 54% 54 уровня ХО.

-Одновременно сигнал 1 со входа 28 поступает в блок 10 на вход узла 36 и через элемент И-ИЛИ 48 включает

-0 генератор 43. Когда на выходе 2 дешифратора 45 появляется сигнал 1, он пропускается элементом И-ИЛИ-НЕ 46, Сигнал О на выходе элемента 46 блокирует работу генератора 43, т.е. с

,с выхода 21 узла 36 от сигнала 28 формируется два импульса.

Генератор 43 вырабатывает последовательность импульсов типа меандр, длительность Т2/2 которых определя5Q ется допустимой длительностью, необходимой для срабатывания счетчиков 34 блока 10 и 60 схемы 14, т.е. выбором их элементной базы.

Два импульса, сформированные узлом 36, поступают на вычитающий счетный вход счетчика 34. Содержание счетчика 34 становится .

Те же два импульса поступают на вход 21 узла 14 и далее на счетчик

60. На выходе 3 дешифратора 61 появляется сигнал 1, который записы- эается в буферный регистр 62 в конце такта Т1. Указатель адреса считывания с портов В1-В или C1-Ch из- Менен на число 2. Начиная с регистра 54 уровня ХО, возможно считывание Очередного командного кода, когда в Начале такта придут новые сигналы Из микрокоманды на входы 28 -28 1f . Для перехода считывания информации с уровня Х1 служит триггер 66, который фиксирует переполнение по

ПЫХОДУ Р+ СЧеТЧИК 60. При. ЭТОМ ВОЗМО-

4ен одновременный вывод информации d нескольких регистров одного и другого уровня.

Оценим длительность такта процессора 2. Под действием сигнала со Входа 28п генератор 43 в течение такта должен выработать п импульсов, которые изменят содержимое счетчика 34 на величину J -п и сосчитаются Счетчиком 60 о Кроме того,, в конце Этого такта в счетчик 34 возможна Запись числа п по концу обмена„ Поэтому к приходу положительной полки taKTa T1 (фиг.5) необходимо, чтобы Счетчик 34 надежно переключился от fi импульсов.

Если критический путь для обработки информации в процессоре 2 меньше, чем расчетная длительность Такта от последовательности п импульсов генератора 43, то возможно jie увеличивать такт процессора 2. Для этого необходимо организовать ра роту процессора 2 таким образом, например, на микропрограммном уровне тобы данную информацию он смог обработать за два или несколько тактов

Возможны случаи, когда потребност процессора 2 в количестве считываемо информации оказывается больше, чем имеющаяся на данный момент в блок 12 о Для этого случая сигналы со входов 28 - 28 + сравниваются с содержимым счетчика 34 в начале такта. На выходе дешифратора 49 формируется сигнал, характеризующий число счетчика 34. На элементе И-ИЛИ 51 собираются различные сочетания сигналов, приходящих на входы 28 - 28 П4 , и сигнала У, когда возникает недостаток считываемой информации из блока 12. На выходе 53 узла 37 сигнал 1 характеризует дефицит информации в блоке 12. Сигнал 1 со

0

5

с;

второго выхода узла 37 фиксируется в триггере 42 во втором полутакте.

С выхода 25 блока 10 появляется „ сигнал О в первом полутакте, который блокирует тактовую частоту процессора 2. Выполнение данной микрокоманды останавливается.

Чтобы счетчик 34 не изменял своего состояния при остановленной микрокоманде, на вход 25 схемы 36 поступает блокирующий сигнал О. Генератор 43 останавливается. К этому времени счетчик 44 успел записать некоторое число импульсов от сигнала на одном из входов + ,

По концу обмена на магистрали 5 в счетчик 34 записывается число п в конце такта. В начале следующего такта снимается блокирующий сигнал 1 на выходе 25 блока 10. Генератор 43 возобновляет работу и достигает необходимое количество импульсов Данная микрокоманда, на которой произошел останов процессора 2, выполняется с

Останов работы процессора 2 от сигнала на выходе 25 блока 10 ухудшает его производительность.

0

0

Чтобы уменьшить вероятность появления этого сигнала, необходимо составить программу работы процессора 2 следующим образом: предельно увеличить частоту выходу запроса на 5 чтение командного кода (обращение процессора 2 к магистрали 5 должно происходить гораздо реже); уменьшать цикл обмена с ОЗУ 4 системы; при выводе информации за р тактов из блока 12 не должно формироваться сигнала блокировки на выходе 25 блока 10, где. р - количество тактов в цикле обмена с ОЗУ 4 В конце р-го такта происходит подкачка буферных регистров 54 блока 12.

В блоке 11 происходит управление запросами на чтение команды и от процессора 2. Запись в триггер 67 происходит в конце такта, запись в триггеры 68, 69 - в начале такта5 Инициализация запроса на магистраль 5 для чтения команды возможна в начале, а от процессора 2 - во втором полутакте следующего такта.

Запрос, фиксированный в триггере 67, блокирует элементы 75 , 75 и наоборот.

Если в начале такте происходит обнуление триггеров 67 и 71 по концу

5

0

5

обмена на магистрали 5, то запрос, зафиксированный в начале этого такта в триггере 68 или 69, во втором полутакте данного такта формирует запрос на магистраль 5 от процессора 2. Обнуление триггеров 68 и 72 или

69и 73 происходит в конце такта. В этом случае запрос на чтение командного кода может формироваться в начале следующего такта. Триггер

70фиксирует конец обмена во втором полутакте, где эта информация и обрабатывается В первом полутакте происходит обнуление триггера 70. Формирование режима чтение по магистрали 5 происходит по сигналу с выхода 80, записи - с выхода 27. Информация для процессора 2 - обслужен ли его предыдущий запрос-поступает

с выхода SO -. Запрос на чтение команного кода формируется аппаратно и не контролируется процессором 2.Чтобы микропрограммно управлять запросом, формируемым на выходе 16 блока 10, используется сигнал 1, поступающий из микрокоманды на вход 29о Этот сигнал блокирует запрос, если не формируется сигнал О на выходе 25 блока 10, так как блокировка запроса при останове процессора 2 не имеет смысла, Сигнал 1 на вхо 31 устанавливает триггер 81 в нуль и блокирует запрос с выхода 16 блока 10, а также прием сигнала конца обмена на элементе И 40.

Сигнал 1 со входа 31 действует, когда необходимо произвести выгрузку СчАК.

Адрес текущей команды при выполнении команд перехода можно вычислить, так как СчАК указывает на адрес упреждения, а смещение от этого адреса содержится в счетчике 34,

По концу обмена чтения команды в СчАК и счетчик 34 записывается

ЧИСЛО По

В случае выгрузки СчАК обнуляется триггер 81, сигнал О с его выхода блокирует загрузку СчАК и счетчика 34, а также формирование запроса на

чтение команды.

i

Затем производится вычисление адреса текущей команды в блоке обработки данных процессора 2„ Для этой цели должен быть предусмотрен вывод информации с СчАК и счетчика 34 на внутреннюю шину 9 процессора 2.

Устройство 1 представляет собой автомат, позволяющий совместить во времени выполнение процессором 2 текущей команды и запись в п .буферные регистры очередного командного кода, УПВК 1 контролирует состояние буферных регистров и формирует запрос на чтение командного кода, если со держимое У счетчика 34, ответственного за количество занятых информацией регистров 54 блока 12, имеет значение 0 6 п , УПВК 1 автоматически управляет запросами (своим и

r от процессора 2) на магистраль 5.

Устройство 1 может останавливать вычисления процессора 2, если потребность- процессора 2 в командной информации оказывается больше, чем имею-

0 щаяся в данный момент в блоке 12. Уменьшение цикла обмена с ОЗУ 4 системы, организация работы процессора 2 таким образом, чтобы в интервалах между подкачкой блока 12 его потреб5 ность информации была меньше ресурса блока 12, уменьшает вероятность останова процессора 2.

При перезагрузке СчАК перезагрузка блока 12 не требуется. В том же так0 те, где производится загрузка СчАК, осуществляется возврат на нулевой указатель адресз записи-чтения блока 12 и формирование запроса чтения команды

Устройство 1 позволяет производить одновременную запись командного кода в п регистров 54 блока 12 за один цикл обмена о

Варьируя количеством регистров 54 в блоке 12, количеством одновременно загружаемых и выгружаемых регистров, можно добиться постоянной загрузки блока 120

Наиболее эффективно применение предлагаемого устройства в процессорах, в программном обеспечении которых используется значительное количество однотактных команд

5

0

5

Формула изобретения

1 о Устройство предварительной выборки команд, содержащее блок регистров, информационные входы и выходы Которого являются соответственно информационными входом и выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит

15

узел анализа занятости устройства, узел управления счетом, счетчик контроля, сумматор, счетчик, дешифрач тор, с первого по одиннадцатый триггеры, с первого по девятый элементы И, с первого по пятый элементы И - НЕ, первый и второй элементы ИЛИ, группу п+1 регистров (где п - количество единиц информации, записываемой или считываемой одновременно в блок регистров), группу п элементов И, группу п-1 элементов ИЛИ и группу п элементов И - ИЛИ, причем группа п+1 входов признаков считывания информации устройства подключена к группе п+1 информационных входов узла управления счетом и к первой группе п+1 информационных входов узла анализа занятости устройства, группа информационных выходов счетчика контроля соединена с второй группой информационных входов узла анализа занятости устройства и с группой входов первого слагаемого сумматора, группа входов второго слагаемого, которого подключена к группе входов кода признака заполненности информацией блока регистров устройства, информационный выход сумматора соединен с информационным входом счетчика контроля, выход узла управления счетом подключен к вычитающему входу счетчика контроля и суммирующему входу счетчика, выход первого элемента И-НЕ соединен с входом разрешения записи счетчика контроля, прямой выход первого триггера соединен с первым входом первого элемента И и первым входом первого элемента И-НЕ, второй вход которого подключен к первому входу синхронизации устройства, инверсный выход первого триггера соединен с прямым входом второго элемента И-НЕ, выход которого соединен с информационным входом первого триггера, вход синхронизации которого подключен к первому входу синхронизации устройства, выход первого элемента ИЛИ соединен с входом, установки в О первого триггера, первый вход первого элемента ИЛИ подключен к входу блокировки запроса устройства, вход разрешения запроса устройства подключен к инверсному входу второго элемента И-НЕ и к первому входу второго элемента И, второй вход которого подключен к второму входу синхронизации

561073

устройства,

16

10

15

20

25

выход второго элемента И соединен с входами сброса счетчика контроля и счетчика, с входами установки в О второго и третьего триггеров, выход блокировки узла анализа занятости устройства соединен с информационным входом четвертого триггера, вход синхронизации которого подключен к третьему входу синхронизации устройства, инверсный выход четвертого триггера является выходом признака блокировки считывания ин- формаиии устройства и подключен к входу блокировки счета узла управления счетом и к первому входу третьего элемента И - НЕ, второй вход которого подключен к входу управления запросом устройства, выход третьего элемента И-НЕ соединен с вторым входом первого элемента И, выход запроса узла анализа занятости устройства соединен с третьим входом первого элемента И, выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к первому входу синхронизации устройства, прямой выход пятого триггера является выходом признака инициализации запроса устройства и подключен к первому входу четвертого элемента И-НЕ и первому входу четвертого элемента И5 выход которого соединен с третьим входом первого элемента И-НС и входом синхронизации шестого триггера, выход третьего элемента И соединен с входом установки в 1 шестого триггера, информационный вход которого и информационные входы седьмого и восьмого триггеров подключены к шине нулевого потенциала устройства, входы установки в 1 седьмого и восьмого триггеров являются соответственно входами признака зад5 просов на чтение и запись операнда устройства, инверсный выход девятого триггера соединен с вторым входом четвертого элемента И, прямой выход девятого триггера соединен с первыми

50 входами пятого и шестого элементов И, вход синхронизации девятого триггера соединен с входом признака сброса запросов устройства, информационный вход девятого триггера соединен с шиной единичного потенциала устройства, вход установки в О девятого триггера подкчючен к третьему входу синхронизации устройства, прямой выход шестого триггера соединен с

30

35

40

55

первым входом седьмого элемента И, второй вход которого подключен к третьему входу синхронизации устройства, инверсный выход шестого триггера соединен с третьим входом третьего элемента И, входом установки в О пятого триггера и первыми входами восьмого и девятого элементов И, прямые выходы седьмого и восьмого триггеров соединены соответственно с вторыми входами восьмого и девятого элементов И, третьи входы восьмого и девятого элементов И подключены к второму входу синхронизации устройства, инверсные выходы седьмого и восьмого триггеров соединены соответственно с третьим и четвертым входами седьмого элемента И, инверсные выходы седьмого и восьмого триггеров соединены и соответственно с входами установки в О десятого, одиннадцатого триггеров, выходы восьмого и девятого элементов И соединены соответственно с входами установки в 1 десятого и одиннадцатого триггеров, прямые выходы которых являются соответственно выходами признака запросов на чтение и запись операнда устройства и подключены соответственно к вторым входам пятого и шестого элементов И, выходы которых соединены ооответственно с входами синхронизации седьмого и восьмого триггеров, второй вход четвертого элемента И - НЕ подключен к входу разрешения загрузки команд устройства, выход четвертого элемента И - НЕ соединен с входом разрешения записи блока регистров и входом синхронизации второго триггера, инверсный выход которого соединен с информационным входом второго триггера, прямой выход которого подключен к входу записи блока регистров, вы-, ход переполнения счетчика соединен с входом синхронизации третьего триггера, инверсный выход которого соединен с информационным входом третьего триггера, а прямой выход - с информационным входом (п-Н)-го регистра группы регистров, выход которого соединен с входом разрешения чтения блока регистров, информационный выход счетчика соединен с информационным входом дешифратора, выходы которого соединены с информационными входами с первого по п-и регистров группы регистров, входы синхронизации всех регистров группы

561073is

подключены к первому входу синхронизации устройства,

10

25

30

выходы с первого по n-й регистров группы регистров, соединены соответственно с первыми входами п элементов п группы, вторые входы которых подключены к (n+O-му входу группы п+1 входов признрков считывания информации устройства, выход 1-го регистра группы регистров i 1,...,п) соединен с первыми входами с 1-го по n-й элементов И-ИЛИ группы, выходы элементов И группы и выходы элементов

I с И-ИЛИ группы подключены соответственно к первой и второй группам входов чтения блока регистров, i-й вход - 1-го элемента ИЛИ группы соединен с i-м входом группы входов признаков

20 считывания информации устройства, выход 1-го элемента ИЛИ группы соединен с (1+2)-м входом элементов И-ИЛИ группы, n-й вход признака считывания устройства соединен с (п+2)-м входом с первого по n-й элементов И-ИЛИ группы, вход сброса устройства соединен с вторым входом первого элемента ИЛИ и с входом установки в О с шестого по восьмой триггеров, прямые выходы пятого и десятого триггеров соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является выходом признака режима чтения устройства, инверсные выходы седьмого и восьмого триггеров соединены соответственно с первым и вторым входами пятого элемента И-НЕ, выход которого является выходом признака обслуживания запроса устройства, прямой выход третьего триггера соединен с информационным входом (п-М)-го регистра группы регистров, выход которого соединен с входом режима работы блока

. регистров, третья группа информационных входов узла анализа занятости устройства подключена к группе входов кода признака заполненности информации блока регистров устройства.

2 о Устройство по п.1, отличающееся тем, что узел анализа занятости устройства содержит дешифратор, схему сравнения, элемент И-ИЛИ группу элементов ИЛИ, причем выход 1-го элемента соединен с i-м входом элемента И - ИЛИ, 1-й вход первой группы информационных входов узла соединен с i-м входом 1-го элемента ИЛИ, вторая группа ин35

40

50

55

формационных входов узла подключена к первой группе входов схемы сравнения, выход которой соединен с выходом запроса узла, вторая группа информационных входов узла подключения к группе информационных входов дешифратора, i-й выход которого соединен с 2 1+1)-м входом элемента И-ИЛИ, выход которого соединен с выходом признака блокировки узла, вторая группа входов схемы сравнения подключена к третьей группе информационных входов узла, n-й вход первой группы информационных входов узла соединен с (2 п-М)-м входом элемента И-ИЛИ о

3„ Устройство по п.1 о т л и- чающееся тем, что узел управления счетом содержит генератор тактовых импульсов, счетчик, дешифратор, элемент ИЛИ, элемент И-ИЛИ, элемент И-ИЛИ-НЕ, причем с первого по (п+1)й информационные входы группы узла подключены к входам эле

5

0

5

мента ИЛИ, выход которого и информационные входы узла с второго по n-й соединены соответственно с первого по n-й входами элемента И-ИЛИ, (п+1)-й вход которого подключен к входу блокировки счета узла, выход элемента И-ИЛИ соединен с входом запуска- генератора тактовых импульсов, выход которого является выходом узла и соединен с суммирующим входом счетчика, информационный выход которого соединен с информационным входом дешифратора, выходы которого соединены соответственно с первого по n-й входами элемента И - ИЛИ - НЕ . Выход элемента ИЛИ соединен с п+1 входом элемента, информационные входы группы узла с второго по n-й соединены соответственно с (гН2)-го по (2п+4)-м входами элемента И - ИЛИ - НЕ, выход которого соединен с инверсным входом установки в О счетчика и входом останова генератора тактовых импульсов.

фиг А

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ И ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2099780C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Предлагаемое устройство целесообразно применять в процессорах, архитектура которых предполагает использование буферной памяти, конвейерного выполнения команд. Наиболее эффективно применение предлагаемого устройства, если в программном обеспечении процессора используется значительное количество однотактных команд. Цель - повышение быстродействия устройства за счет обеспечения постоянной загрузки буфера команд устройства, непрерывная подкачка которого со стороны магистрали и выгрузка информации производится по требованию процессора. Устройство предварительной выборки команд содержит блок формирования запросов, блок согласования запросов, блок регистров, узел чтения, узел записи, узел управления загрузкой. 2 з.п.ф-лы, 4 ил.

Заказ 977

Тираж 576

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Микропроцессорные средства и системы | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Пом А | |||

| Быстродействующие системы памяти | |||

| М„: Мир, 1987 | |||

| Корнейчук В.И0 Запоминающие устройства ЦВМ | |||

| Киев, 1976, с | |||

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

Авторы

Даты

1990-04-30—Публикация

1987-10-01—Подача