Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для связи процессоров с внешними или запоминающими устройствами.

Целью изобретения является сокра- гцение количества выходных каналов связи.

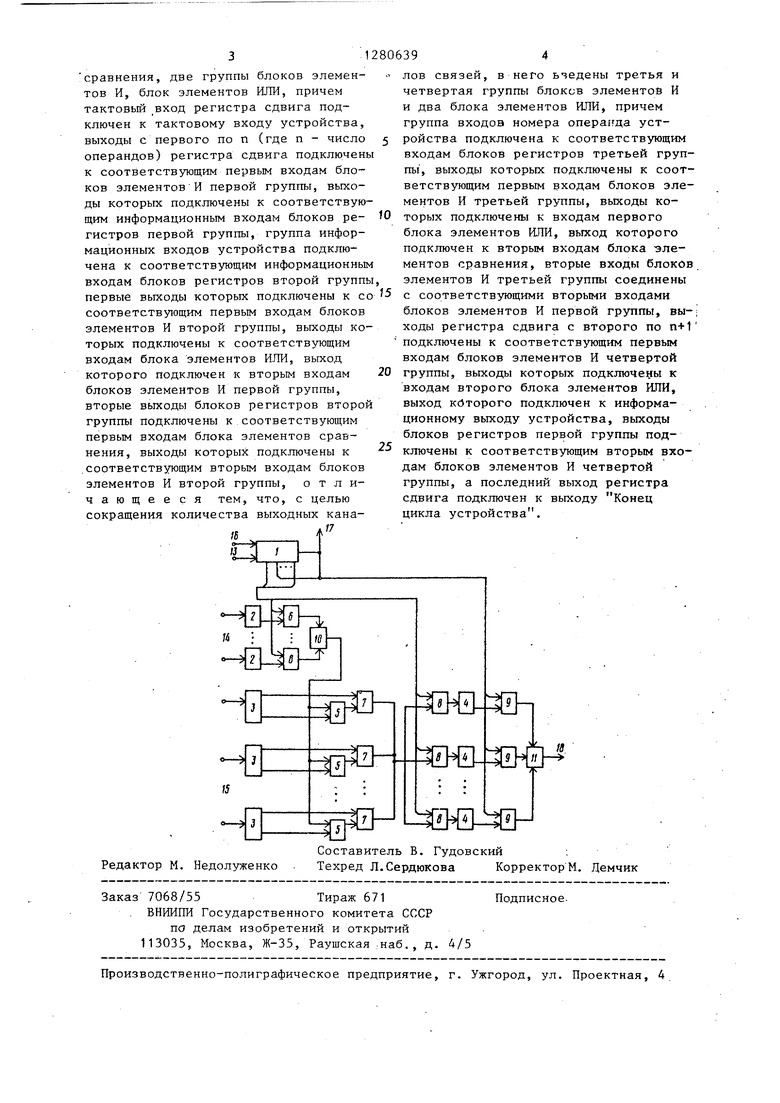

На чертеже дана структурная схема устройства.

Устройство содержит регистр 1 сдвига, первую, вторую и третью группы блоков регистров 2-4, блок элементов 5 сравнения, первую, вторую, третью, четвертую группы блоков элементов И 6-9, первый, второй, блоки элементов ИЛИ 10-12, первый, второй, третий,, четвертый входы 13-16 устройства, первый и второй выходы 17 и 18 устройства.

Устройство работает следующим образом.

Принцип работы устройства основан на последовательной выборке операндов находящихся в регистрах 3, в соответствии с их порядковыми номерами и заключается в том, что производится поочередное сравнение порядковых номеров, записанных в регистрах 2, с признаковыми частями всех операндов, и выбранные операнды последовательно записываются в регистры 4, откуда с задержкой на один такт устройства производится параллельно с записью их последовательная выдача в память или микропроцессор вычислительной системы.

Через входы 15 на регистры 3-подаются операнды с признаковыми частя- ми, представляющими собой порядковые номера операндов, В регистрах 2 (по входам 14) последовательно записаны номера операндов. Через вход 13 подается сигнал, записывающий 1 в первый разряд регистра 1 сдвига. Через вход 16 подается последовательность ;т1«1пульсов, которая осуществляет поразрядный последовательный сдвиг 1 последнего разряда регистра 1 . При сдвиге 1 на соответствующем выходе регистра 1 сдвига появляется сигнал 1. Этот сигнал разрешает подачу номера операнда из соответствую- ш,его регистра R через соответствую- нщй блок элементов И 6 и блок элементов ИЛИ 10 на первые входы всех элементов 5 сравнения. На вход каждого из элементов 5 сравнения по

5

0

5

5

Q

дается номер операнда из соответствующего регистра 3. На выходе того элемента 5 сравнения, на входах которого совпадают номера операндов, появляется сигнал, которьй поступает на второй вход соответствующего блока 7 элементов И и служит для него разрешающим сигналом. На первый вход каждого блока 7 элементов И поступает операнд, который проходит только че- рез один соответствующий блок 7 элементов И и поступает на вторые входы всех блоков элементов И 8.

Так как выборка операндов из регистров 3 проходит последовательно по номерам этих операндов, то на вторые входы блоков В элементов- И поступает первый, потом второй, потом все остальные операнды в порядке, определенном значениями признаков, содержащихся в регистрах 3.

Одновременно с поступлением на второй вход блоков 8 операнда на пер- вьй вход этого блока поступает разрешающий сигнал с выхода регистра 1 сдвига что позволяет операнду поступить на вход i-ro (,n) регистра 4 и записаться в него. Сигнал с выхода i+1-го разряда регистра 1 сдвига разрешает считывание операнда из i-ro регистра 4 через i-й блок элементов И 9 и блок элементов ИЛИ 11 на выход 18 устройства для записи в память или микропроцессор вычислительной 5 системы. Когда последний операнд окажется записанным в п-м регистре 4 и сигнал с выхода п+1-го разряда регистра 1 сдвига разрешит его считывание в память, цикл работы устройства завершается, о чем свидетельствует сигнал на выходе п+1-го разряда регистра 1, которьй поступает на выход 17.

В результате работы устройства неупорядоченная последовательности операндов, поступающих на входы 15 устройства, преобразуется в ряд операндов, записанных в регистрах 4 в соответствии со своими порядковыми номерами и выдаваемых в указанном порядке для записи в память вычислительной системы или микропроцессор.

0

0

JQ

55

Формула изобретения

Устройство для загрузки данных, содержащее регистр сдвига, три группы блоков регистров, блок элементов

сравнения, две группы блоков элементов И, блок элементов ИЛИ, причем тактовый вход регистра сдвига подключен к тактовому входу устройства, выходы с первого по п (где п - число операндов) регистра сдвига подключены к соответствующим первым входам блоков элементов И первой группы, выходы которых подключены к соответствующим информационным входам блоков регистров первой группы, группа информационных входов устройства подключена к соответствующим информационным входам блоков регистров второй группы первые выходы которых подключены к со соответствующим первым входам блоков элементов И второй группы, выходы которых подключены к соответствующим входам блока элементов ИЛИ, выход которого подключен к вторым входам блоков элементов И первой группы, вторые выходы блоков регистров второй группы подключены к соответствующим первым входам блока элементов сравнения, выходы которых подключены к соответствующим вторым входам блоков элементов И второй группы, отличающееся тем, что, с целью сокращения количества выходных канаJ7

O

5

0

5

лов связей, в него ьзедены третья и четвертая группы блоков элементов И и два блока элементов ИЛИ, причем группа входов номера опера1тда устройства подключена к соответствующим входам блоков регистров третьей группы , выходы которых подключены к соответствующим первым входам блоков элементов И третьей группы, выходы которых подключены к входам первого блока элементов ИЛИ, выход которого подключен к вторым входам блока элементов сравнения, вторые входы блоков. элементов И третьей группы соединены с соответствующими вторыми входами блоков элементов И первой группы, вы-; ходы регистра сдвига с второго по п+1 подключены к соответствующим первым входам блоков элементов И четвертой группы, выходы которых подключены к входам второго блока элементов ИЛИ, выход которого подключен к информационному выходу устройства, выходы блоков регистров первой группы подключены к соответствующим вторым входам блоков элементов И четвертой группы, а последний выход регистра сдвига подключен к выходу Конец цикла устройства.

Редактор М. Недолуженко

Составитель В. Гудовский

Техред Л.Сердюкова Корректор М. Демчик

Заказ 7068/55Тираж 671

. БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская ;Наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для упорядочения данных | 1985 |

|

SU1259246A1 |

| Устройство для загрузки данных | 1983 |

|

SU1103236A1 |

| Устройство для загрузки данных | 1986 |

|

SU1365083A2 |

| Устройство для загрузки данных в вычислительной системе | 1984 |

|

SU1254484A1 |

| Устройство для загрузки групповых данных | 1986 |

|

SU1328816A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для связи процессоров с внешними или запоминающими устройствами. Цель изобретения - сокращение количества выходных каналов связей. Устройство содержит регистр сдвига, три блока регистров, элементы сравнения. И, ИЛИ. Новым в устройстве является использование элементов И, ИЛИ. Устроит ство обеспечивает совмещение процес-. сов упорядочивания операндов по номерам и считывание их в полученном порядке в память вычислительной системы. 1 ил.

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для загрузки данных | 1983 |

|

SU1103236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-04-15—Подача