10

ч

9

fc

vi

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем, таких как суперкомпьютеры, цифровые фильтры, процессоров быстрого преобразования Фурье и решения систем линейных алгебраических уравнений. Известно суммирующее устройство, содержащее .постоянный запоминающий блок, ассоциативный запоминающий блок, элемент И, первую группу элементов И, вторую группу элементов И, третью группу элементов И, первую и вторую группы элементов задержки, причем первый раз- рядный выход ассоциативного запоминающего блока является выходом суммы устройства, остальные выходы ассоциативного блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы ко- торых подключены к первому входу синхронизации устройства, а выходы - к со- ответствующим входам оп роса первой труп п ы ассоциативного блока, адресные входы постоянного запоминающего блока соединены С выходами соответствующих элементов И второй группы, первые входы которых соединены с входами слагаемых устройства соответственно, а вторые входы -со вторым входом синхронизации устройства, младший разрядный выход постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подклю- чен к первому входу синхронизации устройства, а выход соединен с входом опроса второй группы ассоциативного блока, остальные разрядные выходы постоянного запоминающего блока через со- ответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к первому входу синхронизации устройства, а выходы соеди- нены с соответствующим входам третьей группы ассоциативного запоминающего блока.

Недостатком известного устройства яв- ляются ограниченные функциональные возможности, так как оно позволяет выполнять только операции группового суммирования двоичных операдов.

Цель изобретения - расширение функ- циональных возможностей устройства путем обеспечения возможности выполнения операции алгебраического сложение над блоками {А} и {Б} массивов двоичных операндов, заданных в прямом коде,и логических операций над ними: {А} {В}; {А} {В} и{А} {В}.

Поставленная цель достигается тем, что в устройство, дополнительно введены элемент НЕ, второй и третий элементы И, регистр-накопитель, четвертая, пятая, шестая и седьмая группы элементов И, третья и четвертая группы элементов задержки, второй и третий постоянные запоминающие блоки, причем младший разрядный выход второго постоянного запоминающего блока соединен с первым входом второго элемента И, второй вход которого подключен к первому входу синхронизации устройства, а выход соединен с входом опроса четвертой группы ассоциативного запоминающего блока, остальные разрядные выходы второго постоянного запоминающего блока через соответствующие элементы задержки четвертой группы соединены с первыми входами элементов И пятой группы, вторые входы которых подключены к первому входу синхронизации устройства, а выходы соединены с соответствующим входом опроса шестой группы ассоциативного запоминающего блока, вторая группа выходов которого через соответствующие элементы задержки третьей группы соединены с первыми входами элементов И четвертой группы, вторые входы которых подключены к первому входу синхронизации устройства, а выходы соединены с соответствующим входом опроса пятой группы ассоциативного запоминающего блока, третьи входы первого и второго элементов И объединены с третьими входами элементов И первой, второй, третьей и четвертой групп и подключены к входу сброса устройства, адресные входы второго постоянного запоминающего блока соединены с выходами элементов Л шестой группы, вторые входы которых подключены к второму входу синхронизации устройства, первые входы элементов И шестой группы подключены к второму информационному входу устройства, вторые входы элементов И седьмой группы объединены и подключены к второму входу синхронизации устройства, третьи входы элементов И седьмой группы объединены и соединены с выходом элемента НЕ, вход которого подключен к входу сброса устройства, первый, второй и третий входы третьего элемента И подключены к входу сброса устройства, первому входу синхронизации и управляющему входу устройства соответственно, выход третьего элемента И соединен с входом разрешения и записи регистра-накопителя, информационный вход которого подключен к первому информационному выходу устройства, весовые выходы регистра-накопителя,

начиная со старших разрядов, соединены с первыми входами соответствующих элементов И седьмой группы, выходы которых соединены с адресными входами третьего постоянного запоминающего блока, пер- вый выход которого является вторым информационным выходом устройства, второй, третий и четвертый выходы третьего постоянного запоминающего блока образуют соответствующие логические выходы устройства.

Сущность изобретения состоит в расширении функциональных возможностей устройства путем введения аппаратных средств, позволяющие выполнять операции Вычитание, помимо операции Сложение, одновременно над блоками {А} и {В} массивов двоичных операндов, заданных в прямом коде, и логических операций вида: {А} {В};{А} {В}и{А} {В}.

Введение второго и третьего постоянных запоминающих блоков, четвертого, пя-. того, шестого и седьмого групп элементов И, третьего и четвертого групп элементов задержки, второго и третьего элементов И, элемента НЕ, регистра-накопителя и обусловленных |ими связей позволяют организовать различные режимы работы устройства.

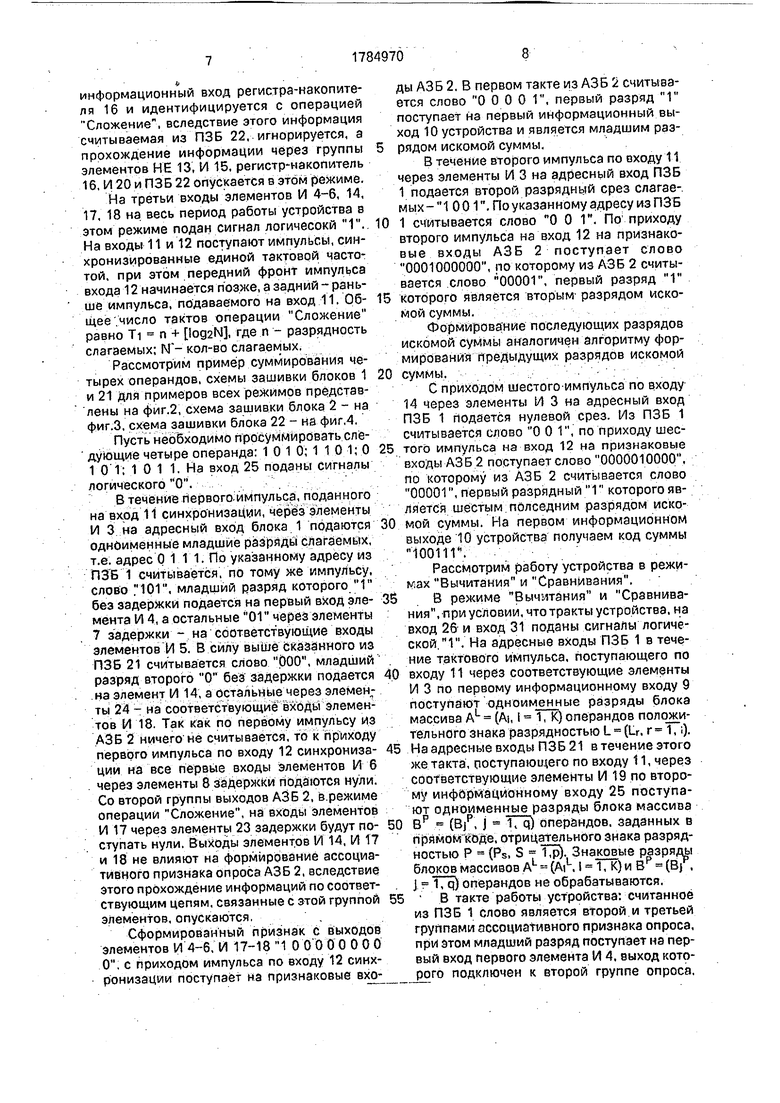

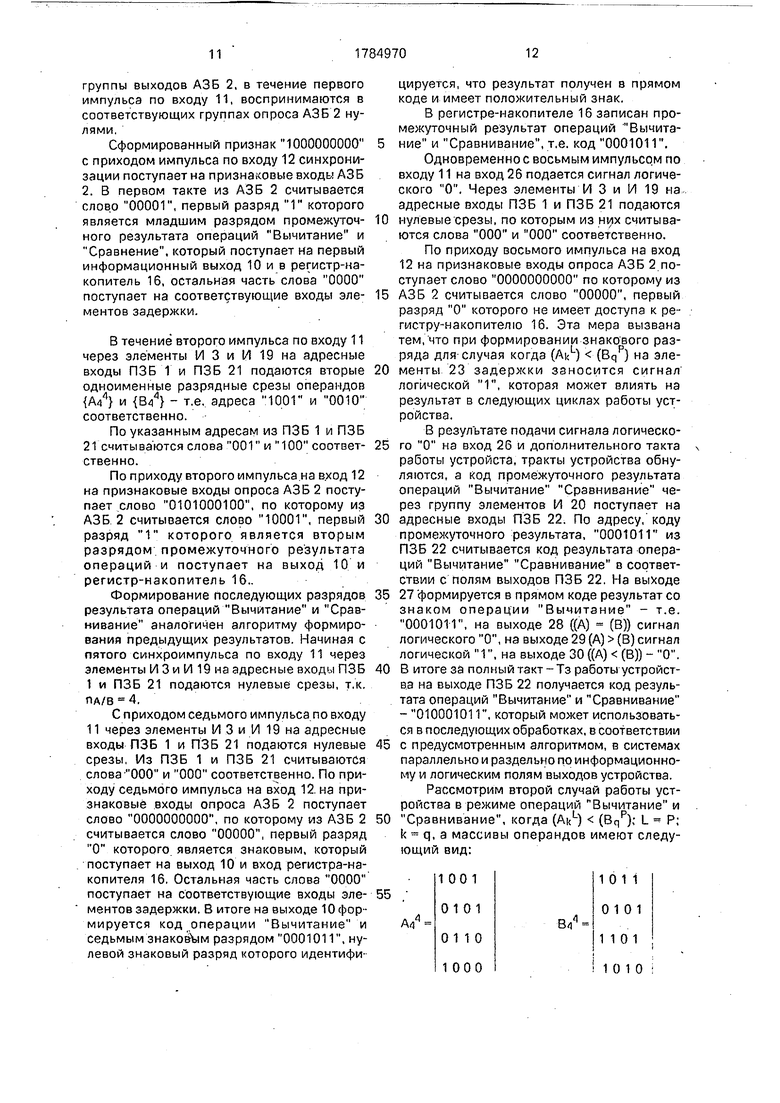

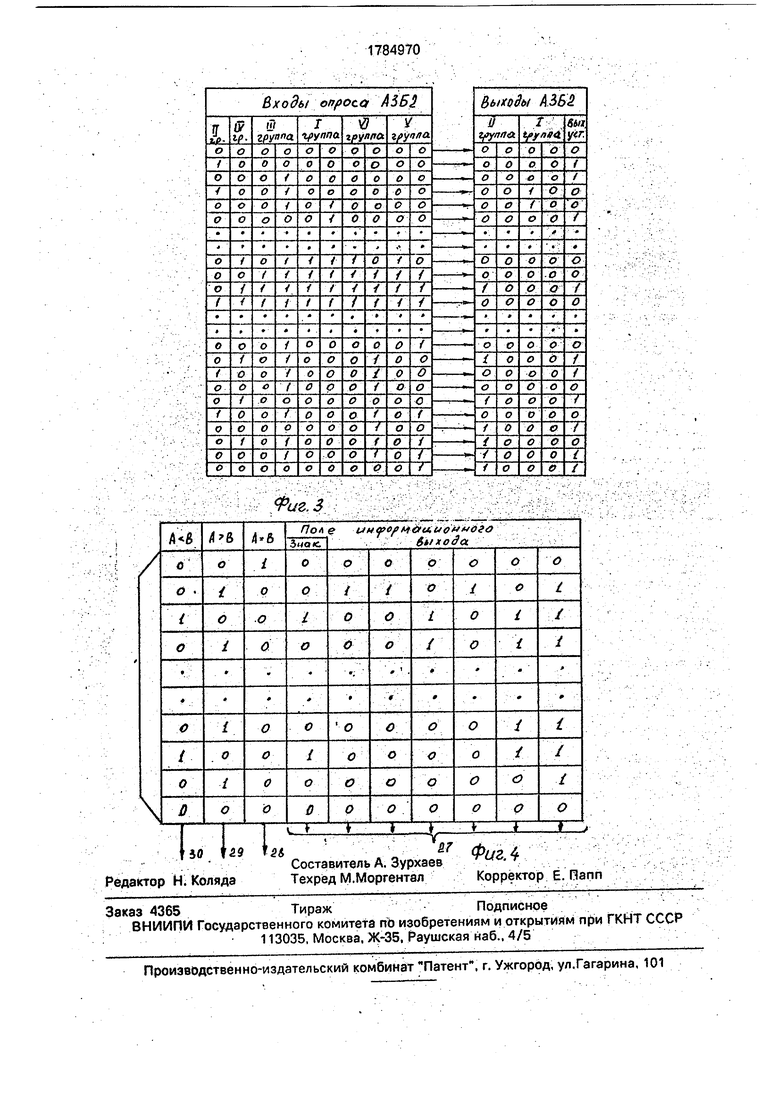

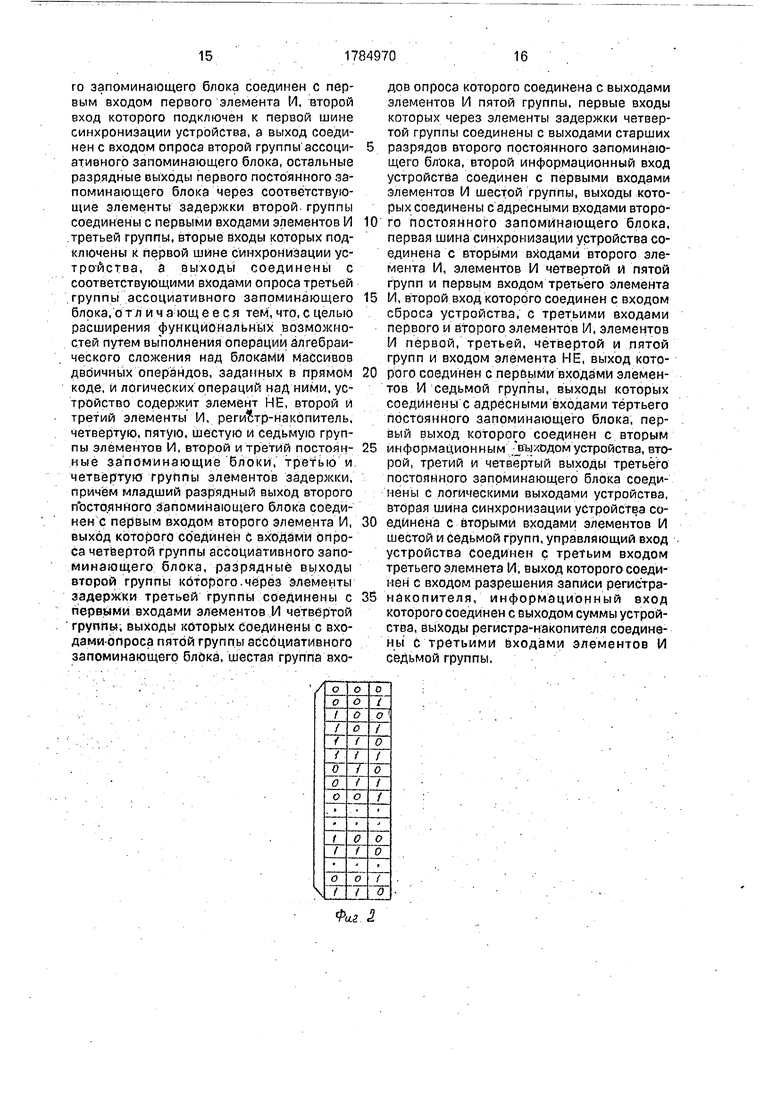

Нафиг.1 представлена функциональная схема заявляемого устройства; на фиг.2 - схема зашивки первого и второго постояно- го запоминающего блока; на фиг.З - схема зашивки третьего постоянного запоминающего блока.

Устройство содержит первый постоянный запоминающий блок (ПЗБ) 1, ассоциативный запоминающий блок (A3 Б) 2, вторую группу элементов И 3, первый элемент И 4, третью группу элементов 1/1 5, первую группу элементов И 6, вторую группу элементов 7 задержки, первую группу элементов 8 задержки, первый информационный выход 10 устройства, второй вход 11 синхронизации устройства, первый вход 12 синхронизации устройства, элемент НЕ 13, второй элемент И 14, третий элемент И 15, регистр-накопитель 16, четвертую группу элементов И 17, пятую группу элементов И 18, шестую груп- пу элементов И 19, седьмую группу элементов И 20. второй ПЗБ 21, третий ПЗБ 22, третью группу элементов 23 задержки, четвертую группу элементов 24 задержки, второй- информационный вход 25 устройства, вход 26 сброса устройства, второй информационный выход 27 устройства, третий 28, четвертый 29 и пятый 30 логические выходы устройства, управляющий вход 31 устройства.

Принцип действия устройства заключается в следующем.

Устройство функционирует в трех режимах: Сложение, Вычитание и Сравнение блоков {А} и {В} массивов двоичных операндов, представленных в прямом коде, при этом режимы Вычитание и Сравнивание совмещены в одном цикле работы устройства.

В режиме Сложение на- все входы 25 ПЗБ 21 и вход 31 поданы сигналы логического О, а на вход 26 -сигнал логической 1. На адресные входы ПЗБ 1 в течение тактового импульса, поступающего по входу 11, через соответствующие элементы И 3 по первому информационному входу 9 поступают одноименные разряды слагаемых. Считанное из ПЗБ 1 слово является частью ассоциативного признака опроса для АЗБ 2. при этом младший разряд поступает на первый вход первого элемента И 4, выход которого подключен ко вто рой группе опроса, остальные разрядные выходы ПЗБ 1 через соответствующие элементы 7 задержки соединены с первыми входами элементов И 5, выходы которых подключены к третьей группе опроса A3 Б 2, На адресные входы ПЗБ 21 в течение этого же такта, поступающего по входу 11, через соответствующие элементы И 19 по второму информационному входу 25 поступает срез сигналов логического О. Считанное из ПЗБ 21 слово из нулей является частью ассоциативного признака опроса для АЗБ 2, при этом младший разряд поступает на первый вход второго элемента И 14, выход которого подключен к четвертой группе опроса, остальные разрядные выходы ПЗБ 21 через соответствующие элементы 24 задержки соединены с первыми входами элементов И 18, выходы которых подключены к шестой группе опроса АЗБ 2. Считанное из АЗБ 2 слово, кроме первого разряда. по первой группе выходов через соответствующие элементы 8 задержки поступают на первые входы элементов И 6, выходы которых подключены к первой группе опроса АЗБ 2. По второй группе выходов АЗБ 2 через соответствующие элементы 23 задержки поступают на первые входы элементов И 17, выходы которых подключены к пятой группе опроса ассоциативного признака. Сформированный признак дополнительно синхронизируется на элементах И путем подачи на вторые входы этих элементов импульса по входу 12 устройства. Такая синхронизация исключает всякие неидеальности соответствующих элементов задержки. На выходе 10 формируется очередной разряд суммы операндов. Сигнал логического О на входе 31 через элемент 15 отключает

информационный вход регистра-накопителя 16 и идентифицируется с операцией Сложение, вследствие этого информация считываемая из ПЗБ 22, игнорируется, а прохождение информации через группы элементов НЕ 13, И 1.5, регистр-накопитель

16,И 20 и ПЗБ 22 опускается в этом режиме.

На третьи входы элементов I/I 4-6, 14,

17,18 на весь период работы устройства в этом режиме подан сигнал логичесокй 1. На входы 11 и 12 поступают импульсы, синхронизированные единой тактовой частотой, при этом передний фронт импульса входа 12 начинается позже, а задний - раньше импульса, подаваемого на вход 11. Об- щее .число тактов операции Сложение равно Ti n + Iog2N, где п - разрядность слагаемых; NT- кол-во слагаемых.

Рассмотрим пример суммирования четырех операндов, схемы зашивки блоков 1 и 21 для примеров всех режимов представлены на фиг.2, схема зашивки блока 2 - на фиг.З, схема зашивки блока 22 - на фиг,4.

Пусть необходимо просуммировать следующие четыре операнда: 1 0 1 0; 1 1 0.1;.О 1 ОТ; 1011. На вход 25 поданы сигналы логического О.

В течение первого-ймпульса, поданного на вход 11 синхро низации, через элементы 1/1 3 на адресный вход блока 1 подаются одноимённые младшие разряды слагаемых, т.е. адрес О 1 1 1. По указанному адресу из ПЗБ 1 считывается, по тому же импульсу, слово 101. младший разряд которого 1 без задержки подается на первый вход эле- мента И 4, а остальные 01 через элементы 7 задержки - на соответствующие входы элементов И 5. В силу выше сказанного из ПЗБ 21 считывается слово 000, младший разряд второго О без задержки подается на элемент И 14, а остальные через элемено- ты 24 - на соответствугощйё входы элементов И 18. Так как по первому импульсу из АЗБ 2 ничего не считывается, то к приходу первого импульса по входу 12 синхрониза- ции на все первые входы элементов 1/1 6 . через элементы 8 заДерхски подаются нули. Со второй группы выходов АЗБ 2, в.режиме операции Сложение, на входы элементов И 17 через элементы 23 задержки будут по- ступать нули. Выходы элементов И 14, И 17 и 18 не влияют на формирование ассоциативного признака опроса АЗБ 2, вследствие этого прохождение информации по соответ- ствующим цепям, связанные с этой группой элемент-ов, опускаются,

Сформированный признак с выходов элементов И 4-б.И 17-18 100000000 О, с приходом импульса по входу 12 синхронизации поступает на признаковые входы АЗБ 2. В первом такте из АЗБ 2 считывается слово 0000 1, первый разряд 1 поступает на первый информационный выход 10 устройства и является младшим разрядом искомой суммы.

В течение второго импульса по входу 11 через элементы И 3 на адресный вход ПЗБ 1 подается второй разрядный срез слагае- 001. По указанному адресу из ПЗБ 1 считывается слово О 0 1. По; приходу второго импульса на вход 12 на признаковые входы АЗБ 2 поступает слово 0001000000, по которому из АЗБ 2 считывается .слово 00001, первый разряд 1 которого является вторым разрядом искомой суммы.

Формйроват-ше последующих разрядов искомой суммы аналогичен алгоритму формирования предыдущих разрядов искомой

СуММЫ..;.- . ;

С приходом шестого-импульса по входу 14 через элементы И 3 на адресный вход ПЗБ 1 подается нулевой срез. Из ПЗБ 1 считывается слово О 0 1, по приходу шестого импульса на вход 12 на признаковые входы АЗБ 2 поступает слово 0000010000, по которому из АЗБ 2 считывается слово 00001, первый разрядный 1 которого является шестым :полседним разрядом искомой суммы. На первом информационном выходе 10 устройства получаем код суммы 100111.

Рассмотрим работу устройства в режимах Вычитания и Сравнивания.

В режиме Вычитания и Сравнивания,-при условии, что тракты устройства, на вход 26 и вход 31 поданы сигналы логической. 1. На адресные входы ПЗБ 1 в течение тактового импульса, поступающего по входу 11 через соответствующие элементы И 3 по первому информационному входу 9 поступают одноименные разряды блока массива AL (At, I 1, К) операндов положительного знака разрядностью L(Lr, г 1, i). На адресные входы ПЗБ 21 в течение этого же такта, поступающего по входу 11, через соответствующие элементы И 19 по второму информационному входу 25 поступают одноименные разряды блока массива Вр .. (Bjp, j TTq) операндов, заданных в прямомтШде, отрицательного знака разрядностью Р (Ps, S Тр). Знаковые разряды блоков массивов AL - (AiL. I 1, К) и Вр (Bj , j iVq) операндов не обрабатываются.

В такте работы устройства: считанное из ПЗБ 1 слово является второй и третьей группами ассоциативного признака опроса, при этом младший разряд поступает на первый вход первого элемента И 4, выход которого подключен к второй группе опроса,

остальные разрядные выходы ПЗБ 1, через соответствующие элементы 7 задержки соединены с первыми входами элементов И 5, выходы которых подключен к третьей группе опроса; считанное из ПЗБ 21 слово является четвертой и шестой группами ассоциативного признаками опроса, при этом младший разряд поступает на первый вход второго элемента И 14, выход которого подключен к четвертой группе опроса, остальные разрядные выходы ПЗБ 21, через соответствующие элементы 24 задержки соединены с первыми входами элементов И 18. выходы которых подключены к шестой группе опроса АЗБ 2. Считанное из АЗБ 2 слово, кроме первого разряда, по первой группе, выходов через соответствующие элементы 8задержки поступают на первые входы И 6, выходы которых подключены к первой группе опроса АЗБ-2. По второй группе выходов АЗБ 2 через соответствующие элементы 23 задержки поступают на первые входы элементов И 17, выходы которых подключены к пятой группе опроса ассоциативного признака АЗБ 2, Сформулированный признак дополнительно синхронизируется на элементах И 4-6, И 14, И 17-18 путем подачи на вторые входы этих элементов импульса по входу 12 устройства и подается на АЗБ 2, по которому считывается слово, первый разряд которого является разрядом промежуточного результата операций Вычитание и Сравнивание над блоками массивов {AkL} и {Bqp} операндов, который поступает на первый информационный выход 10 устройства и заносится в регистр-накопитель 16.

Число тактов для формирования промежуточного результата равно1

Т2 ПА/В + IOQ2 NA/B + 1.

где

пд L. при L Р : пв Р.

NA AkL, при AkL BqP РLР

N8 Bq , При Ak Bq ,

ПА/В разрядность операндов в массивах А/В;

NA/B - количество операндов в массивах А/В.

На выходе 10 за Та - тактов формируется промежуточный результат операции, при этом (Ak j (Вч в правильном прямом коде, при (Ak ) (Bq ) в обратном коде. Последний формируемый разряд в такте работы устройства является знаковым, при этом логический О отожествляется положительным результатом операции (знаком) Вычитание, логическая 1 - отрицательным

результатом (знаком) операции Одновременно за Та-тактов промежуточный результат последовательно в такте работы устройства заносится в регистр-накопитель 5 16.

Окончательный результат получается за один дополнительный такт работы устройства и за счет подачи сигнала логического О на вход 26, который через элемент I/I 15

0 отключает регистр-накопитель 16 от первого информационного выхода 10 устройства, а через элемент НЕ 13 разрешает считывание содержимого регистра-накопителя 16. Считанная информация с регистра яоляется

5 адресом ПЗБ 22, по которому считывается слово, часть которой по выходу 27 является результатом операции Вычитание, выдаваемая в прямом коде со знаком. Другая часть слова - результат операции Сравни0 вание и является логическими выходами устройства, при этом выход 28 идентифицируется сигналом логической 1 логику.

{А} {В}; выход 29 - {А} {В}; эыход 30 {А} {В}. Сигнал логического О, поданного

5 в последнем работы устройства, обнуляет тракты устройства и подготавливает для следующего цикла работы устройства.

Общее число тактов работы при этом равен:

0 Т3 ПА/В + ioga NA/B + 2

Рассмотрим два случая работы устройства в режиме операции Вычитание и Сравнивание. Пусть необходимо вычислить разность двух массивов операндов при слу5 чае, когда выполняются условия (AkL) (Bq ), L Р; k q и имеют следующий вид:

0

А4

1011 0101 1101 1010

В44

1001 0101

0110 1 000

45

0

5

В течение первого импульса, поданного на вход 11 синхронизации, на адресные входы блоков ПЗБ 1 и ПЗБ 21 подаются одноименные младшие разряды операндов а прямом коде из массивов и в соответствии их физических связей; через элементы ИЗ-адрес 1110, через элементы И 19-адрес 1100. По указанным адресам из ПЗБ 1 и.ПЗБ2Считываются, потому же импульсу, слова осответственно 101 и 001, младшие разряды которых 1 и О соответственно, без задержки, подаются на соответствующие входы элементов И 4 и И 14, а остальные разряды слов 01 и 01 нп элементы 7 и 24 задержки. Первая и вторая

группы выходов АЗБ 2, в течение первого импульса по входу 11, воспринимаются в соответствующих группах опроса АЗБ 2 нулями.

Сформированный признак 1000000000 с приходом импульса по входу 12 синхронизации поступает на признаковые входы АЗБ 2. В первом такте из АЗБ 2 считывается слово 00001, первый разряд 1 которого является младшим разрядом промежугоч- ного результата операций Вычитание и Сравнение, который поступает на первый информационный выход 10 и в регистр-накопитель 16, остальная часть слова 0000 поступает на соответствующие входы эле- ментов задержки.

В течение второго импульса по входу 11 через элементы И 3 и И 19 на адресные входы ПЗБ 1 и ПЗБ 21 подаются вторые одноименные разрядные срезы операндов {А44} и {В44} - т.е. адреса 1001 и 0010 соответственно.

По указанным адресам из ПЗБ 1 и ПЗБ 21 считываются слова 001 и 100 соответ- ственно.

По приходу второго импульса на вход 12 на признаковые входы опроса АЗБ 2 поступает слово 0101000100, по которому из АЗБ 2 считывается слово 10001, первый разряд 1 которого является вторым разрядом промежуточного результата операций и поступает на выход 10 и регистр-накопитель 16..

Формирование последующих разрядов результата операций Вычитание и Сравнивание аналогичен алгоритму формирования предыдущих результатов. Начиная с пятого синхроимпульса по входу 11 через элементы И 3 и И 19 на адресные входы ПЗБ

Iи ПЗБ 21 подаются нулевые срезы, т.к. ПА/В 4.

С приходом седьмого импульса по входу

IIчерез элементы И 3 и I/I 19 на адресные входы ПЗБ 1 и ПЗБ 21 подаются нулевые срезы, Из ПЗБ 1 и ПЗБ 21 считываются слова 000 и 000 соответственно. По приходу седьмого импульса на вход 12 на признаковые входы опроса АЗБ 2 поступает слово 0000000000, по которому из АЗБ 2 считывается слово 00000, первый разряд О которого является знаковым, который поступает на выход 10 и вход регистра-накопителя 16. Остальная часть слова 0000 поступает на соответствующие входы эле- ментов задержки. В итоге на выходе 10 фор- мируется код операции Вычитание и седьмым знаковом разрядом 0001011, нулевой знаковый разряд которого идентифицируется, что результат получен в прямом коде и имеет положительный знак.

В регистре-накопителе 16 записан промежуточный результат операций Вычитание и Сравнивание, т.е. код 0001011.

Одновременно с восьмым импульсом по входу 11 на вход 26 подается сигнал логического О, Через элементы И 3 и И 19 на адресные входы ПЗБ 1 и ПЗБ 21 подаются нулевые срезы, по которым из них считываются слова 000 и 000 соответственно.

По приходу восьмого импульса на вход 12 на признаковые входы опроса АЗБ 2 поступает слово 0000000000 по которому из АЗБ 2 считывается слово 00000, первый разряд О которого не имеет доступа к регистру-накопителю 16. Эта мера вызвана тем, что при формировании знакового разряда для случая когда (AkL) (Bqp) на элементы 23 задержки заносится сигнал логической 1, которая может влиять на результат в следующих циклах работы устройства.

В результате подачи сигнала логического О на вход 26 и дополнительного такта работы устройств, тракты устройства обнуляются, а код промежуточного результата операций Вычитание Сравнивание через группу элементов И 20 поступает на адресные входы ПЗБ 22. По адресу, коду промежуточного результата, 0001011 из ПЗБ 22 считывается код результата операций Вычитание Сравнивание в соответствии с полям выходов ПЗБ 22. На выходе 27 формируется в прямом коде результат со знаком операции Вычитание - т.е. 0001011, на выходе 28 ((А) (В)) сигнал логического О, на выходе 29 (А) (В) сигнал логической 1, на выходе 30 ((А) (В)) - О. В итоге за полный такт-Тз работы устройства на выходе ПЗБ 22 получается код результата операций Вычитание и Сравнивание - 010001011, который может использоваться в последующих обработках, в соответствии с предусмотренным алгоритмом, в системах параллельно и раздельно по информационному и логическим полям выходов устройства.

Рассмотрим второй случай работы устройства в режиме операций Вычитание и Сравнивание, когда (AkL) (Bqp),- L Р; k q, а массивы операндов имеют следующий вид:

1 001 0101 0110 1 000

в

1011 0101 1101 1010

Алгоритм формирования результата аналогичен предыдущему примеру, когда

(AkL) (BqP).

С приходом седьмого импульса по входу 11 через элементы И 3 и И 19 на адресные входы ПЗБ 1 и ПЗБ 21 подаются нулевые срезы. Из ПЗБ 1 и ПЗБ 21 считываются слова 000 и 000 соответственно. По приходу седьмого импульса на вход 12 на признаковые входы опроса A3 Б 2 поступает слово ОООООООООГ, по которому из АЗБ 2 считывается слово 10001, первый разряд 1 которого является знаковым, который поступает на выход 10 и вход регистра-накопителя 16. Остальная часть слова 1000 поступает: по первой группе выходов код 00 на элементы 8 задержки, по второй группе выходов код 10 поступает на элементы 23 задержки,

В итоге на выходе 10 формируется код операции Вычитание с седьмым знаковым разрядом 1110101, единичный знаковый разряд которого идентифицирует, что результат получен в обратном коде и имеет отрицательный знак.

В регистре-накопителе 16 записан промежуточный результат операций Вычитание и Сравнивание, т.е. код 1110101. Одновременно с восьмым импульсом по входу 11 на вход 26 подается сигнал логического О. Через элементы И 3 и И 19 на адресные входы ПЗБ 1 и ПЗБ 21 подаются нулевые срезы, по которым из них считываются слова 000 и 000 соответственно. По приходу восьмого импульса на вход 12 на признаковые входы опроса АЗБ 2 поступает слово 0000000000 по которому из АЗБ 2 Считывается слово 00000, первый разряд О которого не имеет доступа к регистру-накопителю 16, за счет сигнала логического О с выхода элемента И 15.

В результате подачи сигнала логическо го О на вход 26 и дополнительного такта работы устройства тракты устройства обнуляются, а код промежуточного результата операций Вычитание и Сравнивание через группу элементов И 20 поступает на адресные входы ПЗБ 22. По адресу, коду промежуточного результата, 1110101 из ПЗБ 22 считывается код результата операций Вычитание и Сравнивание в соответствии с полями выходов ПЗБ 22. На выходе 27 формируется в прямом коде результат со знаком операции Вычитание - т.е. 10001011. На выходах 28-30 ПЗБ 22 формируется результата операции Сравнивание, при этом на выходе 28 ((А) (В)) сигнал логического О, на выходе 29 ((А) (В) сигнал логического О, на выходе 30 ((А) (В)) сигнал логической 1.

В итоге за полный такт - Т3 работы устройства на выходе ПЗБ 22 получается код результата операции Вычитание и Сравнивание - 1001001011, который может использоваться в последующих обработках. Работа устройства в режиме операций Вычитание и Сравнивание когда {AkL} {Bqp} аналогичен предыдущим случаям. На выходе 1.0 формируется код

операций Вычитание - 0000000, а на выходах ПЗБ 2 код результата операций Вычитание и Сравнивание - 0010000000 с раскладкой по выходам: выход 28 ((А) (В) - выход 29 ((А) (В) - выход 30

((А) (В) - второй информационный выход 28 - 0000000.

Техническое преимущество изобретения, по сравнению с известным состоит в расширении функциональных возможностей за счет дополнительного выполнения операции Вычитание и Сравнивание, Положительный эффект заключается в совмещении в одном устройстве выполнения операции алгебраического сложения и логических операций над блоками массивов операндов, кроме того возможность выполнения операции алгебраического сложения над блоками массивов операндов, представленных в прямом коде, приводит к значительному уменьшению стоимости машинной операции по преобразованию отрицательных операндов.

35

Формула изобретения

Суммирующее устройство, содержащее первый постоянный запоминающий блок, ассоциативный запоминающий блок, первый элемент И, элементы И первой, вто0. рой и третьей групп, элементы задержки первой и второй групп, причем первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, разрядные выходы первой

5 группы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых под0 ключены к первой шине синхронизации устройства, а выходы - к соответствующим входам опроса первой группы ассоциативного запоминающего блока, адресные входы первого постояного запоминающего

5 блока соединены с выходами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства, а вторые входы - с второй шиной синхронизации устройства, младший разрядный выход первого запоминающего блока соединен с первым входом первого элемента И, второй вход которого подключен к первой шине синхронизации устройства, а выход соединен с входом опроса второй группы ассоци- ативного запоминающего блока, остальные разрядные выходы первого постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входами опроса третьей группы ассоциативного запоминающего блока, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей путем выполнения операции алгебраического сложения над блоками массивов двоичных операндов, заданных в прямом коде, и логических операций над ними, устройство содержит элемент НЕ, второй и третий элементы И, регистр-накопитель, четвертую, пятую, шестую и седьмую группы элементов И, второй и третий постоян- иые запоминающие блоки, третью и четвертую группы элементов задержки, причем младший разрядный выход второго постоянного запоминающего блока соединен с первым входом второго элемента И, выход которого со единен с входами опроса четвертой группы ассоциативного запоминающего блока, разрядные выходы второй группы которого.через элементы задержки третьей группы соединены с первыми входами элементов И четвертой группы, выходы которых соединены с вхо- дами-onpoca пятой группы ассоциативного запоминающего блока, шестая группа входов опроса которого соединена с выходами элементов И пятой группы, первые входы которых через элементы задержки четвертой группы соединены с выходами старших разрядов второго постоянного запоминающего блока, второй информационный вход устройства соединен с первыми входами элементов И шестой группы, выходы которых соединены с адресными входами второго постоянного запоминающего блока, первая шина синхронизации устройства соединена с вторыми входами второго элемента И, элементов И четвертой и пятой групп и первым входом третьего элемента И, второй вход которого соединен с входом сброса устройства, с третьими входами первого и второго элементов И, элементов И первой, третьей, четвертой и пятой групп и входом элемента НЕ, выход которого соединен с первыми входами элементов И седьмой группы, выходы которых соединены с адресными входами тертьего постоянного запоминающего блока, первый выход которого соединен с вторым информационным jbj/одомустройства, второй, третий и четвёртый выходы третьего постоянного запоминающего блока соединены с логическими выходами устройства, вторая шина синхронизации устройства соединена с вторыми входами элементов И шестой и седьмой групп, управляющий вход устройства соединен с третьим входом третьего элемнета И, выход которого соединен с входом разрешения записи регистра- накопителя, информационный вход которого соединен с выходом суммы устройства, выходы регистра-накопителя соединены с третьими входами элементов И седьмой группы.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1972 |

|

SU330670A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

Изобретение может быть использовано при построении высокопроизводительных вычислительных систем, таких как суперкомпьютеры, цифровые фильтры, процессоров быстрого преобразования Фурье и решения систем линейных уравнений. Цель изобретения состоит в расширении функциональных возможностей путем обеспечения возможности выполнения операции алгебраического сложения над блоками массивов двоичных операндов, заданных в прямом коде, и логических операций над ними. Устройство содержит три постоянных запоминающих блока 1, 21, 27, ассоциативный запоминающий блок 2, три элемента И 4,14, 15, с первой по седьмую группы 5, 6% 17-20 элементов И, с первой по четвертую группы 7,8,23,24 элементов задержки, элемент НЕ 13 и регистр-накопитель 16. Выбор режимов работы устройства производится путем подачи на управляющий и сбросовый входы ус- тройства соответствующих логических сигналов. 4 ил. (Л С

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-10-31—Подача