Изобретение относится к области выислительной техники и может быть исользовано 6 скалярных и векторных ыстродействующих процессорах обработи цифровой информации,5

Известно устройство для умножения воичньТхЧ блТсодержащее регистры мно- й,могогй множителя, блок анализа разря- сгв множителя, блок формирования кратных множимого, бло к сумматоров двух- 10 рядного кода первого уровня, блок регистров первого уровня, сумматор двухрядного кода второго уровня, два регистра второго ровня, параллельный сумматор, регистр результата.15

Недостатком данного устройства явля- ются сложная организация вычислительного процесса , обусловленая выработкой ольшого количества управляющих сигна- ов путем анализа разрядов множителя; уз- 20 кая область применения, обусловленная отсутствием возможности выполнения других операций, помимо операции умножителя.

Известно ассоциативное устройство. 25 осуществляющее операции одновременного сложения нескольких и умножения двух чисел. Данное устройство содержит регистр множимого, регистр множителя, постоянный запоминающий блок, ассоциативный 30 блок, два преобразователя двоичного кода в код количества единиц, три группы элементов И, две группы элементов задержки, элемент И и элемент задержки.

Недостатком данного устройства явля- 35 ется структурная организация операции умножения, обусловленная отсутствием возможности выполнения операции одновременного умножения нескольких операндов.40

Наиболее близким к предлагаемому является суммирующее устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, элемент И, три группы элементов И, две группы 45 элементов задержки, причем первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, выходы остальных разрядов которого через соответствующие элементы за- 50 держки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первому входу синхронизации устройства, а выходы - к 55 соответствующим входам опроса третьей группы ассоциативного запоминающего блока, адресные входы постоянного запоминающего блока соединены с входами соответствующих элементов И третьей

группы, первые входы которых соединены с входами слагаемых устройства, соответственно, младший разрядный выход постоянного запоминающего блока соединен с вторым входом элемента И, первый вход которого подключен к первому входу синхронизации устройства, а выход соединен с входом опроса первой группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с вторыми входами элементов И второй группы, а выходы соединены с соответствующими входами опроса второй группы ассоциативного запоминающего блока.

Недостатком данного устройства является - ограниченные функциональные возможности, так как позволяет выполнять только операцию одновременного суммирования двоичных чисел.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности выполнения:

операции вида Р

2, ак Bim;

I 1

; одновременного умножения трех операндов; помимо операции одновременного суммирования.

Поставленная цель достигается тем, что в устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, элемент И, три группы элементов И, две группы элементов задержки, причем выход устройства соединен с выходом первого разряда ассоциативного запоминающего блока, выходы остальных разрядов которого через элементы задержки первой группы соединены с первыми входами элемнетов И первой группы, вторые входы которых соединены с первым входом синхронизации устройства, с первыми входами элементов И второй группы и первым входом элемента И, второй вход которого соединен с выходом младшего разряда постоянного запоминающего блока, выход остальных разрядов которого через элементы задержки второй группы соединены с вторыми входами элементов И второй группы, выход элемента И и элементов И второй и первой групп соединены с входами опроса первой, второй и третьей группы соответственно ассоциативного запоминающего блока, адресные входы постоянного запоминающего блока соединены с выходами элементов И третьей группы, дополнительно введены первый регистр разрядности К, второй регистр разрядности g N/K, где N - количество одновременно суммируемых

операндов, q - буферных блоков регистров по К регистров каждый, элементы задержки и злемнет ИЛИ, R - входов которого соединены с шиной синхронизации, выход элемента ИЛИ через элемент задержки соединен с первыми входами элементов И третьей группы, синхровход j-ro регистра, где 1К, 1-го буферного блока регистров соединен с j-м выходом i-й шиной синхронизации устрйоства, первые ин- формационные входы которого соединены с информационными входами соответствующих регистров буферных блоков регистров, выходы которых соединены с вторыми входами соответствующих элементов И третьей группы, третьи и четвертые входы которых соединены с выходами соответствующих разрядов первого и второго регистров соответственно, информационные входы которых соединен ы соответственно с вторым и третьим информационными входами устройства. .

Сущность изобретения состоит в расширении функциональных возможностей устройства путем введения технических средств, позволяющие выполнять операции умножения трех операндов и операции вида

Р ак Bim. (где ак - постоянный коэффиi 1

циент разрядностью К, В (Bim, I 1, q) - операнды разрядностью т).

Введение технических средств и обусловленных ими связей позволяет организовать три режима работы устройства: суммирования N операндов, умножения трех операндов и выполнения операции вида Р

i 1

ак Bim.

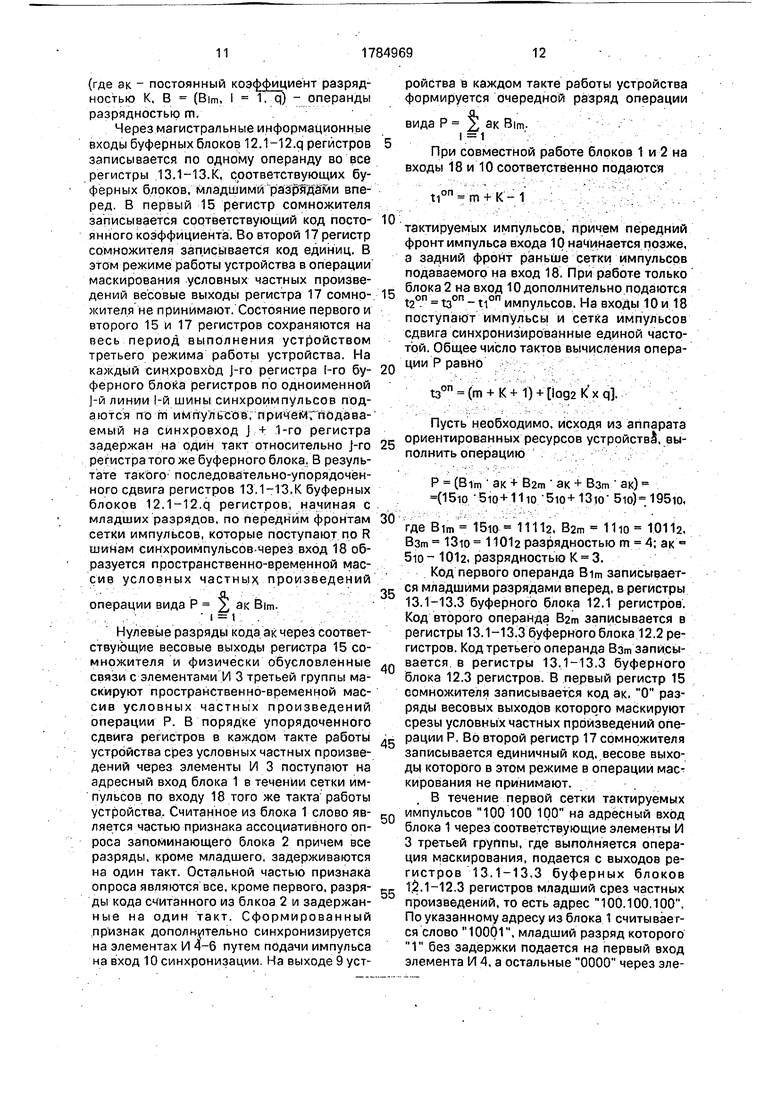

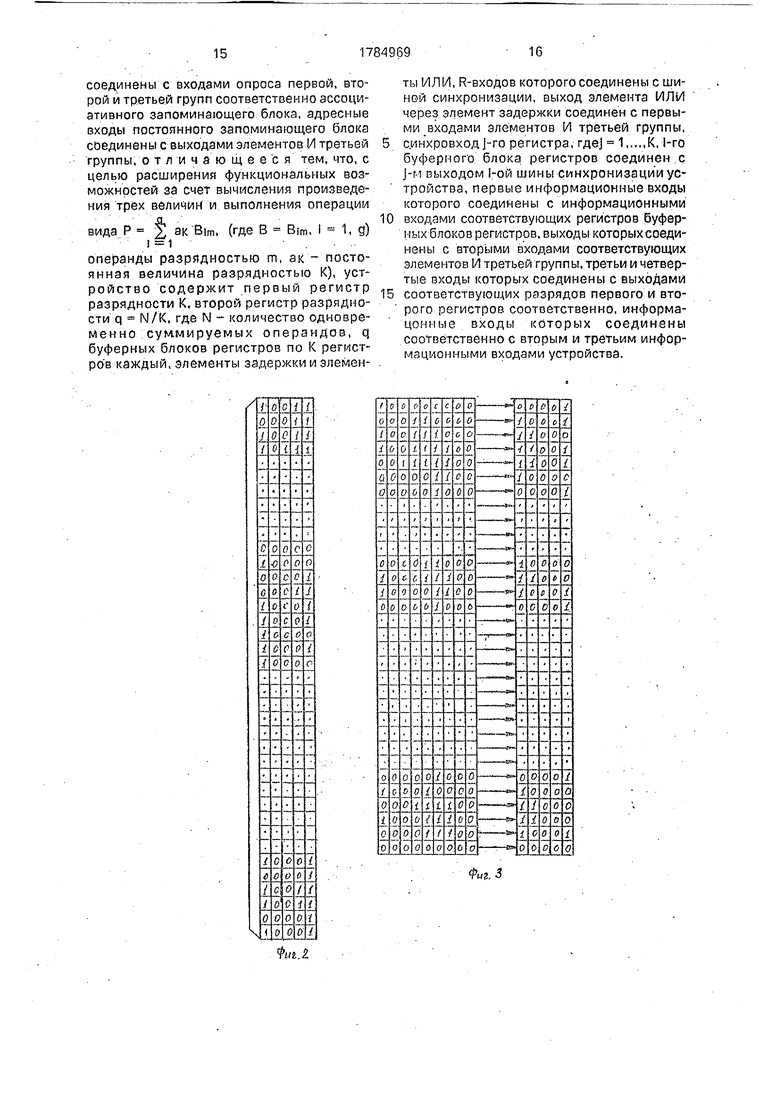

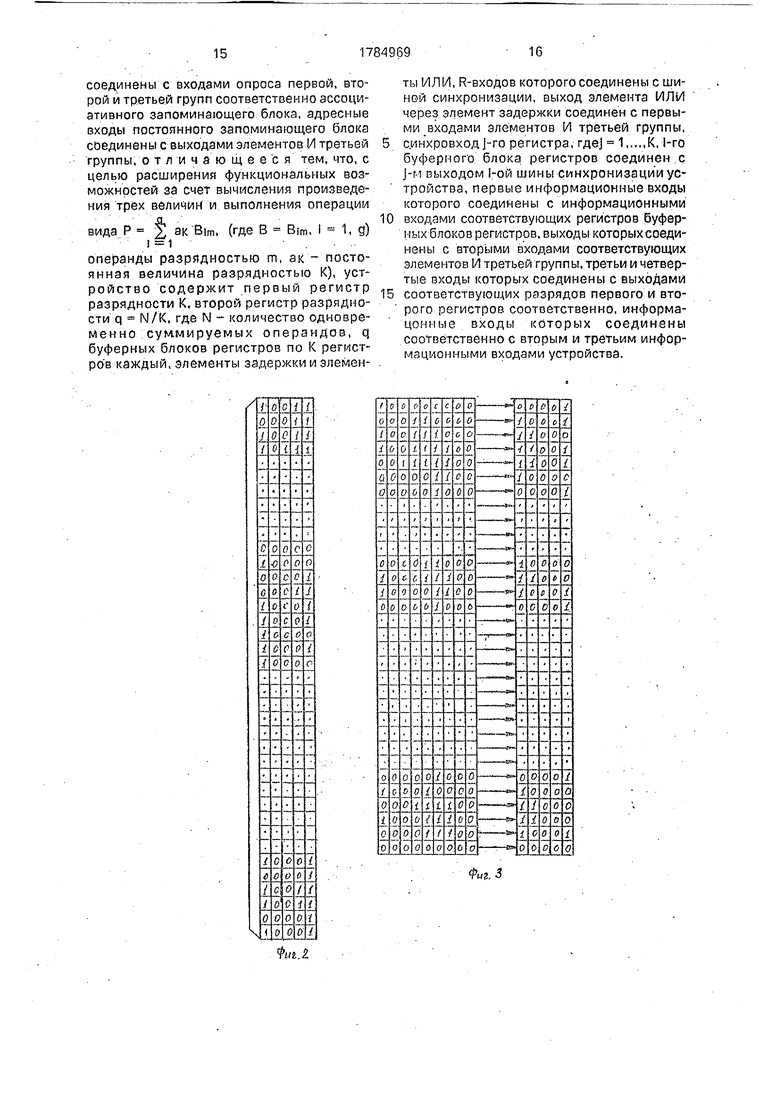

На фиг.1 представлена функциональная схема заявляемого устройства: на фи г.2 - схема зашивки постоянного запоминающего блока: на фиг.З - схема зашивки ассоциативного запоминающего блока.

Устройство содержит (фиг.1) постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, первую группу элементов И 6. вторую группу элементов И 5. третью группу элементов И 3, элемент И 4, первую группу элементов 8 задержки, вто- рую группу 7 задержки, общий выход 9 для всех операций, первый вход 10 синхрониза- ции устройства, многовходовый элемент ИЛИ 19, элемент 20 задержки, второй информационный вход 14 сомножителя, первый регистр 15 сомножителя, третий информационный вход 16 сомножителя, второй регистр 17 сомножителя, буферных блоков 12.1-12.q регистров по 13.1-13.Kpe50 5 0

5

0

с

0

5

0 5

гистра каждый, первый информационный вход 11 устройства, второй вход 18 синхронизации устройства (шина синхронизации).

Рассмотрим работу устройства в трех режимах.

В первом режиме производится вычисление суммы m-разрядныхМ слагаемых, при этом через вторую и третью информационные входы 14 и 16 записываются соответственно в первый 15 и второй 17 регистры сомножителей коды единиц, весовые выходы которых соответствующим образом соединены с третьими и четвертыми входами элементов И 3 третьей группы. Состояния первого и второго регистров 15 и 17 не изменяются на период работы устройства в режиме суммирования. Операнды слагаемых через первый информационный вход 11 записываются в регистры 13.1-13.К буферных блоков 12.1-12.q регистров. Сдвиг содержимого регистров 13.1-13.К буферных блоков 12.1-12.q регистров, начиная с младших разрядов, происходит одновременно по передним фронтам импульсов, которые поступают по R (Ri, I 1, q) шинам синхроимпульсов, причем RI шинз синхроим- пульсов состоит из L (Lj, j 1. К) линии синхронизации и соответствующим образом подключены к синхровходам регистров 13.1- 13.К i-ro блока буферных регистров. Одноименные разряды N слагаемых через элементы И 3 поступают на адресный вход блока 1 в течение сетки импульсов, которые поступают на шину 18 синхронизации устройства, гдемкоговходовым.элементом ИЛИ 19 и элементом 20 задержки достигается синхронизация подаваемого среза. Считанное из блока 1 слово является частью ассоциативного признака для ассоциативного запоминающего блока 2, причем все разряды, кро.ме младшего, задерживаются на один такт. Остальной частью признака являются все, кроме первого, разряды кода, считанного из блока 2 и задержанные на один такт. Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи импульса на вход 10 синхронизации. Такая синхронизация исключает влияние неидеальности элементов 7 и 8 задержки. На выходе 9 формируется очередной разряд суммы. При совместной работе блоков 1 и2на входы 10й 18 соответственно подаются по m импульсов, причем передний фронт сигнала входа 10 начинается позже, а задний раньше сетки импульсов, подаваемого на вход 18. При работе только блока 2 на вход 10 дополнительно подаются log2N импульсов. На входы 10 и 18 поступают импульсы, синхронизированные единой тактовой частотой. Общее число такто в вычисления суммы равно: t m + pog2N.

Во втором режиме производится одновременное вычисление произведения операндов разрядностью m 4, К 3 м q - 3 соответственно. Первый операнд разрядностью m 4 по первому информационному входу 11 устройства, младшими разрядами вперед, записываются в регистры 13.1-13.3 буферных блоков 12.1-12.3 в соответствии их физических связей,

В первый регистр 15 сомножителей записывается через второй информационный вход 14 устройства второй операнд разрядностью К 3. Во второй регистр 17 сомножителя записывается через третий информационный вход 16 устройства третий операнд разрядностью q 3. Состояние первого и второго 15 и 17 регистров сохраняются на весь период выполнения устройством второго режима работы устройства.

Весовые выходы регистра 15 подключены к соответствующим тертьим входам, физически образованных i - х подгрупп элементов И 3 третьей группы, начиная с младшего разряда.

Весовые выходы регистра 17 подключены, начиная с младшего разряда, к соответствующим объединенным входам 1-й подгруппы элементов И 3 третьей группы, причем элементы И 3 третьей группы обье- динены в 1-й подгруппе по четвертым входам. На синхровход j-го регистра 1-го буферного блока регистров по одноименной j-й линии 1-й шины синхроимпульсов подается m импульсов, причем импульс подаваемый на синхровход j-И-го регистра 1-го буферного блока регистров задержан на один такт относительно j-ro регистра того же блока, а каждый импульс подаваемый на j-й регистр i+1-ro буферного блока регистров задержан на один такт относительно 1-го буферного блока регистров. В результате такого последовательного-упорядоченного сдвига регистров 13.1-13.К буферных блоков 12.1-12.q регистров, начиная с младших разрядов, по передним фронтам сетки импульсов, которые поступают по R шинам синхроимпульсов через вход 18 образуется пространственно-временной массив условных частных произведений трех операндов. Нулевое разряды кодов второго и третьего сомножителя через соответствующие весовые выходы регистров 15 и 17 и физически обусловленные связи с элементами 1Л 3 третьей группы, маскируют пространственно-временной массив условных частных произведений трех операндов. В порядке упорядоченного сдвига регистров в

каждом такте работы устройства срез условных частных произведний через элементы И 3 поступают на адресный вход блока 1 в течение сетки импульсов по входу 18 того же

такта. Считанное из блока 1 слово является частью признака ассоциативного опроса запоминающего блока 2, причем все разряды, кроме младшего, задерживаются на один такт. Остальной частью признака опроса ялвяются все, кроме первого, разряды кода считанного из блока 2 и задержанные на один такт. Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи импульса на вход 10

синхронизации. На выходе 9 устройства в каждом такте работы устройства формируется очередной разряд произведения трех операндов. При совместной работе блоков 1 и 2 на входы 18 и 10 соответственно подаготся

т.1п-(т + К- 1) + (q-1)

тактируемых импульсов, причем передний

фронт импульса входа 10 начинается позже, а задний фронт раньше сетки импульсов, подаваемого на входе 18.

При работе только блока 2 на вход 10 дополнительно подается г/1 (т + К + q) - ti

импульсов.

На входы 10 и 18 поступают импульсы и сетка импульсов сдвига синхронизированные единой частотой. Общее число тактов вычисления произведения трех операндов

равно ts m + К-ь q.

Пусть необходимо вычислить произведение следующих трех операндов: 11 х 5 х х7 - 385; 11 ю 10112:5ю - 1012; 7ю - 1112. Код операнда 1011 записываются по

первому информационному входу 11, младшими разрядами вперед, в регистры 13.1- 13.3 буферных блоков 12.1-12.3 регистров в соответствии их физических связей. В первый 15 и во второй 17 регистры сомножителей записываются коды 101 и 111 соответственно, О разряды весовых выходов которых маскируют срезы условных частных произведений трех операндов,

В течение первой сетки тактируемых

импульсов 10000000 по входу 18 синхронизации устройства на адресный вход блока 1, через соответствующие элементы И 3 третьей группы подается с выходов регистров 13.1-13.3 буферных блоков 12.1-12.3

регистров младший срез частных произведений, то есть адрес 100 000 000. Код адреса синхронизируется на элементах И 3 третьей группы синхроимпульсом, выраба- тывамый многовходовым элементом ИЛИ 19 и элементом задержки 20, что исключает

возможность неправильной выработки кода адреса По указанному адресу из блока 1 считывается слово 10000, младший разряд которого 1 без задержки подается на первый вход элемента И 4, а остальные 0000 через элементы 7 задержки - на соответствующие входы элементов И 5, К приходу первого импульса по первому входу 10 синхронизации устройства на все первые входы И 6, через элементы 8 задержки под- аготся нули.

Сформированный признак с выходов И 4, элементов И 5 и И 6 - 100000000 с приходом импульса по входу 10 синхронизации поступает на признаковые входы бло- ка 2. В первом такте работы устройства из блока 2 считывается слово 00001, первый разряд которого 1 является младшим разрядом произведения трех операндов.

В течение второй сетки тактируемых им- пульсов 110100000 на адресный вход блока 1 подается второй срез частных произведений 1001 00000. По указанному адресу из блока 1 считывается слово OOOOV1. По приходу второго импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово 000000000, по которому из блока 2 считывается слово 00000 первый разряд которого О является вторым разрядом произведения трех операндов.

В течение третьей сетки импульсов 11111 0100 на даресный вход блока 1 подается третий срез частных произведений 00 11 001 OQ. По указанному адресу из блока 1 считывается слово 10001. По приходу третьего импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово 1,0001.0000. по которому из блока 2 считывается слово 10000 пер- вый разряд которого О является третьим разрядом произведения.

В течение четвертой сетки импульсов 111111110 на адресный вход блока 1 подается четвертый срез частных произведе- ний 101 00 11 00, по которому из блока 1 считывается слово 00011. По приходу четвертого импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово О 000 11 000, по которому считыва- ется слово 10000, первый разряд которого О является четвертым разрядом произве- дения трех операндов.

В течение пятой сетки импульсов 011111111 на адресный вход блока 1 пода- ется пятый срез частных произведений 000101001, по которому из блока 1 считывается слово 10001. По приходу пятого импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово

100111000, по которому считывается слово 11000, первый разряд которого О является пятым разрядом произведения трех операндов

В течение шестой сетки импульсов 001011111 на адресный вход блока 1 подается шестой срез частных произведений 001 000 101, по которому из блока 1 считывается слово 10001. По приходу шестого импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово 100011100, по которому считывается слово 11000, первый разряд которого О является шестым разрядом произведения.

В течение седьмой сетки импульсов 00000 1011 на адресный вход блока 1 подается седьмой срез частных произведений 000001000, по которому из блока 1 считывается слово 10000. По приходу седьмого импульса на вход 10 синхронизации на признаковые входы блока 2 поступает слово 100011100, по которому считывается слово 11000 первый разряд которого О является седьмым разрядом произведения,

В течение восьмой сетки импульсов 0000 00001 на адресный вход блока 1 подается восьмой срез частных произведений 000000001, по которому из блока 1 считывается слово 10000. По приходу восьмого импульса, на вход 10 синхронизации на признаковые входы блока 2 поступает слово 10000 1100, по которому считывается слово 10001, первый разряд которого 1 является восьмым разрядом произведения трех операндов.

Так как содержимое регистров буферных блоков выбрано, согласно tin (m + К+ + 1) + (q - 1) 8, подачи сетки синхроимпульсов прерывается, а выходы блока 1 воспринимаются в признаковой части блока 2 нулями, в последующих тактах работы устройства.

По приходу девятого импульса по входу 10 синхронизации по признаковые входы блока 2 поступает слово 000001000, по которому из блока 2 считывается слово 00001, первый разряд которого 1 является девятым разрядом произведения.

По приходу десятого импульса по входу 10 синхронизации на признаковые входы блока 2 поступает слово 000000000, по которому из блока 2 ситывается слово 00000, первый разряд которого О явлп- ется, согласно t3n m + K + q 10, последним разрядом произведения трех операндов. Код произведения трех операндов при этом равен 011 000 0001 385ю

В третьем режиме работы устройства

выполянется операция вида Р У ак В mi.

i -1

(где эк - постоянный коэффициент разрядностью К, В (Bim, I 1, q) - операнды разрядностью т.

Через магистральные информационные входы буферных блоков 12.1-12.q регистров записывается по одному операнду во все регистры 13,1-13.К, соответствующих буферных блоков, младшими разрядами вперед. В первый 15 регистр сомножителя записывается соответствующий код постоянного коэффициента. Во второй 17 регистр сомножителя записывается код единиц. В этом режиме работы устройства в операции маскирования условных частных произведений весовые выходы регистра 17 сомножителя не принимают. Состояние первого и второго 15 и 17 регистров сохраняются на весь период выполнения устройством третьего режима работы устройства. На каждый синхровход j-ro регистра 1-го буферного блока регистров по одноименной j-й линии 1-й шины синхроимпульсов подаются по m импульсов, причем; подава- емый на синхровход j + 1-го регистра задержан на один такт относительно -го регистра того же буферного блока, В результате такого последовательно-упорядоченного сдвига регистров 13.1-13.К буферных блоков 12,1-12.q регистров, начиная с младших разрядов, по передним фронтам сетки импульсов, которые поступают по R шинам синхроимпульсов-через вход 18 образуется пространственно-временной массив условных частных, произведений

операции вида Р У ак Bim.

i 1

Нулевые разряды кода ак через соответствующие весовые выходы регистра 15 сомножителя и физически обусловленные связи с элементами И 3 третьей группы маскируют пространственно-временной массив условных частных произведений операции Р. В порядке упорядоченного сдвига регистров в каждом такте работы устройства срез условных частных произведений через элементы И 3 поступают на адресный вход блока 1 в течении сетки импульсов по входу 18 того же такта работы устройства. Считанное из блока 1 слово является частью признака ассоциативного опроса запоминающего блока 2 причем все разряды, кроме младшего, задерживаются на один такт. Остальной частью признака опроса являются все, кроме первого, разряды кода считанного из блкоа 2 и задержан- ные на один такт. Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи импульса на вход 10 синхронизации На выходе 9 устройства в каждом такте работы устройства формируется очередной разряд операции

вида Р 2) ак Bim.

I 1

При совместной работе блоков 1 и 2 на входы 18 и 10 соответственно подаются

tion m + K-1

тактируемых импульсов, причем передний фронт импульса входа 10 начинается позже, а задний фронт раньше сетки импульсов подаваемого на вход 18. При работе только

блока 2 на вход 10 дополнительно подаются t2° гзоп - tion импульсов. На входы 10 и 18 поступают импульсы и сетка импульсов сдвига синхронизированные единой частотой. Общее число тактов вычисления операции Р равно

t3on (m + K+1) + log2K xq.

Пусть необходимо, исходя из аппарата ориентированных ресурсов устройства, выполнить операцию

Р (Bim ак + В2го ак + Взт ак) (15ю 5io+11io 5io+13io 5ю)195ю,

где Bim 15ю 11112, Ват 11 ю 10112, Взт 13ю 11012 разрядностью m 4; ак - 5ю - 1012, разрядностью К 3.

Код первого операнда Bim записываегся младшими разрядами вперед, в регистры 13.1-13.3 буферного блока 12.1 регистров. Код второго операнда В2т записывается в регистры 13.1-13.3 буферного блока регистров. Код третьего операнда Взт записывается в регистры 13.1-13.3 буферного блока 12.3 регистров. В первый регистр 15 сомножителя записывается код ак. О разряды весовых выходов которого маскируют срезы условных частных произведений операции Р, Во второй регистр 17 сомножителя записывается единичный код, весове выходы которого в этом режиме в операции маскирования не принимают.

В течение первой сетки тактируемых

импульсов 100 100 100 на адресный вход блока 1 через соответствующие элементы И 3 третьей группы, где выполняется операция маскирования, подается с выходов регистров 13.1-13,3 буферных блоков

12.1-12.3 регистров младший срез частных произведений, то есть адрес 100.100.100. По указанному адресу из блока 1 считывается слово 10001, младший разряд которого 1 без задержки подается на первый вход элемента И 4, а остальные 0000 через элементы 7 задержки - на соответствующие входы элементов И 5. К приходу первого импульса по первому входу 10 синхронизации устройства через элементы 8 задержки подаются нули. Сформированный признак с выходов И 4, И5иИ6- 100000000 с приходом импульса по входу 10 синхронизации поступает на признаковые входы блока 2. В первом такте работы устройства из блока 2 считывается слово 00001, первый разряд которого 1 является младшим разрядом выполянемой операции Р.

В течение второй сетки тактируемых импульсов 110110110 на адресный вход блока 1 подается второй срез 100 100 000, по которому считывается слово 00001. На признаковые входы блока 2 поступает слово 00001 0000, по которому считывается слово 00001, первый разряд которого 1 является вторым разрядом операции Р.

В течение третьей сетки тактируемых импульсов 111 111 111 на адресный вход блока 1 подается третий срез 101 000 101, по которому считывается слово 10011 . На признаковые входы блока 2 поступает слово 10001 0000, по которому считывается слово 10000, первый разряд О которого является третьим разрядом операции Р.

В течение четвертой сетки импульсов 111 111 111 на адресный вход блока 1 подается четвертый срез 101 101 001, по которому считывается слово 10011. На признаковые входы блока 2 поступает слово 10011 1000, по которому считывается слово 11000, первый разряд О которого яв- ляется четвертым разрядом операции Р.

В течение пятой сетки импульсов 011 011011 на адресный вход блока 1 подается пятый срез 001 000 001, по которому считывается слово- 00001 На признаковые входы 2 поступает слово 000111100, по которому считывается слово 11000, первый разряд О которого является г(ятым разрядом операции Р.

В течение шестой сетки импульсов 001 001 001 на адресный вход блока 1 подается шестой срез 001 001 001, по которому считывается слово 10001 На признаковые входы блока 2 поступает слово 100011100, по которому считывается слово 11000, первый разряд О которого является шестым разрядом операции Р. Так как содержимое регистров буферных блоков выбрано, согласно tion m + К - 1 6, подача сетки синхроимпульсов прерывается, а выходы блока 1 воспринимаются в признаковой ча-- сти блока 2 нулями в последующих тактах работы устройства.

По приходу седьмого импучьса по входу 10 синхронизации на признаковые входы

блока 2 поступает слово 000011100, по которому считывается слово 10001, первый разряд 1 которого является седьмым разрядом операции Р.

По приходу восьмого импульса по входу 10 на признаковые входы блока 2 поступает слово 000 001 000, по которому считывается слово 00001, первый разряд 1 которого является восьмым разрядом операции Р.

По приходу девятого импульса по входу 10 синхронизации на признаковые входы блока 2 поступает слово 000 000 000, по которому считывается слово 00000, первый разряд которого О является согласно t3on (m + К - 1) + IQQ2K x q 9, последним разрядом операции Р (Bim ак - +В2т ак + Взт ак). Код операции при этом равен 011 0000 112 195ю.

Техническое преимущество изобретения, по сравнению с известным состоит в расширении функциональных возможностей за счет дополнительного выполнения операции одновременного умножения трех сомножителей и операции вида

Р /L ак Положительный эффект

заключается в совмещении в одном устройстве выполнения нескольких операций и в более полном использовании аппаратно-зл- горитмических ресурсов устройства, кроме того параллельная обработка разрядных срезов частных произведений за счет организации операции маскирования разрядами сомножителей приводит к уменьшению стоимости машинной операции умножения я быстродействующих процессорах обработки данных.

Формула изобретения Вычислительное устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, элемент И, три группы элементов И, две группы элементов задержки, причем выход уст- ройства соединен с выходом первого разряда ассоциативного запоминающего блока, ЁЫХОДЫ остальных разрядов которого через элементы задержки первой группы соединены с первыми входами элементов И первой группы, вторые входы которых соединены с первым входом синхронизации устройства, с первыми входами элементов И второй группы и первым входом элемента И, второй сход которого соединен с выходом младшего разряда постоянного запоминающего блока, выходы старших разрядов которого через элементы задержки второй группы соединены с вторыми входами элементов И второй группы, выходы элемента И и элементов И второй и первой гр/ппы

соединены с входами опроса первой, второй и третьей групп соответственно ассоциативного запоминающего блока, адресные входы постоянного запоминающего блока соединены с выходами элементов И третьей группы, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления произведения трех величин и выполнения операции

вида Р У ак Bim, (где В Brm, 1 1,9)

1 1

операнды разрядностью т, ак - постоянная величина разрядностью К), устройство содержит первый регистр разрядности К, второй регистр разрядности q N/K, где N - количество одновременно суммируемых операндов, q буферных блоков регистров по К регистров каждый, элементы задержки и элементы ИЛИ, R-входов которого соединены с шиной синхронизации, выход элемента через элемент задержки соединен с первыми входами элементов И третьей группы,

с.инхровходНо регистра, где 1К, 1-го

буферного блока регистров соединен с J-n выходом 1-ой шины синхронизации устройства, первые информационные входы которого соединены с информационными

входами соответствующих регистров Буферных блоков регистров, выходы которых соединены с вторыми входами соответствующих элементов И третьей группы, третьи и четвертые входы которых соединены с выходами

соответствующих разрядов первого и второго регистров соответственно, информа- цоипые входы которых соединены соответственно с вторым и третьим информационными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

Изобретение относится к области вычислительной техники и может быть использовано, в скалярных и векторных быстродействующих процессорах обработ1/7 ки цифровой информации. Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности выполнения операций вида: Р 2 ак im, одновремен( г ного умножения трех операндоа. Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, третью группу 3 элементов И, элемент И 4, вторую и первую группы 5,6 элементов Л, вторую группу 7 элементов задержки, первую группу 8 элементов задержки, выход 9, входы 10, 18 синхронизации, информационные входы 11, 14, 16, буферные блоки 12|-12q регистров 13, регистры 15, 17 со- множителей. 3 ил. ч 1W Ё Х| со 4 О CN Ю фиг, -I

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-08-01—Подача