Изобретение относится к цифровой ычислительной технике и может быть спользовано для проверки устойчивоси к сбоям программ ЦВМ, имеющих средства аппаратурного контроля и программную защиту от сбоев, организованную путем разбиения программ на онтролируемые участки, допускающие повторное исполнение после сбоя.

Цель изобретения - повышение быстродействия устройства.

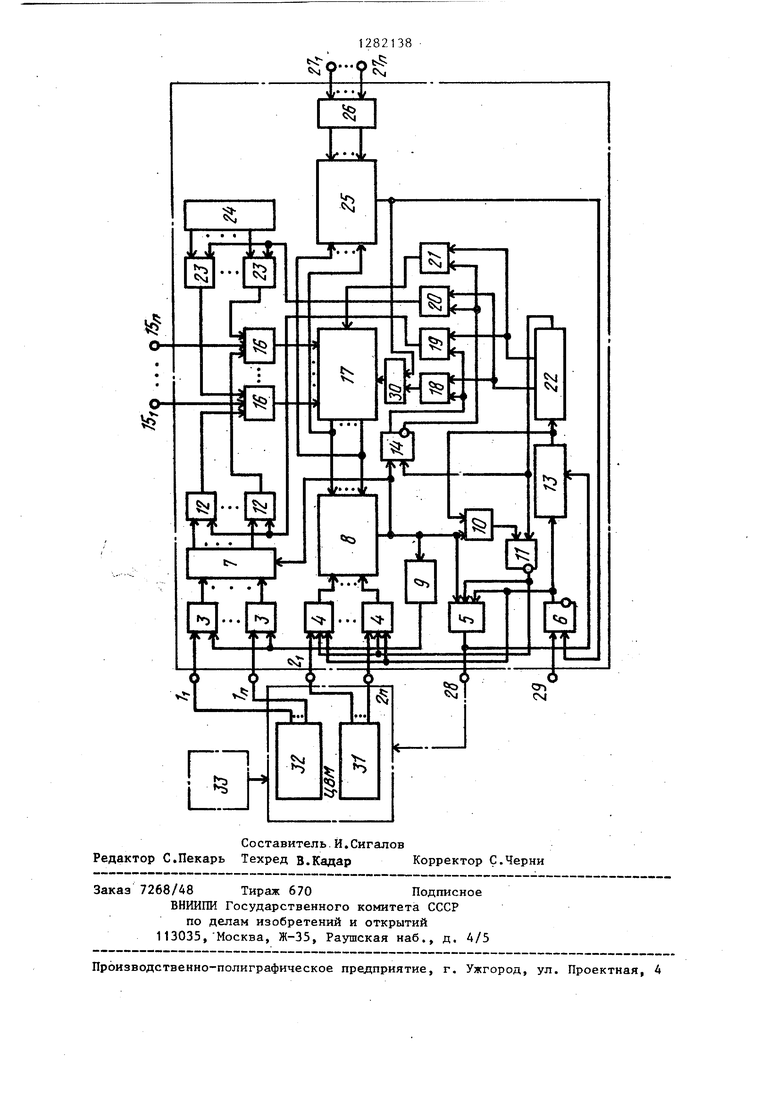

На чертеже представлена структурная -схема устройства для проверки программ на сбоеустойчивость.

Устроййтво содержит вторые адрес- ные входы 1.1-1.П, где п - разряд- ность адреса ЦВП, и первые адресные входы 2.1-2.П, третью группы злемен- тов И 3, первую группу злементовИ4, первьш элемент И 5, второй триггер 6, третий регистр 7, первую схему 8 сравнения, второй элемент 9 задержки, первый элемент ИЛИ 10, первьш триггер 11, четвертую группу элементов И 12, таймер 13, третий триггер 14, входы 15.1-15,п установки начального адреса устройства, группу элементов ИЛИ 16, сумматор 17, второй элемент И 18, третий элемент И 19, четвертый элемент И 20, пятыйоэле- мент И 21, первый элемент 22 задержки, вторую группу элементов И 23, второй регистр 24, вторую схему 25 сравнения, первый регистр 26, входы 27.1- 27.п установки конечного адреса устройства, выход 28 сбоя устройства, вход 29 пуска устройства, второй элемент ИЛИ 30.

Дополнительно изображены регистр 31 адреса команд ЦВМ, блок 32 формирования адреса команд ЦВМ, имитатор 33 входной информации. В исходном состоянии триггеры 6, 11 и 14 обнулены. Нулевой уровень с прямого выхода триггера 6 закрывает элементы И 4 и элемент И 5, а также блокирует работу таймера. Единичный уровень с инверсного выхода триггера 11 поступает на второй вход элемента И 5 и на третьи входы элементов И 4. Единичный уровень с инверсного выхода триггера 14 поступает на первые входы элементов И 20 и И 21, а нулевой уровень с прямого выхода триггера 14 закрывает элементы И 18 и И 19. Начальный адрес А программь, проверяемой на сбоеустойчивость, зано- .сится по входам 15.1-15.П на предва

рительно обнуленный сумматор 17, а конечный, в качестве которого выбирается адрес первой команды, выходящей за пределы программы А,

по входам 27.1-27.п - в предварительно обнуленный регистр 26. Настройка таймера 13 осуществляется в зависимости от соотношения периода запуска программ или периода запуска имитатора 33 входной информации Tj и интервала времени между сбоями на одном и том же контролируемом участке Тс , при котором программная защита от сбоев не классифицирует

их как отказ. Б случае, если , таймер настраивается на вьщачу налов через после его запуска, если же , то таймер настраивается на вьщачу сигналов через Ц Тпосле его запуска.(вход занесения соответствующего кОда константы в таймер 13 не показан). На регистр 24 заносится код шага сбоя (входы за- несения не показаны), который равен минимально .возможной длине команды. в ЦВМ (предполагается, что остальные форматы команд ЦВМ кратны., минимально возможному фбрмату). Код А с разрядных выходов сумматора подается на вторые и первые входы схемы 8 сравнения и на первые входы схемы 25 сравнения, на вторые входы которой поступает .. с разрядных выходов регистра 26.

Запуск устройства осуществляется подачей сигнала на вход 29 запуска устройства, которьй переводит гер в единичное состояние. Единичный уровень с прямого выхода триггера 6 запускает таймер 13, поступает на третий вход элемента И 5 и на вторые входы элементов И 4, разрешай прохождение потенциального кода адреса команды с разрядных выходов регистра 31 адреса команд ЦВМ йе первые входы схемы 8 сравнения.

В случае совпадения кодов на первых и вторых входах схемы 8 сравнения последняя выдает сигнал, который

проходит через элемент И 5 на выход 28 сбоя устройства, объединяющийся с выходом схем аппаратурного контроля ЦВМ (не показан). Этот же сигнал переводит триггеры 14 и 11 (последНИИ через элемент ИЛИ 10) в единичное состояние, обнуляет регистр 7 и поступает на вход элемента 9 задержки. Сигнал с выхода элемента И 5

31

обнуляет счетчик таймера 13, синхронизируя его работу с. реальным периодам запуска программ. Нулевой уровен с инверсного выхода триггера 11 закрывает элемент И 5 и элементы И 4, Единичный уровень с прямого выхода триггера 14 поступает на первые входы элементов И 18 и ,19, а нулевой уровень с его инверсного выхода закрывает элементы И 20 и 21. Время задержки в элементе 9 задержки выбира ется достаточным для того, чтобы в блоке 32 формирования адреса команды ЦВМ успел сформироваться адрес следующей команды, код которого считы- вается через элементы И 3 импульсы

:С выхода элемента 9 задержки и заносится в регистр 7.

Через время Т после формирования сигнала на выходе 28 сбоя устройства таймер 13 формирует сигнал, который перезапускает таймер и подается на вход элемента 22 задержки, где задерживается на время перевода триг- гера 11 в единичное состояние, пос- ле чего с первого выхода элемента 22 задержки через элементы И 18 и ИЛИ 30 обнуляет сумматор. 17. Сигнал с второго выхода элемента 22 задержки (время задержки между первым и вторым выходом определяется временем переходных процессов сумматора 17.) через элемент И 20 поступает на вторые входы элементов И 12, считывая значение адреса очередной команды из регистра 7 в сумматор 17.

Задержа нньй на время считывания адреса очередной команды и на время срабатьюания схемы 25 сравнейия сигнал с третьего выхода элемента 22 задержки обнуляет триггеры 11 и 14.

В случае, если за время Т-г совпадения кодов на входах схемы 8 срав- яения не произошло, на выходе таймера 13 появляется сигнал, который пе- piesanycKaeT таймер, устанавливает триЬгер 11 в единичное состояние и поступает на вход элемента 22 задержки. Нулевой уровень с инверсного выхода триггера 11 закрывает эле- мент И 5 и элементы И 4, сигнал с первого выхода элемента 22 задержки проходит через элемент И 20 и используется для чтения шага сбоя на счетные входы сумматора 17, сигнал с вто рого выхода элемента 22 задержки проходит через элемент И 21 и используется для реализации переносов в сум38 4

маторе 17. СИГРШЛ с третьего выхода элемента 22 задержки переводит триггер 11 в нулевое состояние. В сумматоре 17, таким образом, в каждом периоде запуска таймера 13 увеличивается значение адреса имитации сбич на шаг сбоя.

При совпадении кодов на входах схемы 25 сравнения лоследняя вьщает сигнал, который обнуляет сумматор 17 и триггер 6, при этом нулевой уровень с прямого выхода последнего закрывает элемент И 5, элементы И 4, останавливает таймер 13 и устройство завершает проверку программ на сбое- устойчивость.

Для проведения проверки программ на сбоеустойчивость на одной ЦВМ с использованием предлагаемого устройства необходим имитатор 33 входной информации (его запуск достаточно просто сделать периодическим). Применение имитатора позволяет сравнить полученные результаты работы программы без подключенного устройства и с подключенным устройством проверки программ на сбоеустойчивость.

Проверка программ по реальной входной информации возможна при наличии двух ЦВМ, ведущих параллельную обработку поступающей информации, при этом к одной из них подключено предлагаемое устройство.

Кроме проведения покомайдной прО верки программы на сбоеустойчивость устройство позволяет проверить программы имитацией однократного сбоя

во время.выполнения меченой команды, что может быть обеспечено соответствующим заданием Aj иА,; при настройке таймера 13 на время выполнения проверяемой программы.

Формула изобретения

Устройство для проверки программы на сбоеустойчивость, содержащее первый элемент И, первый элемент ИЛИ, первый и второй триггеры, первую и вторую схемы сравнения, первый и второй регистры, первую и вторую группы элементов И, -группу элементов ИЛИ, сумматор, первый элемент задержки и таймер, причем входы первой группы адресных входов устройства соединены с первыми входами элементов И перой группы, выходы элементов И первой группы соединены с первой груп

51

пой информационных входов первой схемы сравнения, выход равнозтшчности которой соединен с первыми входами первого элемента И и первого элемента ИЛИ, вькод которого соединен с еди ничным входом.первого триггера, инверсный выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с входом записи таймера и является вьссодом сбоя устройства, группа выходов сумматора соединена с второй группой входов первой схемы сравнения и с первой группой входов второй схемы сравнения, выход равенства которой соединен, с нулевым входом второго Триггера, группа входов установки конечного адреса .устройства соединена с группой информационных входов первого регистра, группа инфор- мационных выходов которого соединена с второй группой информационных входов второй схемы сравнения, вход пуска устройства соединен с единичным входом второго триггера, прямой вьпсод которого соединен с третьим входом первого элемента И, вторыми входами элементов И первой группы и входом запуска таймера, выход окончания временного интервала которого соединен с вторым входом первого элемента ИЛИ и с входом первого элемента задержки, группа входов установки начального адреса устройства соединена с первыми входами элементов ИЛИ группы, выходы которых соединены с соответствующими входами группы информационных входов сумматора, информационные выходы второго регистра соединены с первыми входами соответ ствующих элементов И второй группы, выходы элементов И второй группы соединены с вторыми входами соответствующих элеме«тов ИЛИ группы, первый выход Первого элемента задержки соединен с нулевьм входом первого триггера, отличающееся тем, что, с целью повышения быстро

р

f5

2821

- 5 35 45

25

30

40

386

действия, в него введены третья и четвертая группы элементов И, третий регистр, второй элемент задержки, третий триггер, второй, третий,четвертый, пятый элементы И, второй элемент ИЛИ, причем входы второй группы адресных входов устройства соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с информационными входами третьего регистра, информационные выходы третьего регистра соединены с первыми входами соответствующих элементов И четвертой группы, выходы которьк Соединены с третьими входами соответствующих элементов ШШ Группы, вь1ход равнозначности первой схемы сравнения соединен с единичным входом третьего триггера, с нулевым входом третьего регистра и через второй элемент задержки - с вторыми входами элементов И третьей группы, единичный выход третьего триггера соединен с первыми входами . третьего и четвертого элементов И, выходы которых соединены соответственно с первым входом второго элемента ИЛИ и вторыми входами элементов И четвертой группы, нулевой выход третьего триггера сое.динен с первыми входами четвертого и пятого элементов И, выходы которых соединены соответственно с вторыми входами элементов И второй группы и с входом переноса сумматора второй выход первого элемента задержки соединен с вторыми входами, второго и четвертого элементов И, третий выход первого элемента задержки соединен с вторыми входами третьего и пятого элементов И, первьй выход первого элемента задержки соединён с нулевым входом третьего триггера, инверсный выход первого триггера, выход равнозначности второй схемы сравнения соединен с вторым входомвторо- то элемента ИЛИ, выход которого соединен с входом установки нуля сумматора.

«

1282138

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки программ на сбое устойчивость | 1984 |

|

SU1205148A1 |

| Устройство для проверки программ на сбоеустойчивость | 1986 |

|

SU1411753A2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

| Устройство для сопряжения двухмашинной вычислительной системы | 1982 |

|

SU1075250A1 |

| Таймер | 1985 |

|

SU1357939A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки устойчивости к сбоям программ ЦВМ, имеющим средства аппаратурного контроля и программную защиту от сбоев, орга-. низованную путем разбиения программ на контролируемые участки, допускающие повторное исполнение после сбоя. Цель изобретения - повьшение быстродействия устройства. Устройство имитирует сигнал сбоя при совпадении со- держимого регистра адреса команд ЦВМ с адресом меченной команды. Период имитации сигнала сбоя задается таймером. Изменение адреса меченной команды производится; при совпадении регистра адреса команд ЦВМ с адресом меченной команды - замененной на значение адреса , очередной команды, выбираемого из блока формирования ад- . ре са команд ЦВМ; при несовпадении содержимого регистра адреса команд ЦВМ с адресом меченной команды - добавлением к предыдущему адресу шага сбоя, равного минимально возможной длине команды конкретной ЦВМ. Устройство содержит регистр, сумматор, схемы сравнения, таймер, элементы задержки, элементы И, ИЛИ. t ил. I сл Ю 00 ьэ

Q

o, . ..| t

f

Составитель.Й.Сигалов Редактор С.Пекарь Техред В.Кадар Корректор С.Черни

Заказ 7268/48 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

| Устройство для проверки программ на сбое устойчивость | 1984 |

|

SU1205148A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-06-21—Подача