Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки устойчивости к сбоям программ ЦВМ, имеющим средства аппаратурного конт роля и программную защиту от сбоев, организованную путем разбиения про грамм на контролируемые участки, допускающие повторное исполнение после сбоя.

Цель изобретения - расширение области применения устройства путем обеспечения возможности проверки циклических программ.

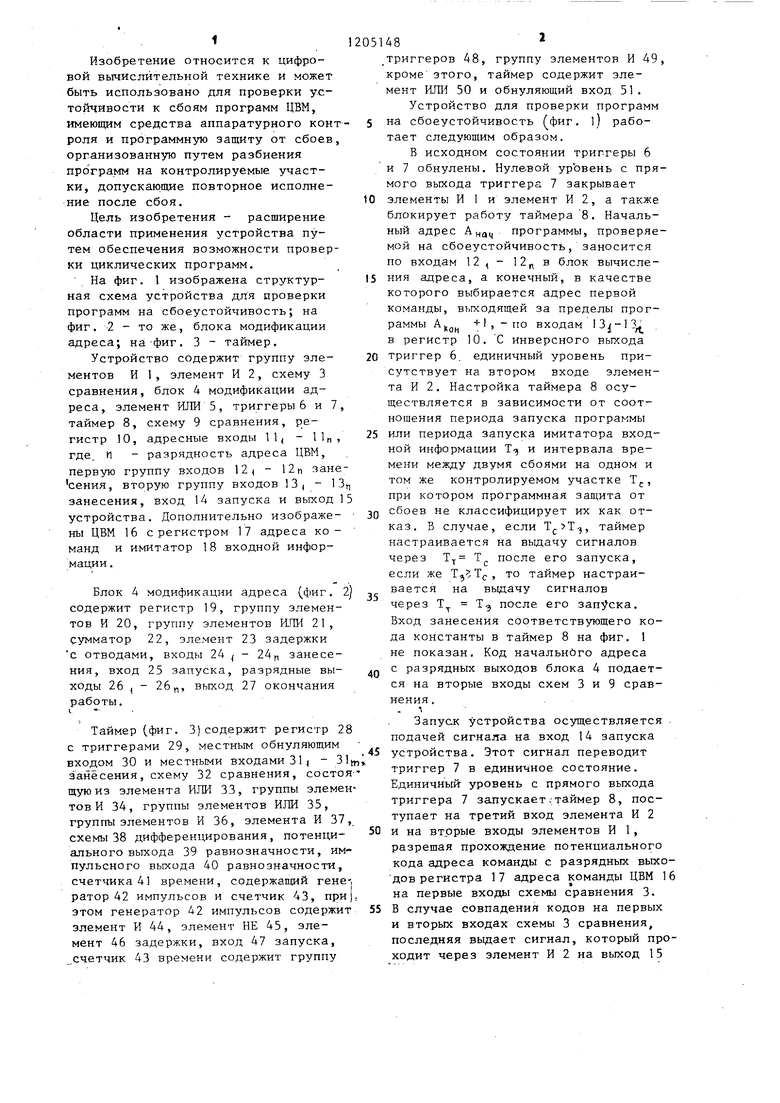

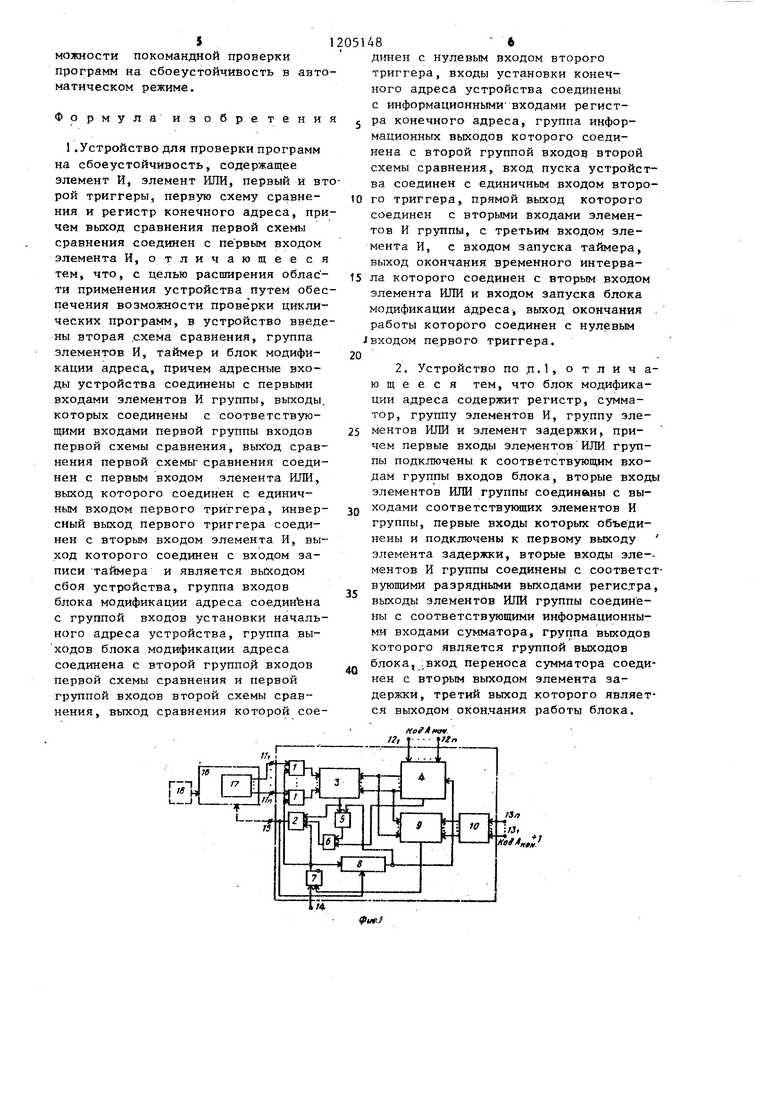

На фиг. 1 изображена структур- ная схема устройства для проверки программ на сбоеустойчивость; на фиг. -2 - то же, блока модификации адреса; на-фиг. 3 - таймер.

Устройство содержит группу эле- ментов И 1, элемент И 2, схему 3 сравнения, блок 4 модификации адреса, элемент ИЛИ 5, триггеры 6 и 7, таймер 8, схему 9 сравнения, регистр 10, адресные входы П, - „, где. И - разрядность адреса ЦВМ, первую группу входов 12( - 12ц зане сения, вторую группу входов 13, - 1 З занесения, вход 1А запуска и выход 1 устройства. Дополнительно изображе- ны ЦВМ 16 с регистром 17 адреса команд и имитатор 18 входной информации .

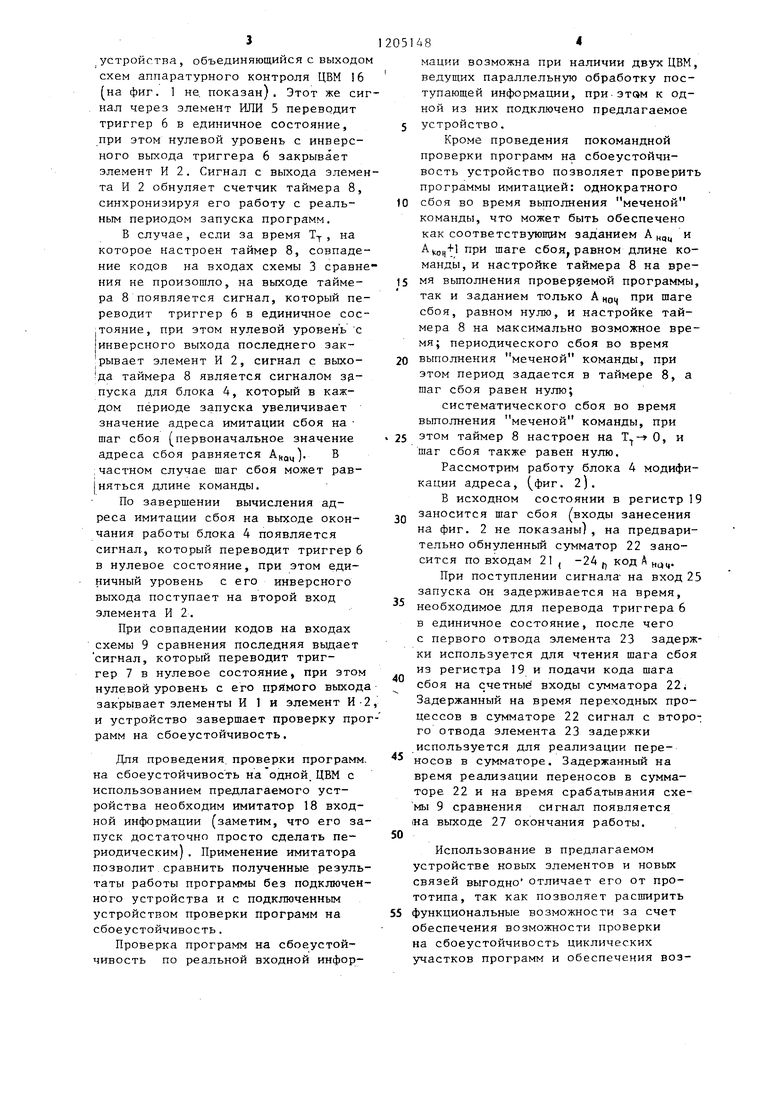

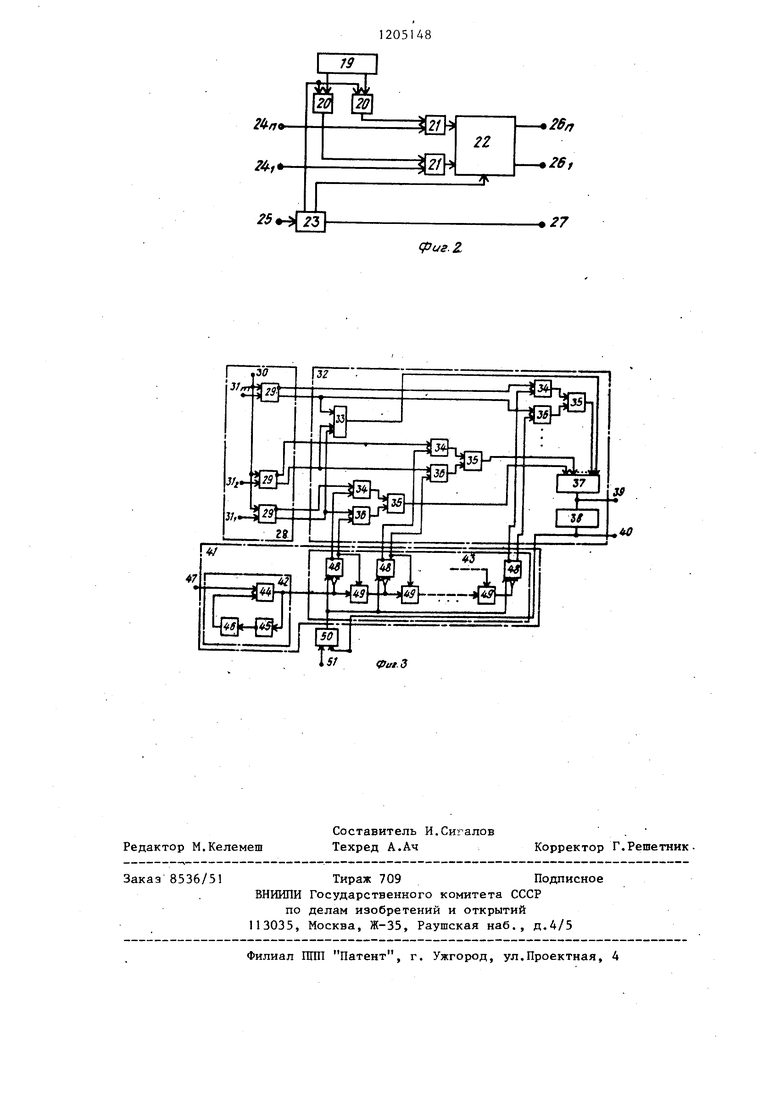

Блок 4 модификации адреса (фиг. содержит регистр 19, группу элементов И 20, группу элементов ИЛИ 21, сумматор 22, элемент 23 задержки с отводами, входы 24 ( - 24f, занесения, вход 25 запуска, разрядные вы- ходы 26 , - 26п, выход 27 окончания работы.

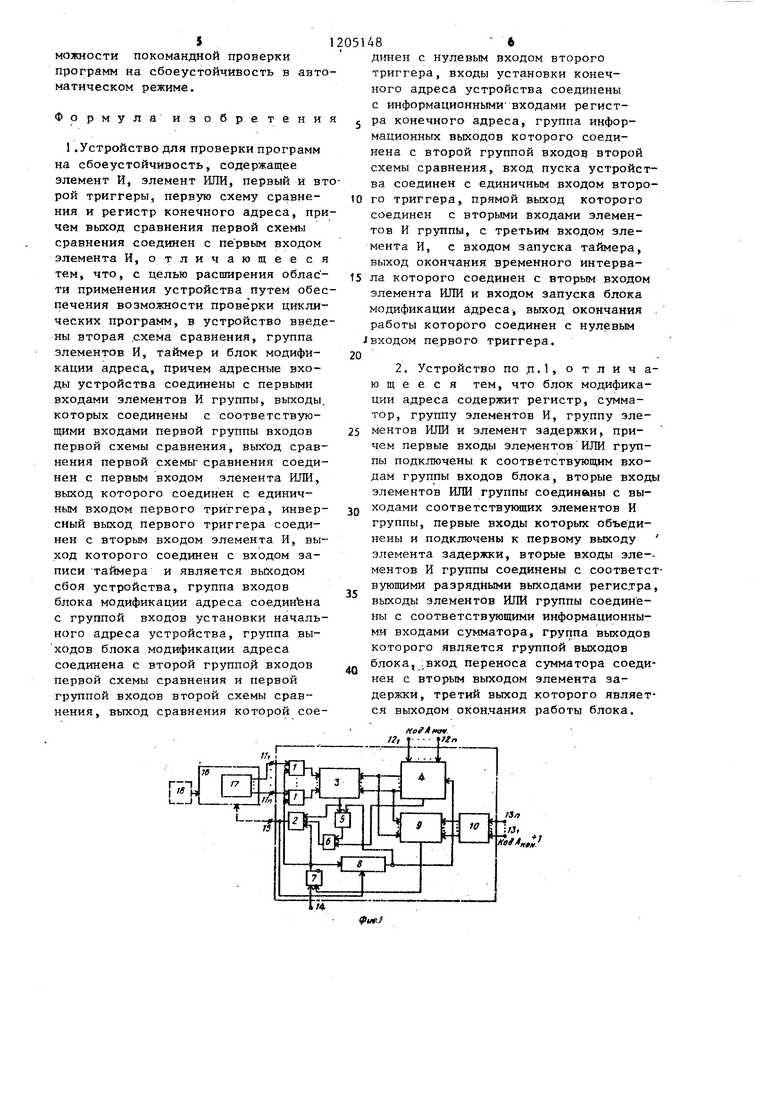

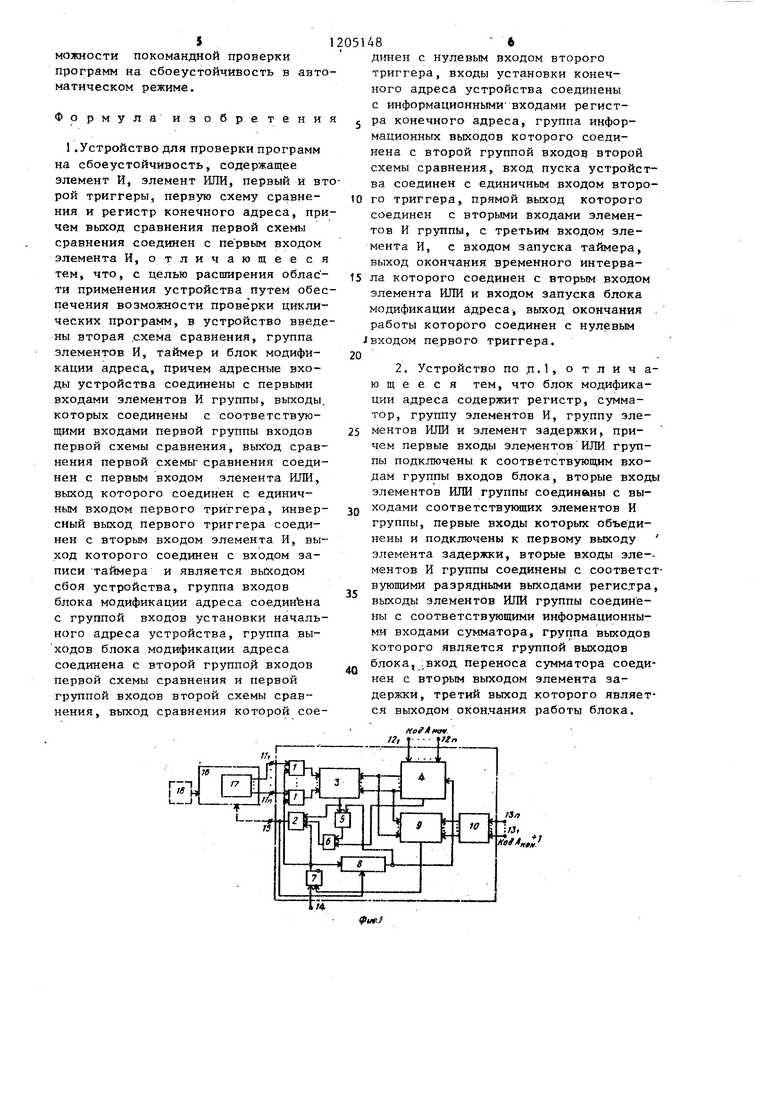

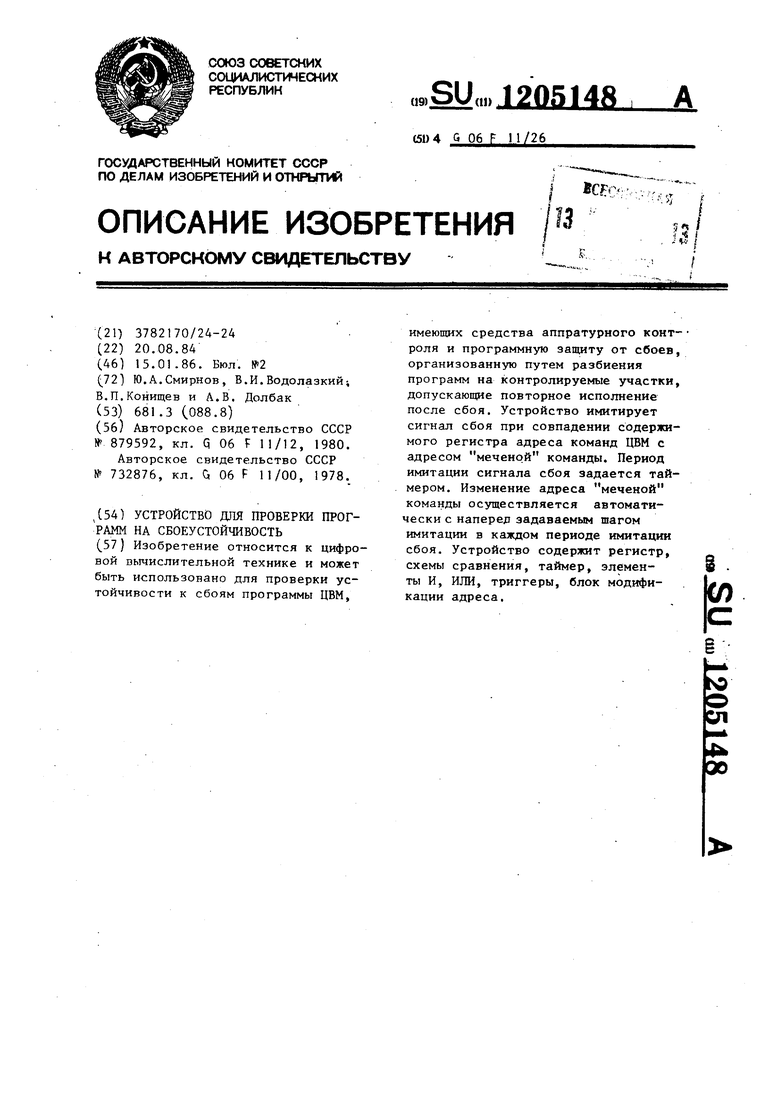

Таймер (фиг. 3)содержит регистр 28 с триггерами 29, местным обнуляющим входом 30 и местными входами 31 - 31, занесения, схему 32 сравнения, состоя-- щуюиз элемента ИЛИ 33, группы элементов И 34, группы элементов ИЛИ 35, группы элементов И 36, элемента И 37, схемы 38 дифференцирования, потенциального выхода 39 равнозначности, импульсного выхода 40 равнозначности, счетчика 41 времени, содержащий генератор 42 импульсов и счетчик 43, при ,. этом генератор 42 импульсов содержит элемент И 44, элемент НЕ 45, элемент 46 задержки, вход 47 запуска, счетчик 43 времени содержит группу

0

Q

5

0

5

48

триггеров 48, группу элементов И 49, кроме зтого, таймер содержит элемент ИЛИ 50 и обнуляющий вход 51.

Устройство для проверки программ на сбоеустойчивость (фиг. l) работает следующим образом.

В исходном состоянии триггеры 6 и 7 обнулены. Нулевой уровень с прямого вькода триггера 7 закрывает элементы И 1 и элемент И 2, а также блокирует работу таймера 8. Начальный адрес А нац. программы, проверяемой на сбоеустойчивость, заносится по входам 12 , - 12 в блок вычисления адреса, а конечный, в качестве которого выбирается адрес первой команды, выходящей за пределы программы Ацд , -по входам в регистр 10. С инверсного выхода триггер 6. единичный уровень присутствует на втором входе элемента И 2 . Настройка таймера 8 осуществляется в зависимости от соотношения периода запуска программы или периода запуска имитатора входной информации Т и интервала времени между двумя сбоями на одном и том же контролируемом участке Т, при котором программная защита от сбоев не классифицирует их как отказ. В случае, если , таймер настраивается на выдачу сигналов через Т Tj, после его запуска, если же , то таймер настраивается на вьщачу сигналов через Т Т после его запуска. Вход занесения соответствующего кода константы в таймер 8 на фиг. 1 не показан. Код начальнбго адреса с разрядных выходов блока 4 подается на вторые входы схем 3 и 9 сравнения .

Запуск устройства осуществляется подачей сигнала на вход 14 запуска устройства. Этот сигнал переводит триггер 7 в единичное состояние. Единичный уровень с прямого выхода триггера 7 залускаетгтаймер 8, поступает на третий вход элемента И 2 и на вторые входы элементов И 1, разрешая прохождение потенциального кода адреса команды с разрядных выхо- дов регистра 17 адреса команды ЦВМ 16 на первые входы схемы сравнения 3. В случае совпадения кодов на первых и вторых входах схемы 3 сравнения, последняя выдает сигнал, который проходит через элемент И 2 на выход 15

3

устройства, объединяющийся с выходом схем аппаратурного контроля ЦВМ 6 на фиг. 1 не. показан). Этот же сигнал через элемент ИЛИ 5 переводит триггер 6 в единичное состояние, при этом нулевой уровень с инверсного выхода триггера 6 закрывает элемент И 2. Сигнал с выхода элемента И 2 обнуляет счетчик таймера 8, синхронизируя его работу с реаль- ным периодом запуска программ.

В случае, если за время Т- , на которое настроен таймер 8, совпадение кодов на входах схемы 3 сравнения не произошло, на выходе тайме- ра 8 появляется сигнал, который переводит триггер 6 в единичное состояние, при этом нулевой уровень с инверсного выхода последнего закрывает элемент И 2, сигнал с выхо- да тайме-ра 8 является сигналом пуска для блока 4, который в каждом периоде запуска увеличивает значение адреса имитации сбоя на шаг сбоя (первоначальное значение адреса сбоя равняется ). В ; частном случае шаг сбоя может равняться длине команды.

По завершении вычисления адреса имитации сбоя на выходе окон- чания работы блока 4 появляется сигнал, который переводит триггер 6 в нулевое состояние, при этом единичный уровень с его инверсного выхода поступает на второй вход элемента И 2.

При совпадении кодов на входах схемы 9 сравнения последняя вьздает сигнал, который переводит триггер 7 в нулевое состояние, при этом нулевой уровень с его прямого выхода закрывает элементы И 1 и элемент И-2 и устройство завершает проверку прорамм на сбоеустойчивость.

Для проведения проверки программ. на сбоеустойчивость на одной. ЦВМ с использованием предлагаемого устройства необходим имитатор 18 входной информации (заметим, что его запуск достаточно просто сделать пе- риодическим). Применение имитатора позволит сравнить полученные результаты работы программы без подключенного устройства и с подключенным устройством проверки программ на сбоеустойчивость.

Проверка программ на сбоеустойчивость по реальной входной информации возможна при наличии двух ЦВМ ведущих параллельную обработку поступающей информации, при.этом к одной из них подключено предлагаемое устройство.

Кроме проведения покомандной проверки программ на сбоеустойчивость устройство позволяет проверит программы имитацией: однократного сбоя во время выполнения меченой команды, что может быть обеспечено как соответствующим заданием А и при шаге сбоя, равном длине команды, и настройке таймера 8 на время выполнения провердемой программы так и заданием только А цоц при шаге сбоя, равном нулю, и настройке таймера 8 на максимально возможное время; периодического сбоя во время выполнения меченой команды, при этом период задается в таймере 8, а шаг сбоя равен нулю;

систематического сбоя во время выполнения меченой команды, при этом таймер 8 настроен на Т.- О, и шаг сбоя также равен нулю.

Рассмотрим работу блока 4 модификации адреса, (фиг. 2).

В исходном состоянии в регистр 1 заносится шаг сбоя входы занесения на фиг. 2 не показаны, на предварительно обнуленньш сумматор 22 заносится по входам 21 , -24 код А .

При поступлении сигнала- на вход 2 запуска он задерживается на время, необходимое для перевода триггера 6 в единичное состояние, после чего с первого отвода элемента 23 задержки используется для чтения шага сбоя из регистра 19 и подачи кода шага сбоя на счетные входы сумматора 22; Задержанный на время переходных процессов в сумматоре 22 сигнал с второго отвода элемента 23 задержки используется для реализации переносов в сумматоре. Задержанный на время реализации переносов в сумматоре 22 и на время срабатывания схе- мы 9 сравнения сигнал появляется (на выходе 27 окончания работы.

Использование в предлагаемом устройстве новых элементов и новых связей выгодно отличает его от прототипа, так как позволяет расширить функциональные возможности за счет обеспечения возможности проверки на сбоеустойчивость циклических участков программ и обеспечения возможности покомандной проверки программ на сбоеустойчивость в автматическом режиме.

Формула изобретени

1 .Устройство для проверки программ на сбоеустойчивость, содержащее элемент И, элемент ИЛИ, первый и врой триггеры, первую схему сравнения и регистр конечного адреса, прчем выход сравнения первой схемы сравнения соединен с пе рвым входом элемента И, отличающее с тем, что, с целью расширения области применения устройства путем обе Г1ечения возможности проверки циклических программ, в устройство введны вторая схема сравнения, группа элементов И, таймер и блок модификации адреса,, причем адресные входы устройства соединены с первыми входами элементов И группы, выходы которых соединены с соответствующими входами первой группы входов первой схемы сравнения, вьисод сравнения первой схемы- сравнения соединен с первым входом элемента ИЛИ, выход которого соединен с единичным входом первого триггера, инверсный выход первого триггера соединен с вторым входом элемента И, выход которого соединен с входом записи таймера и является вьОсодом сбоя устройства, группа входов блока модификации адреса соедин%на с группой входов установки начального адреса устройства, группа выходов блока модификации адреса соединена с второй группой входов первой схемы сравнения и первой группой входов второй схемы сравнения, выход сравнения которой сое

динен

с нулевым входом второго триггера, входы установки конечного адреса устройства соединены с информационными- входами регист- 5 ра конечного адреса, группа информационных выходов которого соединена с второй группой входов второй схемы сравнения, вход пуска устройства соединен с единичным входом второ0 го триггера, прямой выход которого соединен с вторыми входами элементов И группы, с третьим входом элемента И, с входом запуска таймера, выход окончания временного интерва5 ла которого соединен с вторым входом элемента ИЛИ и входом запуска блока модификации адреса, выход окончания . работы которого соединен с нулевым входом первого триггера.

0

2. Устройство по д.1, о т л и ч а- ю щ е е с я тем, что блок модификации адреса содержит регистр, сумматор, группу элементов И, группу эле5 ментов ИЛИ и элемент задержки, причем первые входь элементов ИЛИ группы подключены к соответствующим входам группы входов блока, вторые входы элементов ИЛИ группы соединаны с выходами соответствующих элементов И группы, первые входы которых объединены и подключены к первому выходу элемента задержки, вторые входы эле-- ментов И группы соединены с соответствующими разрядными выходами регистра, выходы элементов ИЛИ группы соединены с соответствующими информационными входами сумматора, группа выходов которого является группой выходов блока,:вход переноса сумматора соединен с вторым выходом элемента задержки, третий выход которого является выходом окончания работы блока.

.

tf, t- rif.

0

5

J, t :; fy

. X TT I

I3a

-.a,

v,/x,;/

г/

2{)-п

24;

/Лг /5,

фиг. 2,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки программы на сбоеустойчивость | 1985 |

|

SU1282138A1 |

| Устройство для проверки программ на сбоеустойчивость | 1986 |

|

SU1411753A2 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для проверки полноты тестирования программ | 1987 |

|

SU1425686A1 |

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

| Устройство для восстановления информации цифровых вычислительных машин | 1982 |

|

SU1027728A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки устойчивости к сбоям программы ЦВМ, имеющих средства аппратурного конт- роля и программную защиту от сбоев, организованную путем разбиения программ на контролируемые участки, допускающие повторное исполнение после сбоя. Устройство имитирует сигнал сбоя при совпадении содержимого регистра адреса команд ЦВМ с адресом меченой команды. Период имитации сигнала сбоя задается таймером. Изменение адреса меченой команды осуществляется автоматически с наперед задаваемым щагом имитации в каждом периоде имитации сбоя. Устройство содержит регистр, схемы сравнения, таймер, элементы И, ИЛИ, триггеры, блок модификации адреса. g . W

Фм.З

Редактор М.Келемеш

Составитель И.Сигалов Техред А.Ач

Заказ 8536/51

Тираж 709Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-33, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул.Проектная, 4

Корректор Г.Решетник

| Устройство для имитации сбоев цифровых вычислительных машин | 1980 |

|

SU879592A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля правильности выполнения программ при сбоях | 1977 |

|

SU732876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-15—Публикация

1984-08-20—Подача