10

15

20

Изобретение относится к вычислительной технике и может быть использовано при исследовании сложных систем.

Целью изобретения является расширение функциональных возможностей за счет определения вероятности перехода системы с непрерывным временем изменения состояния в любое возможное состояние за заданное время.

Состояние системы отображается в виде графа, дугами которого являются вероятности перехода системы из одного состояния в другое.

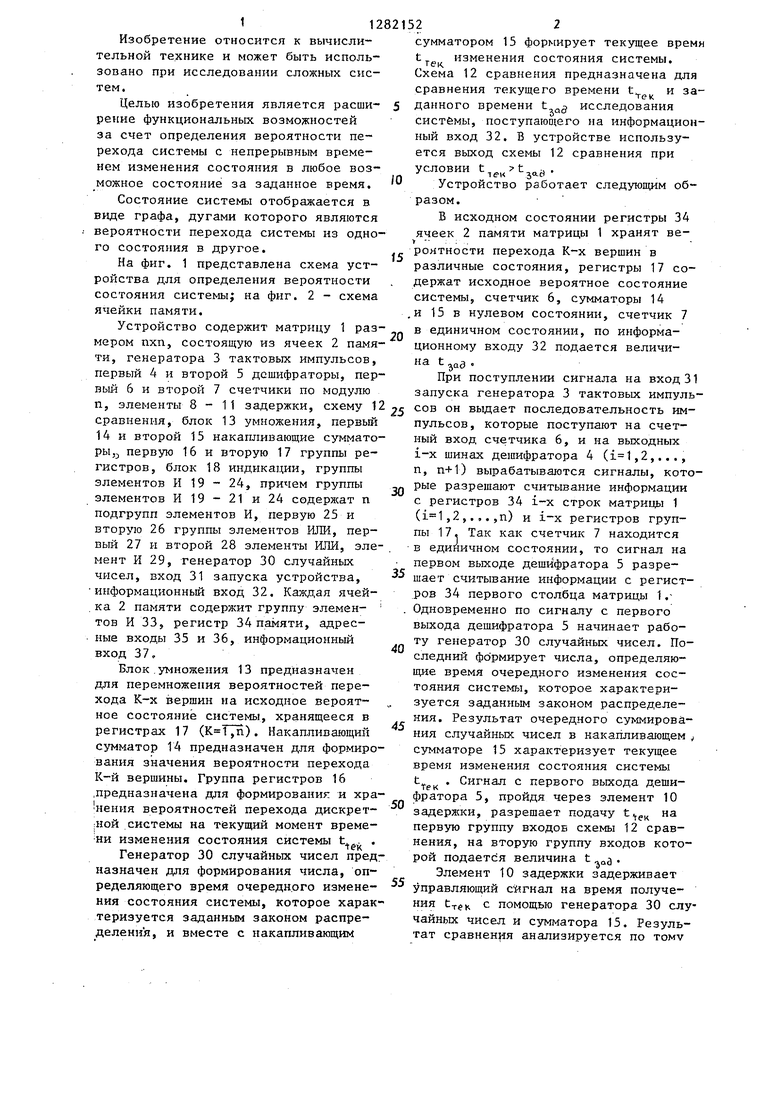

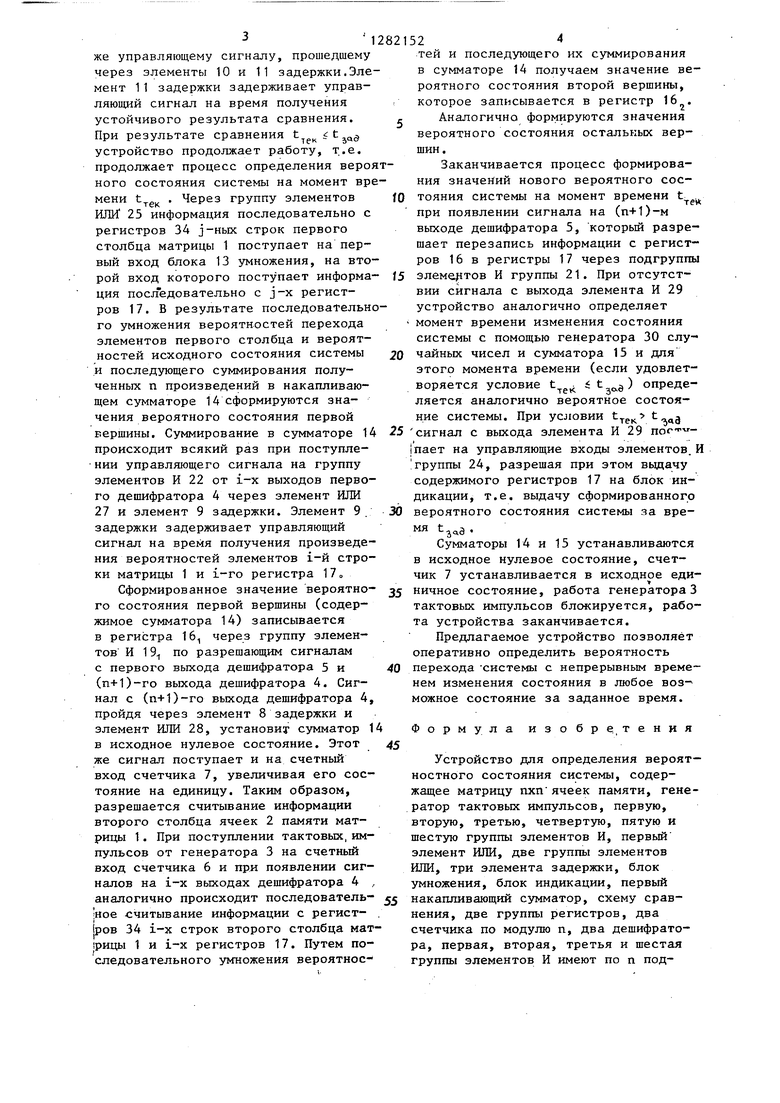

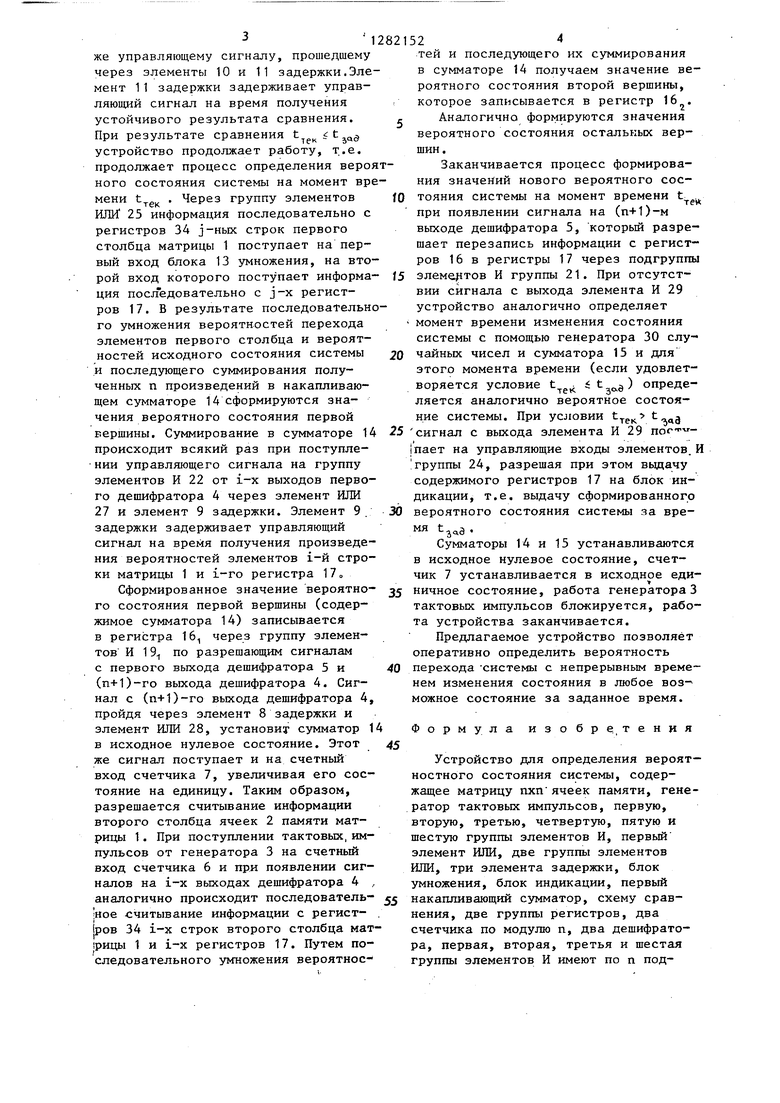

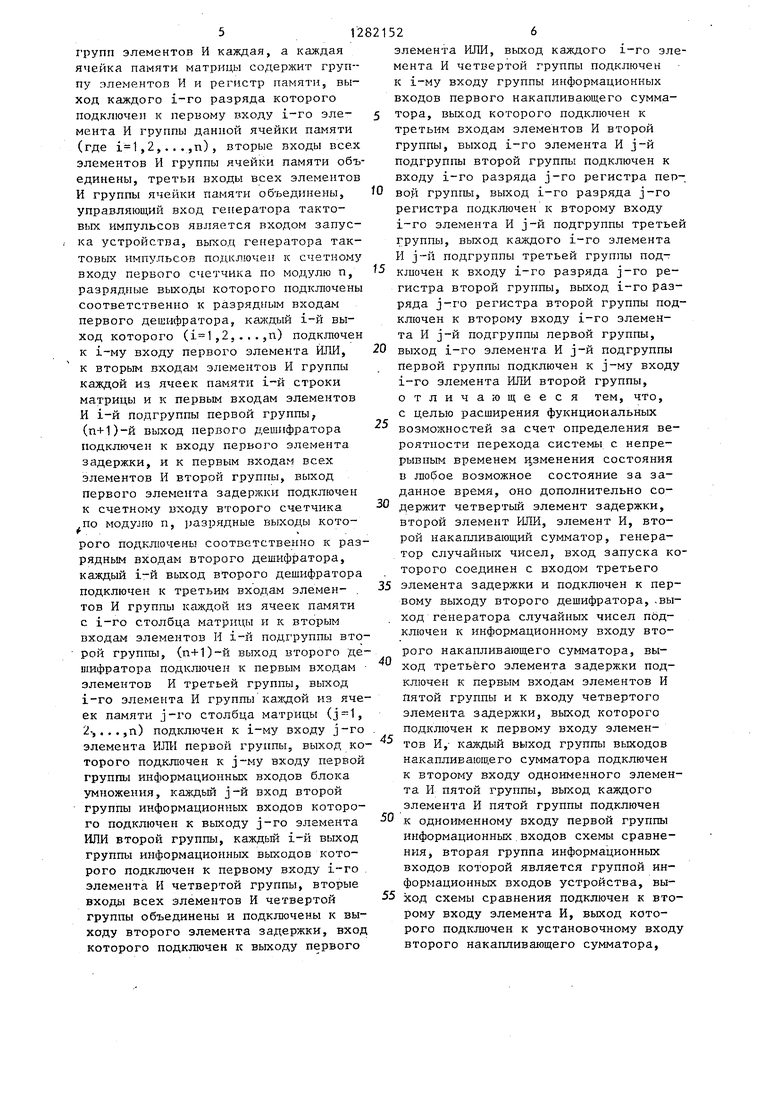

На фиг. 1 представлена схема устройства для определения вероятности состояния системы; на фиг. 2 - схема ячейки памяти.

Устройство содержит матрицу 1 размером пхп, состоящую из ячеек 2 памяти, генератора 3 тактовых импульсов, первый 4 и второй 5 дешифраторы, первый 6 и второй 7 счетчики по модулю п, элементы 8-11 задержки, схему 1225 сравнения, блок 13 умножения, первый 14 и второй 15 накапливающие сумматоры,,, первую 16 и вторую 17 группы регистров, блок 18 индикации, группы элементов И 19 - 24, причем группы элементов И 19 - 21 и 24 содержат п подгрупп элементов И, первую 25 и вторую 26 группы элементов ИЛИ, первый 27 и второй 28 элементы ИЛИ, элемент И 29, генератор 30 случайных чисел, вход 31 запуска устройства, информационный вход 32. Каждая ячей- . ка 2 памяти содержит группу элемен- тов И 33, регистр 34 памяти, адресные входы 35 и 36, информационный вход 37,

Блок.умножения 13 предназначен для перемножения вероятностей перехода К-х зершин на исходное вероятное состояние системы, хранящееся в регистрах 17 (,п). Накапливающий сумматор 14 предназначен для формирования значения вероятности перехода К-й вершины. Группа регистров 16 .предназначена для формирования и хра- нения вероятностей перехода дискрет- :ной системы на текущий момент време- ни изменения состояния системы Ц .

Генератор 30 случайных чисел предназначен для формирования числа, опсумматором 15 формирует текущее время

тек

изменения состояния системы.

Схема 12 сравнения предназначена для сравнения текущего времени t и заданного времени t исследования системы, поступающего на информационный вход 32. В устройстве используется выход схемы 12 сравнения при условии t,tj,.

Устройство работает следующим образом.

В исходном состоянии регистры 34 ячеек 2 памяти матрицы 1 хранят .

роятности перехода К-х вершин в различные состояния, регистры 17 содержат исходное вероятное состояние системы, счетчик 6, сумматоры 14 и 15 в нулевом состоянии, счетчик 7 в единичном состоянии, по информационному входу 32 подается величина t

jaa

30

При поступлении сигнала на вход 31 запуска генератора 3 тактовых импульсов он выдает последовательность импульсов, которые поступают на счетный вход счетчика 6, и на выходных i-x шинах дешифратора 4 (,2,..., п, п+1) вырабатываются сигналы, которые разрешают считывание информации с регистров 34 i-x строк матрицы 1 (,2,.,.,п) и 1-х регистров группы 17. Так как счетчик 7 находится в единичном состоянии, то сигнал на первом выходе деши фратора 5 разре- шает считывание информации с регистров 34 первого столбца матрицы 1 .- . Одновременно по сигналу с первого выхода дешифратора 5 начинает работу генератор 30 случайных чисел. Последний формирует числа, определяющие время очередного изменения состояния системы, которое характеризуется заданным законом распределения. Результат очередного суммирова,- ния случайных чисел в накапливающем сумматоре 15 характеризует текущее время изменения состояния системы t . Сигнал с первого выхода дешифратора 5, пройдя через элемент 10 задерлски, разрешает подачу t. на первую группу входов схемы 12 сравнения, на вторую группу входов которой подается величина t 3.

Элемент 10 задержки задерживает

40

45

ределяющего время очередного измене- управляющий сигнал на время получения состояния системы, которое харак- ния помощью генератора 30 слу- теризуется заданным законом распределения, и вместе с накапливающим

чайных чисел и сумматора 15. Результат сравнения анализируется по тому

сумматором 15 формирует текущее время

тек

изменения состояния системы.

Схема 12 сравнения предназначена для сравнения текущего времени t и заданного времени t исследования системы, поступающего на информационный вход 32. В устройстве используется выход схемы 12 сравнения при условии t,tj,.

Устройство работает следующим образом.

В исходном состоянии регистры 34 ячеек 2 памяти матрицы 1 хранят .

роятности перехода К-х вершин в различные состояния, регистры 17 содержат исходное вероятное состояние системы, счетчик 6, сумматоры 14 и 15 в нулевом состоянии, счетчик 7 в единичном состоянии, по информационному входу 32 подается величи5

на t

jaa

0

При поступлении сигнала на вход 31 запуска генератора 3 тактовых импульсов он выдает последовательность импульсов, которые поступают на счетный вход счетчика 6, и на выходных i-x шинах дешифратора 4 (,2,..., п, п+1) вырабатываются сигналы, которые разрешают считывание информации с регистров 34 i-x строк матрицы 1 (,2,.,.,п) и 1-х регистров группы 17. Так как счетчик 7 находится в единичном состоянии, то сигнал на первом выходе деши фратора 5 разре- шает считывание информации с регистров 34 первого столбца матрицы 1 .- . Одновременно по сигналу с первого выхода дешифратора 5 начинает работу генератор 30 случайных чисел. Последний формирует числа, определяющие время очередного изменения состояния системы, которое характеризуется заданным законом распределения. Результат очередного суммирова,- ния случайных чисел в накапливающем сумматоре 15 характеризует текущее время изменения состояния системы t . Сигнал с первого выхода дешифратора 5, пройдя через элемент 10 задерлски, разрешает подачу t. на первую группу входов схемы 12 сравнения, на вторую группу входов которой подается величина t 3.

Элемент 10 задержки задерживает

0

5

управляющий сигнал на время получения помощью генератора 30 слу-

управляющий сигнал на время получения помощью генератора 30 слу-

чайных чисел и сумматора 15. Результат сравнения анализируется по тому

же управляющему сигналу, прошедшему через элементы 10 и 11 задержки.Элемент 11 задержки задерживает управляющий сигнал на время получения устойчивого результата сравнения. При результате сравнения устройство продолжает работу, т.,е. продолжает процесс определения вероятного состояния системы на момент вре

мени . Через группу элементов ИЛИГ 25 информация последовательно с регистров 34 j-ных строк первого столбца матрицы 1 поступает на первый вход блока 13 умножения, на второй вход которого поступает информация посл едовательно с j-x регистров 17. В результате последовательнго умножения вероятностей перехода элементов первого столбца и вероятностей исходного состояния системы и последующего суммирования полученных п произведений в накапливающем сумматоре 14 сформируются значения вероятного состояния первой верщины. Суммирование в сумматоре 14 происходит всякий раз при поступлении управляющего сигнала на группу элементов И 22 от i-x выходов первого дешифратора 4 через элемент ИЛИ 27 и элемент 9 задержки. Элемент 9 задержки задерживает управляющий сигнал на время получения произведения вероятностей элементов i-й строки матрицы 1 и i-ro регистра 17„

Сформированное значение вероятного состояния первой вершины (содержимое сумматора 14) записывается в регистра 16 через группу элементов И 19 по разрешающим сигналам с первого выхода дешифратора 5 и (п+1)-го выхода дешифратора 4. Сигнал с (п+1)-го выхода дешифратора 4, пройдя через элемент 8 задержки и элемент ИЛИ 28, установит сумматор 1 в исходное нулевое состояние. Этот же сигнал поступает и на счетный вход счетчика 7, увеличивая его состояние на единицу. Таким образом, разрешается считывание информации второго столбца ячеек 2 памяти матрицы 1. При поступлении тактовых, импульсов от генератора 3 на счетный вход счетчика 6 и при появлении сигналов на i-x выходах дешифратора 4 , аналогично происходит последователь- «ое считывание информации с регист- Ьов 34 i-x строк второго столбца мат |рицы 1 и i-x регистров 17. Путем последовательного умножения вероятнос

теи и последующего их суммирования в сумматоре 14 получаем значение вероятного состояния второй вершины, которое записывается в регистр 16 .

O

5

0

0

те

Аналогично формируются значения вероятного состояния остальных вершин.

Заканчивается процесс формирования значений нового вероятного состояния системы на момент времени t при появлении сигнала на (п+1)-м выходе дешифратора 5, который разрешает перезапись информации с регистров 16 в регистры 17 через подгруппы элементов И группы 21. При отсутствии сигнала с выхода элемента И 29 устройство аналогично определяет момент времени изменения состояния системы с помощью генератора 30 случайных чисел и сумматора 15 и для этого момента времени (если удовлетворяется условие t i t g) определяется аналогично вероятное состояние системы. При условии -хаз 5 сигнал с выхода элемента И 29 |пает на управляющие входы элементов. И группы 24, разрешая при этом вьщачу содержимого регистров 17 на блок индикации, т.е. выдачу сформированного вероятного состояния системы за вре

мя t

аЭ

Сумматоры 14 и 15 устанавливаются в исходное нулевое состояние, счетчик 7 устанавливается в исходное единичное состояние, работа генератора 3 тактовых импульсов блокируется, работа устройства заканчивается.

Предлагаемое устройство позволяет оперативно определить вероятность

перехода системы с непрерывным временем изменения состояния в любое возможное состояние за заданное время.

Формула изобретения

Устройство для определения вероятностного состояния системы, содержащее матрицу пхп ячеек памяти, генератор тактовых импульсов, первую, вторую, третью, четвертую, пятую и шестую группы элементов И, первый элемент ИЛИ, две группы элементов ШШ, три элемента задержки, блок умножения, блок индикации, первый накапливающий сумматор, схему сравнения, две группы регистров, два счетчика по модулю п, два дешифратора, первая, вторая, третья и шестая группы элементов И имеют по п подгрупп элементов И каждая, а каждая ячейка памяти матрицы содержит группу злемеитоп И и регистр памяти, выход каждого i-ro разряда которого подключен к первому входу i-ro элемента И группы данной ячейки памяти (где ,2,...jn), вторые входы всех элементов И группы ячейки памяти объединены, третьи входы всех элементов И группы ячейки памяти объединены, управляющий вход генератора такто- вьк импульсов является входом запуска устройства, выход генератора тактовых импульсов подключен к счетному входу первого счетчика по модулю п, разрядные выходы которого подключены соответственно к разрядным входам первого дешифратора, каждый i-й выход которого (,2,,..,п) подключен к 1-му входу первого элемента ИЛИ, к вторым входа1 1 элементов И группы каждой из ячеек памяти 1-й строки матрицы и к первым входам элементов И 1-й подгруппы первой группы, (п+1)-й выход первого дешифратора подключен к входу первого элемента задержки, и к первым входам всех элементов И второй группы, выход первого элемента задержки подключен к счетному входу второго счетчика По модулю и, }азрядные выходы которого подключены соответственно к разрядным входам второго дешифратора, каждый 1-й выход второго дешифратора подключен к третьим входам элемен- . тон И группы каждой из ячеек памяти с 1-го столбца матрицы и к вторым входам элементов И 1-й подгруппы вто- рой группы, (п+1)-й выход второго дешифратора подклюхшн к первым входам элементов И третьей группы, выход 1-го элемента И группы каяздой из ячеек памяти j-ro столбца матрицы (, 2., ...,п) подключен к 1-му входу j-ro элемента ИЛИ первой группы, выход которого подключен к входу первой группы информационных входов блока умножения, каждый j-й вход второй группы информационных входов которого подключен к выходу j-ro элемента ИЛИ второй группы, каждьй 1-й выход группы информационных выходов которого подключен к первому входу 1-го элемента И четвертой группы, вторые входы всех элементов И четвертой группы объединены и подключены к выходу второго элемента задержки, вход которого подключен к выходу первого

5

0

5

элемента ИЛИ, выход каждого х-го элемента И четвертой группы подключен к 1-му входу группы информационных входов первого накапливающего сумматора, выход которого подключен к третьим входам элементов И второй группы, выход 1-го элемента И j-й подгруппы второй группы подключен к входу 1-го разряда j-ro регистра первой группы, выход 1-го разряда j-ro регистра подключен к второму входу 1-го элемента И j-й подгруппы третьей группы, выход каждого 1-го элемента И j-й подгруппы третьей группы под- к;иочен к входу 1-го разряда j-ro регистра второй группы, выход 1-го разряда j-ro регистра второй группы подключен к второму входу 1-го элемента И j-й подгруппы первой группы, выход 1-го элемента И j-й подгруппы первой группы подключен к j-му входу 1-го элемента ИЛИ второй группы, отличающееся тем, что, с целью расширения фукнциональных

0

возможностей за счет определения вероятности перехода системы с непре- рывньм временем и,зменения состояния в любое возможное состояние за заданное время, оно дополнительно содержит четвертый элемент задержки, второй элемент РШИ, элемент И, второй накапливающий сумматор, генератор случайных чисел, вход запуска которого соединен с входом третьего 5 элемента задержки и подключен к первому выходу второго дешифратора,.выход генератора случайных чисел подключен к информационному входу второго накапливающего сумматора, выход третьего элемента задержки подключен к первым входам элементов И Пятой группы и к входу четвертого элемента задержки, выход которого подключен к первому входу элементов И,- каждый выход группы выходов накапливаюш,его сумматора подключен к второму входу одноименного элемента И пятой группы, выход каждого элемента И пятой группы подключен

0

5

0

55

к одноименному входу первой группы информационных входов схемы сравнения, вторая группа информационных входов которой является группой информационных входов устройства, выход схемы сравнения подключен к второму входу элемента И, выход которого подключен к установочному входу второго накапливающего сумматора.

712821

к установочным входам первого и второго счетчиков по модулю п, к блокировочному входу генератора тактовых импульсов, к первому входу второго элемента ИЛИ и к первым входам всех .5 элементов И шестой группы, выходы которых подключены к одноименным входам блока индикации, выход каждо528

го i-ro разряда j-ro регистра второй группы подключен к второму входу i-ro элемента И j-H подгруппы шестой группы, второй вход второго элемента ИЛИ подключен к выходу первого элемента задержки, выход второго элемента ИЛИ соединен с установочным входом первого накапливающего сумматора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения вероятностного состояния дискретной системы | 1983 |

|

SU1164729A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для моделирования биматричных игр | 1986 |

|

SU1388847A1 |

| Устройство для ортогонального преобразования цифровых сигналов по функциям Хаара | 1983 |

|

SU1116435A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Устройство для моделирования канала передачи дискретной информации | 1983 |

|

SU1088006A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для классификации нестационарных случайных процессов | 1987 |

|

SU1462358A1 |

| Устройство для определения показателя эффективности системы передачи данных | 1988 |

|

SU1501091A1 |

| Устройство для моделирования систем массового обслуживания | 1985 |

|

SU1290342A1 |

Изобретение относится к области вычислительной техники и может быть использовано при исследовании сложньк систем. Целью изобретения является расширение функциональных возможностей за счет определения вероятности перехода системы с непрерывным временем изменения состояния в любое возможное состояние за заданное время. Сос.тоя ние системы отображается в виде вершин графа, дугами которого являются вероятности перехода системы из одного состояния в любое возможное состояние за заданное время. Устройство содержит матрицу пхп ячеек памяти, генератор тактовых импульсов, шесть групп-элементов И, первый элемент ИЛИ, две группы элементов ИЛИ, три элемента задержки, блок умножения, блок индикации, первый накапливающий сумматор, схему сравнения, две группы регистров, два счетчика по модулю п, два дешифратора, первая, вторая, третья и шестая группы элементов И содержат по п подгрупп элементов И каждая, а каждая ячейка памяти со- держлт группу элементов И и регистр памяти. Поставленная цель достигается введением четвертого элемента задержки, второго элемента ШШ, элемента И, второго накапливающего сумматора и генератора случайных сигналов, а также за счет новых связей между блоками устройства. 2 ил. i (Л С hO X ю ел ю

г-ЕНЗ

L

Редактор И.Шулла

Фиг. 2

Составитель Т.Сапунова

Техред М.Ходанич Корректор Е.Сирохман

Заказ 7269/49 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

36

| УСТРОЙСТВО для ПОИСКА ПУТЕЙ НАПРАВЛЕННОГО ГРАФА | 0 |

|

SU271907A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения вероятностного состояния дискретной системы | 1983 |

|

SU1164729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-06-19—Подача