Изобретение относится к импульсной технике и может быть использовано при конструировании генераторов предназначенных для синхронизации цифровых схем.

Цель изобретения - расширение функциональных возможностей за счет изменения генерируемых синхросерий и повышение быстродействия генератора импульсов,

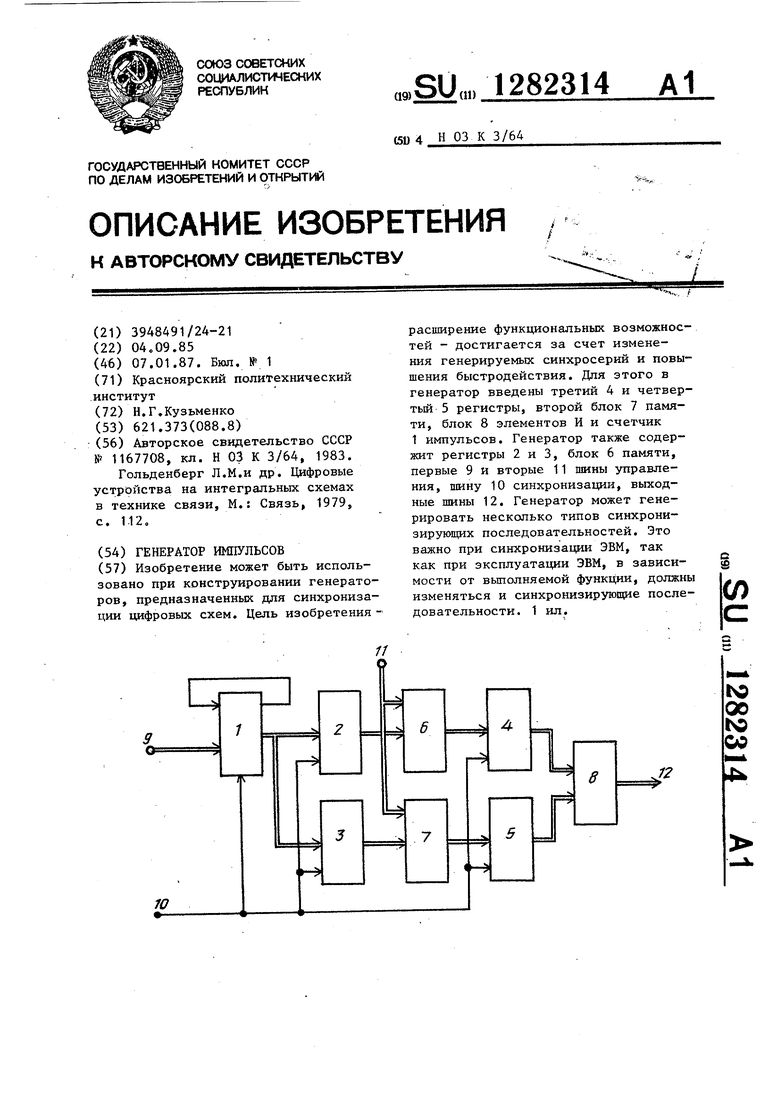

На чертеже приведена функциональная блок-схема генератора импульсов.

Генератор импульсов содержит счетчик 1 импульсов, регистры 2-5, блоки 6 и 7 памяти, блок элементов И 8, первые пшны 9 управления, шину 10 синхросигнала, вторые шины 11 управления, выходные шины 12, причем шина синхросигнала соединена с син- хровходами счетчика 1 и .регистров 2 - 5. Шины 9 управления соединены с информационными входами счетчика 1, выход заема которого соединен со своим входом записи. Информацион- ;ные выходы счетчика 1 соединены с ии

формационными входами регистров 2 и 3 Выходы регистра 2 соединены с младшими адресными входами блока 6, выходы которого соединены с информационными входами регистра 4. Выходы регистра 3 соединены с младшими адресными входами блока 7, выходы которого соединены с информационными входами регистра 5. Выходы регистров 4 и 5 соединены с входами блока элементов И 8. Выходы блока И 8 подключены к выходнь1м шинам 12, Шины 11 управления соединены со старшими адресными входами блоков 6 и 7.

Генератор импульсов работает следующим образом.

По нарастающему фронту каждого синхроимпульса, поступающего с шины 10 синхросигнала, счетчик 1 изменяет свое состояние на -1, регистры 2 и 4 по нарастающему фронту каждого синхроимпульса с шины 10 фиксируют предыдущее состояние счетчика и блока 6 памяти соответственно. Регистры 3 и 5 по падающему фронту каждого синхроимпульса с шины 10 фиксируют текущее состояние счетчика 1 и блока 7 памяти соответственно. По адресу, записанному в регистр 2, из блока 6 памяти считьшается очередное слово, которое фиксируется по нарастающему фронту синхроимпульса в реги стре.4, а в регистр 2 заносится но

.

вое состояние счетчика 1. По адресу, записанному в регистр 3, из блока 7 памяти считывается очередное слово, которое фиксируется по падающему

5 фронту синхроимпульса в регистре 5, а в регистр 3 заносится новое состоя ние счетчика 1. При этом счетчик 1 по нарастающему фронту синхроимпульса изменяет свое состояние на -1.Так

О происходит до тех пор, пока в счетчике 1 не будет установлен ноль. В этом случае по следующему синхро- лмпульсу на первом выходе счетчика 1 появляется импульс, по нарастающе 5 му фронту которого происходит запись в счетчике 1 кода с шины 9 управления. И весь цикл повторяется снова.

В каждом конкретном случае код на шине 9 жестко запаивается. Реги20 стры 4 и 5 необходимы для того, чтобы в момент смены адреса переходный процесс с выходов блоков 6 и 7 памяти не проник на выходные шины 12 через блок элементов И 8 и не вызвал ложного срабатьшания схемы. В регистры 4 и 5 записывается уже установившаяся информация из блоков 6 и 7 памяти соответственно.

Регистры 3 и 5 и блок 7 памяти позволяет на одних входах блока элементов И 8 получить коды, сдвинутые относительно кодов на других входах блока элементов И 8 на полпериода синхрочастоты. В блоке элементов И 8

35 осуществляется сложение одноименных сигналов, в результате на выходах блока И 8 получаются синхросерий, период которых кратен половине периода частоты синхронизации.

40 Кроме того, регистры 2 и 3 выполняют роль конвейерных регистров и позволяют уменьшить общее время цикла генератора, так как позволяют осуществить параллельную работу счетчи45 ка 1 и блоков 6 и 7.

Это обеспечивает увеличение максимальной частоты генерируемых синхросерий.

25

30

Код на шине 11 управления определяет номер адресуемой области памяти блоков 6 и 7, а следовательно, и закон генерирования синхросерий. При смене кода на шине 11 изменяется область адресуемой памяти и закон генерирования синхросерий. Таким образом, один и тот же генератор может генерировать несколько типов синхронизирующих последовательностей без

3

переделки последнего. Это но при синхронизации ЭВМ, при ее эксплуатации в зав от вьтолняемой функции доняться и синхронизирующие тельности.

Формула изобретения

Генератор импульсов, содержащий первый регистр, выходы которого соединены с мпадшими адресными входами первого блока памяти, выходы которого подключены к информационным входам второго регистра, синхровход которого соединен с синхровходом первого регистра и шиной синхросигнала, отличающийся тем, что, с целью расширения функциональных возможностей и повышения быстро- действия, в него введены третий и четвертый регистры, второй блок памяти, блок элементов И и счетчик имРедактор В. Данко

Составителе В, Потапов Техред Л.Олейник

Кор Подп

7285/57 Тираж 899

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4 I.

O 5 0

пульсов, в котором вход заема соединен со входом записи, а вход вычитания подключен к шине синхросигнала и синхровходам tpeTbero и четвертого регистров, выходы третьего регистра соединены с младшими адресными входами второго блока памяти, старшие адресные входы которого соединены со старшими адресными входами первого блока памяти и первыми шинами управления, а выходы подключены к информационным входам четвертого .регистра, выходы которого соединены с первыми входами блока элементов И, вторме входы которого подключены к выходам второго регистра,., а выходы соединены с выходными шинами, при этом информационные входы первого регистра подключены к информацион - ным входам -претьего регистра и к информационным выходам счетчик а импульсов, информационные входы которого соединены со вторыми шинамиуправления.

Корректор В. Бутяга Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный генератор импульсов | 1984 |

|

SU1347160A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Программируемый логический контроллер | 1988 |

|

SU1647518A1 |

| Запоминающее устройство | 1976 |

|

SU613402A1 |

| Устройство для преобразований изображений | 1986 |

|

SU1367023A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

Изобретение может быть использовано при конструировании генераторов, предназначенных для синхронизации цифровых схем. Цель изобретения расширение функциональных возможностей - достигается за счет изменения генерируемых синхросерий и повышения быстродействия. Для этого в генератор введены третий 4 и четвертый 5 регистры, второй блок 7 памяти, блок 8 элементов И и счетчик 1 импульсов. Генератор также содержит регистры 2 и 3, блок 6 памяти, первые 9 и вторые 11 шины управления, шину 10 синхронизации, выходные шины 12. Генератор может генерировать несколько типов синхрони- зируюш 1Х последовательностей. Это важно при синхронизации ЭВМ, так как при эксплуатации ЭВМ, в зависимости от вьшолняемой функции, должны изменяться и синхронизирующие последовательности. 1 ил. i (Л 00 to со

| Авторское свидетельство СССР № 1167708, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гольденберг Л.М.и др | |||

| Цифровые устройства на интегральных схемах в технике связи, М.: Связь, 1979, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

Авторы

Даты

1987-01-07—Публикация

1985-09-04—Подача