записи результата. Наличие трех тактов обусловно структурой запоминающего устройства.

Цель изобретения - повышение быстродействия запоминающего устройства путем сокращения тактов выполнения операций.

Поставленная цель достигается тем, что устройство содержит дополнительный блок памяти, коммутатор и элементы И-НЕ, один из входов которых подключен к третьему и четвертому выходам блока управления, другие входы - к выходам блоков памяти, а выходы элементов И-НЕ соединены с информационными шинами первой и второй групп. Входы дополнительного блока памяти подключены к третьему входу блока памяти и информационным шинам третьей группы, к выходу коммутатора и пятому выходу блока управления, входы коммутатора соединены с выходами счетчиков и генератора и пятым выходом блока управления.

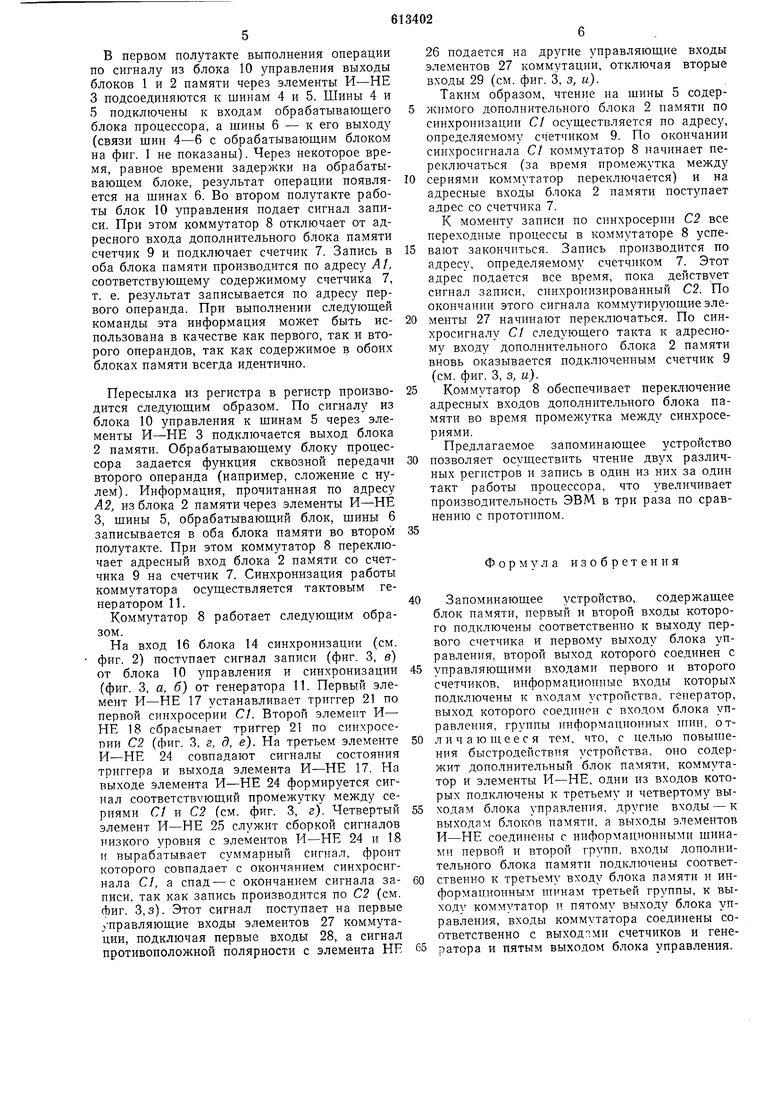

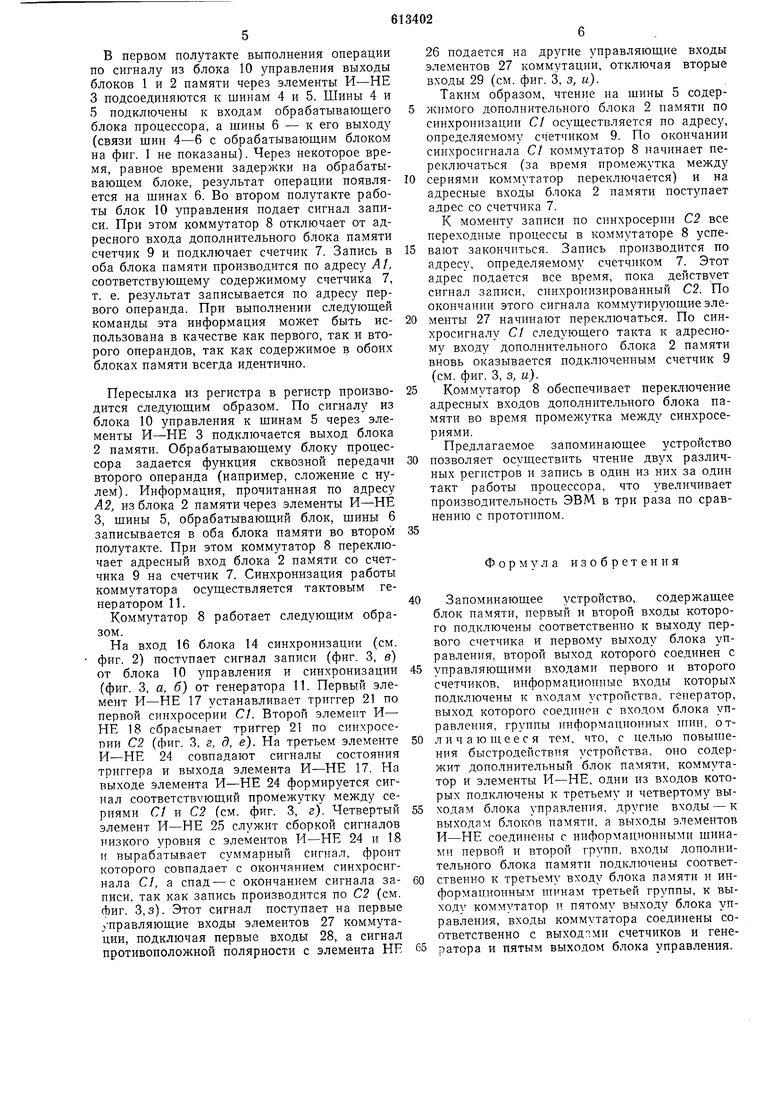

На фиг. 1 изображена функциональная схема запоминающего устройства; на фиг. 2 - схема коммутатора; на фиг. 3 показана временная диаграмма, поясняющая работу коммутатора.

Запоминающее устройство содержит (см. фиг. 1) блок 1 памяти, дополнительный блок 2 памяти, элементы И-НЕ 3, группы информационных шин 4-6, первый счетчик 7, коммутатор 8, второй счетчик 9, блок 10 управления, генератор 11.

Входы счетчиков соединены с входами 12 и 13 устройства. Первый и второй входы блока 1 подключены соответствепно к выходу счетчика 7 и первому выходу блока 10, второй выход которого соединен с управляющими входами счетчиков 7 и 9. Одни из входов элементов И-НЕ 3 подключены к третьему и четвертому выходам блока 10, другие входы - к выходам блоков 1 и 2 памяти, а выходы элементов И-НЕ соединены с информационными шинами первой 4 и второй 5 групп. Входы блока 2 подключены ктретьему входу блока 1 и информационным шинам третьей группы 6, к выходу коммутатора 8 и пятому выходу блока 10. Входы коммутатора 8 соединены с выходами счетчиков 7 и 9 и генератора 11 и пятым выходом блока 10.

На фиг. 2 приняты следующие обозначения: 14 - блок синхронизации; 15 - блок коммутации; 16 - первый вход коммутатора; 17 и 18 - первый и второй элементы И-НЕ соответственно; 19 и 20 - второй и третий входы коммутатора соответственно, 21 - триггер; 22 и 23 - элементы триггера; 24 и 25 - третий и четвертый элементы И-НЕ соответственно, 26 - элементы НЕ; 27 - коммутирующие элемеиты; 28 и 29 - первые и вторые информационные входы блока коммутации соответственно; 30 - выход блока коммутации.

На фиг. 3 показаны первая синхросерия С1 импульсов (а) и вторая синхросерия С2

импульсов (б), сигнал записи (в), а также сигналы на выходах элементов 17 (г), 18 (д), 23 (е), 24 (ж), 25 (з), 26 (и).

Работает устройство следующим образом. Для выполнения команд обработки данных необходимо извлечь из запоминающего устройства два операнда и загрузить в запоминающее устройство результат обработки. Для экономии объема команд обычно адрес

результата задается неявно, например результат загружается на место первого операнда.

Таким образом, в команде обычно указаны два адреса: адрес регистра запоминающего устройства (А1), где расположен первый операнд и куда следует загружать результат, и адрес регистра запоминающего устройства, содержащего второй операнд (А2). Адреса первого и второго регистров по входам

12 и 13 загружаются соответственно на первый 7 и второй 9 счетчики. Операнды загружаются в запоминающее устройство с шин 6, куда подаются, например, из оперативной памяти (на фиг. I не показано).

Сигнал записи из блока 10 управления (например, микропрограммного) поступает на блоки 1 и 2 памяти и на коммутатор 8. Коммутатор 8 подключает к адресному входу дополнительного блока 2 памяти выход

счетчика 7. Таким образом информация записывается одновременно в одноименные регистры обоих блоков 1 и 2 памяти по адресу, определяемому содержимым счетчика 7. Запись следующих операндов проводится аналогично, путем смены адреса записи на счетчике 7 загрузкой в него определенного поля следующей команды загрузки или увеличением содержимого счетчика 7 на единицу при загрузке массива. Продвижение счетчика 7 осуществляется по сигналу из блока 10 управления. После загрузки блоков памяти в обоих блоках одна и та же информация будет расположепа в одноименных регистрах запоминающего устройства.

В некоторый момент времени процессор ЭВМ, в состав которого входит описанное запоминающее устройство, выполняет команду обработки двух операндов, например сложение. Оба операида располагаются в разных регистрах запомииающего устройства, например, по адресу А1 и А2. Результат обработки следует загрузить также в запоминающее устройство по адресу А1. При выборке

команды адрес первого операнда А1 засылается на счетчик 7, а адрес второго операнда А2 - на счетчик 9, коммутатор 8 при отсутствии сигнала записи с блока 10 управления подключает к адресному входу дополнительного блока 2 памяти счетчик 9. Блоки 1 и 2 памяти находятся в режиме постоянного чтения. На выходах блока 1 присутствует информация, прочитанная из регистра по адресу А1, а на выходах блока 2 - из регистра

по адресу А2.

В первом полутакте выполнения операции по сигналу из блока 10 управления выходы блоков 1 и 2 памяти через элементы И-НЕ 3 подсоединяются к шинам 4 и 5. Шины 4 и 5 подключены к входам обрабатывающего блока процессора, а шины 6 - к его выходу (связи шин 4-6 с обрабатывающим блоком на фиг. 1 не показаны). Через некоторое время, равное времени задержки на обрабатывающем блоке, результат операции появляется на шинах 6. Во втором полутакте работы блок 10 управления подает сигнал записи. При этом коммутатор 8 отключает от адресного входа дополнительного блока памяти счетчик 9 и подключает счетчик 7. Запись в оба блока памяти производится по адресу Л/, соответствующему содержимому счетчика 7, т. е. результат записывается по адресу первого операнда. При выполнении следующей команды эта информация может быть использована в качестве как первого, так и второго операндов, так как содержимое в обоих блоках памяти всегда идентично.

Пересылка из регистра в регистр производится следующим образом. По сигналу из блока 10 управления к шинам 5 через элементы И-НЕ 3 подключается выход блока 2 памяти. Обрабатывающему блоку процессора задается функция сквозной передачи второго операнда (например, сложение с нулем). Информация, прочитанная по адресу А2, из блока 2 памяти через элементы И-НЕ 3, шины 5, обрабатывающий блок, шины 6 записывается в оба блока памяти во втором полутакте. При этом коммутатор 8 переключает адресный вход блока 2 памяти со счетчика 9 на счетчик 7. Синхронизация работы коммутатора осуществляется тактовым генератором 11.

Коммутатор 8 работает следующим образом.

На вход 16 блока 14 синхронизации (см. фиг. 2) поступает сигнал записи (фиг. 3, в) от блока 10 управления и синхронизации (фиг. 3, а, б) от генератора П. Первый элемент И-НЕ 17 устанавливает триггер 21 по первой синхросерии С/. Второй элемент И- НЕ 18 сбрасывает триггер 21 по синхросерии С2 (фиг. 3, г, д, е). На третьем элементе И-НЕ 24 совпадают сигналы состояния триггера и выхода элемента И-НЕ 17. На выходе элемента И-НЕ 24 формируется сигнал соответствующий промежутку между сериями С/ и С2 (см. фиг. 3, г). Четвертый элемент И-НЕ 25 служит сборкой сигналов низкого уровня с элементов И-НЕ 24 и 18 и вырабатывает суммарный сигнал, фронт которого совпадает с окончанием синхросигнала С/, а спад - с окончанием сигнала записи, так как запись производится по С2 (см. фиг. 3, з). Этот сигнал поступает на первые управляющие входы элементов 27 коммутации, подключая первые входы 28, а сигнал противоположной полярности с элемента НЕ

26 подается на другие унравляющие входы элементов 27 коммутации, отключая вторые входы 29 (см. фиг. 3, з, и).

Таким образом, чтение на шины 5 содержимого дополнительного блока 2 памяти по синхронизации С/ осуществляется по адресу, определяемому сч етчиком 9. По окончании синхросигнала С/ коммутатор 8 начинает переключаться (за время промежутка между

сериями коммутатор переключается) и на адресные входы блока 2 памяти поступает адрес со счетчика 7.

К моменту записи по сннхросерии С2 все переходные процессы в коммутаторе 8 успевают закончиться. Занись производится по адресу, определяемому счетчиком 7. Этот адрес подается все время, пока действует сигнал записи, синхронизированный С2. По окончании этого сигнала коммутирующие элементы 27 начинают переключаться. По синхросигналу С/ следующего такта к адресному входу дополнительного блока 2 памяти вновь оказывается подключенным счетчик 9 (см. фиг. 3, 3, и).

Коммутатор 8 обеснечивает переключение адресных входов дополнительного блока памяти во время промежутка между синхросериями. Предлагаемое запоминающее устройство

позволяет осуществить чтение двух различных регистров и запись в один из них за один такт работы процессора, что увеличивает производительность ЭВМ в три раза по сравнению с прототипом.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, первый и второй входы которого подключены соответственно к выходу первого счетчика и первому выходу блока управления, второй выход которого соединен с

управляющими входами первого и второго счетчиков, информационные входы которых подключены к входам устройства, гетшратор, выход которого соедт нен с входом блока управления, группы информационных нпт, отл и ч а ю HI е е с я тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный блок памяти, коммутатор и элементы И-НЕ, одни из входов которых подключены к третьему и четвертому выходам блока управления, другие входы-к выходам блоков памяти, а выходы элементов П-НЕ соединены с информационными шинами первой и второй групп, входы дополнительного блока памяти подключены соответственно к третьему входу блока памяти и информационным тинам третьей группы, к выходу коммутатор пятому выходу блока управления, входы коммутатора соединены соответственно с выходами счетчиков и генератора и пятым выходом блока управления.

Источники информации, нринятые во внимание при эксиертизе 1. Микроирограммное управление, Вып. II. М., изд. «Мир, 1974. с. 72.

2. Микропрограммное управление. Вып. II, М., изд. «Мир, 1974. с. 168, рис. 8.1 и рис. 8.9.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU877613A1 |

| Устройство для выбора информации из блока памяти | 1976 |

|

SU615538A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Процессор для быстрого преобразования Фурье | 1989 |

|

SU1633426A1 |

| Устройство для восстановления информации при сбоях в блоках ЦВМ | 1988 |

|

SU1689954A1 |

| Запоминающее устройство | 1989 |

|

SU1695381A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

-/

23

/

/ 29

7Л

JO

27k /

Л

27

/

.J

Авторы

Даты

1978-06-30—Публикация

1976-07-07—Подача