1

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах.

. Целью изобретения является повышение быстродействия устройства.

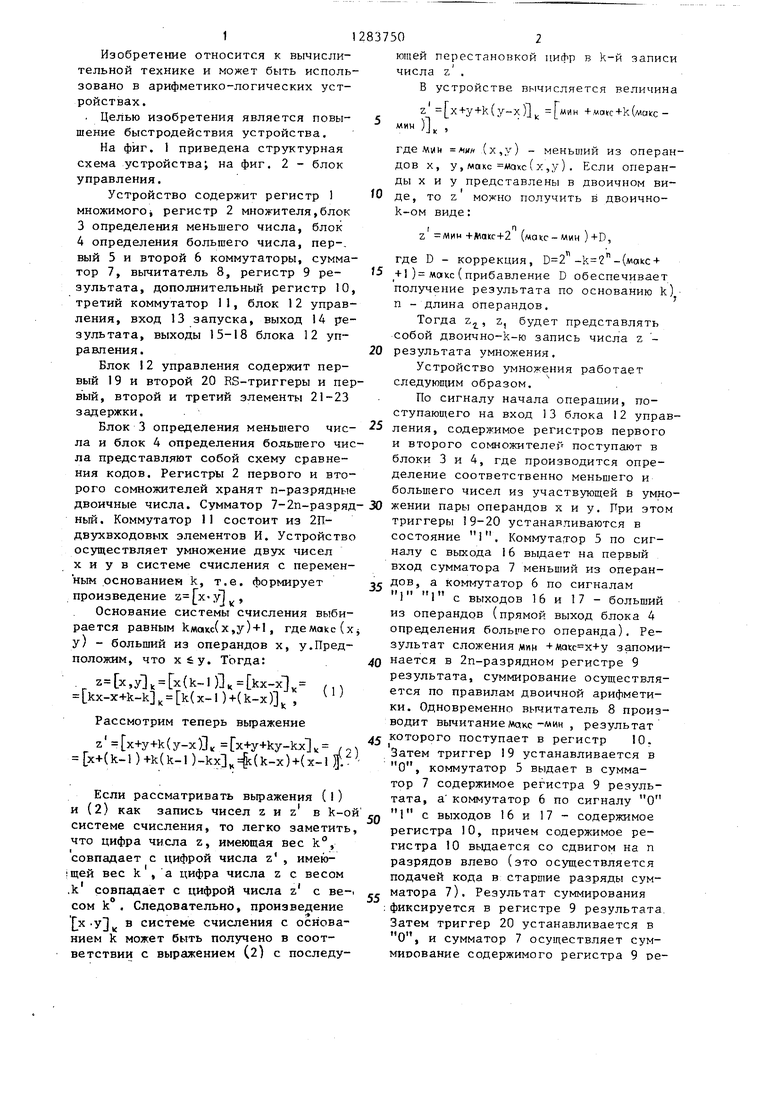

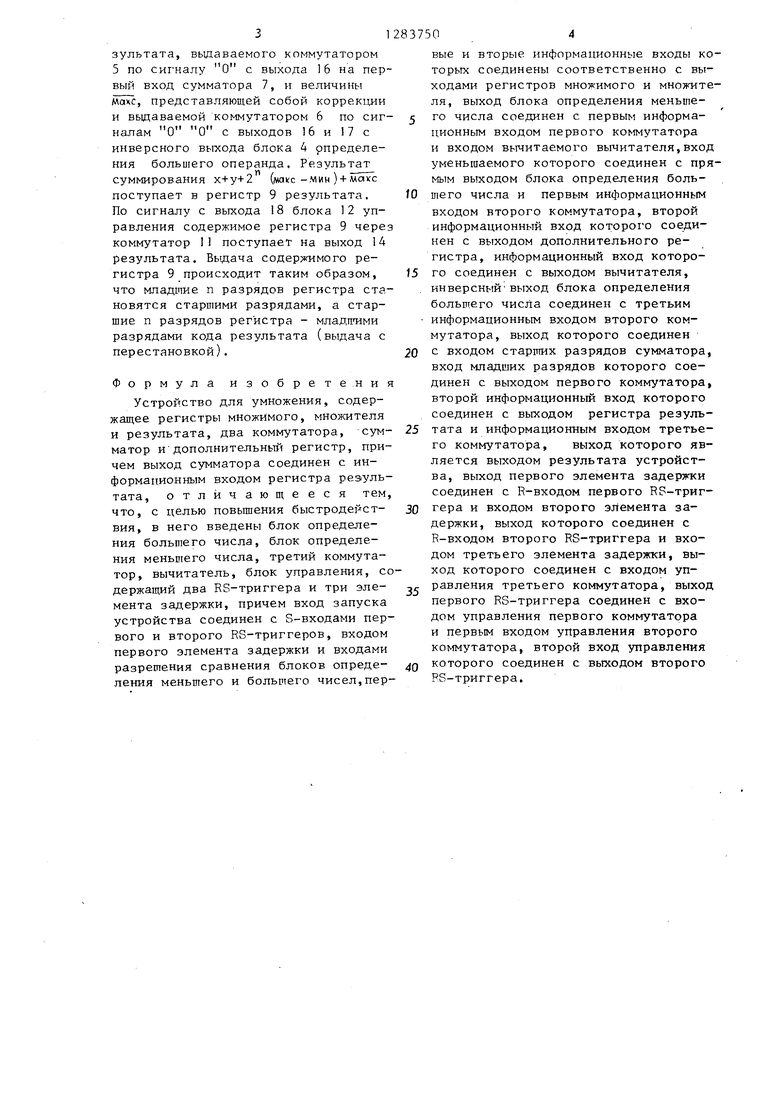

На фиг. 1 приведена структурная схема устройстваJ на фиг. 2 - блок управления.

Устройство содержит регистр множимогоj регистр 2 множителя,блок

3определения меньшего числа, блок

4определения большего числа, пер-, вый 5 и второй 6 коммутаторы, сумматор 7, вьгчитатель 8, регистр 9 результата, дополнительный регистр 10, третий коммутатор 11, блок 12 управления, вход 13 запуска, выход 14 зультата, выходы 15-18 блока 12 управления.

Блок I2 управления содержит первый 19 и второй 20 RS-триггеры и первый, второй и третий элементы 21-23 задержки.

Блок 3 определения меньшего чис- ла и блок 4 определения большего числа представляют собой схему сравнения кодов. Регистры 2 первого и вто1

По сигналу начала операции, поступающего на вход 13 блока 12 управления, содержимое регистров первого и второго сомножителей поступают в блоки 3 и 4, где производится определение соответственно меньшего и большего чисел из участвующей в умноэ дов, а коммутатор

- и 1 II И| tt

рого сомножителей хранят п-разрядные

двоичные числа. Сумматор 7-2п-разряд- 30 жении пары операндов х и у. При этом

ньш. Коммутатор 11 состоит из 2П- триггеры 19-20 устанавливаются в

состояние . Коммутатор 5 по сигналу с выхода 16 выдает на первый вход сумматора 7 меньший из операн6 по сигналам

с выходов 16 и 17 - больший из операндов (прямой выход блока 4 определения большего операнда). Результат сложения Мин +WQtt x+y запоми- jjQ нается в 2п-разрядном регистре 9

результата, суммирование осуществляется по правилам двоичной арифметики. Одновременно вьгчитатель 8 производит вычитание Макс-лАин , результат 45 которого поступает в регистр 10. Затем триггер 19 устанавливается в

двухвходовых элементов И. Устройство осуществляет умножение двух чисел X и у в системе счисления с переменным рснованиен k, т.е. формирует произведение у ,

Основание системы счисления выбирается равным Кмакс(х,у) + 1, гдeмakc(xj у) - больший из операндов х, у.Предположим, что . Тогда:

(1)

. ,y, x(k-l),kx-x kx-x+k-k k( х-1 ) +(k-x) j. ,

Рассмотрим теперь выражение

z х+у+k (у-х ) к x+y+ky-kxl к / - 4 х+( k-1 )+k( k-1 )-kx рс( k-x)+(х-1 If.

Если рассматривать вьфажения (I) и (2) как запись чисел z и z в k-ой системе счисления, то легко заметить, что цифра числа z, имеющая вес k°, совпадает с цифрой числа z , имеющей вес k , а цифра числа z с весом ,k совпадает с цифрой числа z с ве-. сом k . Следовательно, произведение Тх у в системе счисления с основанием k может быть получено в соответствии с выражением (2) с последу50

55

О, коммутатор 5 выдает в сумматор 7 содержимое регистра 9 результата, а коммутатор 6 по сигналу О 1 с выходов 16 и 17 - содержимое регистра 10, причем содержимое регистра 10 вьщается со сдвигом на п разрядов влево (это осуществляется подачей кода в старшие разряды сумматора 7). Результат суммирования фиксируется в регистре 9 результата. Затем триггер 20 устанавливается в О, и сумматор 7 осуществляет суммирование содержимого регистра 9 реfO

837502

ютей перестановкой цифр в k-й записи числа Z .

В устройстве вычисляется величина

z x+y+k()3 мин +Mare+k(Matc- мин ) ,

где мкй НИИ (х,у) - меньший из операндов X, у, макс махс ( х,у) . Если операнды х и у представлены в двоичном виде, то Z можно получить в двоично- k-OM виде:

Z /иим+Mai(c+2 (макс-Мин )+D,

где D - коррекция, -(ма1сс + 5 +1 ) мокс ( прибавление D обеспечивает получение результата по основанию k) п - длина Операндов.

Тогда z, Z, будет представлять собой двоично-К-ю запись числа z - результата умножения.

Устройство умножения работает следующим образом.

По сигналу начала операции, поступающего на вход 13 блока 12 управления, содержимое регистров первого и второго сомножителей поступают в блоки 3 и 4, где производится определение соответственно меньшего и большего чисел из участвующей в умно20

дов, а коммутатор

и 1 II И| tt

с выходов из операндов (прям определения больше зультат сложения Ми нается в 2п-разряд

0

5

О, коммутатор 5 выдает в сумматор 7 содержимое регистра 9 результата, а коммутатор 6 по сигналу О 1 с выходов 16 и 17 - содержимое регистра 10, причем содержимое регистра 10 вьщается со сдвигом на п разрядов влево (это осуществляется подачей кода в старшие разряды сумматора 7). Результат суммирования фиксируется в регистре 9 результата. Затем триггер 20 устанавливается в О, и сумматор 7 осуществляет суммирование содержимого регистра 9 результата, выдаваемого коммутатором 5 по сигналу О с выхода 16 на первый вход сумматора 7, н величины Махе, представляющей собой коррекции и выдаваемой коммутатором 6 по сигналам О О с выходов 16 и 17 с инверсного выхода блока 4 рпределе- ния большего операнда. Результат суммирования х+у+2 (макс-.мин ) + Ma«; поступает в регистр 9 результата. По сигналу с выхода 18 блока 12 управления содержимое регистра 9 через коммутатор 1 поступает на выход 14 результата. Выдача содержимого регистра 9 происходит таким образом, что младшие п разрядов регистра становятся старшими разрядами, а старшие п разрядов регистра - младтгими разрядами кода результата (выдача с перестановкой).

Формула изобретения Устройство для умножения, содержащее регистры множимого, множителя и результата, два коммутатора, сумматор И дополнительньтй регистр, причем выход сумматора соединен с информационным входом регистра результата, отличающееся тем, что, с целью повышения быстродействия, в него введены блок определения большего числа, блок определения меньшего числа, третий коммутатор, вычитатель, блок управления, содержащий два RS-триггера и три элемента задержки, причем вход запуска устройства соединен с S-входами первого и второго RS-триггеров, входом первого элемента задержки и входами разрешения сравнения блоков определения меньшего и большего чисел,пер

2837504

вые и вторые информационные входы которых соединены соответственно с выходами регистров множимого и множителя, выход блока определения меньте- 5 го числа соединен с первым информационным входом первого коммутатора и входом вычитаемого вычитателя,вход уменьшаемого которого соединен с прямым выходом блока определения больfO шего числа и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом дополнительного регистра, информационный вход которо15 го соединен с выходом вычитателя, инверсный выход блока определения большего числа соединен с третьим информационным входом второго коммутатора, выход которого соединен

20 с входом старших разрядов сумматора, вход младших разрядов которого соединен с выходом первого коммутатора, второй информационный вход которого соединен с выходом регистра резуль25 тата и информационным входом третьего коммутатора, выход которого является выходом результата устройства, выход первого элемента задержки соединен с R-входом первого RS-триг30 гера и входом второго элемента задержки, выход которого соединен с R-входом второго RS-триггера и входом третьего элемента задержки, выход которого соединен с входом управления третьего коммутатора, выход первого RS-триггера соединен с входом управления первого коммутатора и первым входом управления второго коммутатора, второй вход управления

40 которого соединен с выходом второго RS-триггера,

35

(Paz.2

/5

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах. Целью изобретения является повьшание быстродействия устройства умножения. Поставленная цель достигается тем, что в устройство для умножения, содержащее регистры первого и второго операндов, регистр результата, сумматор, два коммутатора и дополнительный регистр, введены блок определения меньшего операнда и блок определения большего операнда , блок управле - ния , третий коммутатор и вы - читатель . Результат умножения представлен двоично -К -и записью. 2 ил. о «е

| УСТРОЙСТВО УМНОЖЕНИЯ ПОСЛЕДОВАТЕЛЬНОГО | 0 |

|

SU383044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-01—Подача