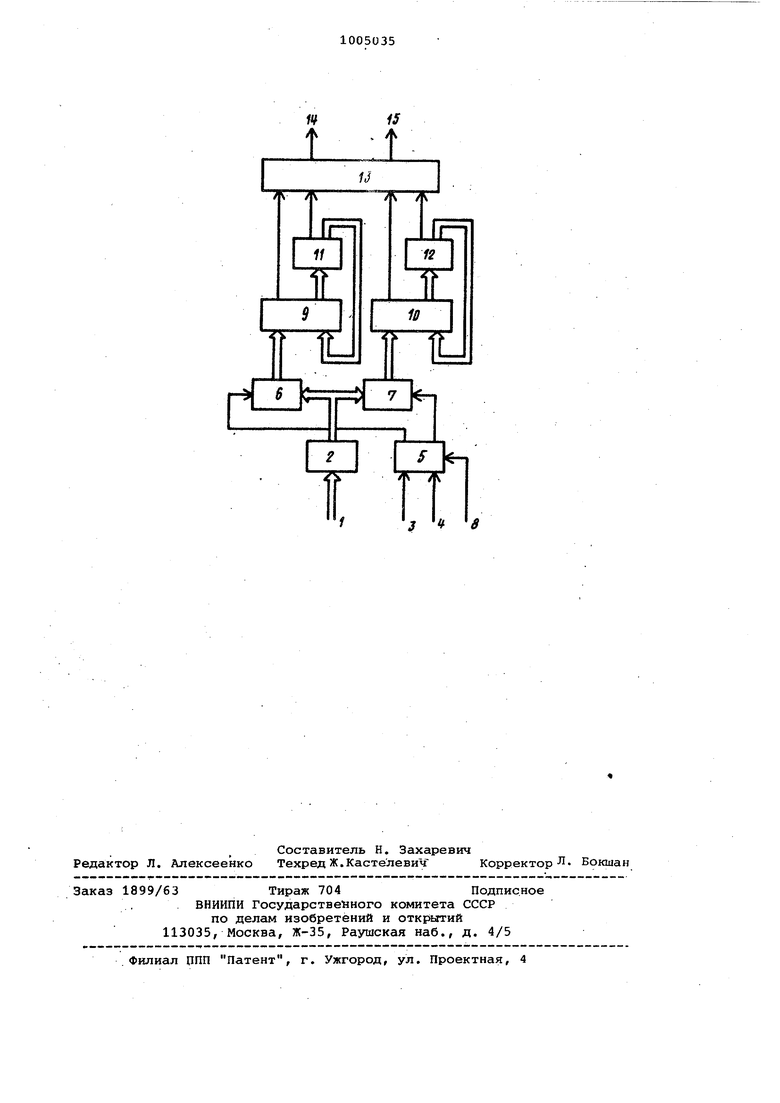

второго регистров результата, выходами старшего разряда результата подключенных к вторым входам первой и второй групп входов сумматора в избыточной двоичной системе счисления, выходы которого подключены к выходам устройства. Устройство производит умножение двух чисел, одно из которых представлено в избыточной двоичной системе счисления а другое - двоичным кодом, и имеет высокое быстродействие, так как результат вычисления произведения выводится последовательным кодом, на.чиная со старшего разряда, в процес се вычисления f 3 . Недостатком устройства является сложность алгоритма умножения, что вызывает большие аппаратурные затраты. Цель изобретения - уменьшение ап паратурных затрат в устройстве. Поставленная цель достигается те что устройство содержащее регистр множителя, входы которого подключены к шине множителя устройства, первый 1и второй блоки элементов И, первые входы которых подключены к выходам регистра множителя,первый и второй сумматоры результата, первый и второй регистры результата, входы которых соединены с выходами соответственно первого и второго сумматоров результата, первые входы которых подключены к выходам младших разрядов соответственно первого и второго регистров результата, и сумматор в избыточной двоичной систэме счисления, первый и второй вхо ды которого подключены к выходам пе реноса соответственно первого и вто рого сумматоров результата, а третий и четвертый входы подключены к выходам старшего разряда соответственно первого и второго регистров результата, выходы сумматора в избы точной двоичной системе счисления подключены к выходам произведения устройства, содержит блок анализа янака, первый и второй входы которо соединены соответственно с первым и вторым входами множимого устройства третий вход подключен к входу злака множителя устройства, а первый и второй выходы соединены с вторыми входами соответственно первого и вто рого блоков элементов И, выходы которых подключены к вторым входам со ответственно первого и второго сумматоров результата. На чертеже приведена схема устрой ства. Устройство для умножения содержит шину 1 множителя, регистр 2 множителя, первый и второй входы 3 и 4 множимого устройства, блок 5 анализа знака, первый и второй блоки б и 7 элементов И вход 8 знака множителя, первый и второй сумматоры 9 и 10 результата, первый и второй регистры 11 и 12 результата, суг матор 13 в избыточной двоичной системе счисления и выходы 14 и 15 произведения устройства. Шина 1 множителя-устройства подключена к входам регистра 2 множителя, входы 3 и 4 множимого устройства подключены к первому и второму входам блока 5 анализа знака, выходы регистра 2 множителя подключены к первым входам первого и второго блоков 6 и 7 элементов И, вторые входы которых соединены соответственно с первым и вторым выходами блока 5 анализа знака, третий вход которого подключен к входу 8 знака множителя устройства. Выходы перво 0 и второго блоков 6 к 7 элементов И соединены с вторыми входами соответственно первого и второго сумматоров 9 и 10 результата, первые входы которых подключены к выходам соответственно первого и второго регистров 11 и 12 результата, выходы переноса сумматоров 9 и 10 результата соединены соответственно с первьм и вторым входами сумматора 13 в избыточной двоичной системе счисления, третий и четвертый входы которого подключены к выходам старшего разряда соответственно первого и второго регистров 11 и 12 результата, входы которых подключены к выходам соответственно первого и второго сумматоров 9 и 10 результата, а выходы 14 и 15 подключены к выходам произведения устройства. Устройство работает следующим образом. в начальном такте работы регистры 11 и 12 результата сбрасываются в нулевое состояние, а в регистр 2 множителя по шине 1 устройства поступает значение множителя параллельным двоичным кодом. Знак множителя с входа 8 устройства подается на третий вход блока 5 ангшиза знака и остается на входе до окончания цикла умножения. Значения множимого подаются на входы 3 и 4 устройстт а последовательным избыточным двоичным кодом, начиная со старшего разряда. На первые входы элементов И блоков 6 и 7 подаются значения п разрядов множителя. Если i-й разряд множимого равен 1 или Т, на первые входы первого или второго сумматоров У или 10 результата в i-м такте работы устройства поступает значение множителя. На вторые вхрды элементов И блоков б и 7 поступает i-е значение знака произведения, полученное путем перемножения с помощью блока 5 анализа знаков знака множина знак i-го разряда множимого. 5 анализа знака вырабатывает произведения согласно уравнению

,

si«yn В V А: В, где ct, положительное и отрицательное 1-е значения знака произведения; А , положитель ное и отрицательное значения 1-го разряда множимого; 51ЯвВ - знак множителя. Если i-e значение знака произведения отрицательно, т.е. перемножаются аргументы с разньвди знаками, то зндчение множителя с выходов элементов И блока 7 подается на первые вхо ды разрядов второго сумматора 10 ре зультата, на вторые входы которого подается отрицательное значение п-1 младших разрядов (i-l)-ro результата с выходов регистра.12. При положительном знаке аналогично работают блоки 6,9,11. Сумматор 13 в избыточной двоич,ной системе счисления суммирует два исла в избыточной двоичной системе счисления. Первое число, at. образует положительным и отрицательным значени ми(п+1)-го разряда 1-го результата, ко торые подаются на пёрзыйи третий йход cy aтopa 13с выходов переноса суммат ров У и10. Второе число Ь| образуется положительным и отрицательным значениями п-го разряда П-1)-го результата, которые подаются на вто рой и четвертый входы сумматора 13 с выходов старшего п-го разряда регистров 11 и 12. Результат умножения с выходов су матора 13 поступает на выходы 14 и 15 устройства (положительных и отри цательных значений произведения). Результат умножения выдается последовательно старяиими разрядами вперед в избыточной двоичной системе счисления. Таким образом, данное устройство позволяет производить умножение двух чисел, одно из которых выражено в избыточной двоичной системе счисления, последовательным методом старпими разрядами вперед. При этом результат умножения получается на выходах устройства одновременно с вводом разрядов множимого.

Разрядность множимого может быть больше разрядности множителя.

В устройстве отсутствуют регистры множимого и коммутатор, что упрощает его конструкцию по сравнению с прототипом. Формула изобретения Устройство для умножения, содержащее регистр множителя, входы кото-; рого подключены к шине множителя уст ройства, первый и второй.блоки элементов И, первые входы которых подключены к выходам регистра множителя, первый и второй сумматоры результата, первый и второй регистры результата, входы которых соединены с выходами, соответственно первого и второго сумматоров результата, первые входы которых подключены к выходам младших разрядов соответственно первого и второго регистров результата, и сумматор в избыточной двоичной системе счисления, первый и второй входы которого подключены к выходгш переноса соответственно первого и второго сумматоров результата, а третий и четвертый входы подключены к выходам старшего разряда соответственно первого и второго регистров результата, выходы сумматора в избыточной двоичной системе счисления подключе-. ны к выходам произведения устройства, о тличающееся тем, что, с целью уменьшения аппаратурных затрат в устройстве, оно содержит блок анализа знака, первый и второй вхо которого соединены соответственно с первым и вторым входами множшлого устройства, третий вход соединен с входом знака множителя устройству, :а первый и второй выходы соединегел iQ вторыми входами соответственно первого и второго блоков элементов И, |Выходы которых подключены к вторым входам соответственно первого и второго сумматоров результата. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 631919, кл. G 06 F 7/49, 1977. 2.Авторское св идетёльство СССР 603989, кл. G 06 F 7/49, 1977. 3.Авторское свидетельство СССР по заявке 2S14123/18-24, кл. G 06 F 7/49, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-23—Подача