Изобретение относится к вычислительной технике и может быть использовано в устройствах, выполняющих операции над десятичными числами.

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения операции сложения чисел с плавающей запятой.

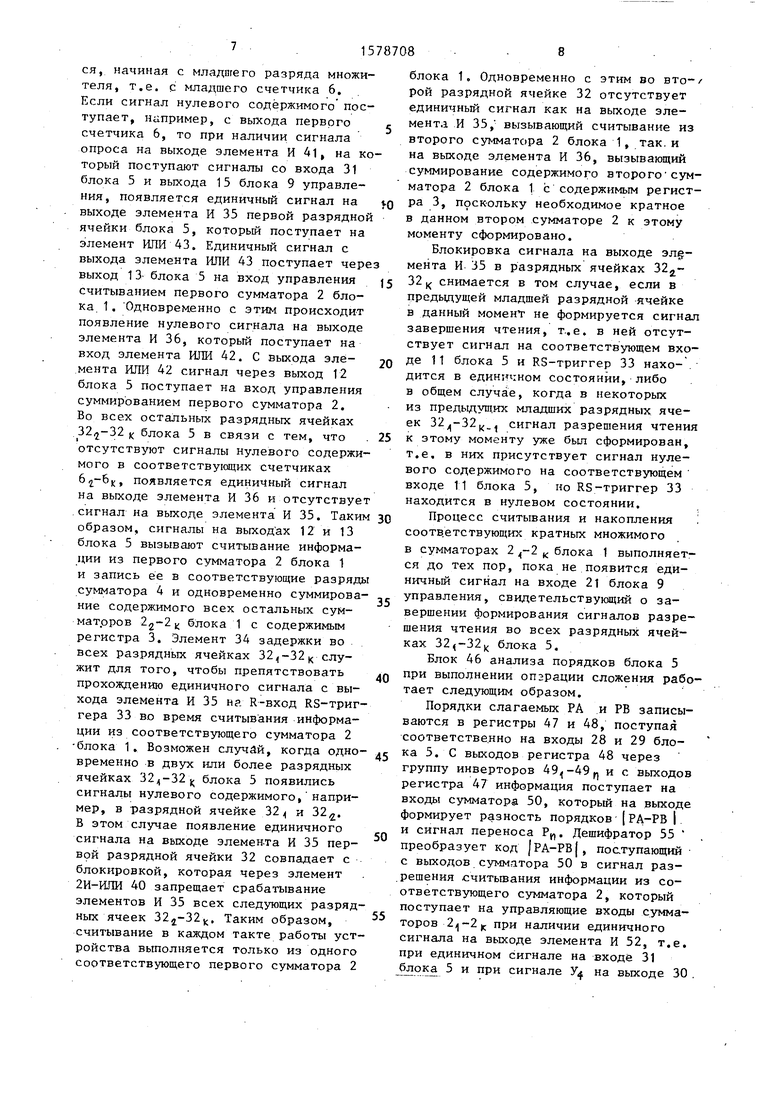

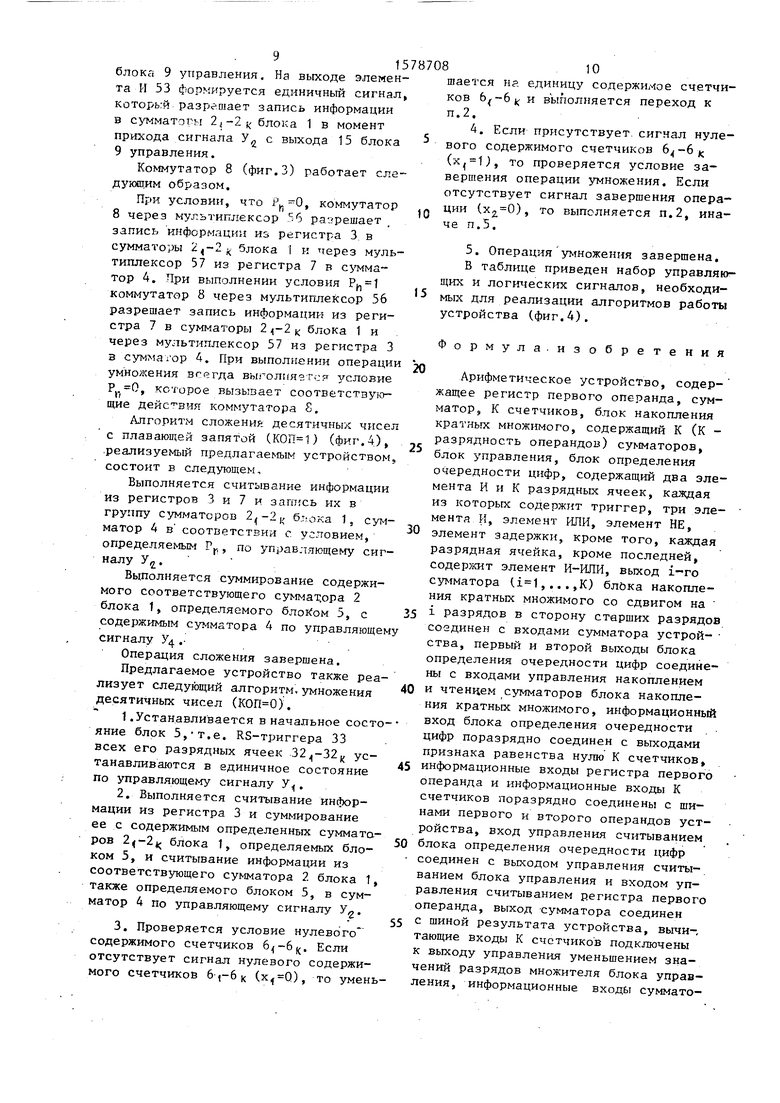

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема блока определения очередности цифр; на фиг.З - функциональная схема коммутатора; на фиг.4 - алгоритм работы устройства.

Арифметическое устройство (фиг,О содержит блок 1 накопления кратных множимого, содержащий К сумматоров , регистр первого операнда 3, 2К-разрядный сумматор 4, блок 5 определения очередности цифр, К счетчиков 6,-6К.регистр второго операнда 7, коммутатор 8, блок 9 управления. Выход 10 блока 5 является выходом завершения формирования кра гных в блоел j

00

о

00

ке 1t выходы признаков нулевого содержимого счетчиков 6 ,-6 к соединены с информационным входом 11 блока 5, выход 12 которого подключен к входам управления суммированием сумматоров 2,|-2к блока 1, а выход 13 - к входам управления считыванием сумматоров 2 ,(-2 к блока 1. Выходы 14 сумматоров 24-2k блока 1 соединены с входами сумматора 4 таким образом, что входы разрядов сумматора 4 с 1-го по (К+1)соединены с выходами 14 сумматора входы разрядов сумматора 4 со 2-го по (К+2)-й соединены с выходами 14 сумматора 2г и т.д., а входы разрядов сумматора 4 с К-го по 2К-й - с выходами 14 сумматора 2 . Вход управления считыванием регистра 3, регистра 7 и второй управляющий вход блока 5 подключены к входу 15, а счетные входы счетчиков подключены к входу 16 блока 9 управления.

I

Информационный вход 17 регистра 3,

является входом первого операнда устройства, информационный вход 18 регистра 7 и информационный вход 19 счетчиков являются входами второго операнда устройства. Выход 20 сумматора 4 является выходом устрой- ства. Выход 21 блока 5 является выходом завершения формирования сигна лов разрешения считывания. Информационный выход 22 коммутатора 8 соединен с информационным входом каждого сумматора 2« блока 1, установочный вход блока 5 подключен к установочному выходу 23 блока 9 управления. Информационные выходы регистров 3 и 7 соединены с информационными входами 24 и 25 коммутатора 8 соответственно, информационный выход 26 которого подключен к входу сумматора 4. Управляющий выход блока 5 соединен с управляющим входом 27 коммутатора 8, а ин- формационные входы 28 и 29 блока 5 подключены к шинам порядков первого и второго операндов устройства соответственно. Управляющий выход 30 блока 9 управления соединен с входом блока 5, вход 31 которого является входом кода операции (.КОП) устройства

Блок 5 определения очередности цифр (фиг.2) состоит из К разрядных ячеек 32 ,(-32 к, каждая из которых со- держит - триггер 33, элемент 34 задержки, элементы И 35, 36, 37, элемент НЕ 38, элемент ИЛИ 39. Кроме того все ячейки содержат

. Q О

5

0 5 0 45 JQ

,,

элемент 2И-ИЛИ 40, элемент И 41, элементы ИЛИ 42 и 43, элементы И 44 и 45, узел 46 анализа порядков операндов, который состоит из двух регистров 47 и 48, группы инверторов , сумматора 50 элементов И 51, 52, 53, группы элементов И 54,-54к, дешифратора 55.

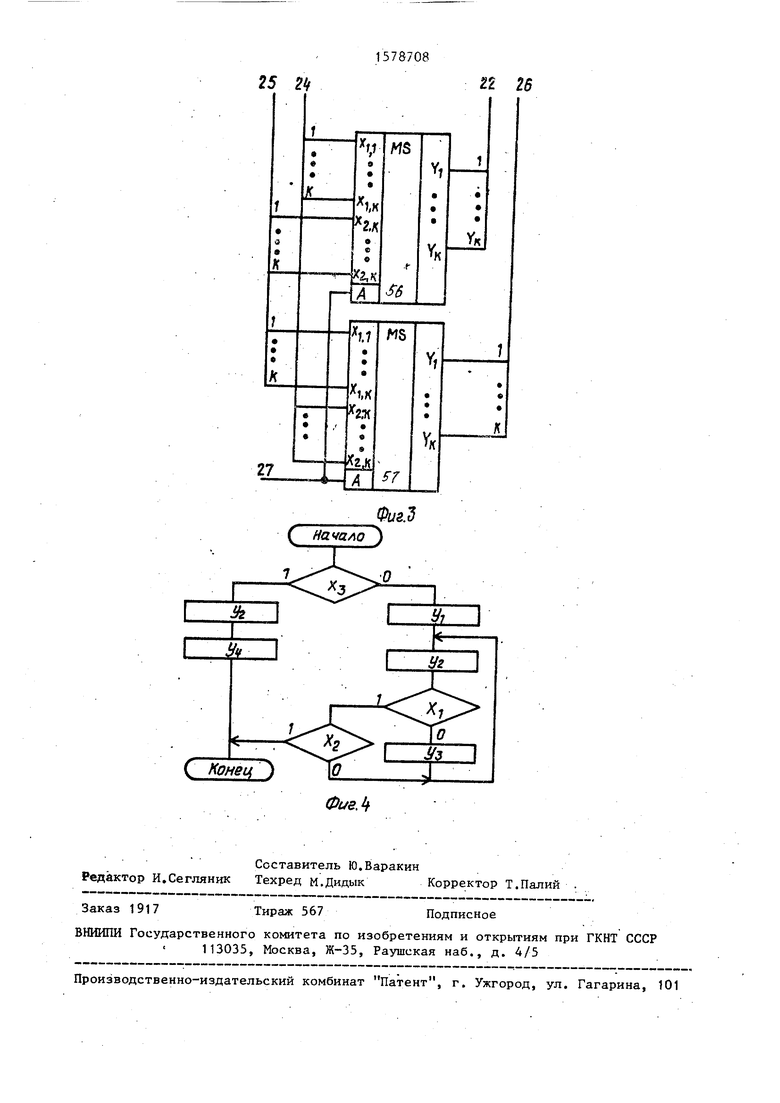

Коммутатор 8 (фиг.З) содержит два мультиплексора 56 и 57, причем первая группа входов мультиплексора 57 и вторая группа входов мультиплексора 56 соединены с группой входов 24 коммутатора 8, а вторая группа входов мультиплексора 56 и первая группа входов мультиплексора 57 соединены с группой входов 25 коммутатора 8. Выходы мультиплексора 56 являются выходами 22 коммутатора 85 выходы мультиплексора 57- выходами 26 коммутатора 8, вход 27 которого подключен к адресному входу мультиплексоров 56 и 57.

Арифметическое устройство работает следующим образом.

При выполнении операции сложения слагаемые А я В записываются в регистры 3 и 7 по входам 17 и 18 соответ- ственно, а их порядки РА и РВ - в блок 5 по входам 28 и 29 соответственно. Сумматор 4 и сумматоры блока 1 обнулены.

Блоком 5 определяется разность порядков |РА-РВ| и значение сигнала переноса РП, которое свидетельствует

0соотношении величин РА и РВ: , если и , если . Если , то коммутатор 8 разрешает запись в сумматора содержимого регистра 3, в противном случае в сумматоры ц блока 1 записывается через коммутатор 8 содержимое регистра 7. Одновременно с записью одного из слагаемых в сумматоры 2ц-2к блока

1в сумматор 4 записывается второе слагаемое через коммутатор 8. В следующий такт работы устройства по управляющему сигналу на выходе 13 блока 5 выполняется считывание содержимого одного из сумматоров к

блока 1 в сумматор 4, причем номер задействованного сумматора

блока 1 определяется величиной

.

((РА-РВ|+1), поскольку номер первого сумматора 2 соответствует величине IPA-PB 0. С учетом связей между сумматорами блока 1 и сумматором 4 в последний будет переписана информация с соответствующим сдвигом на величину JPA-PBJ в сторону старших разрядов. Таким образом, в сумматоре 4 будет выполнена операция сложения двух слагаемых с учетом выравнивания их порядков.

При выполнении операции умножения множимое Л записывается в регистр 3 по шине 17, множитель В записывается в сметчики 6,-6 к по шине 1У такиг-f образон, что i-я десятичная цифра К-разрядного множителя В записывается в i-й десятичный счетчик 6. Все RS- триггеры 33 блока 5 устанавливаются в единичное состояние по сигналу У , поступающему с выхода 23 блока 9 управления на управляющий вход блока 5. Сумматоры 2,|-2к блока 1 и сумматор 4 обнулены. Блоком 5 выполняется анализ цифр множителя с учетом сигналов нулевого содержимого всех десятичных счетчиков (., поступающих на вход 11 блока 5, и при наличии сигнала опроса У, поступающего с выхода 15 блока 9 управления.

В случае, если присутствует сигнал нулевого содержимого в счетчике , происходит формирование сигнала разрешения считывания информации из 1-го сумматора 2 блока 1, поступающего с выхода 13 блока 5 на вход управления считыванием соответствующего 1-го сумматора 2. А поскольку в данном случае информация во всех сумматорах

10

в данном цикле% Этот процесс повторя ется до тех пор, пока не появится сигнал признака нуля на входе 21 бло ка 9 управления.

Считывание информации из регистра 3 и анализ информации блоком 5 выпол няется по управляющему сигналу на выходе 15 блока 9 управления, а умен шение на единицу содержимого всех счетчиков по управляющему сигналу, поступающему с выхода 16 блока 9 управления на счетные входы всех счетчиков 6,,-бк. Таким образом, результа 15 находится в сумматоре 4, в регистре 3 сохраняется множимое А, а все сумматоры 2ц-2% блока 1 и счетчики обнулены,.поскольку считывание инфор мации из сумматоров 2 f-2« происходит с обнулением.

Блок 5 определения очередности цифр (фиг.2) работает следующим обра зом.

При выполнении операции умножения на входе 31 блока 5 отсутствует единичный сигнал. Первоначально по сигналу У|. поступающему с выхода 23 блока 9 управления, происходит установка в единичное состояние RS-триг- геров 33 с учетом сигналов нулевого содержимого на входах 11 всех разряд ных ячеек . В случае наличия сигнала нулевого содержимого в соответствующих разрядных ячейках блока появляется единичный сигнал на выхо20

25

30

к блока 1 равна нулю, то соответ- Де элемента И 37, который через элествующие разряды сумматора 4 останутся в нулевом состоянии. Одновременно со считыванием информации из определенного сумматора выполняется суммирование содержимого соответствующих сумматоров к с множимым А, поступающим с выхода 22 коммутатора 8, по сигналам управления с выхода 12 блока 5.

Затем происходит уменьшение на единицу содержимого всех счетчиков 6|-6({. В следующем цикле работы уст- ройства снова анализируется содержимое счетчиков блоком 5 и выполняется считывание кратного множимого из определенного сумматора 21, соответствующего счетчику 61, содержимое которого обнулялось, и выполняется формирование кратных множимого путем суммирования с содержимым регистра 3 в сумматорах , соответствующих счетчикам , в которых информация не равна нулю и уменьшится на единицу

40

мент ИЛИ 39 поступает на R-вход RS- триггера 33 и устанавливает его в нулевое состояние, что соответствует формированию сигнала завершения считывания информации из соответствующих сумматоров блока 1. В случае отсутствия сигнала нулевого содержимого в соответствующих разрядных ячей -5 ках нулевой сигнал на выходе элемента И 37 через элемент НЕ 38 поступает на S-вход RS-триггера 33 и устанавливает его в единичное состо яние. Это означает,, что соответствующие разрядные ячейки готовы к формированию управляющих сигналов суммирования и чтения в процессе работы устройства.

55 Основная задача блока 5 заключает7 ся в выделении десятичного разряда множителя, в котором информация равна нулю в данный такт работы устройства. При этом просмотр разрядов выгголняет50

0

в данном цикле% Этот процесс повторяется до тех пор, пока не появится сигнал признака нуля на входе 21 блока 9 управления.

Считывание информации из регистра 3 и анализ информации блоком 5 выполняется по управляющему сигналу на выходе 15 блока 9 управления, а уменьшение на единицу содержимого всех счетчиков по управляющему сигналу, поступающему с выхода 16 блока 9 управления на счетные входы всех счетчиков 6,,-бк. Таким образом, результат 5 находится в сумматоре 4, в регистре 3 сохраняется множимое А, а все сумматоры 2ц-2% блока 1 и счетчики % обнулены,.поскольку считывание информации из сумматоров 2 f-2« происходит с обнулением.

Блок 5 определения очередности цифр (фиг.2) работает следующим образом.

При выполнении операции умножения на входе 31 блока 5 отсутствует единичный сигнал. Первоначально по сигналу У|. поступающему с выхода 23 блока 9 управления, происходит установка в единичное состояние RS-триг- геров 33 с учетом сигналов нулевого содержимого на входах 11 всех разрядных ячеек . В случае наличия сигнала нулевого содержимого в соответствующих разрядных ячейках блока 5 появляется единичный сигнал на выхо0

5

0

Де элемента И 37, который через Де элемента И 37, который через эле0

мент ИЛИ 39 поступает на R-вход RS- триггера 33 и устанавливает его в нулевое состояние, что соответствует формированию сигнала завершения считывания информации из соответствующих сумматоров блока 1. В случае отсутствия сигнала нулевого содержимого в соответствующих разрядных ячей- 5 ках нулевой сигнал на выходе элемента И 37 через элемент НЕ 38 поступает на S-вход RS-триггера 33 и устанавливает его в единичное состояние. Это означает,, что соответствующие разрядные ячейки готовы к формированию управляющих сигналов суммирования и чтения в процессе работы устройства.

5 Основная задача блока 5 заключает7 ся в выделении десятичного разряда множителя, в котором информация равна нулю в данный такт работы устройства. При этом просмотр разрядов выгголняет0

ся, начиная с младшего разряда множителя, т.е. с младшего счетчика 6. Если сигнал нулевого содержимого поступает, например, с выхода первого счетчика 6, то при наличии сигнала опроса на выходе элемента И 41, на который поступают сигналы со входа 31 блока 5 и выхода 15 блока 9 управления, появляется единичный сигнал на выходе элемента И 35 первой разрядной ячейки блока 5, который поступает на элемент ИЛИ 43. Единичный сигнал с выхода элемента ИЛИ 43 поступает чере выход 13 блока 5 на вход управления считыванием первого сумматора 2 блока 1. Одновременно с этим происходит появление нулевого сигнала на выходе элемента И 36, который поступает на вход элемента ИЛИ 42. С выхода эле- мента ИЛИ 42 сигнал через выход 12 блока 5 поступает на вход управления суммированием первого сумматора 2. Во всех остальных разрядных ячейках к блока 5 в связи с тем, что отсутствуют сигналы нулевого содержимого в соответствующих счетчиках 6г-6к, появляется единичный сигнал на выходе элемента И 36 и отсутствует сигнал на выходе элемента И 35. Таким образом, сигналы на выходах 12 и 13 блока 5 вызывают считывание информации из первого сумматора 2 блока 1 и запись ее в соответствующие разряды сумматора 4 и одновременно суммирование содержимого всех остальных сумматоров 2g-2 к блока 1 с содержимым регистра 3. Элемент 34 задержки во всех разрядных ячейках 32,,-32K служит для того, чтобы препятствовать прохождению единичного сигнала с выхода элемента И 35 н R-вход RS-триг- гера 33 во время считывания информации из соответствующего сумматора 2 блока 1. Возможен случай, когда одно- временно в двух или более разрядных ячейках 32,,-32 блока 5 появились сигналы нулевого содержимого, например, в разрядной ячейке 32 и 322. В этом случае появление единичного сигнала на выходе элемента И 35 первой разрядной ячейки 32 совпадает с блокировкой, которая через элемент 2И-ИЛИ 40 запрещает срабатывание элементов И 35 всех следующих разрядных ячеек 322-32. Таким образом, считывание в каждом такте работы устройства выполняется только из одного соответствующего первого сумматора 2

0 п с

5

0

5

блока 1. Одновременно с этим во вто-/ рой разрядной ячейке 32 отсутствует единичный сигнал как на выходе эле- мент.1 И 35, вызывающий считывание из второго сумматора 2 блока 1, так и на выходе элемента И 36, вызывающий суммирование содержимого второго сумматора 2 блока 1 с содержимым регистра 3, поскольку необходимое кратное в данном втором сумматоре 2 к этому моменту сформировано.

Блокировка сигнала на выходе эл#- мента И .35 в разрядных ячейках 322- 32 к снимается в том случае, если в предыдущей младшей разрядной ячейке в данный момент не формируется сигнал завершения чтения, т.е. в ней отсутствует сигнал на соответствующем входе 11 блока 5 и RS-триггер 33 находится в единичном состоянии, либо в общем случае, когда в некоторых из предыдутих младших разрядных ячеек 32/( сигнал разрешения чтения к этому моменту уже был сформирован, т.е. в них присутствует сигнал нулевого содержимого на соответствующем входе 11 блока 5, но RS-триггер 33 находится в нулевом состоянии.

Процесс считывания и накопления соответствующих кратных множимого в сумматорах 2 4-2 к блока 1 выполняется до тех пор, пока не появится единичный сигнал на входе 21 блока 9 управления, свидетельствующий о завершении формирования сигналов разрешения чтения во всех разрядных ячейках блока 5.

Блок 46 анализа порядков блока 5 при выполнении опзрации сложения работает следующим образом.

Порядки слагаемых РА и РВ записываются в регистры 47 и 48, поступая соответственно на входы 28 и 29 блока 5. С выходов регистра 48 через группу инверторов и с выходов регистра 47 информация поступает на входы сумматора 50, который на выходе формирует разность порядков |РА-РВ | и сигнал переноса Рп. Дешифратор 55 преобразует код |РА-РВ|, поступающий с выходов сумматора 50 в сигнал разрешения считывания информации из соответствующего сумматора 2, который поступает на управляющие входы сумматоров 2,|-2к при наличии единичного сигнала на выходе элемента И 52, т.е. при единичном сигнале на входе 31 Jxnoica 5 и при сигнале У на выходе 30

блока 9 управления. На выходе элемента И 53 формируется единичный сигнал, который разрешает запись информации в сумматтгн 2(-2« блока 1 в момент прихода сигнала У2 с выхода 15 блока 9 управления.

Коммутатор 8 (фиг.З) работает сле- дукшим образом.

При условии, что -О, коммутатор 8 через мультиплексор -Ъ разрешает запись информации из регистра 3 в сумматоры 2t-2k блока I и через мультиплексор 57 из регистра 7 в сумматор 4. При выполнении условия коммутатор 8 через мультиплексор 56 разрешает запись информации из регистра 7 в сумматоры 2 ц-2% блока 1 и через мультиплексор 57 из регистра 3 в сумма/ор 4. При выполнении операции умножения вгргда выголпяероя условие Р (}, которое вызывает соответствующие действия коммутатора 8.

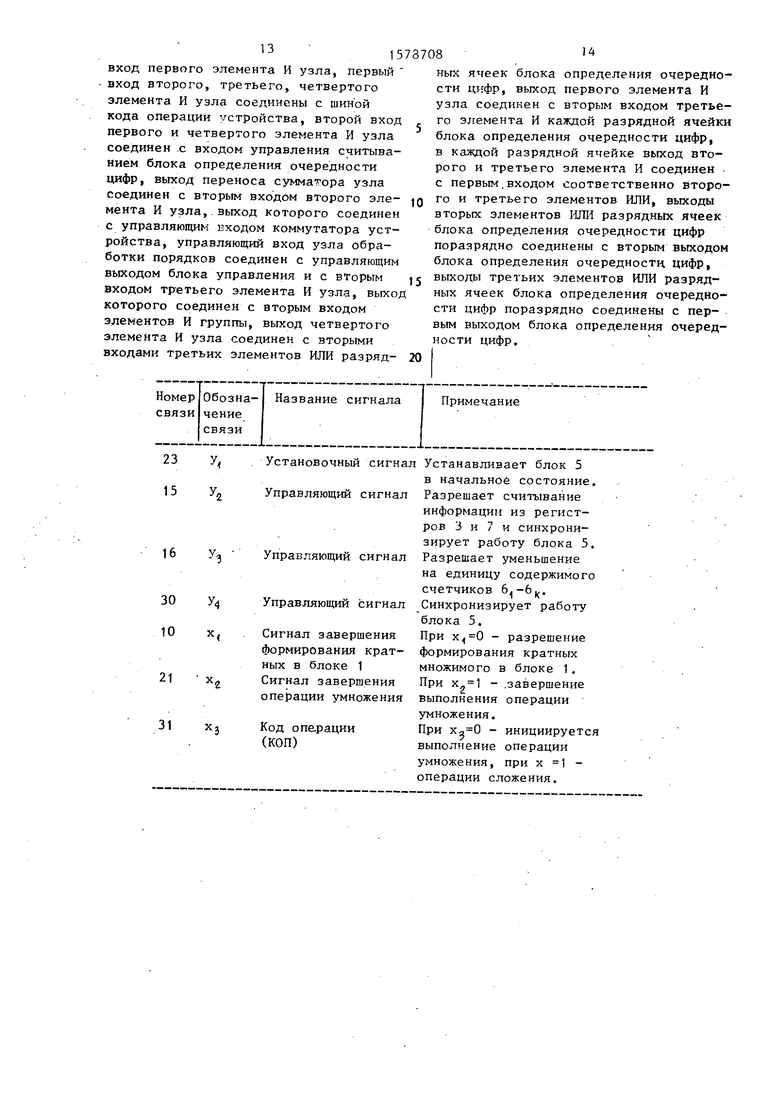

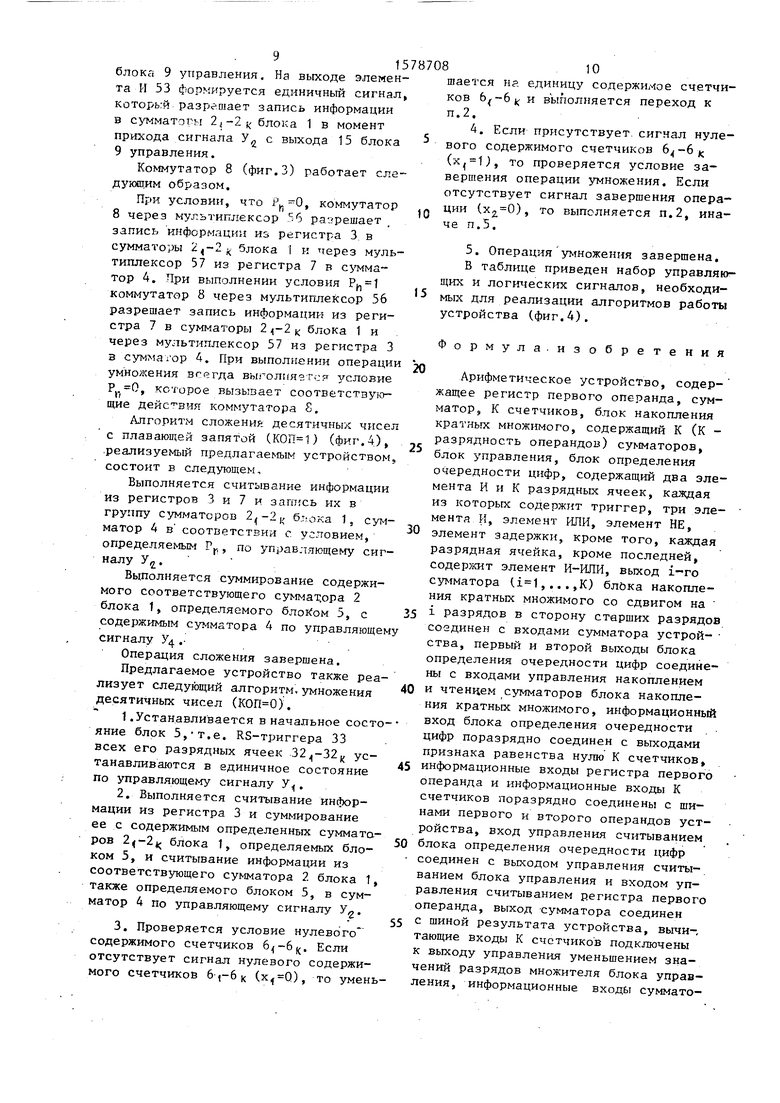

Алгоритм сложения десятичных чисел с плавающей запятой () (фиг.4), реализуемый предлагаемым устройством,, состоит в следующем,

Выполняется считывание информации из регистров 3 и 7 и запись их в группу сумматоров к 1, сумматор 4 в соответствии с условием, определяемым Р, по управляющему сигналу УЈ.

Выполняется суммирование содержимого соответствующего сумматора 2 блока 1, определяемого блокЪм 5, с содержимым сумматора 4 по управляющем сигналу У4 .Операция сложения завершена.

Предлагаемое устройство также реализует следующий алгоритм,умножения десятичных чисел ().

1.Устанавливается в начальное состояние блок 5,-т.е. RS-триггера 33 всех его разрядных ячеек ,, устанавливаются в единичное состояние по управляющему сигналу У,,.

2. Выполняется считывание информации из регистра 3 и суммирование ее с содержимым определенней сумматоров блока 1, определяемых блоком 5, и считывание информации из соответствующего сумматора 2 блока 1, также определяемого блоком 5, в сумматор 4 по управляющему сигналу У„.

3. Проверяется условие нулевого содержимого счетчиков . Если отсутствует сигнал нулевого содержимого счетчиков 6(-6 к (), то умень

8708Ю

шается н единицу содержимое счетчиков Ь(-6К и выполняется переход к п.2.

4. Если присутствует сигнал нулевого содержимого счетчиков (х.1), то проверяется условие завершения операции умножения. Если отсутствует сигнал завершения операции (), то выполняется п.2, иначе п.5.

10

5. Операция умножения завершена. В таблице приведен набор управляющих и логических сигналов, необходи- мых для реализации алгоритмов работы устройства (фиг.4).

Формула, из об ре те ния

20

5

0

Арифметическое устройство, содер- жащее регистр первого операнда, сумматор, К счетчиков, блок накопления кратных множимого, содержащий К (К - разрядность операндов) сумматоров, блок управления, блок определения очередности цифр, содержащий два элемента И и К разрядных ячеек, каждая из которых содержит триггер, три элемента И, элемент ИЛИ, элемент НЕ, элемент задержки, кроме того, каждая разрядная ячейка, кроме последней, содержит элемент И-ИЛИ, выход i-ro сумматора (,...,К) блока накопления кратных множимого со сдвигом на i разрядов в сторону старших разрядов соединен с входами сумматора устрой- ства, первый и второй выходы блока определения очередности цифр соединены с входами управления накоплением и чтением сумматоров блока накопления кратных множимого, информационный вход блока определения очередности цифр поразрядно соединен с выходами признака равенства нулю К счетчиков, 5 информационные входы регистра первого операнда и информационные входы К счетчиков поразрядно соединены с шинами первого и второго операндов устройства, вход управления считыванием 0 блока определения очередности цифр соединен с выходом управления считыванием блока управления и входом управления считыванием регистра первого операнда, выход сумматора соединен 5 с шиной результата устройства, вычи-, тающие входы К счетчиков подключены к выходу управления уменьшением значений разрядов множителя блока управления, информационные входы суммато5

0

1115

ров блока накопления кратных множимого соединены с информационным входом блока накопления кратных множимого, первые входы первых элементов И разрядных ячеек блока определения очередности цифр поразрядно соединены с информационным входом блока определения очередности ЦИФР, з. вторые входы - с установочным входом блока определения очередности цифр, который подключен к установочному выходу блока управления, в каждой разрядной ячейке блока определения очередности цифр выход первого элемента И через элемент НЕ подключен к S-входу триггера, которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и с первым входом (инверсным) третьего элемента И, а во всех разрядных ячейках, кроме последней, соеди

708

5

0

12

элементов И являются третьим и четвертым выходами блока определения очередности цифр, которые подключены к входам завершения формирования кратных и завершения формирования сигналов разрешения считывания блока управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения операции сложения чисел с плавающей запятой, в устройство введены регистр второго операнда, и коммутатор, в блок определения очередности цифр введен узел обработки порядков слагаемых, содержащий регистр порядка первого слагаемого, регистр порядка второго слагаемого, группу элементов НЕ, сумматор, дешифратор, группу элементов И, первый, второй, третий и четвертый элементы И, в каждую разрядною ячейку блока определения очередкссти цифр введены второй и третий элекенты ИЛИ. при

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения десятичных чисел | 1986 |

|

SU1410023A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах, выполняющих операции над десятичными числами. Целью изобретения является расширение функциональных возможностей устройства за счет выполнения операции сложения чисел с плавающей запятой. Для достижения поставленной цели в устройство, содержащее регистр первого операнда, сумматор, блок управления, K счетчиков, блок накопления кратных множимого, содержащий K (K - разрядность операндов) сумматоров, блок определения очередности цифр, содержащий два элемента И и K разрядных ячеек, каждая из которых содержит триггер, три элемента И, элемент ИЛИ, элемент НЕ и элемент задержки, введены регистр второго операнда, коммутатор, в блок определения очередности цифр введен узел обработки порядков слагаемых, содержащий регистр порядка первого слагаемого, регистр порядка второго слагаемого, блок элементов НЕ, сумматор, дешифратор, блок элементов И, четыре элемента И, в каждую разрядную ячейку блока определения очередности цифр введены два элемента ИЛИ с соответствующими связями. 4 ил., 1 табл.

нен также с первым входом первой груп-25 этом выход регистра первого операнда

пы входов элемента И-ИЛИ и первым входом (инверсным) второй группы входов элемента И-ИЛИ, второй вход третьего элемента И соединен с вторым входом второго элемента И и входом управления считыванием блока определения очередности цифр, в каждой разрядной ячейке блока определения очередности цифр прямой выход триггера соединен с третьим входом второго элемента И, а во всех разрядных ячейках, кроме последней, соединен также с вторым входом второй группы входов элемента И-ИЛИ, второй вход первой группы входов элемента И-ИЛИ каждой разрядной ячейки, кроме последней, соединен с инверсным выходом триггера, четвертый вход второго элемента И подключен к выходу элемента И-ИЛИ предыдущей разрядной ячейки блока определения очередности цифр, а во всех разрядных ячейках, кроме последней, соединен также с третьими входами первой и второй групп входов элемента И-ИЛИ, выход второго элемента И через элемент задержки подключен к второму входу первого элемента ИЛИ, входы первого элемента И блока определения очередности цифр соединены с первыми входами первых элементов И разрядных ячеек, инверсные выходы триггеров которых соединены с входами второго элемента И блока определения очередности цифр, выходы первого и второго

0

соединен с первым информационным входом коммутатора, вход управления считыванием регистра первого операнда соединен с входом управления считыванием регистра второго операнда, информационный вход которого соединен с шиной второго операнда, информационный выход регистра второго операнда соединен с вторым информационным входом коммутатора, первый информацион- 5 ный выход которого соединен с соответствующим входом сумматора, второй информационный выход коммутатора соединен с информационным входом блока накопления кратных множимого, шина порядка первого операнда соединена с информационным входом регистра порядка первого операнда, выход которого порязрядно соединен с первым входом сумматора узла обработки порядков, шина порядка второго операнда соединена с информационным входом регистра порядка второго операнда, выход которого поразрядно через группу элементов НЕ соединен с вторым входом сумматора узла обработки порядков, выход суммы которого соединен с входом дешифратора узла, выход которого поразрядно соединен с первым входом элементов И группы, выход которого поразрядно соединен с первым входом второго элемента ИЛИ каждой разрядной ячейки блока определения очередности цифр, первый (инверсный)

5

0

5

вход первого элемента И узла, первый вход второго, третьего, четвертого элемента И узла соединены с шиной кода операции -устройства, второй вход первого и четвертого элемента И узла соединен с входом управления считыванием блока определения очередности цифр, выход переноса сумматора узла соединен с вторым входом второго элемента И узла, выход которого соединен с управляющим входом коммутатора устройства, управляющий вход узла обработки порядков соединен с управляющим выходом блока управления и с вторым входом третьего элемента И узла, выход которого соединен с вторым входом элементов И группы, выход четвертого элемента И узла соединен с вторыми входами третьих элементов ИЛИ разряд-

16 У-j Управляющий сигнал

Управляющий сигнал

Сигнал завершения формирования кратных в блоке 1

Сигнал завершения операции умножения

Код операции

(КОП)

0

0

5

ных ячеек блока определения очередности цифр, выход первого элемента И узла соединен с вторым входом третьего элемента И каждой разрядной ячейки блока определения очередности цифр, в каждой разрядной ячейке выход второго и третьего элемента И соединен с первым входом соответственно второго и третьего элементов ИЛИ, выходы вторых элементов ИЛИ разрядных ячеек блока определения очередности цифр поразрядно соединены с вторым выходом блока определения очередности, цифр, выходы третьих элементов ИЛИ разрядных ячеек блока определения очередности цифр поразрядно соединены с первым выходом блока определения очередности цифр.

информации из регистров 3 и 7 и синхронизирует работу блока 5. Разрешает уменьшение на единицу содержимого счетчиков . Синхронизирует работу блока 5.

При - разрешение формирования кратных множимого в блоке 1. При х 1 - завершение выполнения операции умножения.

При - инициируетс выполнение операции умножения, при х 1 - операции сложения.

и и

25 21}

( На vaАО 3

С Конец j

Фиа.Ь

Составитель Ю.Варакин Редактор И.Сегляник Техред м.Дидык Корректор Т.Палий

Заказ 1917

Тираж 567

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

П 26

Подписное

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-15—Публикация

1988-09-07—Подача