112

Изобретение относится к электросвязи и может быть использовано в системах передачи данных, в том числе а цифровых: системах с импульсио-кодо- в о и мод ул я ци е и.

Цель изобретения - сокращение времени фазирования.

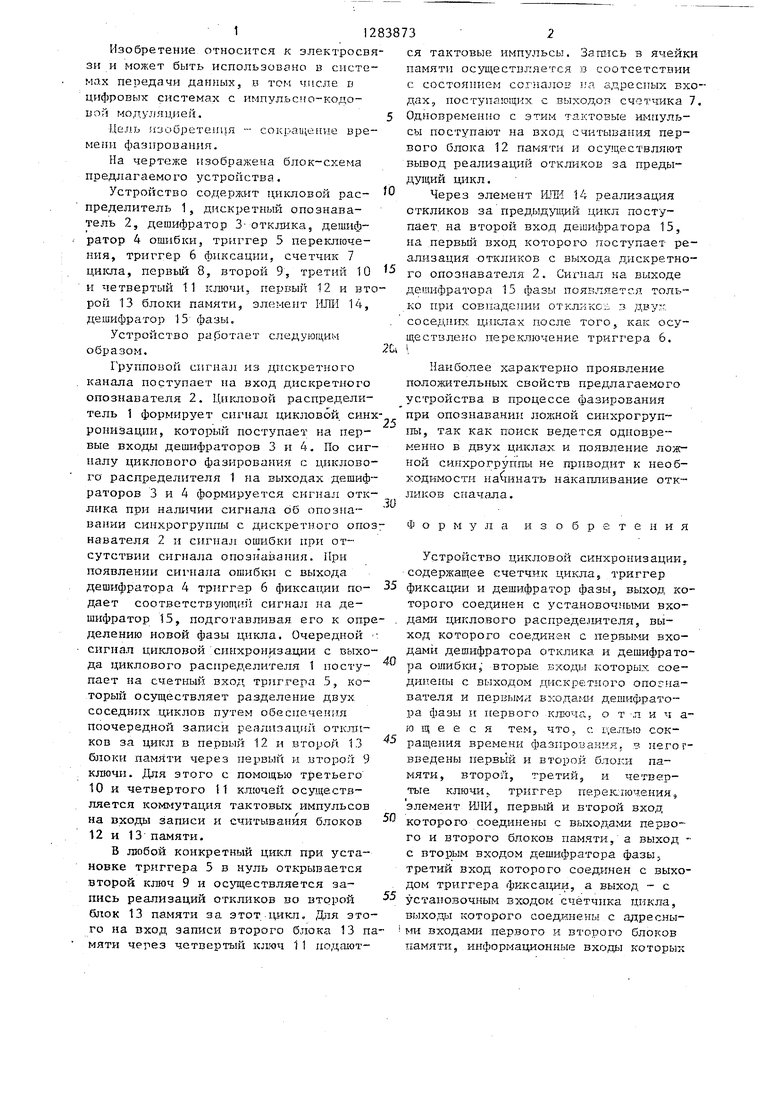

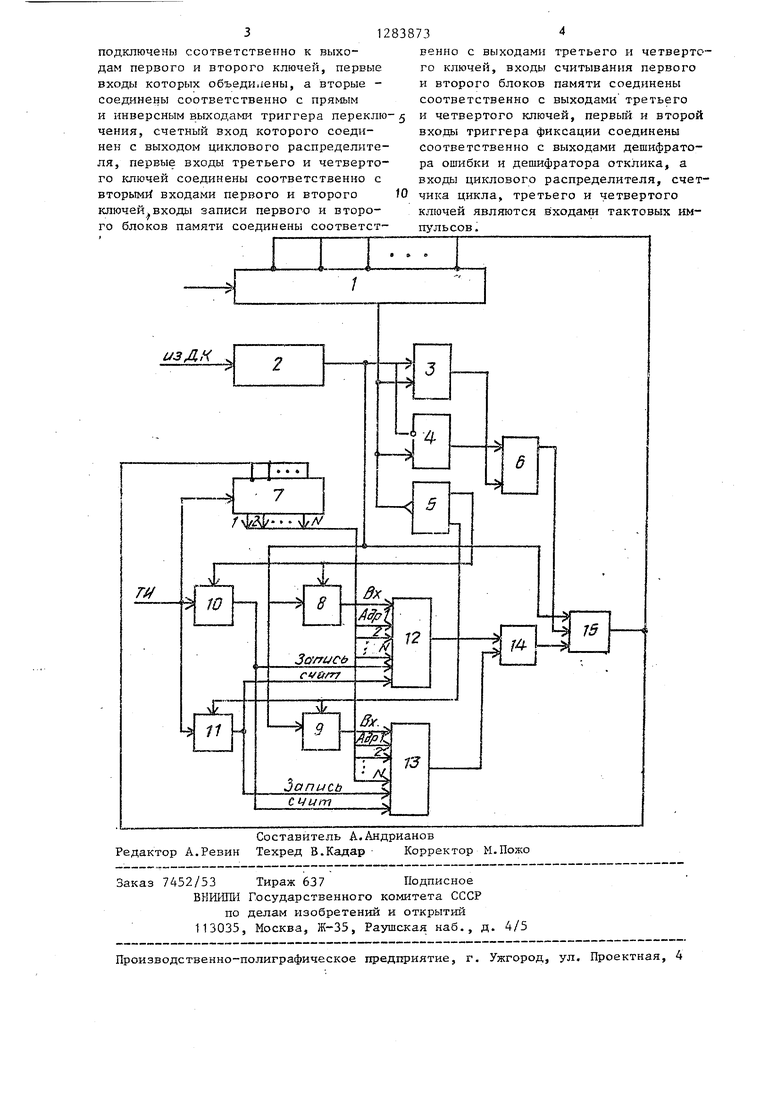

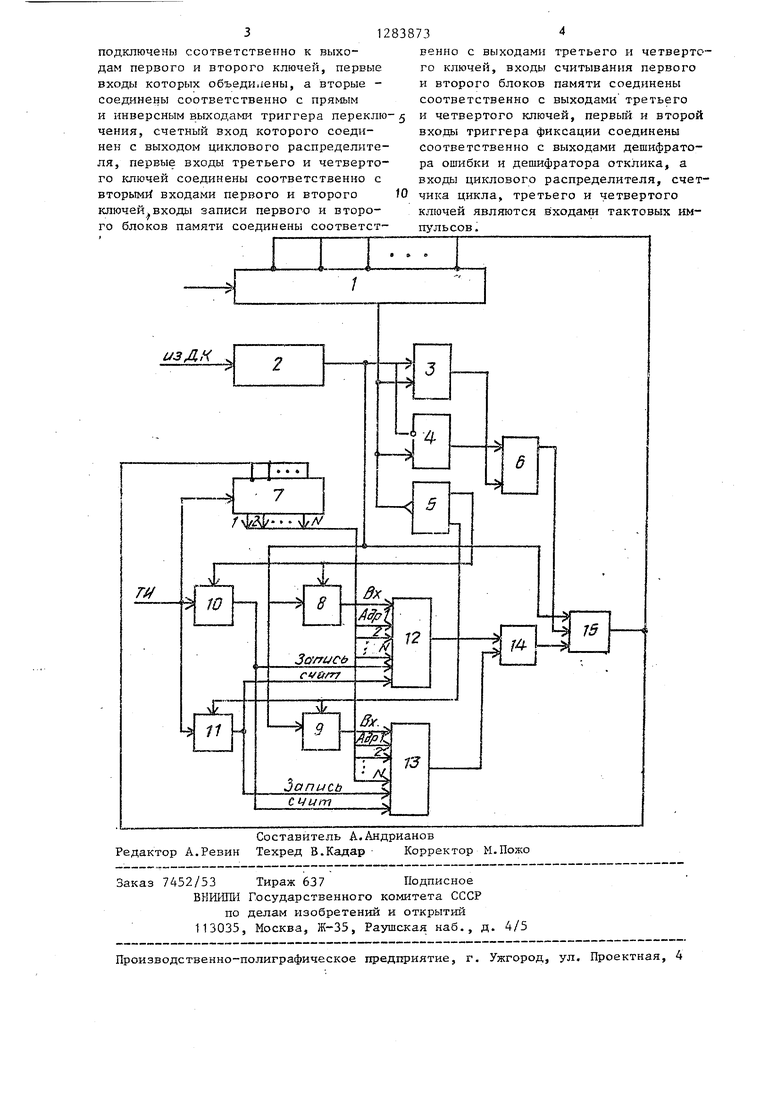

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содерлсит цикловой распределитель 1, дискретный опознава- тель 2, дешифратор 3 oTKjniKa, дешифратор 4 ошибки, триггер 5 перегшгаче- ния, триггер 6 фиксации, счетчик 7 ци1сла, первьй В, второй 9, третий 10 и четвертый 11 ключи, первый 12 и втрой 13 блоки памяти, элемент ЩТИ 14, дешифратор 15 фазы.

Устройство работает следующие; образом.

Групповой сигнал из дискретного канала поступает на вход дискретного опознавателя 2. Цикловой распределитель 1 формирует сигнал цикловой, синронизации, который поступает на первые входы дешифраторов 3 и 4. По сигналу циклового фазирования с циклового распределителя 1 на выходах дешифраторов 3 и 4 формируется сигнал отк

лика при наличии сигнала об опозна- ва1ши синхрогруппы с дискретного опонавателя 2 и сигнал ошибки при отсутствии сигнала опознавания. При появлении сигнала ошибки с выхода дешифратора 4 триггер 6 фиксап,ии по- дает соответствующий сигнал на дешифратор 15, подготавливая его к опр делению новой фазы цикла. Очередной сигнал цикловой синхронизации с выхода циклового распределителя 1 поступает на счетный вход триггера 5, который осуществляет разделение двух соседних циклов путем обеспечения поочередной записи реализаций откликов за цикл в первы51 12 и второй 13 блоки памяти через первый и второй 9 ключи. Для этого с помощью третьего 10 и четвертого 11 ключей осуществляется ком утация тактовых импульсов на входы записи и считывания блоков 12 и 13 памяти.

В конкретный цикл при установке триггера 5 в нуль открывается второй ключ 9 и ос тцествляется запись реализаций откликов во второй блок 13 памяти за этот 1щкп. Для этого на вход записи второго блока 13 пмяти четвертый ключ 1 1 подают

O

15

U

25

ся тактовые импульсы. Запись в ячейки памяти осуществляется в соотсетствии с состоянием согналов i;a адресных входах, поступа ощих с выходов счетчика 7. Одновременно с этим тактовые импульсы поступают на вход считывания первого блока 12 памяти и осуществляют вывод реализаций откликов за предыдущий цикл.

Через элемент ffiH-i 14 реализация откликов за предыду1ций цикл поступает, на второй вход дешифратора 15, на перрзый вход которого поступает реализация откликов с выхода дискретного опознавателя 2. Сигнал на выходе дешифратора 15 фазы появляется только при совпадении отклике;:, з дву:; соседних Ц1ислах после того, как осуществлено переключение триггера 6.

Наиболее характерпо проявление положительных свойств предлагаемого устройства в процессе фазирования при опознавании лолшой синхрогруппы, так как поиск ведется одновременно в двух циклах и появление ложной синхрогруппы не приводит к необходимости на гинать накапливание откликов сначала.

Формула изобретения

Устройство цикловой синхронизации, содержащее счетчик цикла, триггер фиксации и дешифратор фазы, выход которого соединен с установочными входами циклового распределителя, выход которого соединен с первыми входами дешифратора отклика и дешифратора ошибки, вторые входы которых соединены с выходом дискретного опогна- вателя и первыми входами дешифратора фазы и первого ключа, о тли ч а- ю щ е е с я тем, что, с целью сок- ращения времени фазирования, в негог- введены первый и второй блоки памяти, второй, третий, и четвертые ключи.. триггер перек:1ючения5 элемент ИЛИ, первый и второй вход которого соединены с выходами первого и второго блоков памяти, а выход - с вторым входом дешифратора фазы, третий вход которого соединен с выходом триггера фкксагд и, а выход - с установочным входом счетчпка цикла, выходы которого соединены с адресны- №-1 входами первого и второго блоков памяти, информационные входы которых

подключены соответственно к выховходы KOTOpt)TX объединены, а вторые - соединены соответственно с прямым и инверсным выходами триггера переклю чения, счетный вход которого соединен с выходом циклового распределителя, первые входы третьего и четвертого ключей соединены соответственно с вторыми входами первого и второго ключей.входы записи первого и второго блоков памяти соединены соответст83873

венно

Ш с выходами третьего и четвертого ключей, входы считывания первого и второго блоков памяти соединены соответственно с выходами третьего и четвертого ключей, первый и второй входы триггера фиксации соединены соответственно с выходами дешифратора ошибки и дешифратора отклика, а входы циклового распределителя, счетчика цикла, третьего и четвертого ключей являются в ходаьш тактовых импульсов.

Составитель А.Андрианов Редактор А.Ренин Техред В.Кадар- Корректор М.Пожо

Заказ 7452/53 Тираж 637 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1987 |

|

SU1529284A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство синхронизации по циклам | 1989 |

|

SU1672579A2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

Изобретение относится к электросвязи и может использоваться в цифровых системах с импульсно-кодо- вой модуляцией. Цель изобрения - сокращение времени фазирования. На дискретный опознаватель 2 постуйает групповой сигнал. По сигналу цифрового фазирования, поступающему с циклового распределителя 1, дешифратор 3 отклика и дешифратор 4 ошибки формируют соответственно сигнал отклика при опознавании синхрогруппы и сигнал опшбки при отсутствии сигнала опознавания. Триггер 5 переключения осуществляет разделение двух соседних циклов, обеспечивая поочередную запись реализации откликов через ключи 8, 9 в блоки памяти 12, 13. Ключи 10, 11 осуществляют коммутацию тактовых импульсов на запись и считывание из блоков памяти 12, 13. Запись в ячейки памяти осуществляется по адресам, сформированным счетчиком 7 цикла. При появлении с дешифратора 4 сигнала ошибки триггер 6 фиксации подает сигнал на дешифратор 15 фазы, подготавливая его к определению новой фазы цикла. Сигнал на его выходе появляется только при совпадении в двух соседних циклах откликов, проходящих через элемент ИЛИ 14, после переключения триггера 6. 1 ил. (Л

| Заводское описание аппаратуры Думка, ТО,ч.11, ячейка 1 МФ ЗТ.З | |||

| Станок для накатывания резьбы | 1950 |

|

SU89044A2 |

| Минск, завод Промсвязь, 1979. | |||

Авторы

Даты

1987-01-15—Публикация

1985-03-21—Подача