сл

О1

ьэ

ijcJiH следующие за ним k n-символьных .комбилацнй являются разрешенным сло- )шм опознавания синхроблока (адреса), Истинное синхросло во вызывает появление декодированного адреса синхро- (5лока на выходной шине 15 адреса и 1|;двиг данных на выходной шине 8. Ес- и нослё истинного ОТКЛИКИ в течение тактов воспроизводимой тактовой

астоты, где N равно либо числу бит

синхроблоке, либо числу бит в пре- мбуле (в случае соответствия вьще- енных слов опознования адресу преам

булы), не был зарегистрирован новый отклик, то считается, что очередная синхрогруппа Поражена ошибками н адрес синхроблока получается увеличением на единицу адреса предьщу- щего синхроблока. Это позволяет избежать нарушений цикловой синхронизации и обеспечить правильное декодирование воспроизводимой информации в случае сбоев синхрогрупп ошибками при низкой вероятности нарушения цикловой синхронизации из-за сложных синхрогрупп. 1 з.п.ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1986 |

|

SU1377906A1 |

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1985 |

|

SU1278970A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

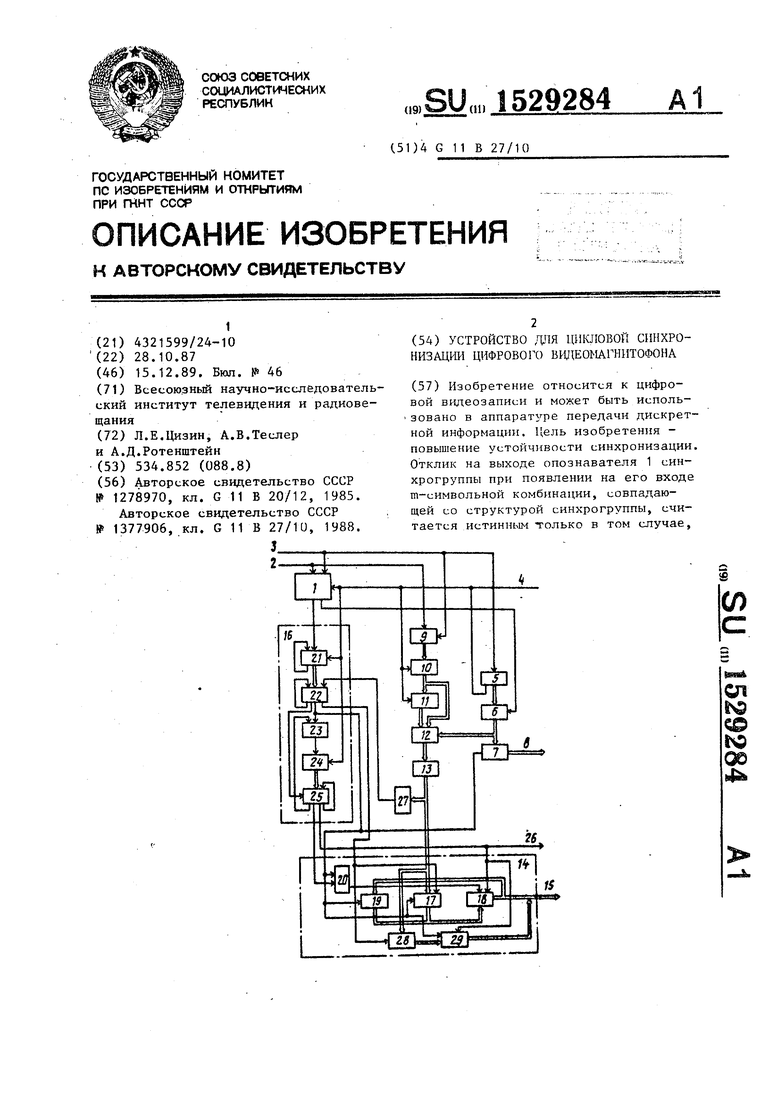

Изобретение относится к цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации. Цель изобретения - повышение устойчивости синхронизации. Отклик на выходе опознавателя 1 синхрогруппы при появлении на его входе M символьной комбинации, совпадающей со структурой синхрогруппы, считается истинным только в том случае, если следующие за ним K N - символьных комбинаций являются разрешенным словом опознавания синхроблока (адреса). Истинное синхрослово вызывает появление декодированного адреса синхроблока на выходной шине 15 адреса и сдвиг данных на выходной шине 8. Если после истинного отклика в течение N тактов воспроизводимой тактовой частоты, где N равно либо числу бит в синхроблоке, либо числу бит в преамбуле (в случае соответствия выделенных слов опознавания адресу преамбулы), не был зарегистрирован новый отклик, то считается, что очередная синхрогруппа поражена ошибками и адрес синхроблока получается увеличением на единицу адреса предыдущего синхроблока. Это позволяет избежать нарушений цикловой синхронизации и обеспечить правильное декодирование воспроизводимой информации в случае сбоев синхрогрупп ошибками при низкой вероятности нарушения цикловой синхронизации из-за сложных синхгрупп. 1 з.п. ф-лы, 1 ил.

Изобрете ие относится к аппарату- е цифровой видеозаписи информации. Цель изобретения - повышение ус- т|ойчивости цикловой синхронизации.

Па чертеже представлена структур- н|ая схема устройства.

Устройство для цикловой синхрониза- пйи цифрового видеомагнитофона содержит цпознаватель 1 синхронизации,подключен- .ш входами к информационной шине первой 3 и второй 4 шинам такто- вЬй синхроиизащн-1, первая из которых срединена с входом счетчика 5, подклю- енного одним выходом к второй шине 4 актовой синхронизации и остальными ыходами через последовательно соединенные первый 6 и второй 7 регистры к первой выходной шине 8, после- розательно соединенные первый регистр

сдвига,, третий 10 и четвертьш 11 р егйстры, второй регистр 12 сдвига, елок 13 памяти и решающий блок 14, выход кото рого подключен к второй пине 15, блок 16 управления, включен- ььш между первым выходом огюзнавате- ля 1 синхрогруппы и управляющими Еходами решающего блока 14, включающего соединенные последовательно первый 17 и второй 18 регистры, входы п|ервого из которых являются входами решающего блока 14, сумматор 19, включенный между входами и выходами второго регистра 18, выходы крторого являются выходами решающего блока 14, элемент ИЛИ 20, выходом подключенный к синхронизируюп1ему входу второ- г1о регистра 18. Блок 16 управления включает последовательно соединенные первый счетчик 21, первый блок 22 памяти, элемент ШШ 23, второй счетчик 24 и второй блок 25 памяти, первый

0

выход которого соединен с вторым входом элемента ШШ 23, второй выход - с третьей выходной шиной 26, третий выход с первым входом элемента ИЛИ 20 решающего блока 14, второй вход которого соединен с управляющими входами

сумматора 19,. регистров 17 и 7 и первым .выходом блока 22 памяти. При этом второй выход опознавателя 1 синхрогруппы соединен с управляющим входом регистра 6, выходы которого соединены с второй группой входов регистра 12 сдвига, третья группа входов которого соединена с выходами регистра 10. Информационная шина 2 подключена к выходу регистра 9, синхрони- зирующий вход которого соединен с

5 шиной 3 тактовой синхронизации. Шина 4 тактовой синхронизации соединена с синхронизирующими входами счетчиков 21 и 24 и регистров 10 и 11. Второй выход блока 22 памяти подключен к синхронизирующему входу регистра 17. Устройство содержит также блок 27 памяти контроля адреса, включенный между выходами блока 13 памяти и адресными входами блока 22 памяти блока 16 управления, в котором дополнительный выход первого счетчика 21 соединен со своим управляющим входом, третий выход блока 22 памяти подключен к своему управляющему входу, четвертый выход - к первому управлядоще- му входу блока 25 памяти, второй управляющий вход которого соединен со своим четвертым выходом. Решающий блок 14 содержит дополнительно тре5 тий 28 и четвертый 29 регистры, входы первого из которых подключены к входам регистра 17, а выходы - через регистр 29 к выходной шине 15. При

0

5

0

этом синхронизирующие входы регистров 18 и 29 подключены к шине 26, управляющий вход регистра 29 подключен к управляющему входу регистра 17, а синхронизирующий вход регистра 28 соединен с вторым выходом блока 22 памяти блока 16 управления.

Устройство для цикловой синхронизации цифрового видеомагнитофона работает следующим образом.

Выделение синхрослов осуществляется в опознавателе 1 синхрогруппы, на который воспроизводимые данные поступают по информационной шине 2, а импульсы воспроизводимой тактовой частоты по шине 3 тактовой синхронизации. Счетчик 5 импульсов формирует импульсы тактовой частоты f дeлe- нием частоты F где п - число символов в словах воспроизводимых данных. Состояние на выходах счет.чи- ка 5 импульсов определяет местоположение первого символа адреса синхро- блока, отмечаемое появлением на втором выходе опознавателя 1 синхрогруппы при вьщелении синхрослова сигнала hs длительностью в период частоты F. В первом регистре 6 запоминается состояние счетчика 5 импульсов, соответствующее моменту появления сигнала hs. Кроме того, выделение синхрослова в опознавателе 1 синхрогруппы сопровождается откликом hsw на его втором выходе в виде сигнала длительностью в период тактовой частоты f. Этот отклик может быть как истинньп4,так и ложный.Поэтому с целью подтверждения достоверности отклика производится проверка .следующих за выделенным синхрословом комбинаций символов На их соответствие разрешенному алфавиту адресов синхроблока. Для зто- го воспроизводимые данные по информационной шине 2 поступают на вход регистра 9 сдвига-, на выходе которого имеются п-разрядные комбинации, следующие с частотой F. В регистрах 10 и 11 .эти комбинации переписываются с тактовой частотой f и поступают в виде (2п - 1)-разрядной комбинации на вход регистра 12 сдвига. На выход регистра 12 сдвига поступают п-разрядные комбинации, выбранные из входных (2п - 1)-разрядных комбинаций путем сдвига, величина которого определена состоянием выходов.регистра 6. Эти выбранные п-разрядные комбинации поступают на вход блока 13памяти опознавателя адреса, в котором осуществляется декодирование их в соответствии с алгоритмом кодирования адресов синхроблока. Декодированные комбинации поступают на блок 27 памяти контроля адресов, Е котором определяется соответствие входных комбинаций разрешающим адресам перQ вого и второго байтов адресов в соответствии с международньм стандартом по цифровой видеозиписи, а также появление адреса преамбул сектором видеозаписи. Все эти команды поступа5 ют на адресные входы первого блока 22 памяти проверки истинности hsw блока 16 управления, В то же время на другие адресные входы блока 22 памяти поступают сигналы с выхода

0 счетчика 21 импульсов. которьп1 запускается сигналом hsw и через определенное число тактов, необходимое для определения истинности сигнала hsw, останавливается посредством вве5 денной обратной связи, позволяющей избежать возможности принятия решения поступления очередного спнхросло- ва при отсутствии тактового. В блоке 22 памяти обрабатываются команды, поступающие с второго блока 27 памяти, только на тех временных позициях, которые соответствуют местоположению слов адреса синхроблока в предполохсении, что отклик опознавателя 1 синхрогруппы истинньш. Кроме того, с второго выхода блока 22 памяти передаются стробирующие сигналы на синхронизирующие входы регистр в 17 и 28 решающего блока 14 для записи соответственно первого и второго байта адреса. Поскольку в соответствии с международным стандартом по цифровой видеозаписи приходится анализировать два байта адреса, необходима фиксация ошибки, возникающей при принятии решения об ошибке в первом байте адреса. Дпя этой цели в блок 22 памяти введена обратная связь. Если в блок 22. памяти не поступают команды с блока 27 памяти об ошибках в словах адреса, то в блоке 22 памяти блока 16 управления принимается решение, что отклик опознавателя 1 синхрогруппы является истинным, и вырабатывается сигнал

5 has, по которому регистр 7 запоминает состояние на выходах регистра 6. Кроме Того, этот сигнал разрешает перезапись в регистр. 29 решающего

0

5

0

5

0

блока 14 второго байта адреса синхро блока, предпарнтельио записанных в регистр 28. При этом на вьгходе схемы Ilini 20 решающего блока 14 появляется сигнал, разрешающий запись этих комбинаций с выхода 17 во второй регист 18 решающего блока 14 и отключающий выходы сумматора 19 от входов второ- j o регистра 18. Сигнал has поступает на схему ИШ1 23 блока 16 управления, вызывая появление на ее выходе сиг- пала, фазирующего счетчик 24, сигналы с выходов которого поступают на входы блока 25 памяти блока 16 управления. Счетчик 24 и блок 25 памяти блока 16 управления работают образом что если очередной сигнал has на первый вход схемы ИЛИ 23 не поступил, что через фиксированное количество тактов на выходе блока 25 памяти появляется сигнал, поступающий на второй вход схемы ИЛИ 23 и вызывающш фазирование счетчика 24 импульсов блока 16 управле- ь ияо Это фиксированное количество тактов фазирования счетчика 24 им- иульсов определяется сигналом появ- лания адреса преамбулы. В случае при иятнл решения о наличии преамбулы количество такто.в в первом цикле при (газировании счетчика 24 определяет- :я длиной преамбулы, а затем в случае сбоя синхроинформацни в последу- i,iii,ux синхроблоках длина цикла фазирования определяется длиной синхро- блока, что позволяет значительно по- ъысить помехозащтценность первых син хроблоков секторов записи. Это дости г-ается введе 1ием обратной связи в блоке 25 памяти блока 16 управления Кроме того, с выхода блока 25 памяти поступают еще два сигнала. Один из I UK вызывает появление сигнала на выходе схемы РШИ 20 решающего блока 14, разрешающего запись во второй 1 егистр 18 комбинации символов с выходов сумматора 19 решающего блока 14, которые представляют собой адрес иредьщущего синхроблока, увеличенный на единицу. Второй выход блока 25 , памяти является выходной шиной 26, в 1чоторой, в частности, присутствуют команды управления считывания адреса поступающие на управляющие входы регистров 18 и 29 решающего блока 14. Формула изобретения

Устройство для цикловой синхро иизации цифрового видеомагнитофона.

0

5

0

5

0

5

0

5

0

5

содержащее опознаватель синхрогруппы, подключенный входами к информационной шине и первой и второй шинам тактовой синхронизации, первая из которых соединена с входом счетчика, подключенного одним выходом к второй шине тактовой синхронизации и остальными выходами через последовательно соединенные первый и второй регистры к первой выходной шине, последовательно соединенные первый регистр сдвига, третий, четвертый регистры, второй регистр сдвига, блок памяти и решающий блок, выход которого подключен к второй выходной шине, блок управления, включенный между первым выходом опознавателя синхрогруппы и управляю- щими входами решающего блока, включающего соединенные последовательно первый-и второй регистры, входы первого из которых являются входами решающего блока, сумматор, включенный между входами и выходами второго регистра, выходы которого являются выходами решающего блока, элемент ШШ, выходом подключенный к синхронизирующему входу второго регистра, блок управления включает последовательно соединенные первый счетчик, первый блок памяти, элемент ИЛИ, второй счетчик и второй блок памяти, первый выход которого соедиинен с вторым входом элемента РШИ, второй выход - с третьей выходной шиной, третий выход - с первым входом элемента 1ШИ решающего блока, второй вход которого соединен с упг:а);ляющими входами сумматора и первого регистра решающего блока, второго регистра и первым выходом первого блока памяти блока управления, при этом второй выход опознавателя синхрогруппы соединен с управляющим входом первого регистра, выходы которого соединены с второй группой входов второго регистра сдвига, третья группа входов которого соединена с выходами третьего регистра, информационная шина подключена к входу первого регистра сдвига, синхронизирующий вход которого соединен с первой шиной такто- вой синхронизации, в-торая шина тактовой синхронизации соединена с синхронизирующими входами первого и второго счетчиков блока управления и четвертого регистра, второй выход первого блока памяти блока управления подключен к синхронизирующему входу первого регистра решающего блока, отличающееся тем, что, с целью повышения устойчивости цикловой синхронизации, в него введен блок памяти контроля адреса, включенный мезвду выходами блока памяти и адресными входами первого блока памяти блока управления, в котором дополнительный выход первого счетчика соединен со своим управляющим входом, третий выход первого блока памяти подключен к своему управляющему входу, четвертый выход - к первому управляющему входу второго блока памяти, второй управляющий вход которого соединен со своим четвертым выходом, при этом вторая шина тактовой синхронизации

соединена с синхронизирующим входом третьего регистра.

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1985 |

|

SU1278970A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1986 |

|

SU1377906A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-15—Публикация

1987-10-28—Подача