Изобретение; относится к у: к -1 с-- технике и может быть исно;;b:jciijo.tiu в электропривсдах цифровых систс1 : автоматического управления„

Целью изобретения: являетси улучшение регулирсвочнь х характерис л,

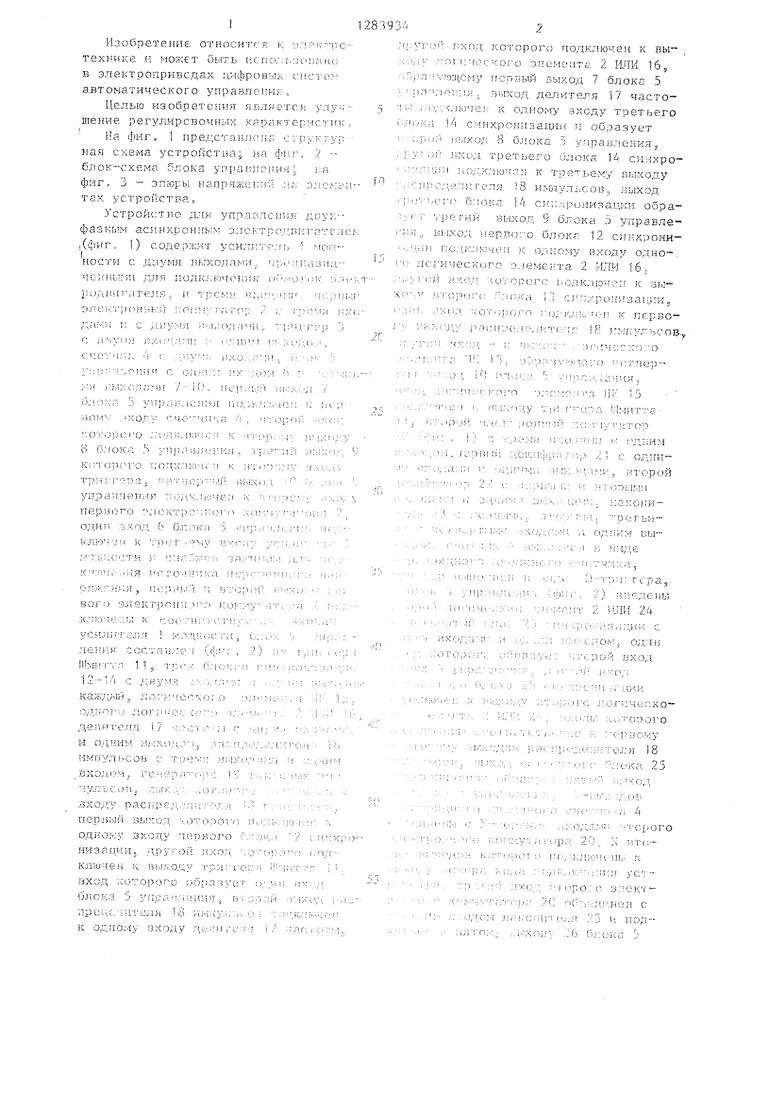

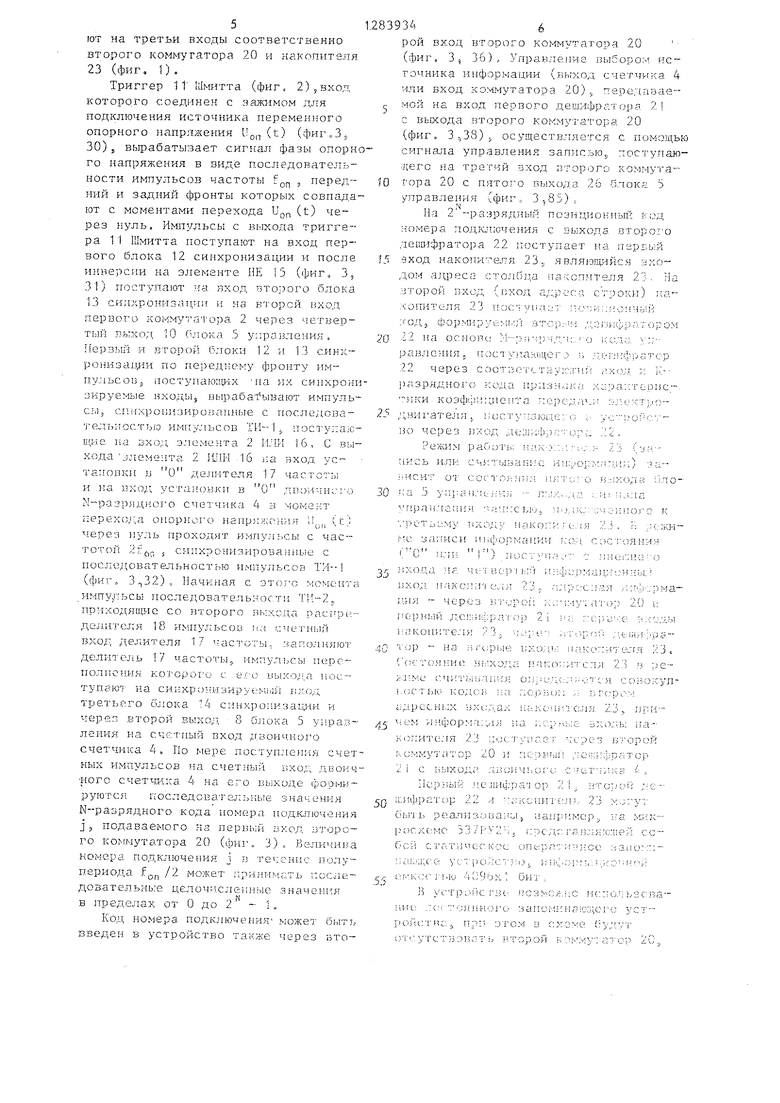

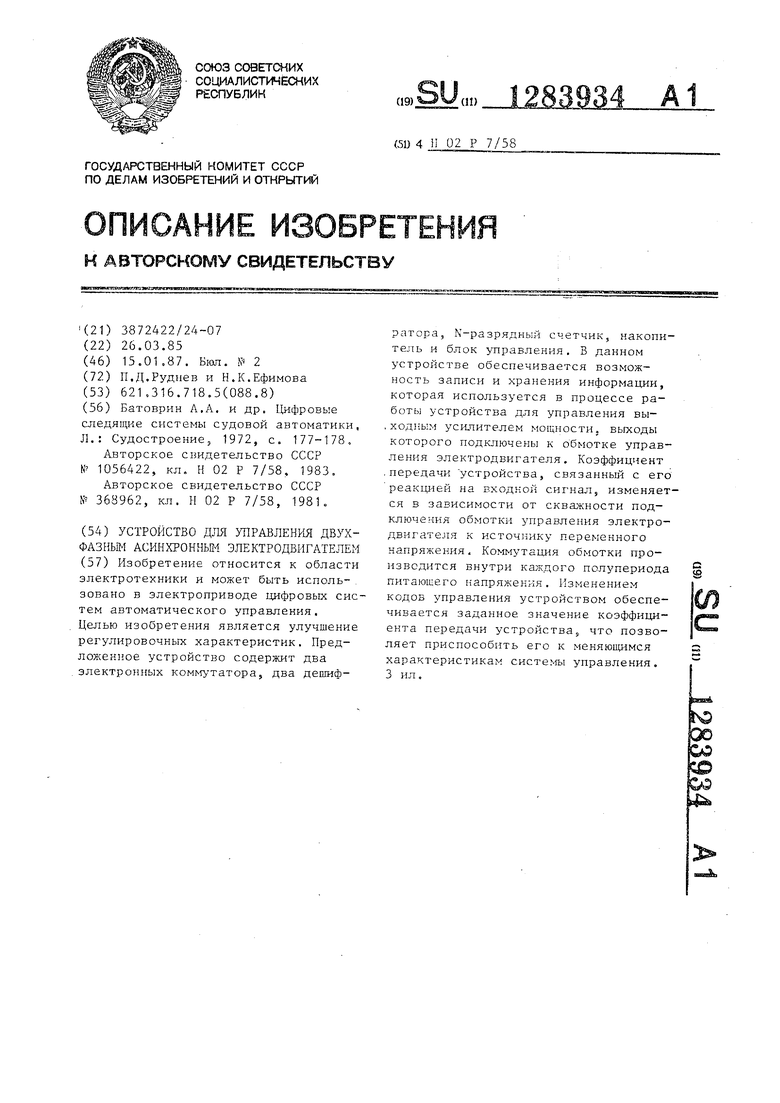

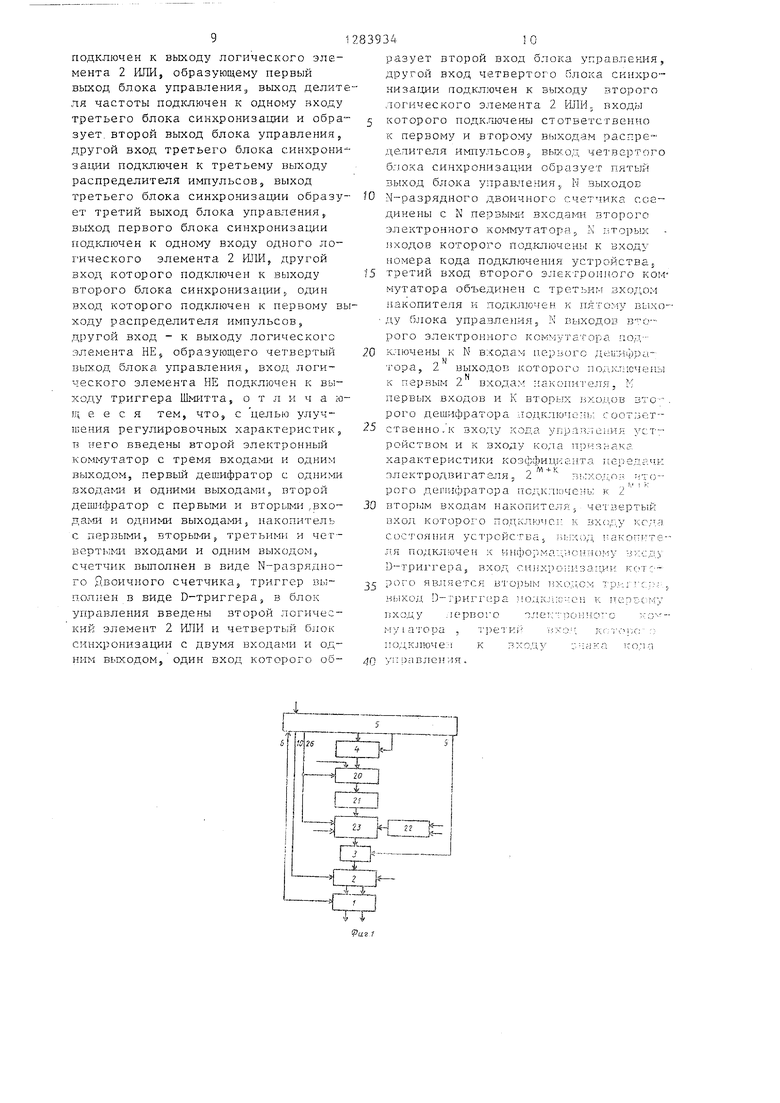

На фиг. 1 нре,цста15ЛС:п;; с урукгуг; ная схема устройстна; яа фиг, /. - блок-схема блока yniiafuicuHH l i:a

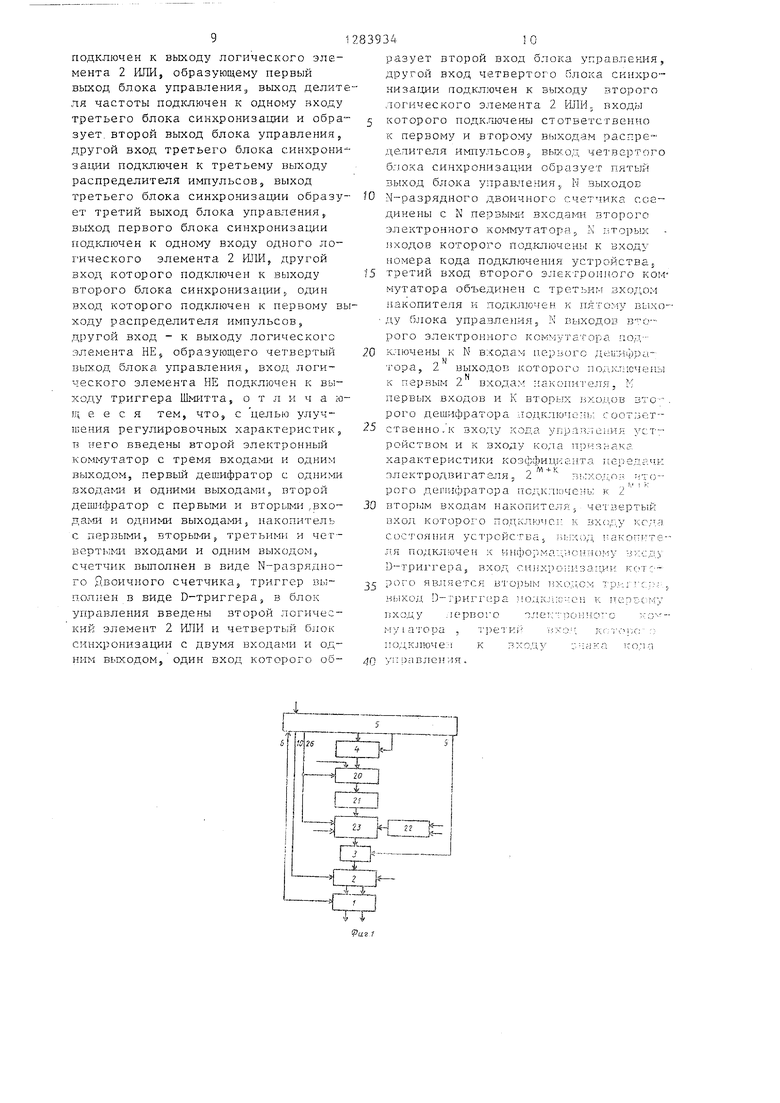

фиг, 3 ЭПЮрЬ напряжений . ;3;1СЬ:с Н-так устройства.

Устройство для управления фазнь м асинхрон; ь;м элс грсх вкгатг.лсг: ;(фиг, 1) содерлит з силнтс л) 1 могг- ности с дзумя 1 ыхо/тами,. нр:.. :1пазна-- чеины:- для подк,;;юч(Л;ик оУ.-ло г ..IK .-K р(.),чтеля ,, и трсь н iiX;;; , : u . .гг элcb: i pc H;ib:;i iiOt:: ; i aTcy; / ;; т;;: .; ;;(; дами и с дну:мя :-i.,;o,;i али „ Г1;чг л-м) 3 С .вхсчали ivau M . Д.(:гУ .

СЧОГЧ Л.. ; , НХОу.аЛИ, ;У-.Л: V:

у:: .ОИмЯ с Oil;;: л Х ;Vi.);.i l : ч;; .;.: i/

. ; гыхсугам) /-10, L ix.a:yi и.:.;ч:. Л У

Юг-Л- , ХО,Г;- СЧе -Л11Ч;1 /;. , М ГОрп; , ..:г:: , O-Vi:ipC i O ЛРЛКЛШЛГ Ч к . Гг; ; : м-. ii: :nj V 8 блока у ,;плп-;я , гр-: -и: | ;;:.:;):. .

КЛТОрСЛ Ю Г;(1ДГС1 {Л;Г ;i к ;Г;ОХ ;ЛГ ;.i...:. .:/,

трЛА , Л:--гно;у: -..:1. ныхо:. ;, ,; ;. . упра; }1енля ;л:;л,х,Л|.;леа к ; ;;:л ч;-.:;. nepwijro :y,ieivTpc x(y-(i :;:п;; .г/i -i- :л:,- ;у один вход (; блока 3 лу; -:.;(. ;ч.: s чг.:.- КЛ У Л( к тпег п -луг: /fyiyy х

ора-ую:цсму пепБЫй выход 7 блока 5 г:рл-лд; уя , выход делитвля 17 часто- у уоу, люлеу к одному зхсду третьего туо; 1/ слнхроннзацил н образует ;;pu;i jjbrxo/i, 8 блока 5 ynpaisjieiiKH, нхид третьего блока 14 сннхро- .ИЛ 1.одклю ен к Т ретьему выходу : ЛЛУ д(Ули1л.ля 18 и шульсов, ;зыход - чего блока. 14 .-;ро)изацки обра л у ,4.егий выход 9 блока 5 управле- у;у, выход нерпого блока 12 СИКХРОНИ- лул: nojyyiHyjtyr )( ОДНОМУ ВХОДУ одно-. .; логического э...(емента 2 ИЛУ 16, УЛ 1Л1 у-:.:;д чоуор(згс лодк:ночпл к зь;

-64/:4V;vii:0:-0 -,,, jMlep- , ч) ИЛ:.;1у.; : .М1Г-у: уаЧ1гя.

чччччяччо; о члслч: 1 а ilF t5

ЛЧ Ч;фчч;ЧЧр 21 с ОД;1Ц-Ч -:У ч.г-ч1чл:и, .второй

к. :.4iH лс гоч У;;ча

вого злйктрои;улч 1Л)у:- у -У У. : .к:,чкуте:У;; к .л(. л: усилитсллг му:пчосугл, бл.. :-. лв)4чх сос гав.уеч (фгуу 2) ;гliKii-f fy 1 1 1 J ГР У: (чок : i ryyi : i 1 2- с двум.:; л-.-. : .. . у каждый,, логлч е Лчо: о .1:у

,1),е.и ЧЧ: ЛЯ 17 УМЧУ л. с Л; - .:

и о/1,ним }Л::хс1дул, .ли. ч:-Ч .:.у i:r;

импульсов С: ТЧЛЗ--:.:Г ).У -.УЧУ i

увхо;:,ом, ле чера. - лч -. ./.;у;.:

,- - L - а 3 ч 2; вчсделы гг 2 Ш1И 2/+

;лччлл одлн чгсрой вход

;У )ЧОД

УС j oryyeoKO- о.чь; :-.отч)оого

ВХО;:Гу раСЛреу.Ч.ЧУ .:-: Л.;; Ч т ;.. ,пер)Ый выход :vOTOoo4o ;ч.-.yi... по ч

ОДНОХУ входу ЛерВОГ О 4.:-,:yi:.. 1/

ниэадни. .:1;г1у; ой вхо;ч л -ллч -лч клшле}) к вы.;;;од;- трлч.чс;л; y-.jyy. вход КОТОРОГО ;.)б;-;а ч Ч.ччч ш

к ОДНОМ;/ вяод,у ..:т11чч: Ч / аг

-.;-;Ч-ч;. -ч-чэдч:- : -ччл- ого

;-яуууач„ра 20, V В iv4: --.) -: лсучулччсчгЬ к Чл; ;.ч,ч; У f vi;y ЧХ(ЧУ .;1(.1рО.Л: З/ТОКТЧ, ОЛ Ча Л}:ЧУ1УмЛ 23 Н НОДуправления, N выходов второго электронного коммутатора 20 подключены к N входам первого дешифратора 21, 2 выходов которого подключены к первым 2 входам накопителя 23, М первых входов и К вторых входов второго дешифратора 22 подключены соответственно к входу кода управления уст ройством и к входу признака характе-

ристики коэффициента передачи элект

„М4-К

родвигателя, 2 выходов второго де- шифратора 22 подключены к 2 вторым входам накопителя 23, четвертый вход которого подключен к входу кода состояния устройства, выход накопителя подключен к информацио шому входу В-триггера, вход синхронизации которого образует второй вход D-триг гера, выход D-триггера подключен к nepBOt-iy входу первого электронного коммутатора 2,, третий вход которого подключен к входу знака кода управления ,

На фиг. 3 приняты следующие обоз-

1ачения: 27, 28 и 29 последователь- 25 ледовательность импульсов ТИ-2 со ности тактовых игшульсов ТИ-1, ТИ25 - второго выхода распределителя 18 импульсов -поступает на другой вход логического элемента 2 ИЛИ 24 и на счетный вход делителя 17 частотЫу который JO вырабатывает последовательность счетТИ-3 соответственно на nepBOMj вто- .ром и третьем выходах распределителя 18 импульсов (фиг, 2)J 30 - переменное напряжение , (t) на одном входе 6 блока 5 управления; 31 - сигнал фазы и (t) на выходе элемента НЕ 15 32, 33, 34 - сигналы соответственно на первом, втором и третьем выходах

ных импульсов с частотой - R fpns где R - коэффициент пропорциональности; , - частота U,, (t) (фиг,3, 33), Последовательность счетных им7-9 блока 5 управления 35, 36 - пульсов частоты f . с выхода делителя 17 частоты поступает на синхрони- зируемь;й вход третьего блока 14 синхронизации и через второй выход 8 блока 5 управления на счетный вход двоичного N-разрядного счетчика 4, С выхода третьего блока 14 синхронизации через третий выход блока 5 управления на вход синхронизации D-триггера приходят импульсы с частотой f(-(j синхронизированные последовательностью тактовых импульсов ТИ-3 (фиг, 3, 34), Последовательность импульсов с выхода логического элемента 2 ИЛИ 24 поступает,на синхронизирующий вход четвертого блока 25 Синхронизации, на синхронизируемый вход которого приходят импульсы управления записью с второго входа блока 5 управления. Импульсы управления записью, синхронизированные последовательностями ТИ-1 и ТИ-2 с выхода четвертого блока 25 синхронизации через пятый выход 26 блока 5 управления поступалитудное значение кода соответственно на первом и втором входах второго электронного коммутатора 20, 37 - сигнал управления записью на четвертом выходе 10 блока 5 управления, 38 - амплитудное значение кода на выходе второго электронного коммутатора 20, 39 - сигнал на выходе накопи- теля 23, 40 - сигнал на выходе триггера , 41 - сигнал на выходах усилителя 1 мощности.

Накопитель 23 (фиг, 1) имеет емкость (А + B)-j, где А - максимальное значение кода управления; В - максимальное значение кода признака ха- рактеристики коэффициента передачи электродвигателя в семействе требуемых; j - число возмож1 ых подключений обмотки управления электродвигателя к источнику переменного напряжения U(5n (t) за полупериод /2,

Усилитель мощности может быть выполнен по любой известной двухтакт- ,ной схеме, каждое плечо которого

подключается к соответствующей секции обмотки управления электродвигателя ,

Устройство работает следующем образом.

Распределитель 18 и шульсов (фиг, 2) формирует из последовательности импульсов высокой частоты, вырабатываемых генератором 19 тактовых iO импульсов, три последовательности

тактовых импульсов ТИ-1, ТИ-2 и ТИ-3 (фиг, 3 27-29), сдвинутых по фазе относительно друг друга на с частотaNm f., f,,,, f..Uocne- 15 довательность импульсов ТИ-1 с первого выхода распределителя 18 и шульсов поступает на синхронизирующие входы первого и второго блоков 12 и 13

синхронизации и на вход логического 20 элемента 2 RHH 24, а последовательность импульсов ТИ-3 с третьего выхода распределителя 18 импульсов поступает на синхронизирующий вход третьего блока 14 синхронизации, Посных импульсов с частотой - R fpns где R - коэффициент пропорциональности; , - частота U,, (t) (фиг,3, 33), Последовательность счетных импульсов частоты f . с выхода делителя 17 частоты поступает на синхрони зируемь;й вход третьего блока 14 синронизации и через второй выход 8 блока 5 управления на счетный вход двоичного N-разрядного счетчика 4, С выхода третьего блока 14 синхронизации через третий выход блока 5 управления на вход синхронизации D-триггера приходят импульсы с частотой f(-(j синхронизированные последовательностью тактовых импульсов ТИ-3 (фиг, 3, 34), Последовательность импульсов с выхода логическог элемента 2 ИЛИ 24 поступает,на синхронизирующий вход четвертого блока 25 Синхронизации, на синхронизируемый вход которого приходят импульсы управления записью с второго входа блока 5 управления. Импульсы управления записью, синхронизированные последовательностями ТИ-1 и ТИ-2 с выхода четвертого блока 25 синхронизации через пятый выход 26 блока 5 управления поступагот на третьи входы соответственно второго коммутатора 20 и нг копятеля 23 (фиг. 1),

Триггер 1 Т Шмитта (фиг 2)58x0,4 которого соединен с зажимом для подключения источника переменного опорного напряжения Upj-, (t) (фиг.З, 30) 5 вьфабатызает сигнал фазы onoptjo го напряжения в виде последовательности импульсов частоты f , передний и задний фронты которых совпадас моментами перехода и„„ (t) чеют

рез нуль. Импульсы с выхода триггера 11 Шмитта поступают на вход первого блока 12 синхронизации и после инверсии на элементе НЕ 13 (фиг 3,, 31) поступают ла вход второго блока 13 сиихронизац-п н на второй в.хо,ц первого комм утатора 2 через четвертый выход 10 С лока 5 управления. ilepBhM и второй блоки 12 и 13 синх- рО11 изавд1И по передг1ему фронту импульсов, поступаюгцих 4ia их синхронн вкруемые входы, выраба т ывают импуль- cjiij сггнхр ОвизирО Кшные с последова- тельность 0 имггудьсов ТИ-I ., nociA ;;a}c щие lia вход элемента 2 11:11- 1б, С выхода элемента 2 ИЛИ 16 ва вход ус- таиовки в О ;:1;елителя 17 частст ы и на вход установки в О двоичнсго N pa3p5iдного счетчика 4 з -юмент переход,; onopiioro lianpKKOHHH u ,,,., (I) герез fryjib проходят импу,;1ьсы с частотой 2f(,,, , еипхронизировагшые с последовательностью импульсов ТИ--1

J, J

2) „ Начиная

импу.тьсы последовательное ти пр гход.япше со второго вь:хсда па делитс,г:я 18 импульсов на счетный вход делителя 17 чгштоты,. загтолняют делрп ель 17 частоты,, имлул1,сы переполнения KOTopoi o с ег(1 выход,а поступают на сипхро -нзируе-ьи.и lixo,,-; тре1Ч)его блока 14 синхропизац;-1И и через второй 8 блока 5 yiipaji- ления на счст ный вход дгвоичног о счетчика 4, По мере постунления С чет- Hbix импульсов на счетг1ый вхо,д двоич- ного счетч -1:са 4 на его форми- Р у ю Т с ,ч г; о с л е д о- в а т ел ь i; ы е з н а ч е н и я 1 1--разрядного кода номера но,цключевия j 5 подаваемого на первый ,д второго коммутатора 20 (фиг. 3). Вели1-1И1;а

периода f /2 может

-

12839346

рой вход второго коммутатора 20 (фиг. 3, 36),, Улра.вле1гие выбором sic- точника информации (гшгход счетчика + или вход коммутатора 20) пере,чавае-- г мой на вход первого дешифратора 2 с выхода второго коммутатора 20 (фиг. 3,38)j осуществляется с помощью сигнала управления записью поступаю- iierc на третий вход второго коммута 0 гора 20 с пятог-о выхода 2о блока з (фиг. 3,85)

5

номера подюиочения с выхода второго де1ш- фратора 22 поступает перБь:й вход накопителя 23., являющийся зхо-- дом адреса столбца пакслителя 23 И; .второй вхо,д (.вход а,дреса строки) на- .(опителя 23 .ч;л. д:.- ;н:. :.оДз формируе:мь ; 1 ;.:,:: 22 ia основе М--рп ;рчдм:.. о равлонМ; ПОС1 удакицег .1 в ; 22 через соотзе1 ству;г:гии )азрядного ирдзн,. ;;. ; козфи ицне11та гчзредач; ,двИ1 ателя ,, во через ) ,aeiii:i:b, Режим рабо Гь; пак uj- Cb или счятывашге от сос тоя;в л i ка 5 (. - в: Ч1рав.чеии.н BJU.

,3 C TB3M ВХОД,у

г-е заггиси иш юрманРВ

,- , М1 , ,,,,.. Т , :l :,

I, и 1 ;.. iS;I / IILH: ; ;. 1

вхо.да да че ; всч1 i ь:ч вхо,;;, наксди 23 , - через BTopoi; ifepBbiH .гичапфратор )чи-сонителя / 3 , чо

- 11Л i

коммутатор 20 и чс/рвьи

21 с выхода ; и.;ОИЧЬО.Г(:

Ис:р;;ык .че:ш1фра 1 ор )а 1Ч)р 22 ,, X/KCunTi; ()Ы .1 1 реализ;.вав: j uaiii; росх(.:ме 537.i3V2-; 1:г)с,дс бей статическое ,.i:i;ce . j ;И До- : ч.,; е..чС(л 1.10 409их1 бит :

15 yc Tp;.-k: гве ..i;C ис: iu-rt: ..:о; ;;и11но1ч.) задомИ11а:с:де. ройствс при з 1 ом в i-} от.:утст}5О1з::т ь втзаой к зг- му:;

7

третий и четвертый вход накопителя 23, элемент 2 ИЛИ 24 и чет вертый блок 25 синхронизации в блоке 5 управления, так как накопитель 23 будет работать только в релдаме считывания информации. Недостатком такого устройства является невозможност оперативного изменения информации в накопителе 23 в процессе работы.

Информация с выхода накопителя 23 (фиг. 2,39) поступает на информационный вход D-триггера (выполненного, например, на микросхеме 133TM2)j на синхронизирующий вход которого поступают через третий выход 9 блока 5 управления импульсы с выхода третьего блока 14 синхронизации (фиг. 3,34), частота следования которых равна частоте следования счетных импульсов f,, ,, постз пающих на счетный вход N-разрядного двоичного счетчика 4, и синхронизированных последовательностью импульсов ТИ-3 „

В момент прихода синхронизирующего импульса на второй вход D-триггера на его выходе устанавливается информация, равная информации на его первом (информационном) входе (фиг, 3, 40). Таким образом, на первый вход первого коммутатора 2 через D-триггер выводится из накопителя 23 хранящаяся в нем информа1 ия которая используется для управления подключением обмотки управления двухфазного асинхронного электродвигателя к источнику переменного напряжения UQ (t), Кроме того, на другие входы перзог о коммутатора 2, формирующего реверс электродвигателя на двух сво их выходах, поступают сигналы: на второй его вход - с четвертого выхода 10 блока 5 управления сигнал Ног, (t) фазы опорного напряжения UQ,, (t). на третий вход - сигнал знака кода управления sign А.

Первый и второй ВРЯХОДЫ d и dj первого коммутатора 2 связаны с первыми двумя входами логическими зависимостями вида:

d 2(Von 2 z(Vo.

sign AV (.sign A) и sign AV (on e

Сигналы с первого и второго выходов коммутатора 2 усиливаются с помощью усилителя 1 мощности по току и напряжению до величины, необходи83934

мой

fO

15

по условиям работы электродвигателя, и выводятся на выходные клеммы, Таким образом, благодаря введению дешифраторов, второго электронного коммутатора и накопителя, а такл;е второго логического элемента 2 ИЛИ и четвертого блока синхрониза- обеспечивается возьюжность реа- лизацрп требуемых характеристик Коэффициента передачи двухфазного асинхронного электродвигателя, что позволяет улучшить регулировочные характеристики электропривода в центом,

Формула изобретения

Устройство для управления двухфазным асинхронным электродвигателемд содержащее си.п:итель мощности с двумя

вь;ходами5 предназначенными для подключения o6.NiOToK электродвигателя, и тремя вxoдa Ш5 первьй электронный коммутатор с тремя входами и двумя выходами, триггер с двумя входами и

CvLiHiJM выходом, счетчик с двумя входами-;; блок управле1 ия с одним входом и четь;рьмя выходами, первый выход ка управления пoдключe i к первому Bxo;i3 счетчика J. второй вход которого

подк;11очен к второму выходу блока уп- равлй -;ия,. третий выход которого подключен к второму входу триггера, четвертый выход блока з правления подключен к второму входз первого электронного ком)утатора, третьему входу усилителя :.ющности и сь;абжен зажимом для подключения источника переменного нг1Пряжсния,, первый и второй выходы первог о электронного коммутатора подключ сны к cooтвeтcтвyю ци входам усилителя моц ности, блок управления составлен из TjMirrepa Шм:1тта, трех блоков си} хронизации с двумя входами и одним выходом калчдый, логического

элемента НЕ,, одного логического эле- мента 2 ИЛИ, делителя частоты с двумя входам -; и одним выходом, распреелителя импульсо}з с тремя выходами и одним входом, ге; ератора тактовых

импульсов, выход которого подтслючен к входу распределителя имлульсов, первьй выход которого под слючен к одноу входу первого блока синхронизации, ругой вход которого подключен к выко

У триггера Шм-ггта, вход которого образует один вход блока управления, торой выход распредел1-:теля импульов подключен к одному входу делиеля частоты, другой вход которого

подключен к выходу логического элемента 2 ИЛИ, образующему первый выход блока управленияэ выход делителя частоты подключен к одному гчходу третьего блока синхронизации и образует, второй выход блока управления, другой вход третьего блока синхрони- зации подключен к третьему выходу распределителя импульсов, выход третьего блока синхронизации образу- ет третий выход блока управления выход первого блока синхрониза1Ц1и подключен к одному входу одного логического элемента 2 ШШ, другой вход которого подключен к выходу второго блока синхронизации,, один вход которого подключен к первому выходу распределителя импульсов, другой вход - к вьжоду логического

элемента НЕ образующего четвертый гзыход, блока управления, вход логического элемента НЕ подкл очен к выходу триггера Шмитта, о т л и ч а ю1кения регулировочных характеристик, в него введены второй электронный комг-гутатор с тремя входа ш и одним выходом, первый дешифратор с одними входа№ и одними выходами, второй дешифратор с первыми и вторыми ,,входами и одними выходами 5 накопитель с первыми, вторьи-м третьими и четвертыми входами и одним выходом, счетчик выполнен в виде N-разрядно- го Двоичного счетчика, триггер оь;- п.олнен в виде В-триггера, в блок управления введены второй логический элемент 2 ЛЛИ и четвертый блок синхронизации с двумя входами и одним выходом, один вход которого об

разует второй вход олока управления, другой вход четвертого блока синхронизации подключен к выходу второго логического элемента 2 ШШ- вход/л которого подключены стответственно к первому и второму выходам распре™ де лителя импульсов, вгзжод четвартс/го б:1ока синхронизации образует пятый выход 6jtoKa управления, Ы выходов

М -разрядного двоичного счетчика соединены с N nep3bi№i входам второго электронного коммутатора N Г Торых входов которого под1-спючены к входу номера кода подключения устройства.;

третий вход второго электронного коммутатора объединен с третьиг-г зхо.цом накопителя и подключен к пятому ду блока упразлепиЯэ N выходов рого электронного коммутатора под-ключены к N входам первого .

первых входов и К вторых «ходов зто-- рого дешифратора лодключси);; соотзет- ственно.к входу кода упралугепия устройством и к входу кода признака характеристики коэффициента пег;епачк

о Л1 + к

электродвигаталя 5 пь:ходо;; пт(1рого дегигсЬратора псдключе Ь: к 2

BTopbSM входам накопителя, четвертый 1зхол которого ПОДКЛЮЧС1: к входу кода состояния уст ройства5 П1:;;чод ;акоп1-:те- ля подключен к инфопма:-,-1снному 1}-триггерад вход cHiixpoinisauHK коте-рого является вторым 5ХОДСМ т p;:l i C.:).- ,

ныкод D-григгс ра одк,:1:о; сн к иервсму ходу лервого тлетггрсипю о хо - MyulTOpa , Т15еткЙi;x:;; К(: гсч;г; :;

подключе:- к зходу :;-:а :п коло VI: равлс ;5Я .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления асинхронным электроприводом | 1987 |

|

SU1522373A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1981 |

|

SU1056422A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1980 |

|

SU868962A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1981 |

|

SU997221A2 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Имитатор электрокардиосигналов | 1985 |

|

SU1250248A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

Изобретение относится к области электротехники и может быть исполь- . зовано в электроприводе цифровых систем автоматического управления. Целью изобретения является улучшение регулировочных характеристик. Предложенное устройство содержит два .электронных KOMNfyTaTopa, два дешифратора, 1 -разряднЬ)й счетчик, накопитель и блок управления. В данном устройстве обеспечивается возможность записи и хранения информации, которая используется в процессе работы устройства для управления вы- ,ходным усилителем мощности, выходы которого подключены к обмотке управления электродвигателя. Коэффициент .передачи устройства, связанный с его реакцией на входной сигнал, изменяется в зависимости от скважности подключения обмотки управления электродвигателя к источнику переменного напряжения. Коммутация обмотки производится внутри ка кдого полупериода питающего напряжен :я . Изменением кодов управления устройством обеспечивается заданное значение коэффициента передачи устройства, что позволяет приспособить его к меняющимся характеристикам системы управления. 3 ил. С (О

г7ШШ1111111ПМ1111шшшшш1Ш1Ц111 111 111 aiuniiiiiiiiiinitiiiiiiiJiHiJiiijJiiHi. iniiJiJii

и 111М/ 11И1П111П11И Ш1Ш111/ПН1П)П11Ш1

31-с зг-t

3 и I I I 1 1 I I I I I I I I ni М f I I I I I

iHOMeHm запаси

п П m U и

OSutJ

Редактор А.Долинич

Составитель Б.Алешечкин

Техред В.Кадар Корректор М.Демчик

7456/56

Тираж 661Подписное

ВНИИПИ Грсударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Батоврин А.А | |||

| и др | |||

| Цифровые следящие системы судовой автоматики, Л.: Судостроение, 1972, с | |||

| Кулисный парораспределительный механизм | 1920 |

|

SU177A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1981 |

|

SU1056422A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для СБОРКИ и АВТОМАТИЧЕСКОЙ СВАРКИ | 0 |

|

SU368962A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-01-15—Публикация

1985-03-26—Подача