1

Изобретение относится к электросвязи и может быть использовано в качестве приемника испытательных сигналов контрольного комплекта.

Цель изобретения - повышение том ности измерения фазовых искажений.

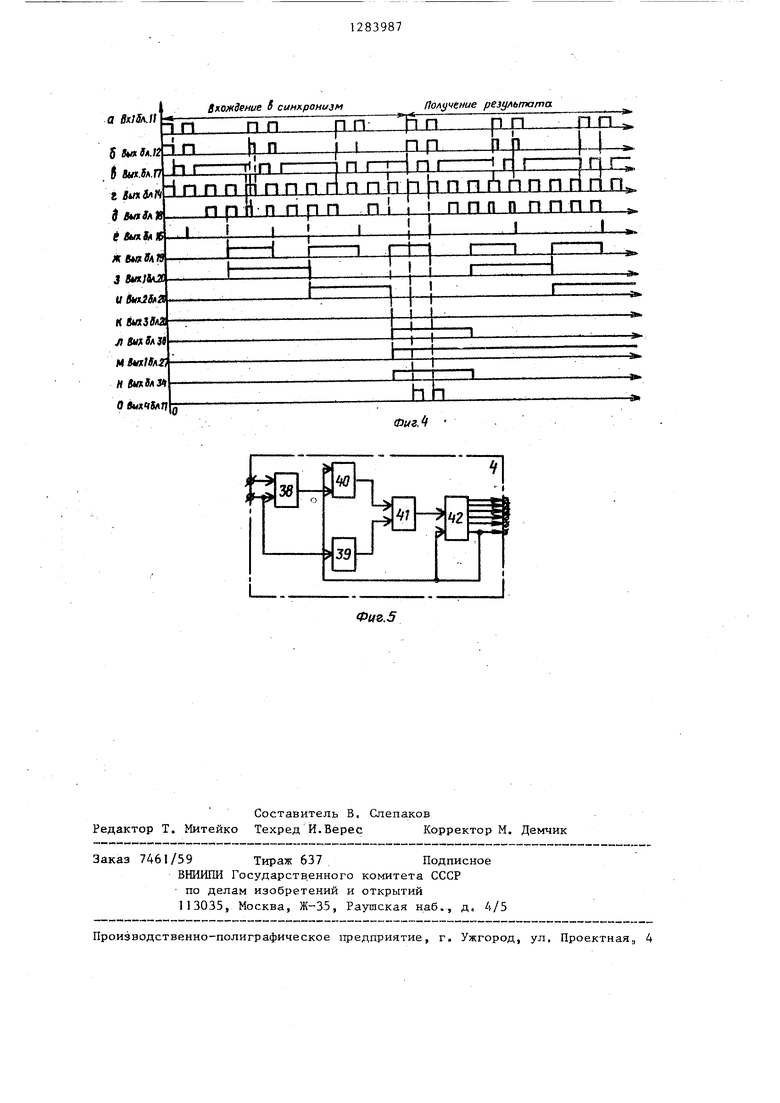

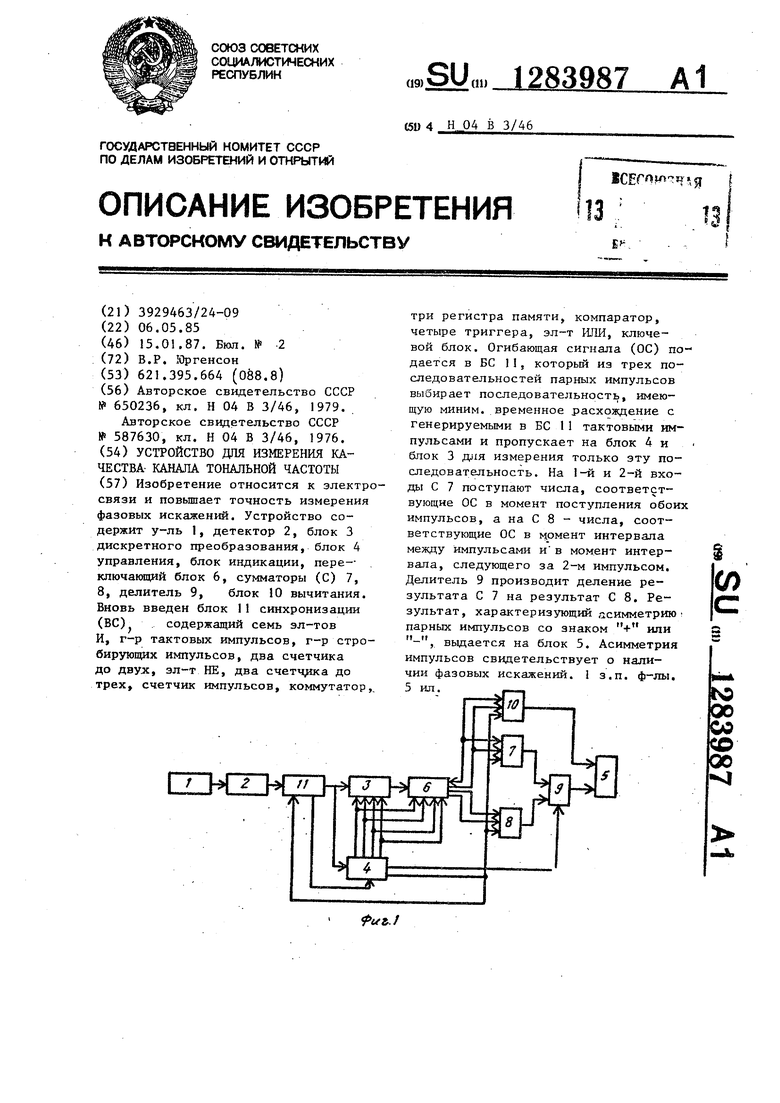

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временная диаграмма испытательного сигнала и процесса синхронизации; на фиг. 3 - структурная электрическая схема блока синхронизации; на фиг, 4 - временная диаграмма работы блока синхронизации; на фиг. 5 - структурная электрическая схема блока управления.

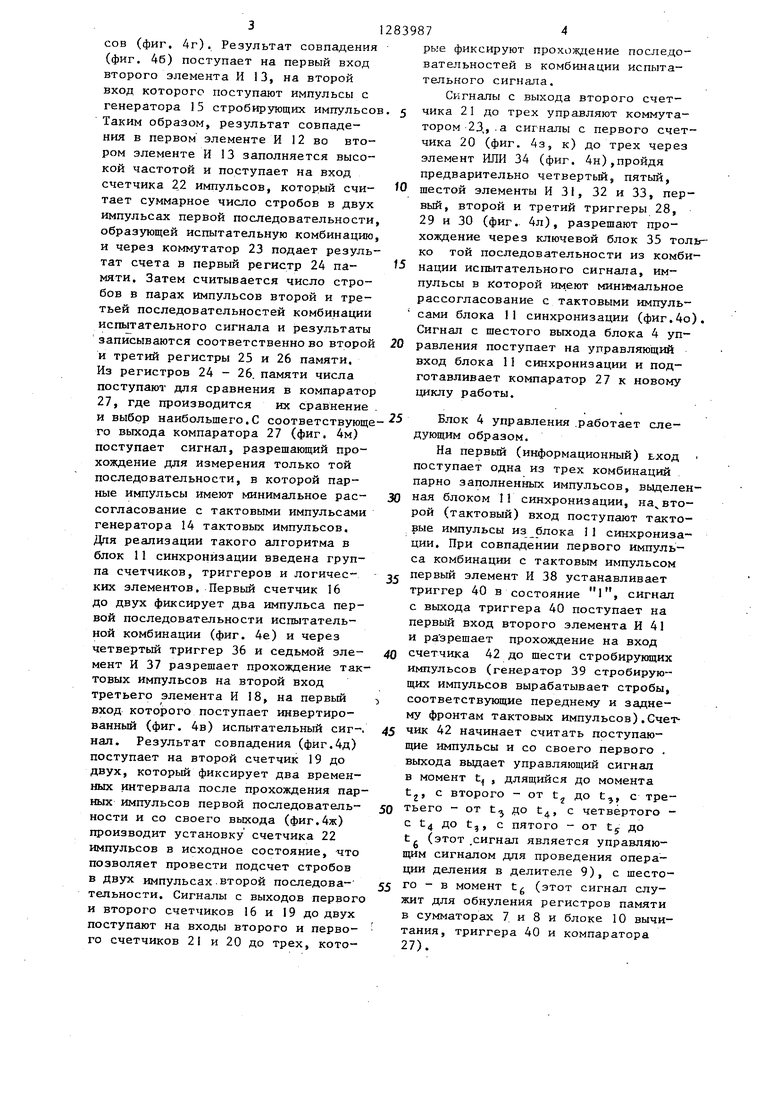

Устройство для измерения качества канала тональной частоты содержи усилитель 1, детектор 2, блок 3 дискретного преобразования, блок 4 управления, блок 5 индикации, переключающий блок 6, первый и второй сумматоры 7 и 8, делитель 9, блок 10 вычитания и блок 11 синхронизации, включающий первый и второй элементы И 12 и 13, генератор 14 тактовых импульсов, генератор 15 стробирую-j щих импульсов, первый счетчик 16 до двух, элемент НЕ 17, третий элемент И 18, второй счетчик 19 до двух, первый и второй счетчики 20 и 21 до трех, счетчик 22 импульсов, коммутатор 23, первый, второй и третий регистры 24, 25 и 26 памяти, компаратор 27, первый, второй и третий триггеры 28, 29 и 30, четвертый, пятый и шестой элементы И 31, 32 и 33, элемент ИЛИ 34, ключевой блок 35, четвертый триггер 36 и седьмой элемент И 37, а блок 4 управления состоит из первого элемента И 38, генератора 39 стробирующих импульсов, триггера 40, второго элемента И 41 и счетчика 42 до шести.

Устройство работает следующим образом.

Испытательный сигнал организуется комбинаций с парно заполненными импульсами, причем импульсы в соседних комбинациях, образующих комбинацию нового испытательного сигнала, сдвинуты по отношению друг к другу на 0,5 г (t - длительность импульса). Таким образом, испытательный сигнал образуется из трех последовательностей (фиг, 2а, в) и имеет ВИД, представленный на фиг. 2г

25

839872

Принимаемый испытательный сигнал, усиленный по мощности усилителем I, поступает на детектор 2. Огибающая сигнала подается в блок 11 синхрони5 зации, который из трех последовательностей парных импульсов (фиг,2г) выбирает последовательностьз имекщуК) минимальное временное расхождение с генерируемыми в блоке I1 синхрони 0 зации тактовыми импульсами (фиг.2д), и в дальнейшем пропускает на вход блока 4 управления и вход блока 3 дискретного преобразования для измерения только эту последовательность

(фиг. 2е). Огибающая такого сигнала подается в блок 4 управления и в блок 3 дискретного преобразования. Сигналы с выхода блока 3, представляющего собой управляемый анало го-цифровой преобразователь, поочередно формируемые параллельными кодовыми группами, подаются на переключающий блок 6, управляемый сигналами с блока 4 управления. С выхода переключающего блока 6 поступают параллельно на первый и второй входы первого сумматора 7 числа, соответствующие огибающей сигнала в момент поступления обоих импульсов (t, t,j),a на второй сумматор 8 - числа, соответствующие огибающей сигнала в момент интервала между импульсами и в момент интервала, следующего за вторым импульсом (t, t),

35 Кроме первого сумматора 7 числа, соответствующие значениям огибающей сигнала в импульсах, подаются на блок 10 вычитания. Делитель 9 произ- водит деление результата первого сумматора 7 на результат второго сумматора 8. Результат, характеризующий асимметрию парных импульсов со знаком плюс или минус, выдается на блок 5 индикации. Асимметрия импульсов свидетельствует о наличии фазовых искажений сигналов. Част- ное от деления является коэффициентом разделения импульсов и фиксируется блоком 5 индикации.

Блок 11 синхронизации работает следующим образом.

Испытательный сигнал с выхода детектора 2 поступает на информа- гг ционный вход блока 11 синхронизации (фиг. 4а), которым является первый вход первого элемента И 12, на второй вход которого поступают импульсы с генератора 14 тактовых импуль30

40

45

50

COB (фиг. 4r). Результат совпадения (фиг, 4б) поступает на первый вход второго элемента И 13, на второй вход которого поступают импульсы с генератора 15 стробирующих импульсо Таким образом, результат совпадения в первом элементе И 12 во втором элементе И 13 заполняется высокой частотой и поступает на вход счетчика 22 импульсов, который считает суммарное число стробов в двух импульсах первой последовательности образующей испытательную комбинацию и через коммутатор 23 подает результат счета в первый регистр 24 памяти. Затем считывается число стробов в парах импульсов второй и третьей последовательностей комбинации испьггательного сигнала и результаты записываются соответственно во второй и третий регистры 25 и 26 памяти. Из регистров 24 - 26. памяти числа поступают для сравнения в компаратор 27, где производится их сравнение и выбор наибольшего.С соответствующе го выхода компаратора 27 (фиг. 4м) поступает сигнал, разрешающий прохождение для измерения только той последовательности, в которой парные импульсы имеют минимальное рассогласование с тактовыми импульсами генератора 14 тактовых импульсов. Дая реализации такого алгоритма в блок 11 синхронизации введена группа счетчиков, триггеров и логических элементов. Первый счетчик 16 до двух фиксирует два импульса первой последовательности испытательной комбинации (фиг. 4е) и через четвертый триггер 36 и седьмой элемент И 37 разрешает прохождение тактовых импульсов на второй вход третьего элемента И 18, на первый вход которого поступает инвертированный (фиг. 4в) испытательный сиг-. нал. Результат совпадения (фиг.4д) поступает на второй счетчик 19 до двух, который фиксирует два временных интервала после прохождения парных импульсов первой последовательности и со своего выхода (фиг.4ж) производит установку счетчика 22 импульсов в исходное состояние, что позволяет провести подсчет стробов в Двзос импульсах .второй последова- тельности. Сигналы с выходов первого и второго счетчиков 16 и 19 до двух поступают на входы второго и первого счетчиков 21 и 20 до трех, кото

O

5

0

рые фиксируют прохождение последовательностей в комбинации испытательного сигнала.

Сигналы с выхода второго счетчика 21 до трех управляют коммутатором 23,, -а сигналы с первого счетчика 20 (фиг. 4з, к) до трех через элемент ИЛИ 34 (фиг. 4н),пройдя предварительно четвертый, пятый, шестой элементы И 31, 32 и 33, первый, второй и третий триггеры 28, 29 и 30 (фиг. 4л), разрешают прохождение через ключевой блок 35 только той последовательности из комбинации испытательного сигнала, импульсы в Которой имеют минимальное рассогласование с тактовыми импульсами блока 11 синхронизации (фиг.4о). Сигнал с шестого выхода блока 4 управления поступает на управляющий вход блока 11 синхронизации и подготавливает компаратор 27 к новому циклу работы.

Блок 4 управления .работает следующим образом.

На первый (информационный) ьход поступает одна из трех комбинаций парно заполненных импульсов, выделенная блоком 11 синхронизации, на,второй (тактовый) вход поступают тактовые импульсы из блока II синхронизации. При совпадении первого импульса комбинации с тактовым импульсом

е первый элемент И 38 устанавливает триггер 40 в состояние l, сигнал с выхода триггера 40 поступает на первый вход второго элемента И 41 и ра зрешает прохождение на вход

0 счетчика 42 до щести стробирующих импульсов (генератор 39 стробирую- щих импульсов вырабатывает стробы, соответствующие переднему и заднему фронтам тактовых импульсов).Cчe

5 чик 42 начинает считать поступающие импульсы и со своего первого , выхода выдает управляющий сигнал в момент t, , длящийся до момента

0

ч t, с второго - от t

до t,, с тре0 тьего - от t до t, с четвертого - с t4 до t,, с пятого - от ty до t, (этот .сигнал является управляющим сигналом для проведения опера- 1Ц1И деления в делителе 9), с шесто5 го - в момент t (этот сигнал служит для обнуления регистров памяти в сумматорах 7 и 8 и блоке 10 вычитания, триггера 40 и компаратора 27).

Формула изобретения

1.Устройство дпя измерения качества канала тональной частоты, содержащее последовательно соединенные усилитель и детектор, последовательно соединенные блок дискретного преобразования, переключающий блок, блок вычитания и блок индикации, последовательно соединенные первый сумматор, первый вход которого соединен с первым входом блока вычитания, и делитель, выход которого подключен к второму Входу блока индикации, а также второй сумматор, выход которого подключен к второму входу блока индикации, и блок управления, информационный вход и первый, вто- рой, третий, четвертьй, и пятый выходы которого соединены соответственно с информационным входом и первым, вторым, третьим и четвертым управляющими входами блока дискретного преобразования и с управляющим входом делителя, отличающеес я тем, что, с целью повышения точности измерения фазовых искажений, введен блок синхронизации, при этом информационный и управляющий входы и первый и второй выходы блока синхронизации соединены cooffeeT- ственно с выходом детектора, шестым выходом и информационным и тактовым входами блока управления, первый, втО(5)ой, третий и четвертьй выходы которого подключены соответственно к первому, второму, третьему и четвертому управляющим входам переключающего блока, второй, третий и четвертый выходы которого подключены соответственно к второму входу первого сумматора, соединенному с вторым входом блока вычитания, и к первому и втopo sr входам второго сумматора, третий вход которого соединен с третьими входами первого сумматора и блока вычитания и с шестым выходом блока управления,

2.Устройство по п. 1, о т л и - чающееся тем, что блок синхронизации содержит первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, генератор тактовых импульсов, генератор стро- бирующих импульсов, первьй, второй, третий и четвертый триггеры, первьш и второй счетчики до двух, первьш и второй счетчики до трех, счетчик импульсов, элемент НЕ, первьй, второй

и третий регистры памяти, коммутатор, компаратор, элемент ИЛИ и ключевой блок, при этом первый вход первого элемента И, являющийся информационным входом блока синхронизации, соединен с входом элемента НЕ и с первым входом ключевого блока, выход генератора тактовых импульсов подключен к первому входу

седьмого элемента И и к второму

входу первого элемента И, выход которого подключен к сигнальному входу первого счетчика до двух и первому входу второго элемента И, второй

вход и выход которого соединены соответственно с выходом генератора стро- бирующих импульсов и первым входом счетчика импульсов, выход первого счетчика до двух подключен к его

установочному входу, сигнальному входу второго счетчика до трех, установочному входу второго счетчика до двух и управлякщему входу четвертого триггера, выход которого

подключен к второму входу седьмого элемента И, выход которого подключен к первому входу третьего элемента И, второй вход и выход которого соединены соответственно с

выходом элемента НЕ и сигнальным входом второго счетчика до двух, выход которого подключен к сигнальному входу первого счетчика до трех и установочному входу счетчика импульсов, первый, второй и третий

выходы первого счетчика до трех подключены к соответствующим входам первого, второго и третьего триггеров, третий выход первого счетчика

до трех подключен к его установочному входу, установочному входу четвертого триггера и входам считывания первого, второго и третьего регистров памяти, выходы и сигнальные входы которых соединены соответственно с соответствующими сигнальными входами компаратора и соответствующими выходами коммутатора, информацион- ньй и управляющие входы которого

соединены соответственно с выходом

счетчика импульсов и соответствующими выходами второго счетчика до трех, третий из выходов которого 55 подключен к его установочному входу, выходы первого, второго и третьего триггеров подключены к первым входам соответственно четвертого, пятого и шестого элементов И, вторые входы

которых соединены с соответствующи-, ми выходами компаратора, управляющий вход которого является управляющим входом.блока синхронизации, а выходы четвертого, пятого и шестого элементов И подключены к соответст-,

Синхронизации Ai,utt,

вующим входам элемента ШШ, выход которого подключен к второму входу ключевого блока, выход которого и выход генератора тактовых импульсов являются соответственно первым и вторым выходами блока синхронизадаи.

OufHita карамплрисглчи

(

Фиг.З

Фиг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство формирования испытательных сигналов для многоканальной системы связи с импульно-кодовой модуляцией и временным разделением каналов | 1977 |

|

SU657633A1 |

| Устройство формирования испытательных сигналов для многоканальной системы связи с импульсно-кодовой модуляцией и временным разделением каналов | 1980 |

|

SU930713A2 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1988 |

|

SU1536514A1 |

| Устройство формирования сигнала изображения | 1989 |

|

SU1798929A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

Изобретение относится к электросвязи и повьшает точность измерения фазовых искажений. Устройство содержит у-ль 1, детектор 2, блок 3 дискретного преобразования, блок 4 управления, блок индикации, переключающий блок 6, сумматоры (С) 7, 8, делитель 9, блок 10 вычитания. Вновь введен блок 11 синхронизации (ВС) . содержащий семь эл-тов И, г-р тактовых импульсов, г-р стро- бирующих импульсов, два счетчика до двух, эл-т НЕ, два счетч;1ка до трех, счетчик импульсов, коммутатор, три регистра памяти, компаратор, четыре триггера, эл-т ИЛИ, ключевой блок. Огибающая сигнала (ОС) по- дается в БС 11, который из трех последовательностей парных импульсов выбирает последовательность, имеющую миним. временное расхождение с генерируемыми в БС 11 тактовыми импульсами и пропускает на блок 4 и блок 3 для измерения только эту последовательность. На 1-й и 2-й входы С 7 поступают числа, соответствующие ОС в момент поступления обоих импульсов, а на С 8 - числа, соответствующие ОС в момент интервала между импульсами и в момент интервала, следующего за 2-м импульсом. Делитель 9 производит деление результата С 7 на результат С 8. Результат, характеризующий асимметриюt парных импульсов со знаком + нли -, выдается на блок 5. Асимметрия импульсов свидетельствует о наличии фазовых искажений. 1 з.п. ф-лы. 5 ил. I сл

| Устройство для оценки качества каналов тональной частоты | 1976 |

|

SU650236A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для измерения качества каналов тональных частот | 1976 |

|

SU587630A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-01-15—Публикация

1985-05-06—Подача