. ,1

Изобретение относится к вычислительной технике и может быть использовано в цифровых и аналого-цифровых вычислительных комплексах, системах робототехники и интерактивной машинной графики.

Целью изобретения является расширение области применения устройства за счет дополнительной возможности вычисления функций двух переменных.

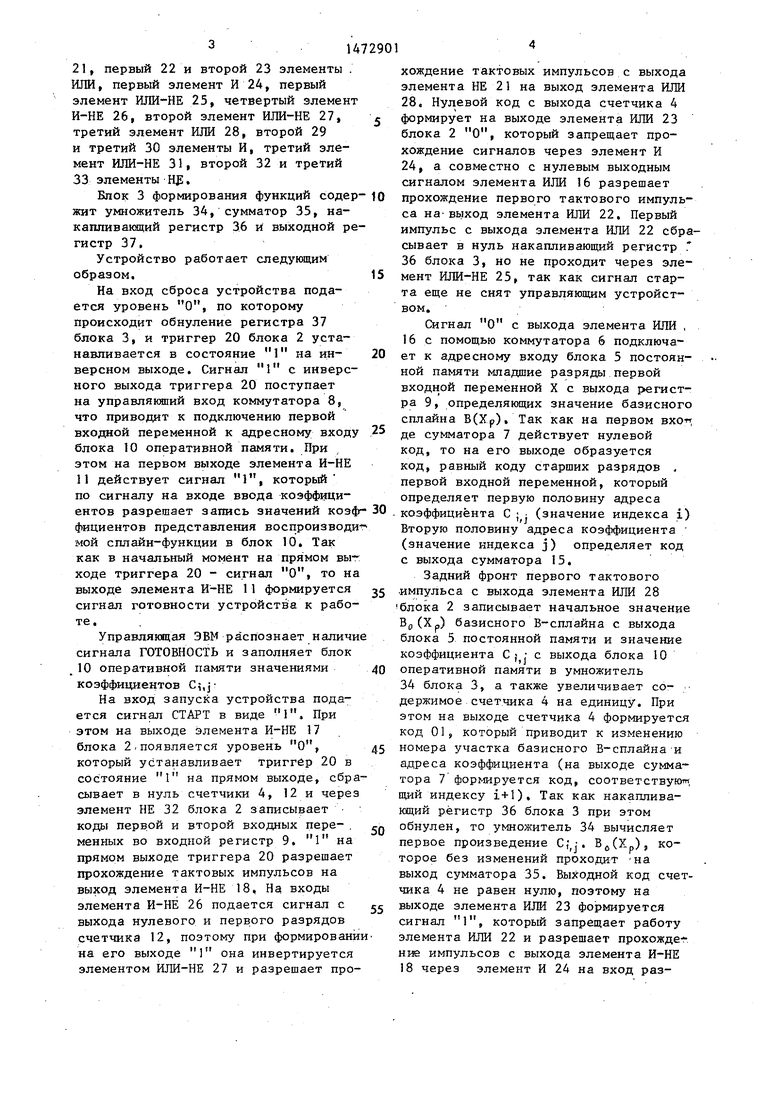

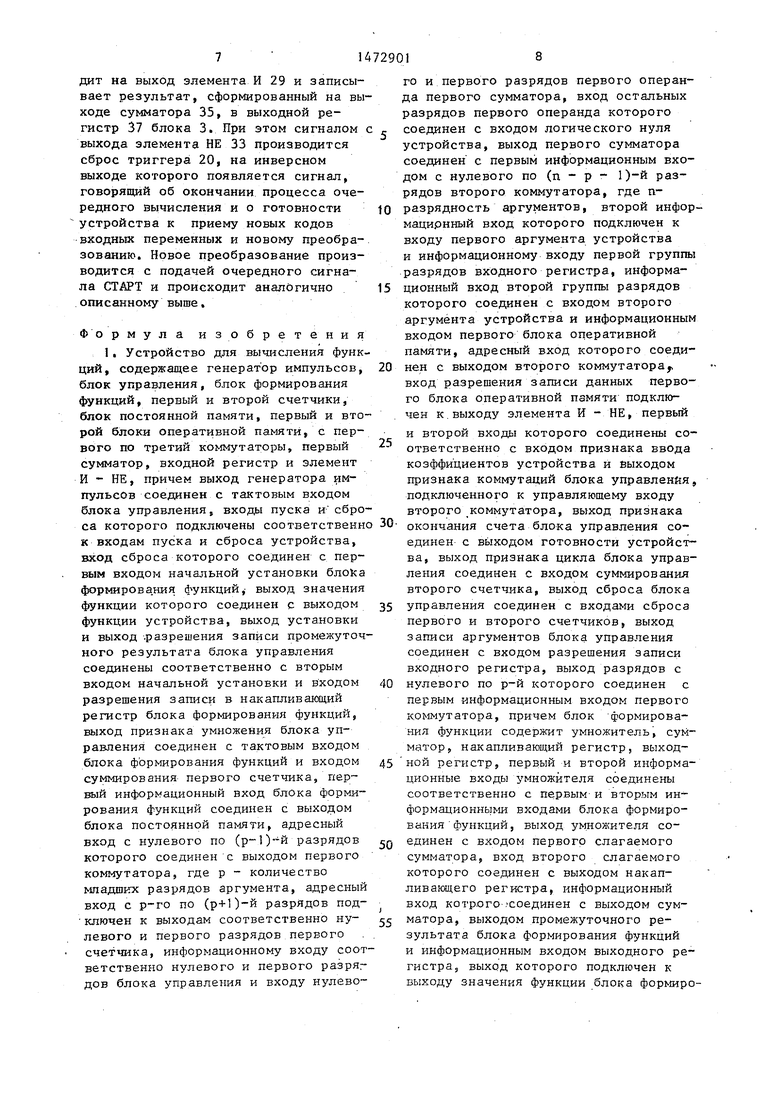

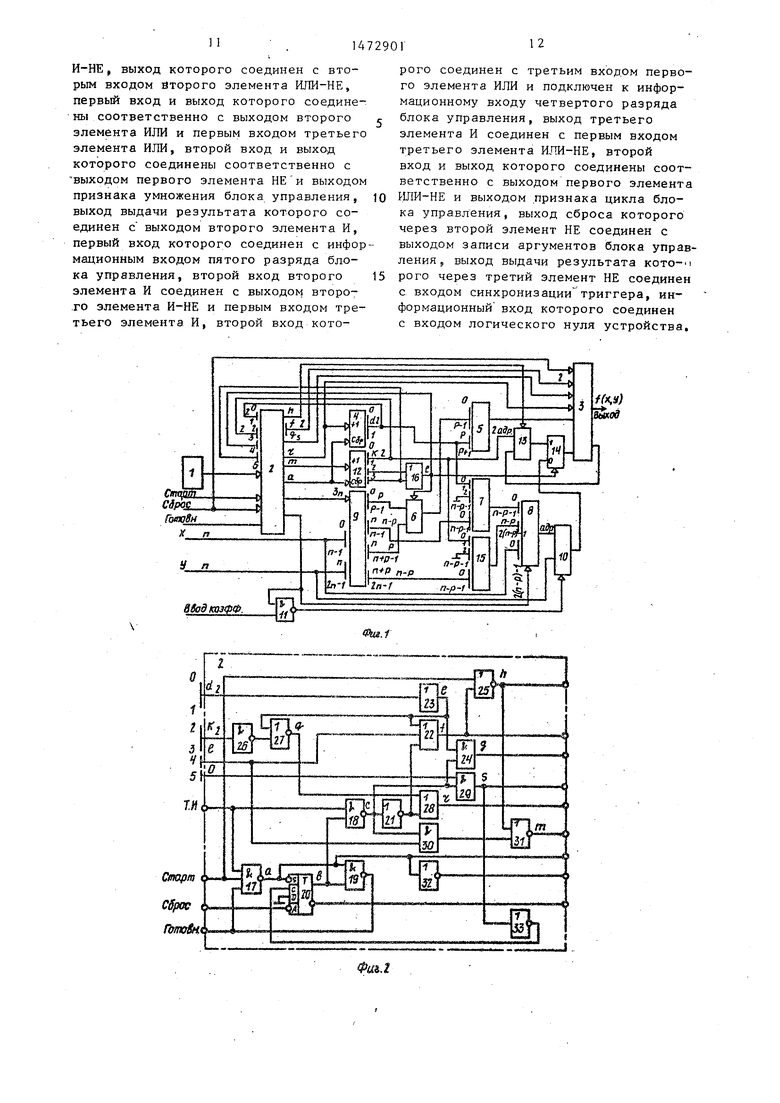

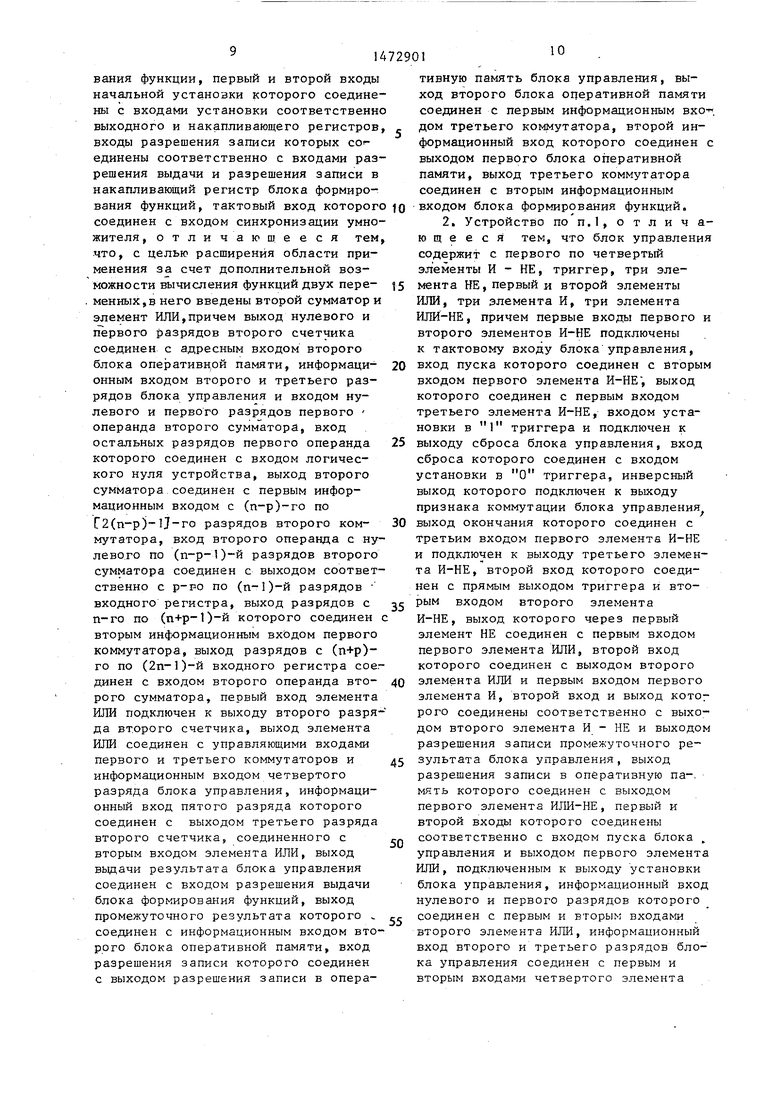

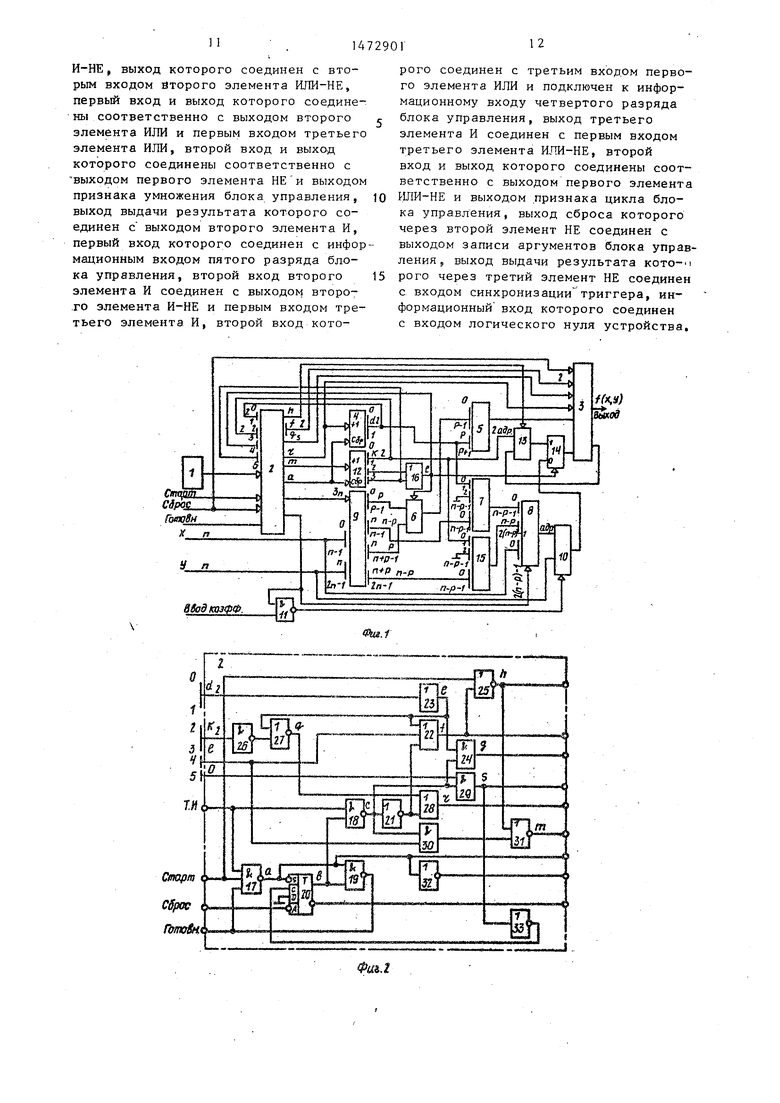

На фиг.1 показана структурная схема устройства; -на фиг. 2 - функци1- ональная схема блока управления; на фиг.З - один из возможных вариантов построения блока формирования функций,

Устройство для вычисления функций содержит генератор 1 тактовых импульсов, блок 2 управления, блок 3 формирования функций, первый счетчик 4, блок 5 постоянной памяти, первый коммутатор 6, первый сумматор 7, второй коммутатор 8, входной регистр 9, первый блок 10 оперативной памяти, элемент И-НЕ 11, второй счетчик 12, второй блок 13 оператив ной памяти, третий коммутатор 14, второй сумматор 15 и элемент ИЛИ 16. Блок 2 управления содержит первый

17, второй 18 и третий 19 элементы И-НЕ, триггер 20, первый элемент НЕ

Јъ 1C

СО

3147

21, первый 22 и второй 23 элементы . ИЛИ, первый элемент И 24, первый элемент ИЛИ-НЕ 25, четвертый элемент И-НЕ 26, второй элемент ИЛИ-НЕ 27, третий элемент ИЛИ 28, второй 29 и третий 30 элементы И, третий элемент ИЛИ-НЕ 31, второй 32 и третий 33 элементы НЕ.

Блок 3 формирования функций содер- жит умножитель 34, сумматор 35, накапливающий регистр 36 и выходной регистр 37.

Устройство работает следующим образом,

На вход сброса устройства подается уровень О, по которому происходит обнуление регистра 37 блока 3, и триггер 20 блока 2 устанавливается в состояние 1 на ин- версном выходе. Сигнал 1 с инверсного выхода триггера 20 поступает на управляющий вход коммутатора 8, что приводит к подключению первой входной переменной к адресному входу блока 10 оперативной памяти. При этом на первом выходе элемента И-НЕ 11 действует сигнал 1, который по сигналу на входе ввода коэффициентов разрешает запись значений козф- фициентов представления воспроизводимой сплайн-функции в блок 10. Так как в начальный момент на прямом вы- ходе триггера 20 - сигнал О, то на выходе элемента И-НЕ 11 формируется сигнал готовности устройства к работе.

Управляющая ЭВМ распознает наличи сигнала ГОТОВНОСТЬ и заполняет блок 10 оперативной памяти значениями коэффициентов C,jНа вход запуска устройства подается сигнал СТАРТ в виде 1, При этом на выходе элемента И-НЕ 17 блока 2.появляется уровень О, который устанавливает триггер 20 в состояние 1 на прямом выходе, сбрасывает в нуль счетчики 4, 12 и через элемент НЕ 32 блока 2 записывает коды первой и второй входных пере- менных во входной регистр 9. 1 на прямом выходе триггера 20 разрешает прохождение тактовых импульсов на выход элемента И-НЕ 18, На входы элемента И-НЕ 26 подается сигнал с выхода нулевого и первого разрядов счетчика 12, поэтому при формировани на его выходе I она инвертируется элементом ИЛИ-НЕ 27 и разрешает про

хождение тактовых импульсов с выхода элемента НЕ 21 на выход элемента ИЛИ 28. Нулевой код с выхода счетчика 4 формирует на выходе элемента ИЛИ 23 блока 2 О, который запрещает прохождение сигналов через элемент И 24, а совместно с нулевым выходным сигналом элемента ИЛИ 16 разрешает прохождение первого тактового импульса на-выход элемента ИЛИ 22. Первый импульс с выхода элемента ИЛИ 22 сбрасывает в нуль накапливающий регистр 36 блока 3, но не проходит через элемент ИЛИ-НЕ 25, так как сигнал старта еще не снят управляющим устройством.

Сигнал О с выхода элемента ИЛИ , 16 с помощью коммутатора 6 подключает к адресному входу блока 5 постоянной памяти младшие разряды первой входной переменной X с выхода регистра 9, определяющих значение базисного сплайна В(Хр), Так как на первом вхо« де сумматора 7 действует нулевой код, то на его выходе образуется код, равный коду старших разрядов , первой входной переменной, который определяет первую половину адреса коэффициента С ; (значение индекса i) Вторую половину адреса коэффициента (значение индекса j) определяет код с выхода сумматора 15.

Задний фронт первого тактового импульса с выхода элемента ИЛИ 28 блока 2 записывает начальное значение во(Хр) базисного В-сплайна с выхода блока 5 постоянной памяти и значение коэффициента С; с выхода блока 10 оперативной памяти в умножитель 34 блока 3, а также увеличивает содержимое счетчика 4 на единицу. При этом на выходе счетчика 4 формируется код 01, который приводит к изменению номера участка базисного В-сплайна и адреса коэффициента (на выходе сумматора 7 формируется код, соответствую, щий индексу i+1). Так как накапливающий регистр 36 блока 3 при этом обнулен, то умножитель 34 вычисляет первое произведение . В6(Х„), которое без изменений проходит на выход сумматора 35. Выходной код счетчика 4 не равен нулю, поэтому на выходе элемента ИЛИ 23 формируется сигнал 1, который запрещает работу элемента ИЛИ 22 и разрешает прохождение импульсов с выхода элемента И-НЕ 18 через элемент И 24 на вход разрешения записи накапливающего регистра 36 блока 3, следовательно, второй так товый импульс записывает первое произведение с выхода сумматора 35 в регистр 36. Так как на выходе счетчика 4 действует код 01, то по заднему фронту второго тактового импульса с выхода элемента ИЛИ 28 производится запись в умножитель 34 новых значений базисного сплайна и коэффициента, а счетчик 4 переводится в состояние 10. Умножитель 34 формирует второе произведение вида, которое суммируется в сумматоре 35 с предыдущим, записан- ным в регистре 35, и результат вновь заносится третьим тактовым импульсом с выхода элемента И 24 блока 2 в регистр 36, По заднему фронту третьего тактового импульса с выхода элемента ИЛИ 28 в умножитель 34 записываются новые значения базисного сплайна и коэффициента, а счетчик 4 переводит- ся в состояние I1, Таким обоазом, на выходе сумматора 35 блока 3 формиру- ется первая сумма четырех произведений.

Счетчик 4 обнуляется, и на выходе элемента ИЛИ 23 снова появляется нулевой сигнал, который запрещает работу элемента И 24 и разрешает прохождение пятого тактового импульса через элемент ИЛИ 22, сбрасывающего в нуль регистр .36 блока 3. Сигнал старта устройства снят, поэтому пятый тактовый импульс с выхода элемента ИЛИ 22 проходит на выход элемента ИЛИ- НЕ 25 и разрешает запись в нулевую ячейку блока 13 оперативной памяти первой суммы четырех произведений. Нулевой сигнал с выхода элемента ИЛИ 16 запрещает работу элемента И 30, поэтому О с его выхода открывает элемент ИЛИ-НЕ 31 и на суммирующий вход счетчика 12 поступает импульс с выхода элемента ИЛИ-НЕ 25, который своим задним фронтом переводит.счетчик 12 в состояние 0001. При этом код второй половины адреса коэффициента, формируемый сумматором 15, увеличива- ется на единицу. На следующих четырех тактах осуществляется формирование второй суммы четырех произведений (причем второй индекс увеличен на единицу) аналогично. На адресном входе блока 13 оперативной памяти действует код 01, поэтому вторая сумма записывается в его первую ячейку. Аналогичным образом происхотг

дит формирование третьей и четвертой сумм четырех произведений.

На выходе элемента ИЛИ-НЕ 27 появляется 1, которая запрещает прохождение тактовых импульсов через . элемент ИЛИ 28. Таким образом, счетчик 4 не перебрасывается, оставаясь нулевом состоянии. Однако тактовый импульс проходит через открытые элементы ИЛИ 22 и ИЛИ-НЕ 25 и записывает четвертую сумму в третью ячейку блока 13 оперативной памяти, а также проходя через открытый элемент ИЛИ-Н 31, перебрасывает счетчик 12 в состояние.0100. В результате сигнал 1, появившийся на выходе элемента ИЛИ 16, с помощью компаратора 6 подает н адресный вход блока 5 постоянной пам ти младшие разряды второй входной переменной У и с помощью коммутатор 14 подключает к второму информационному входу умножителя 34 блока 3 вы- ход блока 13 оперативной памяти, а также разрешает прохождение тактовых импульсов с выхода элемента И-НЕ 18 через элемент И 30. 1 с выхода элемента ИЛИ 16 проходит через элемент ИЛИ 22, инвертируется элементом ИЛИ-НЕ 25 и держит элемент ИЛИ-НЕ 31 в открытом состоянии. Следовательно, тактовые импульсы начинают поступать с выхода элемента И 30 через открытый элемент ИЛИ-НЕ 31 на суммирующий вход счетчика 12. Тактовый импульс записывает своим задним фронтом значение B0(Yp) базисного Б-сплайна, соответствующего младшим разрядам второй входной переменной Y, а также первую сумму четырех произведений, считываемую из нулевой ячейки блока 13 оперативной памяти, в умножитель 34 блока 3 и устанавливает на выходе нулевого и первого разрядов счетчика 12 код 01. Умножитель 34 формирует произведение, которое заносится так- товым импульсом в накапливающий регистр 36 блока 3. При этом импульс с выхода элемента ИЛИ 28 своим задним фронтом переписывает из блока 13 оперативной памяти и блока 5 постоян ной памяти в умножитель 34 блока 3 новые значения суммы произведений и базисного сплайна и перебрасывает счетчик 12 в состояние 10. Процесс вычисления протекает аналогично .

Когда на третьем выходе счетчика 12 появляется сигнал I, открывающий элемент И 29, тактовый импульс проходит на выход элемента И 29 и записывает результат, сформированный на выходе сумматора 35, в выходной регистр 37 блока 3. При этом сигналом выхода элемента НЕ 33 производится сброс триггера 20, на инверсном выходе которого появляется сигнал, говорящий об окончании процесса очередного вычисления и о готовности устройства к приему новых кодов входных переменных и новому преобразованию. Новое преобразование производится с подачей очередного сигнала СТАРТ и происходит аналогично описанному выше,

Формула изобретения 1. Устройство для вычисления функций, содержащее генератор импульсов, блок управления, блок формирования функций, первый и второй счетчики, блок постоянной памяти, первый и второй блоки оперативной памяти, с первого по третий коммутаторы, первый сумматор, входной регистр и элемент И - НЕ, причем выход генератора импульсов соединен с тактовым входом блока управления, входы пуска и сброса которого подключены соответственн к входам пуска и сброса устройства, вход сброса которого соединен с первым входом начальной установки блока формирования функций, выход значения функции которого соединен с выходом функции устройства, выход установки и выход разрешения записи промежуточного результата блока управления соединены соответственно с вторым входом начальной установки и входом разрешения записи в накапливающий регистр блока формирования функций, выход признака умножения блока управления соединен с тактовым входом блока формирования функций и входом суммирования первого счетчика, первый информационный вход блока формирования функций соединен с выходом блока постоянной памяти, адресный вход с нулевого по (р-1)й разрядов которого соединен с выходом первого коммутатора, где р - количество младших разрядов аргумента, адресный вход с р-го по (Р+П-Й разрядов под- ключей к выходам соответственно ну- левого и первого разрядов первого счетчика, информационному входу соответственно нулевого и первого разрядов блока управления и входу нулевого и первого разрядов первого операнда первого сумматора, вход остальных разрядов первого операнда которого соединен с входом логического нуля устройства, выход первого сумматора соединен с первым информационным входом с нулевого по (д-р - 1)-й разрядов второго коммутатора, где п- разрядность аргументов, второй инфор мацирнный вход которого подключен к входу первого аргумента устройства и информационному входу первой группы разрядов входного регистра, информационный вход второй группы разрядов которого соединен с входом второго аргумента устройства и информационным входом первого блока оперативной памяти, адресный вход которого соединен с выходом второго коммутатора вход разрешения записи данных первого блока оперативной памяти подключен к выходу элемента И - НЕ, первый

и второй входы которого соединены соответственно с входом признака ввода коэффициентов устройства и выходом признака коммутаций блока управления, подключенного к управляющему входу второго коммутатора, выход признака окончания счета блока управления соединен с выходом готовности устройства, выход признака цикла блока управления соединен с входом суммирования второго счетчика, выход сброса блока управления соединен с входами сброса первого и второго счетчиков, выход записи аргументов блока управления соединен с входом разрешения записи входного регистра, выход разрядов с нулевого по р-й которого соединен с первым информационным входом первого коммутатора, причем блок формирования функции содержит умножитель, сумматор, накапливающий регистр, выходной регистр, первый и второй информационные входы умножителя соединены соответственно с первым и вторым информационными входами блока формирования функций, выход умножителя соединен с входом первого слагаемого сумматора, вход второго слагаемого которого соединен с выходом накапливающего регистра, информационный вход котрого -соединен с выходом сумматора, выходом промежуточного результата блока формирования функций и информационным входом выходного регистра, выход которого подключен к выходу значения функции блока формирования функции, первый и второй входы начальной установки которого соединены с входами установки соответственно выходного и накапливающего регистров, входы разрешения записи которых сог- единены соответственно с входами разрешения выдачи и разрешения записи в накапливающий регистр блока формирования функций, тактовый вход которого соединен с входом синхронизации умножителя, отличающееся тем, что, с целью расширения области применения за счет дополнительной возможности вычисления функций двух пере- менных,в него введены второй сумматор и элемент ИЛИ,причем выход нулевого и первого разрядов второго счетчика соединен с адресным входом второго блока оперативной памяти, информаци- онным входом второго и третьего разрядов блока управления и входом нулевого и первого разрядов первого операнда второго сумматора, вход остальных разрядов первого операнда которого соединен с входом логического нуля устройства, выход второго сумматора соединен с первым информационным входом с (п-р)-го по Г2(п-р)lj-го разрядов второго ком- мутатора, вход второго операнда с нулевого по (п-р-1)-й разрядов второго сумматора соединен с выходом соответственно с р-ро по (п-1)-й разрядов входного регистра, выход разрядов с n-го по (п+р-1)-й которого соединен с вторым информационным входом первого коммутатора, выход разрядов с (п+р) го по (2п-1)-й входного регистра соединен с входом второго операнда вто- рого сумматора, первый вход элемента ИЛИ подключен к выходу второго разряда второго счетчика, выход элемента ИЛИ соединен с управляющими входами первого и третьего коммутаторов и информационным входом четвертого разряда блока управления, информационный вход пятого разряда которого соединен с выходом третьего разряда второго счетчика, соединенного с вторым входом элемента ИЛИ, выход выдачи результата блока управления соединен с входом разрешения выдачи блока формирования функций, выход промежуточного результата которого ,. соединен с информационным входом второго блока оперативной памяти, вход разрешения записи которого соединен с выходом разрешения записи в опера-

ю f5 20 5 30 5 0 5 с

0

тивную память блока управления, выход второго блока оперативной памяти соединен с первым информационным BX.Q-. дом третьего коммутатора, второй информационный вход которого соединен с выходом первого блока оперативной памяти, выход третьего коммутатора соединен с вторым информационным входом блока формирования функций.

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок управления содержит с первого по четвертый элементы И - НЕ, триггер, три элемента НЕ, первый и второй элементы ИЛИ, три элемента И, три элемента ИЛИ-НЕ, причем первые входы первого и второго элементов И-НЕ подключены к тактовому входу блока управления, вход пуска которого соединен с вторым входом первого элемента И-НЕ , выход которого соединен с первым входом третьего элемента И-НЕ, входом установки в 1 триггера и подключен к выходу сброса блока управления, вход сброса которого соединен с входом установки в О триггера, инверсный выход которого подключен к выходу признака коммутации блока управления выход окончания которого соединен с третьим входом первого элемента И-НЕ и подключен к выходу третьего элемента И-НЕ, второй вход которого соединен с прямым выходом триггера и вторым входом второго элемента И-НЕ, выход которого через первый элемент НЕ соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и первым входом первого элемента И, второй вход и выход котог рого соединены соответственно с выходом второго элемента И - НЕ и выходом разрешения записи промежуточного результата блока управления, выход разрешения записи в оперативную память которого соединен с выходом первого элемента ИЛИ-НЕ, первый и второй входы которого соединены соответственно с входом пуска блока . управления и выходом первого элемента ИЛИ, подключенным к выходу установки блока управления, информационный вход нулевого и первого разрядов которого соединен с первым и вторым входами второго элемента ИЛИ, информационный вход второго и третьего разрядов блока управления соединен с первым и вторым входами четвертого элемента

И-НЕ, выход которого соединен с вторым входом Второго элемента ИЛИ-НЕ, первый вход и выход которого соединены соответственно с выходом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого элемента НЕ и выходом признака умножения блока управления, выход выдачи результата которого соединен с выходом второго элемента И, первый вход которого соединен с информационным входом пятого разряда блока управления, второй вход второго элемента И соединен с выходом второго элемента И-НЕ и первым входом третьего элемента И, второй вход которого соединен с третьим входом первого элемента ИЛИ и подключен к информационному входу четвертого разряда блока управления, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход и выход которого соединены соответственно с выходом первого элемента ИЛИ-НЕ и выходом признака цикла блока управления, выход сброса которого через второй элемент НЕ соединен с выходом записи аргументов блока управления, выход выдачи результата кото-ч рого через третий элемент НЕ соединен с входом синхронизации триггера, информационный вход которого соединен с входом логического нуля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| Цифровой функциональный генератор | 1985 |

|

SU1282104A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения устройства. Устройство содержит генератор тактовых импульсов, блок управления, блок формирования функций, первый и второй счетчики, блок постоянной памяти, первый, второй и третий мультиплексоры, первый и второй сумматоры, входной регистр, первый и второй блоки оперативной памяти, элемент И-НЕ, элемент ИЛИ. Блок управления и синхронизации содержит первый, второй, третий и четвертый элементы И-НЕ, триггер, первый, второй и третий элементы НЕ, первый, второй и третий элементы ИЛИ, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ-НЕ. Блок формирования функций содержит умножитель, сумматор, накапливающий регистр, выходной регистр. Благодаря дополнительно введенным блокам и новому построению схемы, устройство позволяет дополнительно реализовать режим вычисления функций двух переменных. 1 з.п.ф-лы, 3 ил.

Cmgaih CdpOSL

35

37

Фиг.Ъ

| Устройство для формирования монотонных функций двух переменных | 1977 |

|

SU763879A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-15—Публикация

1987-08-18—Подача