Изобретение относится к вычислительной технике и может быть использовано в устройствах для распределения ресурсов в вычислительных комплексах.

Цель изобретения - повышение быстродействия устройства.

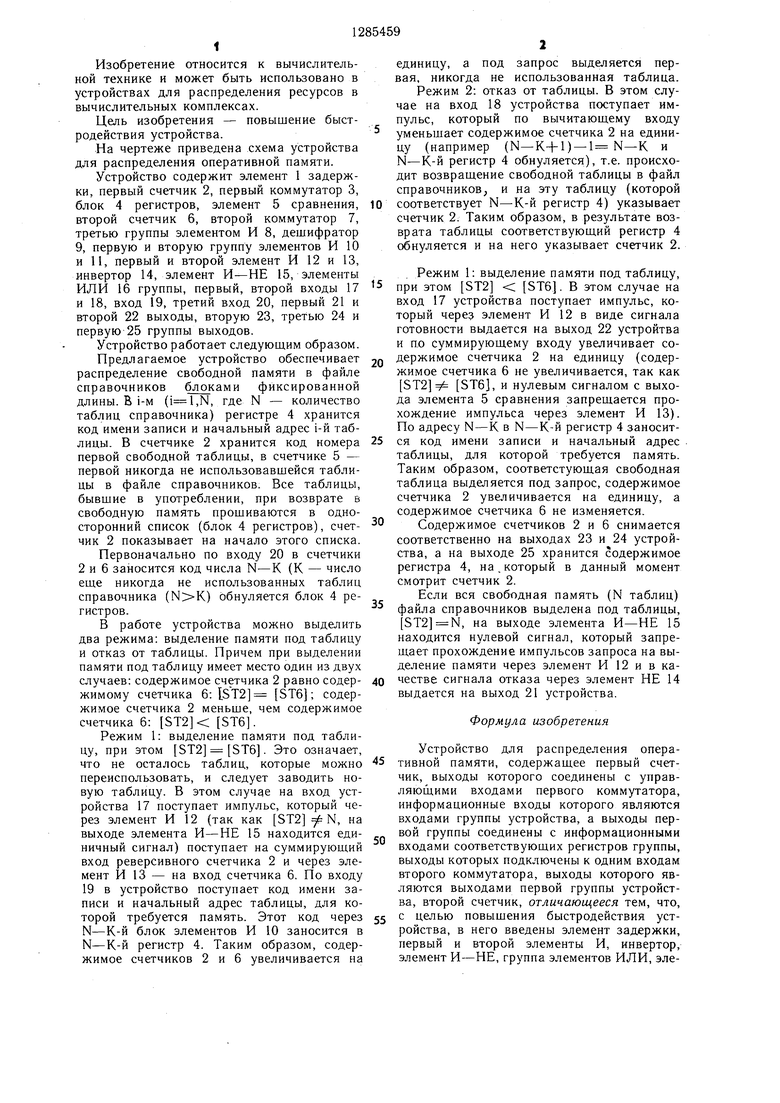

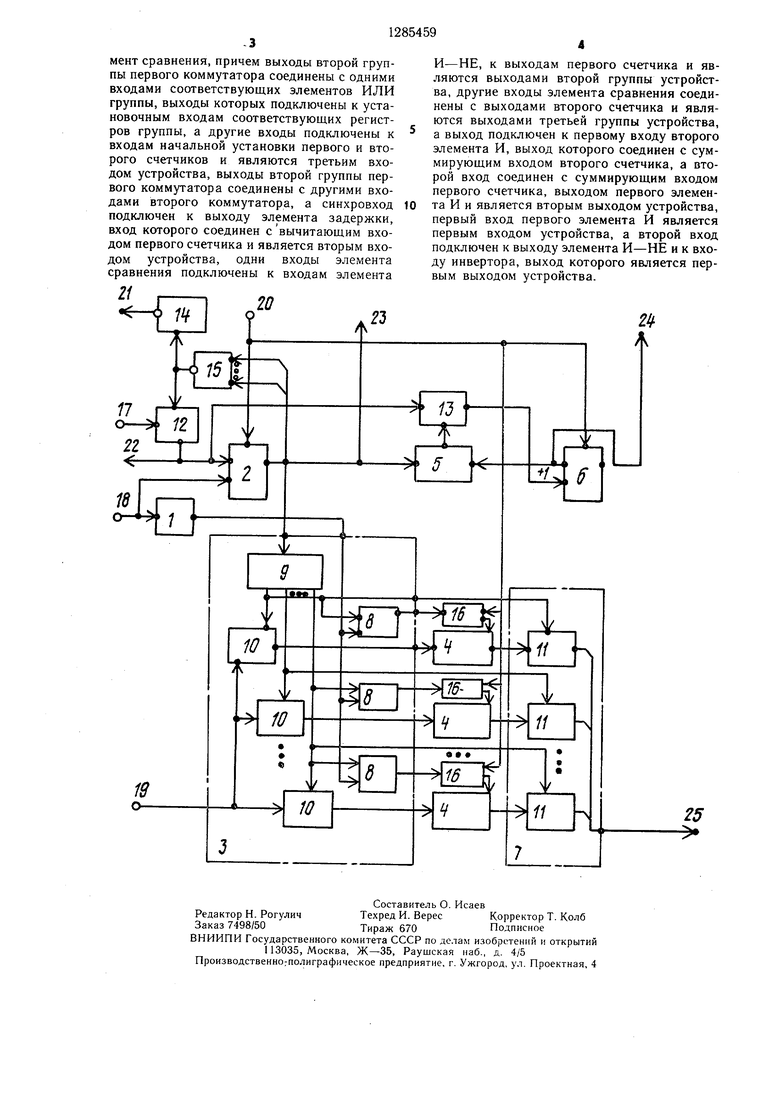

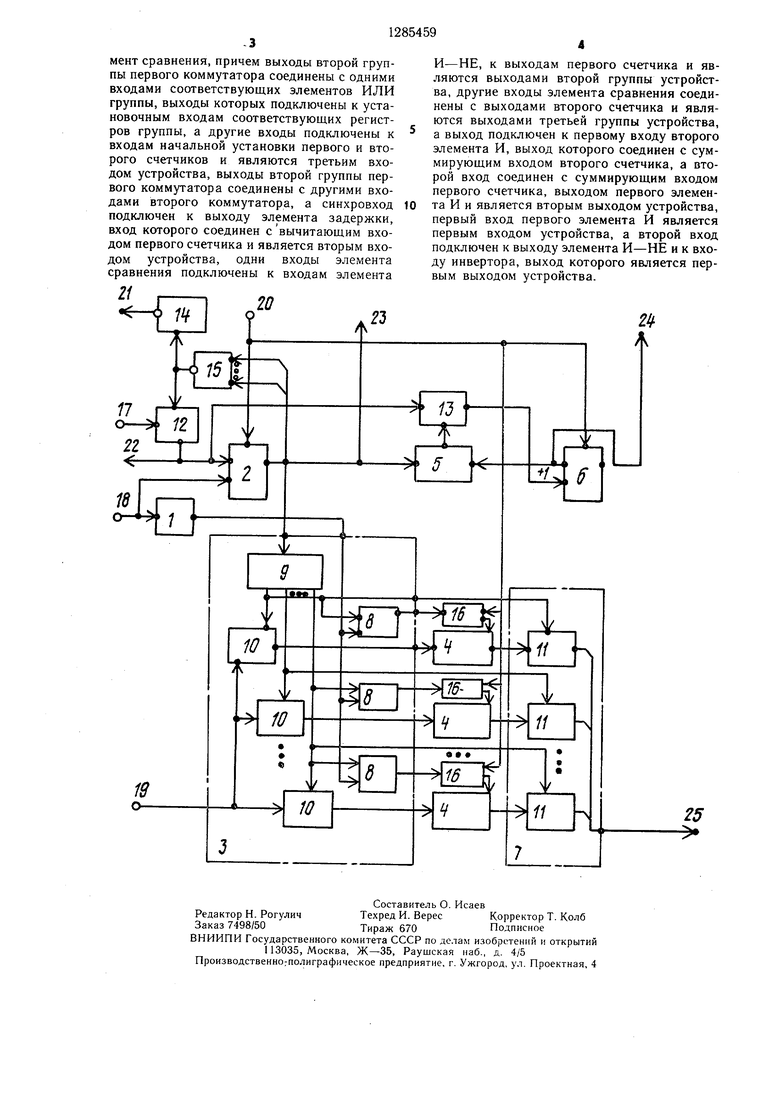

На чертеже приведена схема устройства для распределения оперативной памяти.

Устройство содержит элемент 1 задержки, первый счетчик 2, первый коммутатор 3, блок 4 регистров, элемент 5 сравнения, второй счетчик 6, второй коммутатор 7, третью группы элементом И 8, дешифратор 9, первую и вторую группу элементов И 10 и 11, первый и второй элемент И 12 и 13, инвертор 14, элемент И-НЕ 15, элементы ИЛИ 16 группы, первый, второй входы 17 и 18, вход 19, третий вход 20, первый 21 и второй 22 выходы, вторую 23, третью 24 и первую 25 группы выходов.

Устройство работает следующим образом.

Предлагаемое устройство обеспечивает распределение свободной памяти в файле справочников блоками фиксированной длины, в i-M (,N, где N - количество таблиц справочника) регистре 4 хранится код имени записи и начальный адрес i-й таблицы. В счетчике 2 хранится код номера первой свободной таблицы, в счетчике 5 - первой никогда не использовавшейся таблицы в файле справочников. Все таблицы, бывшие в употреблении, при возврате в свободную память прошиваются в односторонний список (блок 4 регистров), счет- чик 2 показывает на начало этого списка.

Первоначально по входу 20 в счетчики 2 и б заносится код числа N-К (К - число еще никогда не использованных таблиц справочника () обнуляется блок 4 регистров.

В работе устройства можно выделить два режима: выделение памяти под таблицу и отказ от таблицы. Причем при выделении памяти под таблицу имеет место один из двух случаев: содержимое счетчика 2 равно содер- жимому счетчика 6: ST2 содержимое счетчика 2 меньше, чем содержимое счетчика 6: ST2 ST6.

Режим 1: выделение памяти под таблицу, при этом ST2 ST6. Это означает, что не осталось таблиц, которые можно переиспользовать, и следует заводить новую таблицу. В этом случае на вход устройства 17 поступает импульс, который через элемент И 12 (так как ST2 N, на выходе элемента И-НЕ 15 находится единичный сигнал) поступает на суммирующий вход реверсивного счетчика 2 и через элемент И 13 - на вход счетчика 6. По входу 19 в устройство поступает код имени записи и начальный адрес таблицы, для которой требуется память. Этот код через N-К-й блок элементов И 10 заносится в N-К-й регистр 4. Таким образом, содержимое счетчиков 2 и 6 увеличивается на

0

0 5

0

55

5

0

единицу, а под запрос выделяется первая, никогда не использованная таблица. Режим 2: отказ от таблицы. В этом случае на вход 18 устройства поступает импульс, который по вычитающему входу уменьшает содержимое счетчика 2 на единицу (например (N-К+1) - 1 N-К и N-К-й регистр 4 обнуляется), т.е. происходит возвращение свободной таблицы в файл справочников, и на эту таблицу (которой соответствует N-К-й регистр 4) указывает счетчик 2. Таким образом, в результате возврата таблицы соответствующий регистр 4 обнуляется и на него указывает счетчик 2.

Режим 1: выделение памяти под таблицу, при этом ST2 ST6. В этом случае на вход 17 устройства поступает импульс, который через элемент И 12 в виде сигнала готовности выдается на выход 22 устройтва и по суммирующему входу увеличивает содержимое счетчика 2 на единицу (содержимое счетчика 6 не увеличивается, так как ST6, и нулевым сигналом с выхода элемента 5 сравнения запрещается прохождение импульса через элемент И 13). По адресу N-К в N-К-й регистр 4 заносится код имени записи и начальный адрес таблицы, для которой требуется память. Таким образом, соответстующая свободная таблица выделяется под запрос, содержимое счетчика 2 увеличивается на единицу, а содержимое счетчика 6 не изменяется.

Содержимое счетчиков 2 и 6 снимается соответственно на выходах 23 и 24 устройства, а на выходе 25 хранится содержимое регистра 4, на, который в данный момент смотрит счетчик 2.

Если вся свободная память (N таблиц) файла справочников выделена под таблицы, , на выходе элемента И-НЕ 15 находится нулевой сигнал, который запрещает прохождение импульсов запроса на выделение памяти через элемент И 12 и в качестве сигнала отказа через элемент НЕ 14 выдается на выход 21 устройства.

Формула изобретения

Устройство для распределения оперативной памяти, содержащее первый счетчик, выходы которого соединены с управ- ЛЯЮ1ДИМИ входами первого коммутатора, информационные входы которого являются входами группы устройства, а выходы первой группы соединены с информационными входами соответствующих регистров группы, выходы которых подключены к одним входам второго коммутатора, выходы которого являются выходами первой группы устройства, второй счетчик, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены элемент задержки, первый и второй элементы И, инвертор, элемент И-НЕ, группа элементов ИЛИ, элемент сравнения, причем выходы второй группы первого коммутатора соединены с одними входами соответствующих элементов ИЛИ группы, выходы которых подключены к установочным входам соответствующих регистров группы, а другие входы подключены к входам начальной установки первого и второго счетчиков и являются третьим входом устройства, выходы второй группы первого коммутатора соединены с другими входами второго коммутатора, а синхровход подключен к выходу элемента задержки, вход которого соединен с вычитающим входом первого счетчика и является вторым входом устройства, одни входы элемента сравнения подключены к входам элемента

И-НЕ, к выходам первого счетчика и являются выходами второй группы устройства, другие входы элемента сравнения соединены с выходами второго счетчика и являются выходами третьей группы устройства, а выход подключен к первому входу второго элемента И, выход которого соединен с суммирующим входом второго счетчика, а второй вход соединен с суммирующим входом первого счетчика, выходом первого элемента И и является вторым выходом устройства, первый вход первого элемента И является первым входом устройства, а второй вход подключен к выходу элемента И-НЕ и к входу инвертора, выход которого является первым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения адреса файла памяти | 1988 |

|

SU1552193A1 |

| Система коммутации | 1985 |

|

SU1317449A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Резервированное устройство для решения интегральных уравнений | 1981 |

|

SU1092511A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1145357A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для распределения ресурсов в вычислительных комплексах. Целью изобретения является повышение быстродействия устройства. Устройство содержит первый и второй счетчики, первый и второй коммутаторы, элемент сравнения, регистры и элементы ИЛИ группы, элементы И, И-НЕ, инвертор и элемент задержки. Повышение быстродействия достигается за счет аппаратной реализации на счетчиках и коммутаторах режимов «Выделение памяти на таблицу и «Отказ от таблицы при распределении памяти в файле справочников. 1 ил. оо СП и1 ел со

| Устройство сопряжения | 1976 |

|

SU602934A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1984-11-11—Подача