Изобретение относится к устройсг вам фильтрации и усреднения электрических сигналов и может быть использовано в системах автоматики и информационно-измерительной техники.

Цель изобретения - повьшение помехоустойчивости устройства.

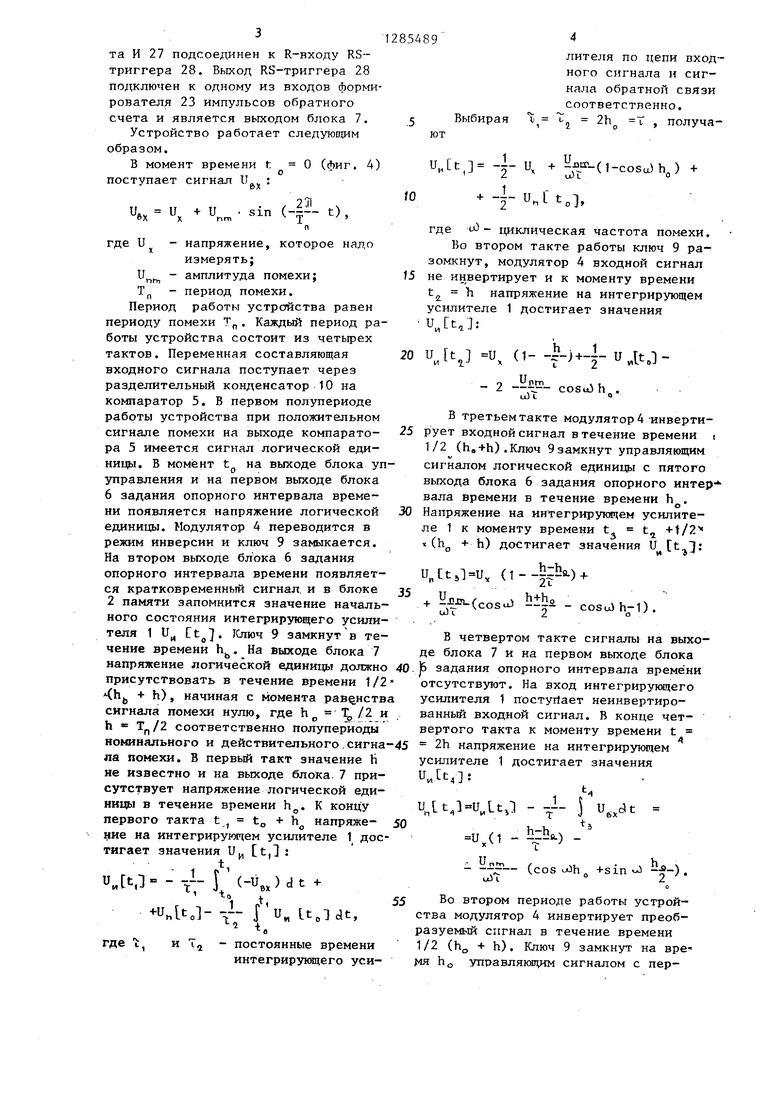

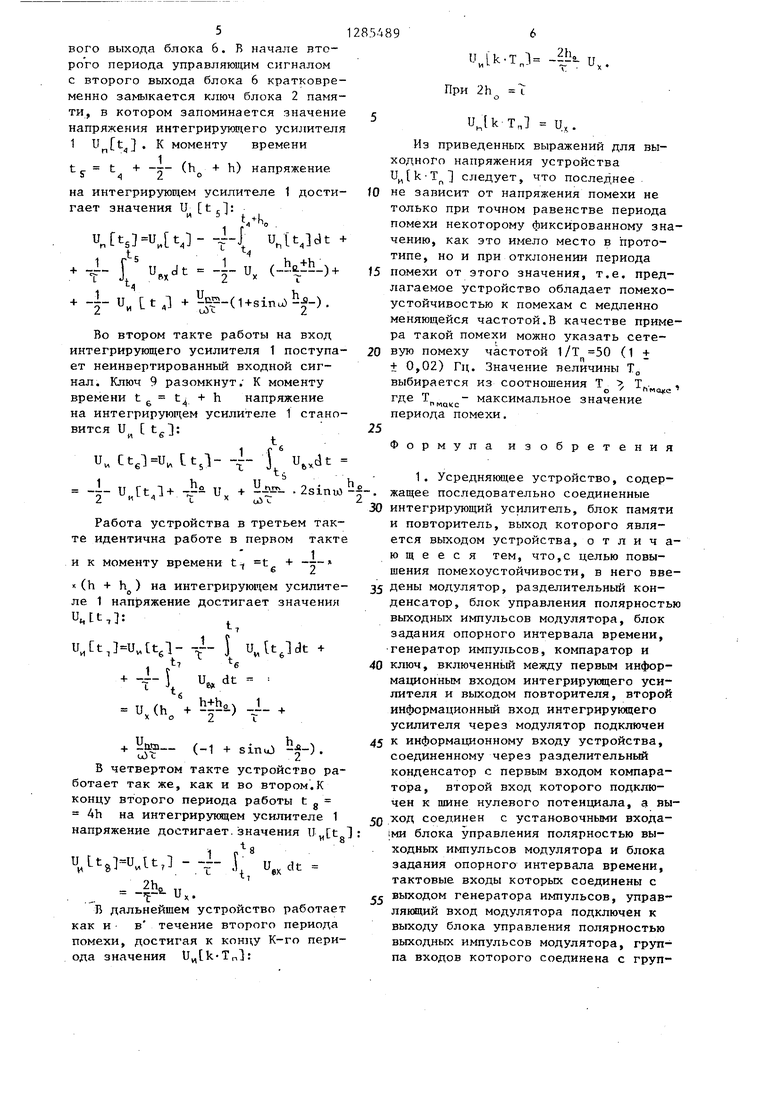

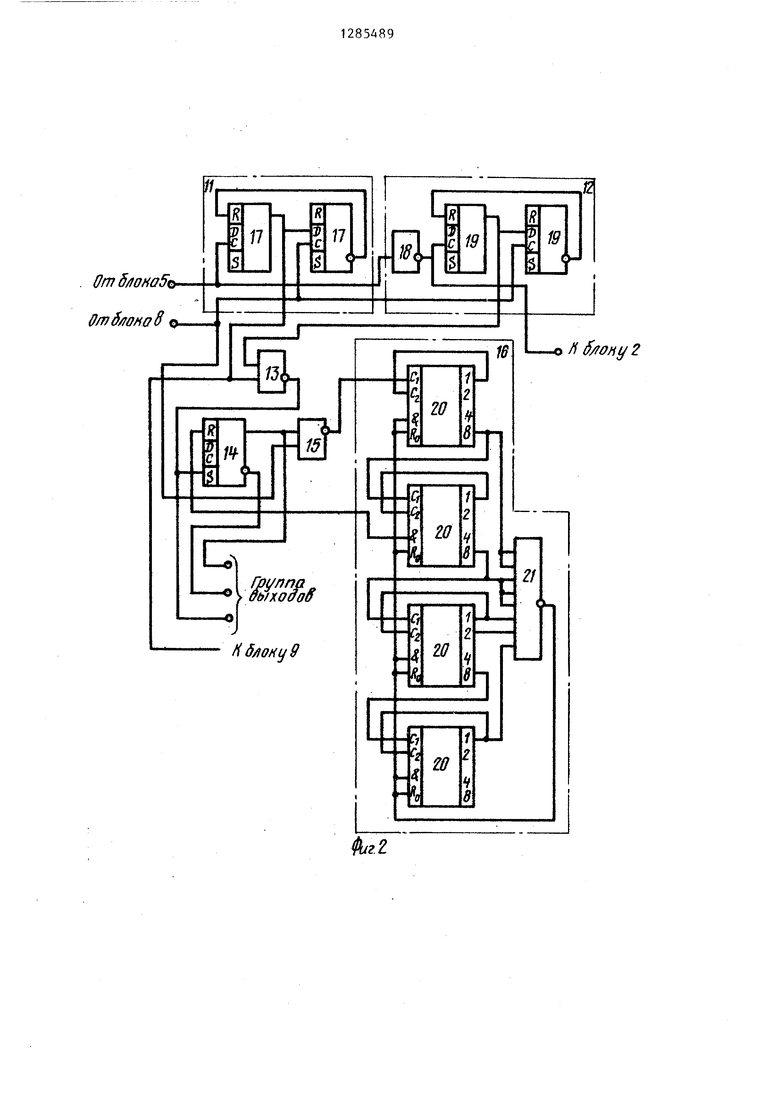

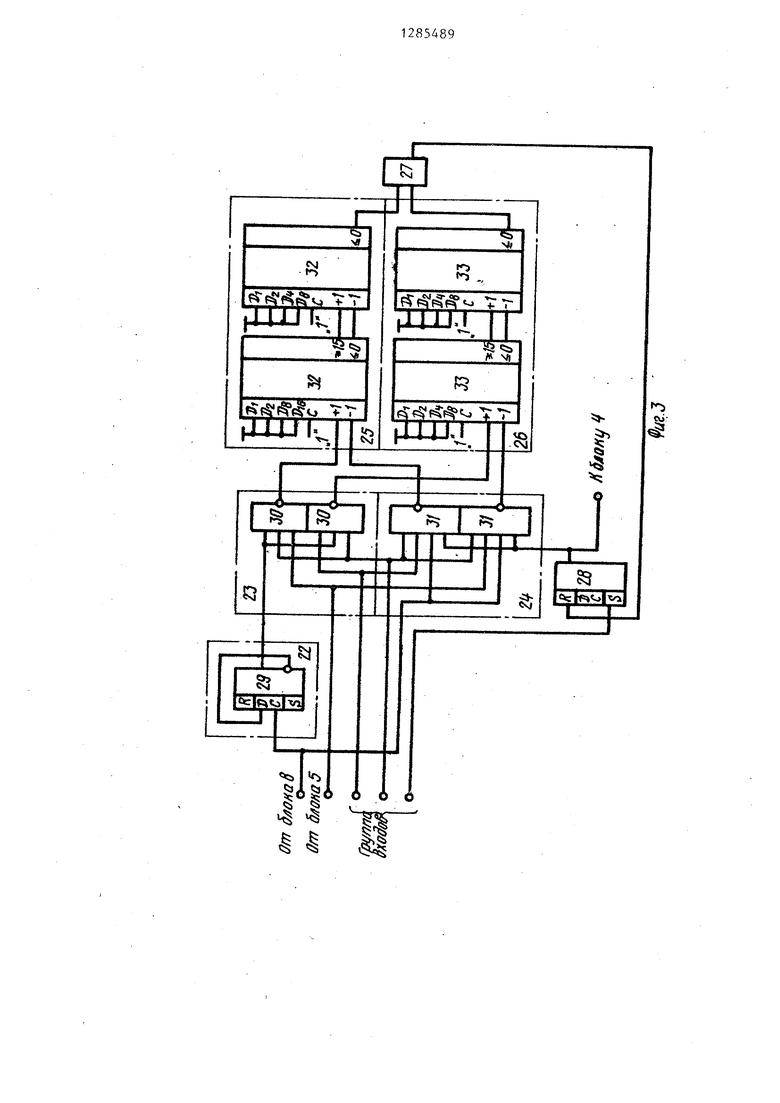

На фиг. 1 представлена функциональная схема усредняющего устройства; на фиг. 2 - структурная схема блока задания опорного интервала времени; на фиг. 3 - схема блока управления полярностью выходных импульсов модулятора; на фиг. 4 - временные диаграммы,поясняющие работу устройства.

Усредняющее устройство (фиг. 1) содержит интегрирующий усилитель 1, ёлок 2 памяти, повторитель 3, модулятор 4, компаратор 5, блок 6 задания опорного интервала времени, блок 7 управления полярностью выходных импульсов модулятора, генератор 8 импульсов, ключ 9, разделительный конденсатор 10. Модулятор 4, интегрирующий усилитель 1, блок

2памяти и повторитель 3 соединены последовательно. Выход повторителя

3через ключ 9 подсоединен к информационному входу интегрирующего усилителя 1 и является выходом устройства. Информационный вход устройства подключен к входу модулятора 4 и через разделительный конденсатор 10 - к входу компаратора 5. Выход последнего соединен с установочными входам блока 7 управления полярностью выходных импульсов модулятора и блока 6 задания опорного интервала времени, тактовые входы которых подключены к выходу генератора 8 импульсов, группа входов блока 7 подсоединена к группе выходов блока 6. Соответственно выход блока 7 соединен с управля- .ющим входом модулятора 4. Первый и второй выходы блока 6 подключены к входу управления записью блока 2 памяти и управляющему входу ключа 9.

Блок 6 задания опорного интервала времени (фиг 2) содержит формирователь 11 положительного фронта импульса, формирователь 12 отрицательного фронта ийпульса, элемент ИЛИ-НЕ 13, RS-триггер 14, элемент И-ИЕ 15, формирователь 16 опорного интервала времени. Установочный и тактнрзпощий входы блока задания опорного интервала времени соединены с первым и

5

вторым входами формирователей положительного 11 и отрицательного 12 фронтов импульса соответственно, выход формирователя 11 положительного фронта импульса и второй выход формирователя 12 отрицательного фронта импульса соединены с соответствующими входами, элемента ИЛИ-НЕ 13. Выход элемента ИЛИ-НЕ 13 соединен также с S-входом RS-триггера 14, R-вход которого подключен к выходу формирователя 16 опорного интервала времени, вход которого подсоединен к выходу элемента И-НЕ 15. Прямой выход 5 RS-триггера 1-4 подключен к первому входу элемента И-НЕ 15, второй вход которого является тактирукщим входом блока 6.

Формирователь 11 положительного 0 фронта импульса состоит из двух RS- триггеров 17. Формирователь 12 отрицательного фронта импульса состоит из элемента НЕ 18 и двух RS-триггеров 19. Формирователь 16 опорного интервала времени содержит счетчики 20 и элемент И-НЕ 21.

Блок 7 управления полярностью выходных импульсов модулятора (фиг. 3) содержит делитель 22 частоты, форми- рователь 23 импульсов прямого счета, формирователь 24 импульсов обратного счета, два реверсивных счетчика 25 и 26, элемент И 27, RS-триггер 28.

5 Делитель частоты 22 выполнен на RS-триггере 29, Формирователи им-- пульсов прямого 23 и обратного 24 счета содержат элементы И-НЕ 30 и 31. Реверсивные счетчики 25 и 26 0 выполнены на счетчиках 32 и 33 соответственно. Вход делителя 22 частоты является тактирукедим входом блока 7, первые входы формирователей импульсов прямого 23 и обратно- 5 го 24 счета являются установочным входом блока 7.

Выход делителя 22 частоты подключен к первому входу формирователя

0 23 импульсов прямого счета, первый и второй выходы которого подсоединены к первым входам реверсивных счетчиков 25 и 26 соответственно. Первый и второй выходы фомировате5 ля 24 импульсов обратного счета подключены к вторым входам реверсивных счетчиков 25 и 26, выходы которых соединены с соответствующими входами элемента И 27. ВыхоД элемента И 27 подсоединен к R-входу КЗ- триггера 28. Выход RS-триггера 28 подключен к одному из входов формирователя 23 импульсов обратного счета и является вькодом блока 7.

Устройство работает следующим образом.

В момент времени поступает сигнал U

t О (фиг. 4)

6Х

и + и

sin

),

п

где и,

- напряжение, которое надо измерять;

и - амплитуда помехи;

Т - период помехи. Период работы устройства равен периоду помехи Т. Каждый период работы устройства состоит из четырех тактов. Переменная составляющая входного сигнала поступает через разделительный конденсатор 10 на компаратор 5. В первом полупериоде работы устройства при положительном сигнале помехи на выходе компаратора 5 имеется сигнал логической единицы. В момент t на выходе блока у управления и на первом выходе блока 6 задания опорного интервала времени появляется напряжение логической единицы. Модулятор 4 переводится в режим инверсии и ключ 9 зa вJIкaeтcя. На втором выходе блока 6 задания опорного интервала времени появляет ся кратковременный сигнал, и в блоке 2 памяти запомнится значение начального состояния интегрирующего усилителя 1 Uj, 9 замкнут в течение времени h. На выходе блока 7 напряжение логической единиць должн присутствовать в течение времени 1/

(h + h), начиная с момента равенств сигнала помехи нулю, где h и h соответственно полупериоды нокинального и действительного.сигна ла помехи. В первый такт значение Н не известно и на выходе блока. 7 присутствует напряжение логической единицы в течение времени h,. К концу первого такта t , t, + h напряже- ние на интегриру1одем усилителе 1 достигает значения U t,l :

UHW - -r(-u,,)dt

t

-Ubltcl- Ги„ It,- At,

-t где t, и T,j - постоянные времени

интегрирунщего уси-

лителя по цепи входного сигнала и сигнала обратной связи соответственно.

Выбирая

2h Т

получают

UHtt:J + Н.шг()Ь„)

iO

-Г

u.l

U U Ctjl U,

где tO - циклическая частота помехи. Во втором такте работы ключ 9 разомкнут, модулятор 4 входной сигнал не инвертирует и к моменту времени tj h напряжение на интегрирующем усилителе 1 достигает значения и t

f45

Ctjl U,

и

(,,

. cOt

cosui h

U U Ctjl U,

в третьем такте модулятор 4 -инверти- рует входной сигнал в течение времени i 1/2 (he+h).Ключ 9замкнут управляющим сигналом логической единицы с пятого выхода блока 6 задания опорного интер- вала времени в течение времени h . Напряжение на интегрирую(чем усилите-i-f/2

ле 1 к моменту времени t (h + h) достигает значения

(t - .)

U U Ctjl U,

+ (COS-J blbo cosu)h-1).

В четвертом такте сигналы на выходе блока 7 и на первом выходе блока б задания опорного интервала времени отсутствуют. На вход интегрирующего усилителя 1 постуйает неинвертированный входной сигнал. В конце четвертого такта к моменту времени t 2h напряжение на интегрирующем усилителе 1 достигает значения

Untt

,u,Lt,:i

U.

и

,(1 - - )

(cos uJh +sin J

b) 2 h

Bo втором периоде работы устройства модулятор 4 инвертирует преобразуемый сигнал в течение времени 1/2 (HO + h). Ключ 9 замкнут на вре о управляюацин сигналом с пер5

вого выхода блока 6. В начале второго периода управляющим сигналом с второго выхода блока 6 кратковременно замыкается ключ блока 2 памяти, в котором запоминается значение напряжения интегрирующего усилителя 1 , К моменту времени

t

4

. -1- (h

-t- h) напряжение

на интегрирующем усилителе 1 достигает значения U t,:

.Vk

и t, tj--J-Ju ltjdt

n -S-l Ltl-| - (4-f и

,

-2-U,

(h.ih) +

I

-|-U, Lt.l -.(Usinu)b|-).

Bo втором такте работы на вход интегрирующего усилителя 1 поступает неинвертированный входной сигнал. Ключ 9 разомкнут. К моменту

времени

6

t/ + h напряжение

на интeгpиpyюF eм усилителе 1 становится и t,.:

И Ь ,

и, Ct, -{- г u,,c3t

U U

- u.rtj+ - и,

+ .2sinu3

(д1 I.

Работа устройства в третьем такте идентична работе в первом такте

и к моменту времени t- t + т

к(h + h) на интегрирующем усилителе 1 напряжение достигает значения U.tt,:

u,ct,uat,i- ujtjdt

. -1- f

Ч.

U,(h,

и dt

h+ho4 1 + --) Ут-

uit

h.)

2

(-1 + sinu3

В четвертом такте устройство работает так же, как и во втором.К концу второго периода работы t g 4h на интегрирующем усилителе 1 напряжение достигает.значения

u.Lt,ujt, --1- i,;dt . . 4- и,.

Б дальнейшем устройство работает как и в течение второго периода помехи, достигая к концу К-го периода значения Uj,k Tn}:

- Jk-Tj -2j} и,.

При 2h

- 1

Ujk Tj и.

Из приведенных выражений для выходного напряжения устройства следует, что последнее

не зависит от напряжения помехи не только при точном равенстве периода помехи некоторому фиксированному значению, как это имело место в прототипе, но и при отклонении периода

помехи от этого значения, т.е. предлагаемое устройство обладает помехоустойчивостью к помехам с медленно меняющейся частотой.В качестве примера такой помехи можно указать сетевую помеху частотой 1/Т 50 (1 + + 0,02) Гц. Значение величины Т выбирается из соотношения Т Т

где ,- максимальное значение периода помехи.

.

5

Формула изобретения

1. Усредняющее устройство, содержащее последовательно соединенные

0 интегрирующий усилитель, блок памяти и повторитель, выход которого является выходом устройства, отличающееся тем, что,с целью повышения помехоустойчивости, в него вве35 дены модулятор, разделительный конденсатор, блок управления полярностью выходных импульсов модулятора, блок задания опорного интервала времени, генератор импульсов, компаратор и

40 ключ, включенной между первым информационным входом интегрирующего усилителя и выходом повторителя, второй

информационный вход интегрирующего усилителя через модулятор подключен

45 к информационному входу устройства, соединенному через разделительный конденсатор с первым входом компаратора, второй вход которого подключен к шине нулевого потенциала, а вы50 ход соединен с установочными входа- 1ми блока управления полярностью выходных импульсов модулятора и блока задания опорного интервала времени, тактовые входы которых соединены с

« выходом генератора импульсов, управ- лякщий вход модулятора подключен к выходу блока управления полярностью выходных импульсов модулятора, группа входов которого соединена с группой выходов биока задания опорного интервала времени, управляющий вход ключа и вход управления записью блока памяти подключены к первому и второму выходам блока задания опорного интервала времени соответственно, причем блок управления полярностью выходных импульсов модулятора содержит делитель частоты, формирователь импульсов прямого счета, формирователь импульсов обратного счета, два реверсивных счетчика, элемент И и RS-триггер, причем выход делителя частоты подключен к тактирующему входу формирователя импульсов прямого счета, первый и второй выходы которого подключены к входам суммирования первого и второго реверсивных счетчиков соответственно, входы вычитания которых соединены с первым и вторым выходами формирователя импульсов обратного счета, а их выходы соединены с первым и вторым входами элемента И, выход которого подключен к R-входу RS-триггера, установочные входы формирователей импульсов прямого и обратного счета являются установочным входом блока управления полярностью выходных импульсов модулятора, вход делителя частоты и тактирующий вход формирователя импульсов обратного счета являются тактирующим входом блока управления полярностью выходных импульсов модулятораi а информационные входы формирователей импульсов прямого и обратного счета и S- вход RS-триггера образуют группу входов блока управления полярностью выходных импульсов модулятора. 2. Устройство по п. 1, о т л и- чающееся тем, что блок задания опорного интервала времени содержит формирователи положительного и отрицательного фронтов импульса, элемент ИЛИ-НЕ, RS-триггер, элемент И-НЕ и формирователь опорного интервала времени, причем первый и второй входы формирователей положительного и отрицательного фронтов импуль- са являются установочным и тактирующим входами блока задания опорного интервала времени, выход формирова- ,теля положительного фронта импульса и первый выход формирователя отрипа- тельного фронта импульса соединены с соответствуюп1ими входами элемента ИЛИ-НЕ, выход которого соединен с S-входом RS-триггера, которого подключен к выходу формирова- теля опорного интервала времени, а прямой выход через элемент И-НЕ соединен с входом формирователя опорного интервала времени, причем выход формирователя положительного фронта импульса является первым выходом блока, второй выход формирователя отрицательного фронта импульса является вторым входом блока, инверсный выход RS-триггера, выход элемента ИЛИ-НЕ и прямой выход RS-триггера являются группой выходов блока.

/,

/z

p П

pC /

Ш

1ШИ /

M

M

/ 5

rc

/J9

Л-1

/J,

/

/ ILJh

/

Л //7/Л et)/WOO(

H длону9

Д

/

уУ

V

11

«3 M чд

ТГ

hU4Jl&

i

IЙ

HI

a

R

a

Qcifttoivj

fl

f

«1

P

f

цЗЖ

o

CsJ

I

J

ib

.- П

gg

.

fl

f

«1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Устройство перемножения двухАНАлОгОВыХ СигНАлОВ | 1979 |

|

SU801000A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| МНОГОКАСКАДНЫЙ УСИЛИТЕЛЬ | 1992 |

|

RU2106740C1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Устройство синхронизации электроразведочных приемников | 1987 |

|

SU1449961A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

Изобретение относится к устройствам фильтрации и усреднения электрических сигналов и может быть использовано в системах автоматики и информационно-измерительной техники. Целью изобретения является повышение помехоустойчивости устройства. Усредняющее устройство содержит интегрирующий усилитель 1, блок 2 памяти и повторитель 3, соединенные последовательно. Введение в устройство модулятора 4, блока 7 управления полярностью выходных импульсов модулятора, блока 6 задания опорного интервала времени и компаратора 5, а также соответствующих связей позволило повысить помехоустойчивость устройства не только при точном равенстве периода помехи некоторому фиксированному значению, но и при отклонении периода помехи от зтого значения. 1 з.п. ф-лы, 4 ил. Фиг.1

| Гутников B.C., Клементьев А.В., Лопатин В.В | |||

| Быстродействующие астатические усреднякщие измерительные преобразователи с синхронным временным квантованием в прямой цепи.- Труды ЛНУ, 1975, Р 342, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Интегро-дифференцирующее устройство | 1981 |

|

SU978161A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Усредняющее устройство | 1981 |

|

SU1023345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-09-17—Подача