(54) ИНТЕГРО-ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Кондукционный электромагнитный расходомер | 1983 |

|

SU1116320A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Интегратор для модуляционного радиометра | 1986 |

|

SU1401424A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Телеизмерительная система | 1983 |

|

SU1161981A1 |

| Способ управления группой импульсных преобразователей | 1981 |

|

SU1020958A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Экстраполятор для прогнозатора постепенных отказов | 1980 |

|

SU883916A1 |

| Преобразователь угловой скорости | 1984 |

|

SU1273810A1 |

Изобретение относится к автоматике и вычислительной технике.

Известно устройство, содержащее делитель напряжения на резисторах, термозависимый элемент, нагрузочный резистор, источник опорного напряжения и переключатель Cl.

Его недостаток - низкая точность и невозможность одновременного выполнения операций дифференцирования и интегрирования.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок умножения, интегратор, два релейных элемента, два запоминающих элемента, сумматор, генератор пилообразного напряжения, iнуль-орган и пороговый элемент. Устройство позволяет получать на выходе усредненную скорость изменения входного сигнала за период Т С2.

Недостатки известного устройства низкое быстродействие и узкий класс решаемых задач. Первое связано с тем, что точное значение скорости может быть получено не чаще, чем через Т/2. Такая дискретность может привести к существенным потерям точности в работе систем автоматического регулирования, использующих устройство. Второй недостаток обусловлен тем, что несмотря на относительную сложность устройства, оно позволяет определять только производную входного сигнгша.

Цель изобретения - расширение класса решаемых задач за счет определения интегральных характеристик

10 исследуемого сигнала и повышение быстродействия.

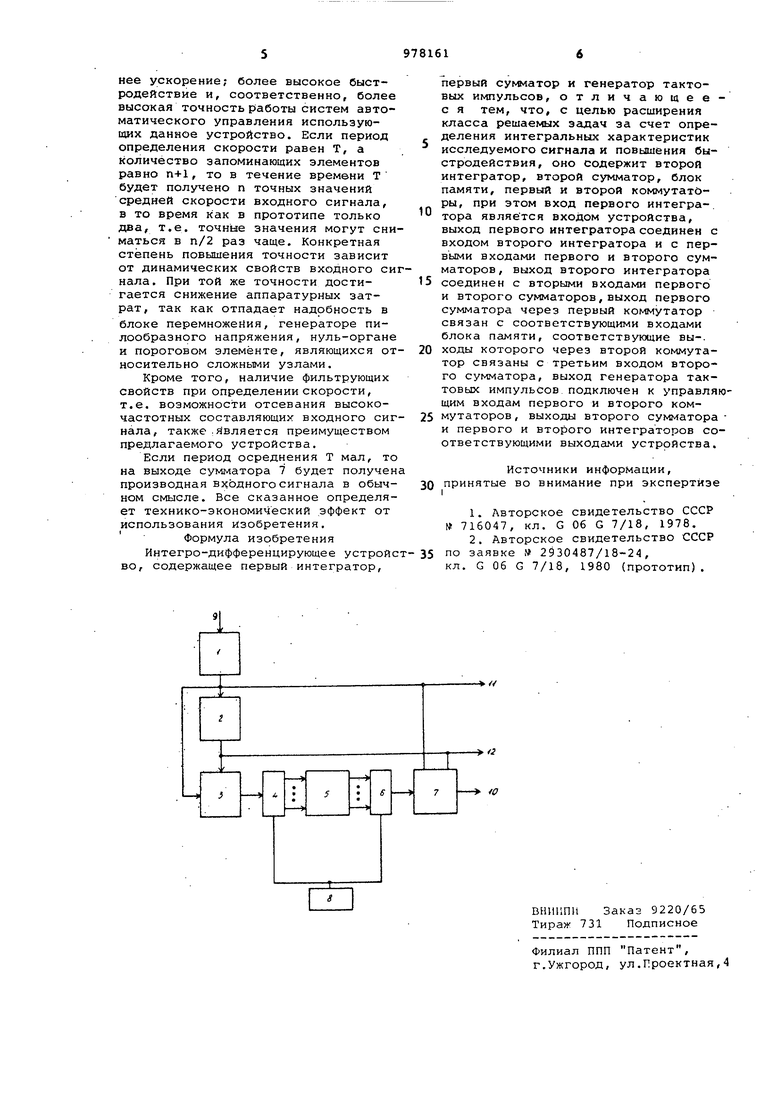

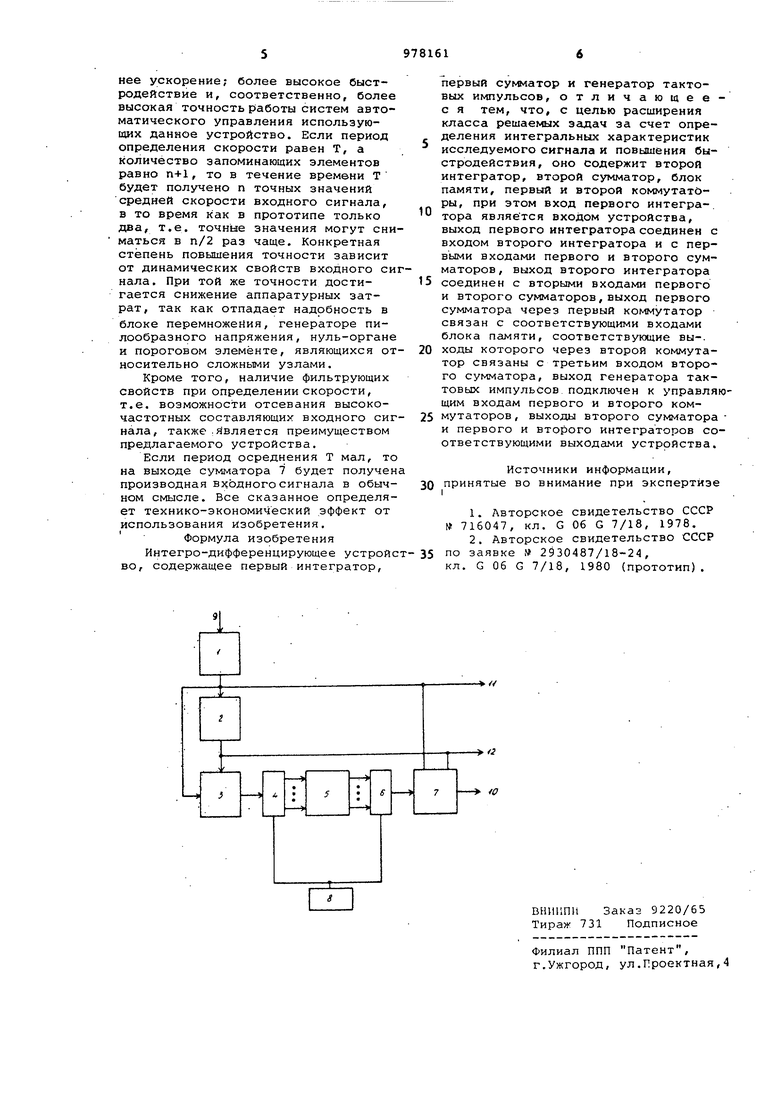

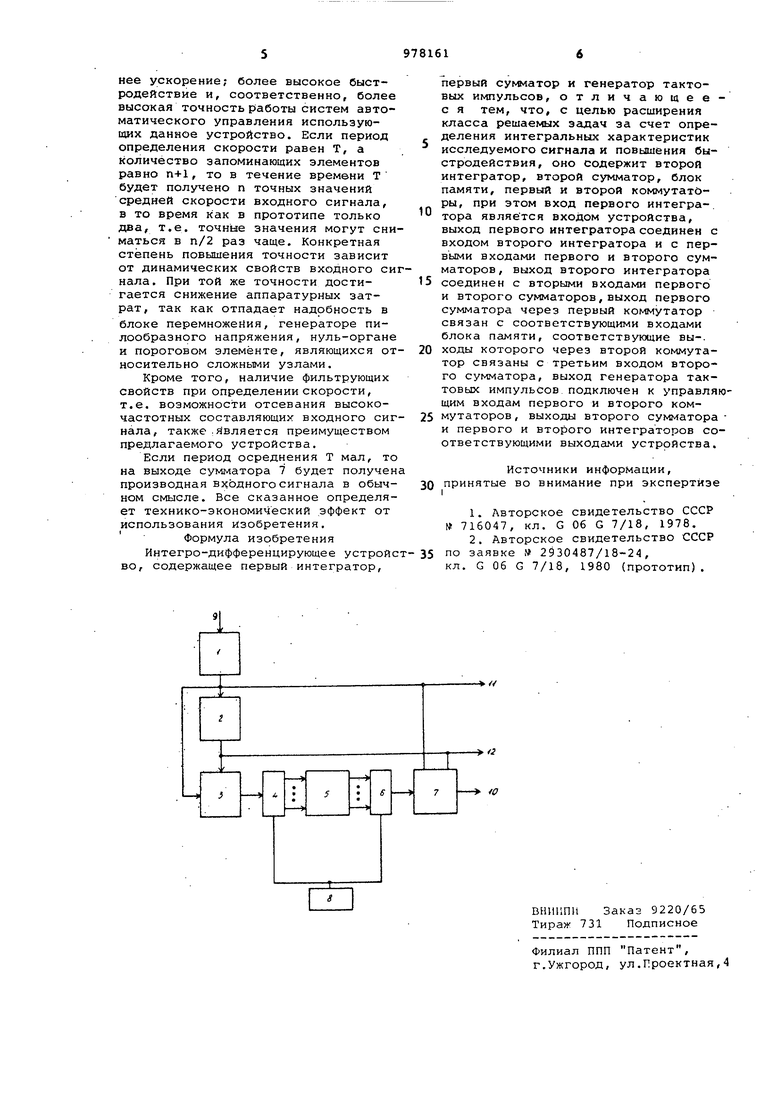

Поставленная цель достигается тем, что интегро-дифференцируютее устройство, содержащее первый ин15тегратор, первый сумматор и генератор тактовых импульсов, содержит второй интегратор, второй сумматор, блок памяти, первый и второй коммутаторы, при этом вход первого ин20тегратора является входом устройства, выход первого интегратора соединен с входом второго интегратора и с первьши входами первого и второго сумматоров, выход второго ин25тегратора соединен с вторыми входами первого и второго сумматоров, выход первого сумматора через перйый коммутатор связан с соответствующими входами блока памяти, соот30ветствующие выходы которого через второй коммутатор связаны с третьим входом второго сумматора, выход ге нератора тактовых импульсов, подключен к управляющим входам первого и второго коммутаторов, выходы второго сумматора и первого и второго интеграторов являются соответствую щими выходами устройства. Повышение быстродействия обуслов лено тем, что в устройстве может быть достигнута практически любая частота измерения средней скорости На чертеже представлена схема устройства. Схема содержит интегратору 1 и 2 сумматор 3, коммутатор 4, блок 5 памяти, коммутатор 6, сумматор 7, генератор 8 тактовых импульсов, вход 9 и выходы 10-12 устройства. В основу работы устройства положены следующим зависимости. Как и в прототипе, средняя скорость определяется на основе аппрок симации входной функции f(t) на некотором промежутке tg-d; tg+d линейной функцией 4(t) . Be личина а находится из условия мини мума среднеквадратической ошибки и представляет собой среднюю скорость изменения f(t) на заданном промежут ке а J5-f(V5) После соответствующих преобразований имеем с(. - {ФCto-6 } + aF(to-a)-d-F (Vd)2d()j ACV eCio- J ))с35; F(to + S)Hto + S)dS. Таким образом, для определения средней скорости изменения входног сигнала на интервалё о-сЗ; tg+d надо определить однократный и двой ной интегралы от входной функции в моменты времени tg-d и tg+d и выпо нить их алгебраическое суммирование в соответствии с формулой (1). Блок 5 памяти предназначен для хранения значений сумм однократног и двойного интегралов от входного сигнала в прошедшие моменты времен Устройство работает следующим о разом. Импульсы генератора 8, поступая на управляющие входы коммутаторов и б, обеспечивают поочередное подключение входов блока 5 памяти к выходу сумматора 3 и выходов блока 5 к входу сумматора 7, причем при подключении 1-го запоминающего элемента блока 5 к выходу сумматора 3 (1+1)-ый запоминающий элемент блока 5 подключается к входу сумматора 7. Если период определения средней скорости Т tQ-d,tQ+d разбит на п промежутков, то коммутаторы 4 и б содержат п-И ключевой элемент, блок 5 - (п+1) запоминающий элемент. В исходном состоянии интеграторы и запоминающие элементы блока 5 обнулены. При этом выход сумматора 3 подключен через коммутатор 4 к первому запоминающему элементу блока 5, выход второго запоминающего элемента через коммутатор 6 подключен к входу сумматора 7. Интеграторы 1 и 2 начинают интегрировать входной сигнал, а импульсы с генератора 8 последовательно подключают i-ые запоминающие элементы к выходу сумматора 3 и (i ) -ые - ко входу сумматора 7. Таким образом, J-ыи запоминающий элемент будет хранить значение Afiitd-l). После прихода п-го импульса с генератора 8 к выходу сумматора 3 будет подключен (п+1) элемент, а к третьему входу сумматора 7 - первый, т.е. будет подано значение А(о). На первый вход сумматора 7 поступит dF(T) с интегратора 1, а на второй (инвертирующий) вход - Ф(Т) с интегратора 2. На выходе сумматора 7 появится значение а, определенное на промежутке О,Т. Следующий импульс генератора 8 обеспечит подключение второго запоминающего элемента вместо первого и первого вместо (п+1)-го. В результате будет получено значение а на промежутке at, T+/3d и т.д. Значения однократного и двойного интегралов с точностью до масштабного множителя могут снижаться с выходов первого и второго интеграторов соответственно. Если значение дифференцируемой функции f О при , то достоверное значение а будет получено только по истечении одного периода осреднения Т, так как в исходном состоянии запоминающие элементы были обнулены. Таким образом, преимуществами предлагаемого устройства являются более широкие функциональные возможности, связанные с возможностью получения, кроме скорости изменения, однократного и двойного интеграла входной величины, так, например, если входная величина пропорциональна скорости, то на выходе первого интегратора будет получен пройденный путь, а на выходе сумматора 7 - сред

Авторы

Даты

1982-11-30—Публикация

1981-06-05—Подача