формационную емкость устройства при сохранении скорости записи. Управление записью осуществляется блоками 19-28, которые формируют сигналы управления преобразователем 9 кодов,

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в устройствах обработки цветовых сигналов в. качестве буферного запоминающего устройства в кодере видеосигналов.

Цель изобретения - повьшение информационной емкости устройства.

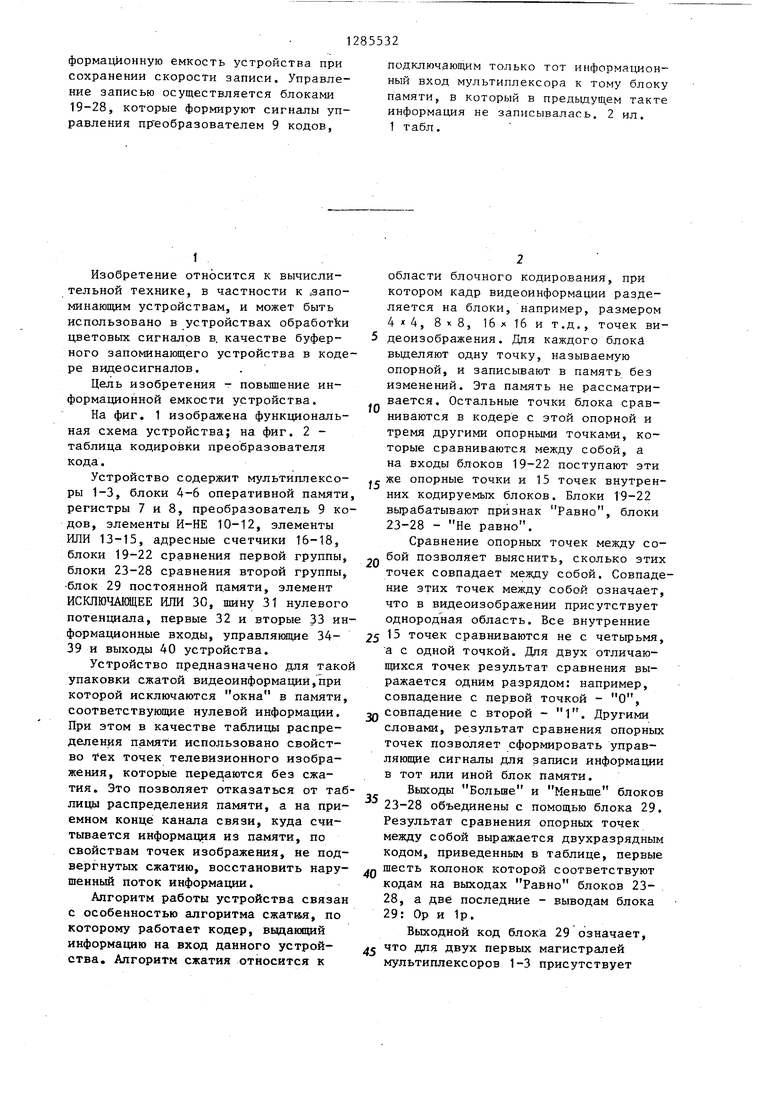

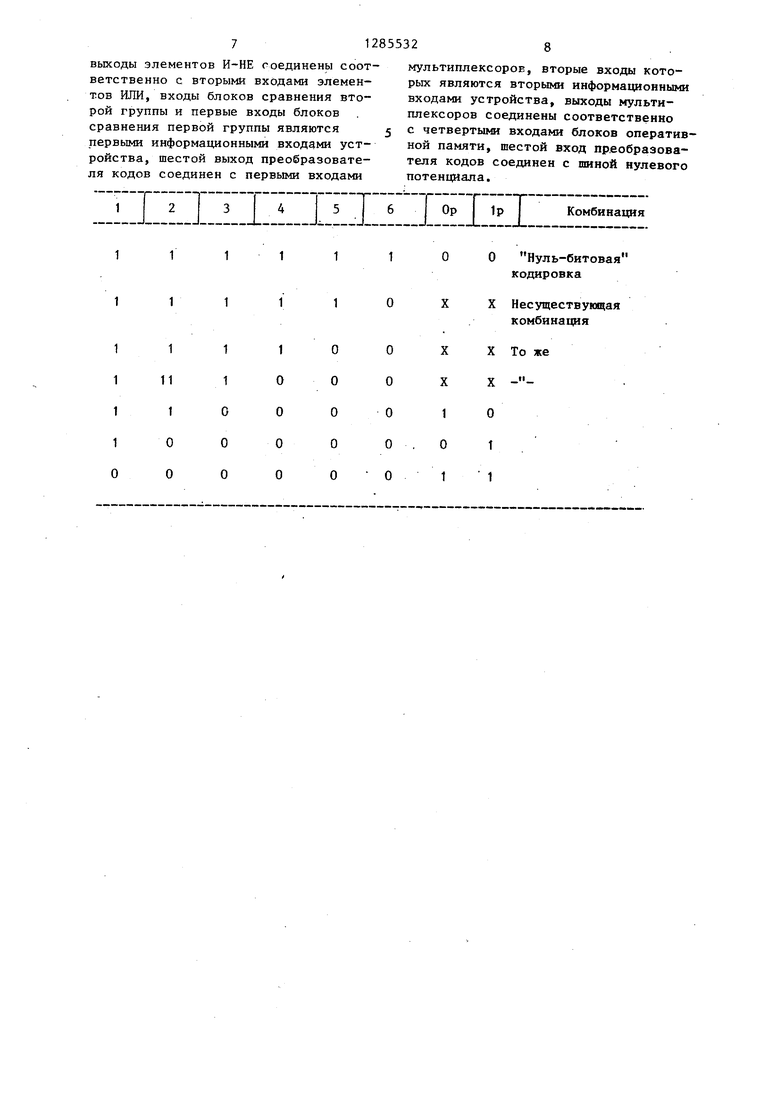

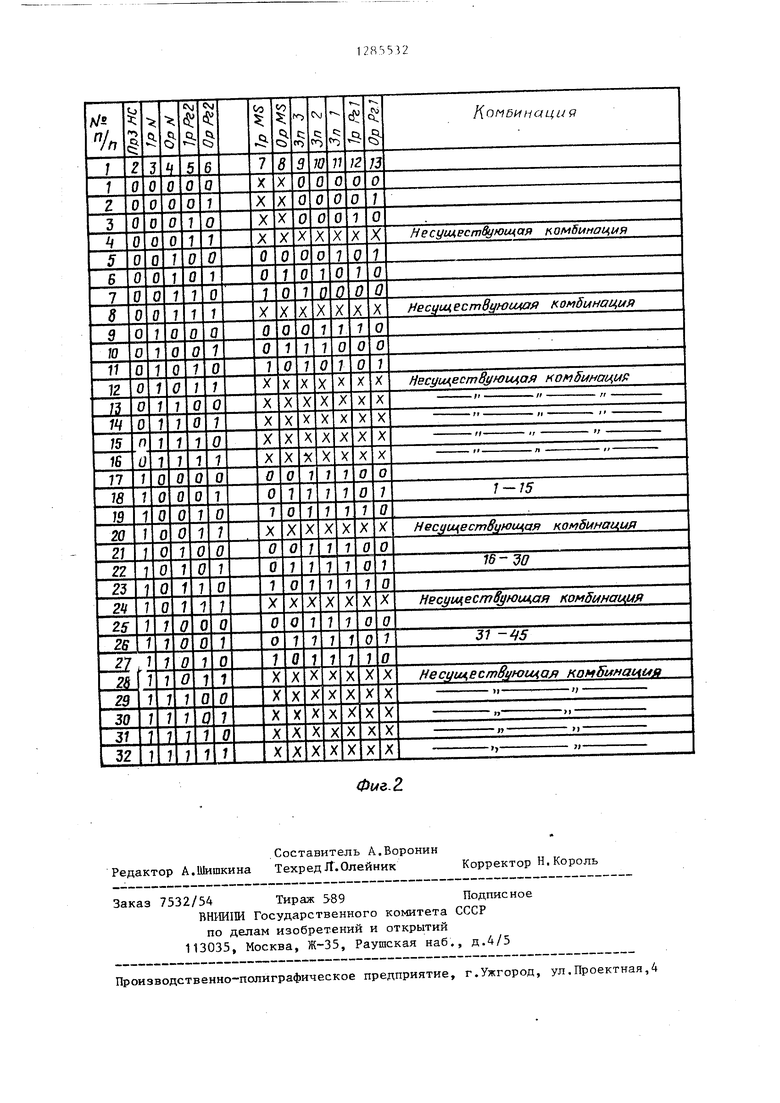

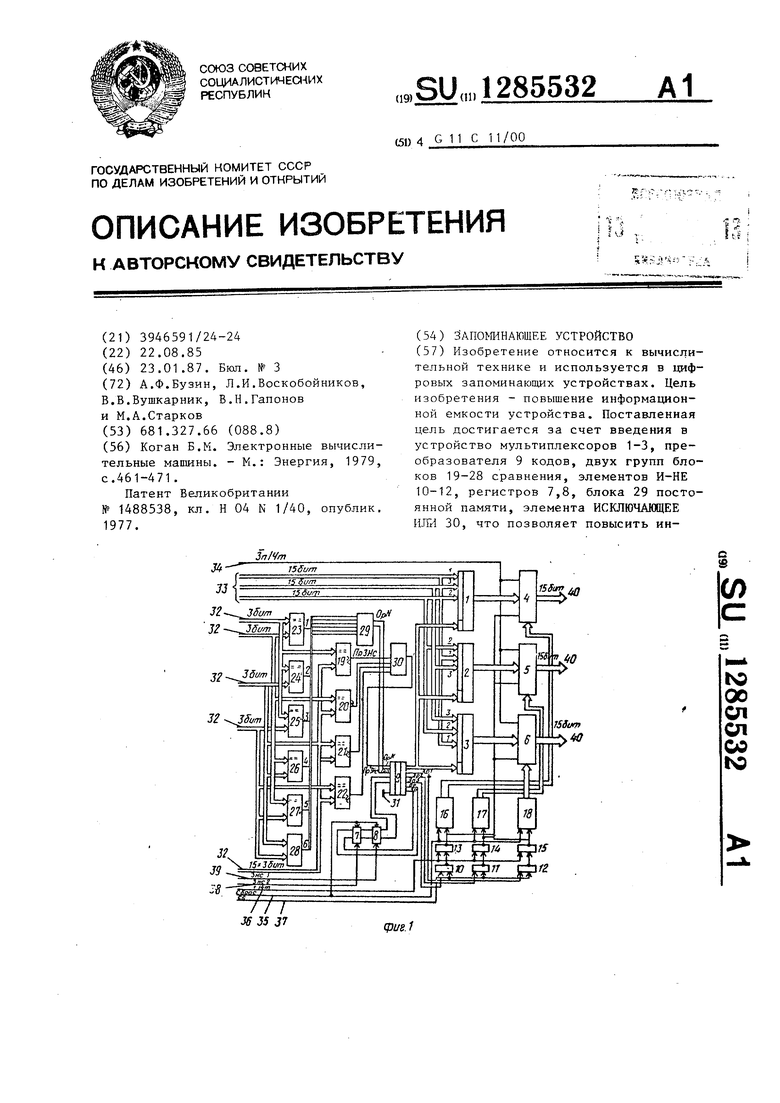

На фиг, 1 изображена функциональная схема устройства; на фиг. 2 - таблица кодировки преобразователя кода.

Устройство содержит мультиплексоры 1-3, блоки 4-6 оперативной памяти регистры 7 и 8, преобразователь 9 кодов, элементы И-НЕ 10-12, элементы ИЛИ 13-15, адресные счетчики 16-18, блоки 19-22 сравнения первой группы, блоки 23-28 сравнения второй группы, блок 29 постоянной памяти, элемент ИСКЛЮЧАКЩЕЕ ИЛИ 30, шину 31 нулевого потенциала, первые 32 и вторые 33 информационные входы, управляющие 34- 39 и выходы 40 устройства.

Устройство предназначено для тако упаковки сжатой видеоинформации,при которой исключаются окна в памяти, соответствующие нулевой информации. При этом в качестве таблицы распределения памяти использовано свойство tax точек телевизионного изображения, которые передаются без сжатия. Это позволяет отказаться от таблицы распределения памяти, а на приемном конце канала связи, куда считывается информация из памяти, по свойствам точек изображения, не подвергнутых сжатию, восстановить нарушенный поток информации.

Алгоритм работы устройства связан с особенностью алгоритма , по которому работает кодер, вьщакщий информацию на вход данного устройства. Алгоритм сжатия относится к

под1слюч, только тот информационный вход мультиплексора к тому блоку памяти, в который в предыдущем такте информация не записывалась. 2 ил. 1 табл.

5

0

5

0

5

0

5

области блочного кодирования, при котором кадр видеоинформации разделяется на блоки, например, размером 4t4, 8x8, 6 и 16 и т.д., точек видеоизображения, Для каждого блоки выделяют одну точку, называемую опорной, и записывают в память без изменений. Эта память не рассматривается. Остальные точки блока сравниваются в кодере с этой опорной и тремя другими опорными точками, которые сравниваются между собой, а на входы блоков 19-22 поступают эти же опорные точки и 15 точек внутренних кодируемых блоков. Блоки 19-22 вьфабатывают признак Равно, блоки 23-28 - Не равно.

Сравнение опорных точек между собой позволяет выяснить, сколько этих точек совпадает между собой. Совпадение этих точек между собой означает, что в видеоизображении присутствует однородная область. Все внутренние 15 точек сравниваются не с четырьмя, а с одной точкой. Для двух отличающихся точек результат сравнения выражается одним разрядом: например, совпадение с первой точкой - О, совпадение с второй - 1. Другими словами, результат сравнения опорных точек позволяет сформировать управ- ляюпре сигналы для записи информации в тот или иной блок памяти.

Выходы Больше и Меньше блоков 23-28 объединены с помощью блока 29, Результат сравнения опорных точек между собой выражается двухразрядным кодом, приведенным в таблице, первые шесть колонок которой соответствуют кодам на выходах Равно блоков 23- 28, а две последние - выводам блока 29: Ор и 1р,

Выходной код блока 29 означает, что для двух первых магистралей мультиплексоров 1-3 присутствует

либо нуль-битовая кодировка (от- сутствует информация), либо занята информацией одна магистраль, либо друга, либо обе вместе.

Одновременно со сравнением опор- ных точек между собой происходит сравнение внутренних точек,блока с опорными. При этом на входы блоков 19-22 поступает поток информации от вс ех внутренних точек блока по одно- му из информационных входов устройства. Например, при трехбитовом представлении каждой точки с помощью блока 19 сравнивается 15 трехбитовых комбинаций сигналов с одной опорной точкой из трех битов. Аналогичное сравнение происходит в блоках 20-22 соответственно с кодами трех других опорных точек. Сигналы неравенства внутренних точек с опорными собира- ются с помощью элементов 30. При этом формируют сигнал Признак несовпадения (ПрзНс). Этот сигнал свидетельствует о том, что в кодируемом блоке есть , отличающи- вся от опорных. Поэтому по всем трем входным магистралям 33 на вход мультиплексоров 1-3 из кодера поступает информация.

Таким образом, на первые три вхо- да преобразователя 9 поступают управляющие сигналы, определякшще сколько и какие информационные магистрали на входе мультиплексоров 1-3 заняты

Каждая посылка информации сопро- вождается синхросигналами занесения 3нс 1 и Знс2, поступающими на управляющие входы 38 и 39 устройства, т.е. на входы разрешения записи информации в регистры 7 и 8.

Поскольку размерность кода заключена в соотношении между опорными точками, то запоминая эту информацию в регистрах 7 и 8, можно учесть, какой блок памяти перед этим бьш загружен и какой после этого следует загружать.

Закодированная информация поступает на входы мультиплексоров 1-3. Входные шины соединены таким обра- зом, что порядок их подключения к каждому мультиплексору сдвигается по отношению к предьщущему. Например, если первая шина подключена к мультиплексору 3 на первый вход, то к мультиплексору 2 - на второй, а к мультиплексору 3 - на третий. Аналогично сдвигаются номера двух других шин. Преобразователь 9 вьфабатывает порядок подключения входных шин на выход каждого мультиплексора, т.е. определяет порядок записи информации в блок 4 памяти либо в блок 5 памяти, либо в блок 6 памяти, либо одновременно во все три.

При этом перед записью информации на адресных входах памяти формируют адрес записи с помощью счетчиков ISIS адреса. Для этого на управляющий вход 34 подают сигнал разрешения, а на входы выборки кристаллов памяти блоков 4-6 соответствующие сигналы выборки, которые формируются на выходе преобразователя 9. На входе этого преобразователя в порядке возрастания разрядов от младших к старшим устанавливают следующие сигналы: признак несовпадения ПрзНс; нулевой разряд номера опорных точек Ор; пер- вьй разряд номера опорных точек 1р; нулевой разряд регистра 8 Ор Рг1; первый разряд регистра 8 1р Рг1; нулевой потенциал.

На выходе преобразователя 9 в порядке возрастания от младших к старшим разрядам формируются сигналы: нулевой разряд управления мультиплексорами Ор MS; первьй разряд управления мультиплексорами; 1р MS; первый сигнал выборки Зп1; второй сигнал выборки Зп2; третий сигнал выборки ЗпЗ; нулевой разряд регистра 7 Ор Рг2; нулевой разряд регистра 7 1р Рг2,

Организация блоков памяти 4-6 тра диционна. Каждый блок памяти представляет собой накопитель информации, в который параллельно записывают или считывают 15 разрядов.

В таблице кодировки (фиг.2) приведена кодировка преобразователя 9, выполненного в виде программируемого постоянного запоминакяцего устройства (ППЗУ). Колонки 2-6 определяют входную информацию ППЗУ, а колонки 7-13 - выходную. Первые 16 строк от- |ражают кодировку ППЗУ для случая совпадения всех промежуточных точек блока с опорным, строки 17-32 - случай несовпадения хотя бы одной точки блока с опорными, когда информация поступает без сжатия.

Первые четыре строки таблицы кодировки отражают случай нуль-битовой кодировки, когда все опорные точки совпадают между собой, а внутренние совпадают с опорными и через мультиплексоры 1-3 информация не про

ходит., в пятой строке описан случай, когда на входы мультиплексоров 1-3 поступает информация по одной шине, При этом формируется сигнал записи Зп1, который через элемент 12 при наличии на входе управляющей шины 37 сигнала разрешения CS (сигнал синхронизации) равного по длительности сигналу записи, поступает на вход выборки блока 6 памяти и одновременно формирует адрес счетчика Сч А 18. На выход мультиплексоров 1-3 подключается первая шина, запись информации происходит только в блок 6 памяти. В два других блока памяти записи информации нет.

По сигналу Ор Рг2 формируется на выходе преобразователя 9 единица, которая заносится в. нулевой разряд регистра 7 под действием сигнала Знс2, подаваемого по управляющей шине 38. Сигнал занесения 3нс1, подаваемый по управляклцей шине 39, по- |ступает во время формирования первого обращения на запись данных в устройство. Поскольку на выходах регистра 8 в этот момент логический О, преобразователь 9 воспринимает этот сигнал как признак того, что информацию следует через мультиплексор 3 записать в блок 6 памяти.

Последующее обращение в памяти приведет к записи информации из регистра 7 в регистр 8, т.е. к формированию на выходе дешифратора (не показан) сигнала записи Зп2 и записи информации в блоке. 5 и т.д.

На выходе преобразователя 9 последовательно формируется двухразрядный код, подаваемый на управляемые входы мультиплексоров 1-3.Одновременно счетчики 16-18 каждый сигнал записи Зп1, Зп2, ЗпЗ воспринимают как сигнал приращения адреса на единицу и выставляют адрес на соответствующие блоки 4-6 памяти.

При поступлении на выход преобразователя 9 сигнала признака несовпадения промежуточной точки с любой из опорных точек (колонка 2, строки 17-32) на выходе дешифратора формируется сразу три сигнала Зп1, Зп2, ЗпЗ, которые разрешают запись данных одновременно в три блока 4-6 памяти и формируют одновременно с помощью счетчиков 16-18 три адреса.

Предлагаемое устройство предназначено для использования на выходе кодера и позвапяет исключить запись в

память нулевой информации, т.е. увеличивает информационную емкость, что, приводит к уменьшению времени занятия канала связи.

Формула изобретения

Запоминающее устройство, содержащее блоки оперативной памяти, первые входы которых являются первым управ- входом устройства, адресные счетчики, выходы которых соединены соответственно с вторыми входами блоков оперативной памяти, элементы ИЛИ, выходы которых соединены соответственно с первыми входами адресных счетчиков, вторые входы адресных счетчиков являются вторым управляющим входом устройства, первые входы элементов ИЛИ являются третьим управляющим входом устройства, выходы элементов ИЛИ соединены соответственно с третьими входами блоков оперативной памяти, выходы которых являются выходами устройства, шину нулевого потенциала, отличающееся тем, что, с целью повышения. информационной емкости устройства, в него введены мультиплексоры, пре-.

образователь кодов, блоки сравнения первой и второй групп, элементы И-НЕ, регистры, блок постоянной памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом преобразователя кодов, входы.элемента

ИСКЛЮЧАЩЕЕ ИЛИ соединены с вькодами блоков сравнения первой группы, выходы блоков сравнения второй группы соединены с входами блока постоянной

ответственно с вторым и третьим входами, преобразователя кодов, выходы первого регистра соединены соответственно с четвертьш и пятым входами

преобразователя кодов, первый, второй и третий выходы которого соединены соответственно с первыми входами элементов И-НЕ, вторые входы которых являются четвертым управляющим входом устройства, четвертый и пятый

выходы преобразователя кодов соединены с первым и вторым входами второго регистра, выходы которого соединены с первым и вторым входами первого

регистра, третьи входы регистров подключены к второму управлякщему входу устройства, четвертые входы регистров являются соответственно пятым и шестым управляюш {ми входами устройства.

712855328

выходы элементов И-НЕ соединены соот-мультиплексоров, вторые входы котоветственно с вторыми входами элемен-рых являются вторыми информационными

тов ИЛИ, входы блоков сравнения вто-входами устройства, выходы мультирой группы и первые входы блоков .плексоров соединены соответственно

сравнения первой группы являются 5 четвертыми входами блоков оперативпервыми информационными входами уст-ной памяти, шестой вход пр.еобразоваройства, шестой выход преобразовате-теля кодов соединен с шиной нулевого

ля кодов соединен с первыми входамипотенциала.

Комбинация

О Нуль-битовая кодировка

X Несуществующая комбинация

,Составитель А.Воронин Редактор А.Шишкина Техред 11.0лейник

Заказ 7532/54 Тираж 589Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-попиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг. г

Корректор Н,Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обработки изображений | 1989 |

|

SU1817108A1 |

| Имитатор внешнего устройства | 1983 |

|

SU1104496A1 |

| Устройство сжатия цифрового телевизионного сигнала | 1985 |

|

SU1334397A1 |

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для обращения двух процессоров к общему блоку памяти | 1989 |

|

SU1656547A1 |

| Устройство для вывода информации на фототелеграфный аппарат | 1983 |

|

SU1161935A1 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ИНФОРМАЦИОННОГО ПОИСКА | 2001 |

|

RU2195015C1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

Изобретение относится к вычислительной технике и используется в цифровых запоминающих устройствах. Цель изобретения - повышение информационной емкости устройства. Поставленная цель достигается за счет введения в устройство мультиплексоров 1-3, преобразователя 9 кодов, двух групп блоков 19-28 сравнения, элементов И-НЕ 10-12, регистров 7,8, блока 29 постоянной памяти, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30, что позволяет повысить инЗп1Чт Л -г 4/7 (/) N9 СХ) СП ел со го (pi/. /

| Коган Б.М | |||

| Электронные вычислительные машины | |||

| - М.: Энергия, 1979, с.461-471 | |||

| Патент Великобритании № 1488538, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1987-01-23—Публикация

1985-08-22—Подача