Изобретение относится к области вычислительной техники и может быть использовано при построении многопроцессорных систем с асинхронным обращением нескольких процессоров к общей памяти.

Известны устройства для сопряжения процессоров с общим блоком памяти, содержащее четыре триггера, генератор импульсов и элементы И. Эти устройства обеспечивают обслуживание асинхронно поступающих от первого и второго процессоров запросов на обращение к общему блоку памяти по очередности поступления без назначения приоритета одному из процессоров. При совпадении во времени запросов от двух процессоров устройства обеспечивают их последовательно обращение к общей памяти на время одного цикла записи или чтения.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для сопряжения двух процессоров с общей памятью, которое содержит два дешифратора адреса.

два дешифратора сегмента, два регистра игомера массива, два коммутатора, четыре приемопередатчика, шифратор, мультиплексор, генератор импульсов, восемь триггеров, шесть элементов l. элемента И-НЁ, пять элементов НЕ,,элемент ИЛИ. При совпадении во времени запросов от двух процессоров устройство обеспечивает их последовательное обращение к общей м1ногоблочной памяти, т.е. позволяет расширить область адресного пространства памяти каждого из процессоров.

Недостаток устройства в том, что оно не обеспечивает синхронизации доступа процессоров к общей памяти при обмене массивами информации. Назначением такой синхронизации является предотвращение считывания одним из процессоров массива из общей памяти в тот момент, когда другой процессор обновляет в данном массиве информацию. Отсутствие указанной синхронизации приводит к считыванию процессором массива, в котором часть информации старая, а часть информации уже

(Л

С

о

00

О

обновлена. Для ряда управляющих систем, работающих в реальном масштабе времени, это недопустимо.

Известен метод связи процессоров через общую память, организованную по принципу почтового ящика, частично решающий эту задачу. В общей памяти отводятся фиксированные области: почтовый ящик состояний и почтовый ящик сообщений. Один йз процессоров формирует массив инфор мацйИ и сопровождающую ее квитанцию, помещай их соответственно в почтовый ящиТГ сообщений и почтовый ящик состояний. Другой процессор по мере готовности обращается к почтовому ящику сообщений и при обнаружении квитанции о наличии данных в соответствующем почтовом ящике сообщений устанавливает в исходное состояние квитанцию и считывает массив информации.

При этом для устройства-прототипа возможны случаи, когда, например, первый процессор перед чтением массива выполняет команду анализа квитанции, которая в данный момент времени указывает на разрешение доступа. Второй процессор перед обновлением информации в массиве также установит запрос на анализ состояния квитанции для данного массива. Так как общая память в данный момент занята первым процессором, запрос на обращение второго процессора к общей памяти будет задержан на время выполнения чтения квитанции первым процессором. После окончания анализа квитанции первым процессором его следующая команда, которой он должен изменить состояние квитанции для блокировки доступа второго процессора к массиву, будет задержана из-за занятости общей памяти вторым процессором. По окончании анализа квитанции вторым процессором его следующая команда, содержащая запись в квитанцию кода блокировки для первого процессора, будет задержана, т.к. первый процессор в данный момент обращается к общей памяти для изменения кода квитанции. Таким образом, существует отличная от нуля вероятность, что оба процессора, проанализировав квитанцию, одновременно получат доступ к одному и тому же массиву.

Цель изобретения - устранение данного недостатка, т.е. расширение области использования за счет обеспечения синхронизации доступа процессоров к общему блоку памяти при обмене массивами информации.

Поставленная цель достигается тем, что в устройство для обращения двух процессоров к общему блоку памяти, содержащее

восемь триггеров, два элемента И-НЕ, два дешифратора адреса, два элемента И, генератор импульсов, причем входы первого и второго дешифраторов адреса подключены

5 к первой и второй шинам адреса устройства соответственно, а выходы первого и второго дешифраторов адреса соединены соответственно с входами данных первого и второго триггеров, выходы которых соединены

0 соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первой и второй шинами записи устройства, инверсные выхоДы третьего и четвертого триггеров

5 подключены соответственно к первой и второй шинам разрешения обмена устройства, синхровходы первого и второго триггеров соединены соответственно с первой и второй шинами синхронизации обмена

0 устройства, выходы первого и второго элементов И-НЕ соединены соответственно с установочными входами пятого и шестого триггеров, введены девятый и десятый триггеры, с третьего по шестой элементы

5 И-НЕ, причем прямые выходы пятого и шестого триггеров соединены соответственно со входами данных третьего и четвертого триггеров и с первыми входами третьего и четвертого элементов И-НЕ, вторые входы

0 которых соединены соответственно с первой и второй шинами запроса устройства и первыми входами первого, второго и пятого, шестого элементов И-НЕ, вторые входы которых соединены соответственно с первым

5 и вторым выходами генератора импульсов и прямыми выходами седьмого и восьмого триггеров, установочные входы которых соединены соответственно с первой и второй шинами установки исходного состояния ус0 тройства, а инверсные выходы которых соединены соответственно с третьими входами второго и первого элементов И-НЕ, четвертые входы которых соединены соответственно с инверсными выходами пятого и

5 шестого триггеров и с первой и второй шинами запрета доступа устройства, синхровходы пятого и шестого триггеров, объединенные со входами сброса соответственно третьего и четвертого триггеров, со0 единены с первой и второй шинами синхронизации обмена устройства соответственно, синхровходы третьего и четвертого триггеров соединены i соответственно с первой и второй тактовыми шинами уст5 ройства, входы данных пятого и шестого триггеров соединены с шиной нулевого потенциала устройства, выходы третьего и четвертого элементов И-НЕ соединены соответственно с синхровходами седьмого и восьмого триггеров, входы данных которых

соединены соответственно с прямыми выходами девятого и десятого триггеров, входы данных, синхровходы и входы сброса которых соединены соответственно с разрядом первой и второй шин адреса устройства, выходами первого и второго элементов И, выходами пятого и шестого элементов И-НЕ.

Совокупность в устройстве известных элементов с вновь введенными двумя триггерами, четырьмя элементами И-НЕ с указанными связями при организации работы двух процессоров на общий блок памяти со стандёртной совмещенной магистралью адрес/данные (типа МПИ) позволяет каждому из процессоров захватить общий блок памяти не на одно, а на два последовательных обращения, что обеспечивает надежную работу при обмене массивами информации с асинхронным поступлением запросов на обращение к памяти от обеих процессоров, т.е. расширить область использования устройства.

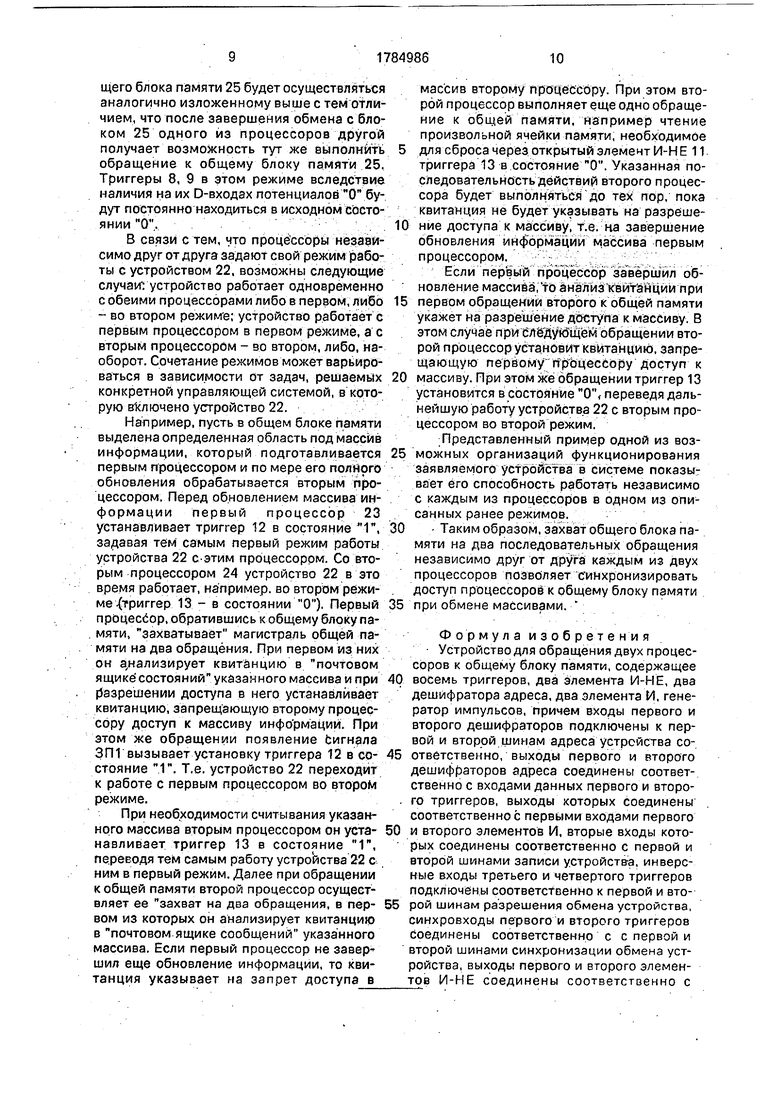

На фиг. 1 приведена схема устройства; на фиг. 2 - схема использования устройства совместно с двумя процессорами.

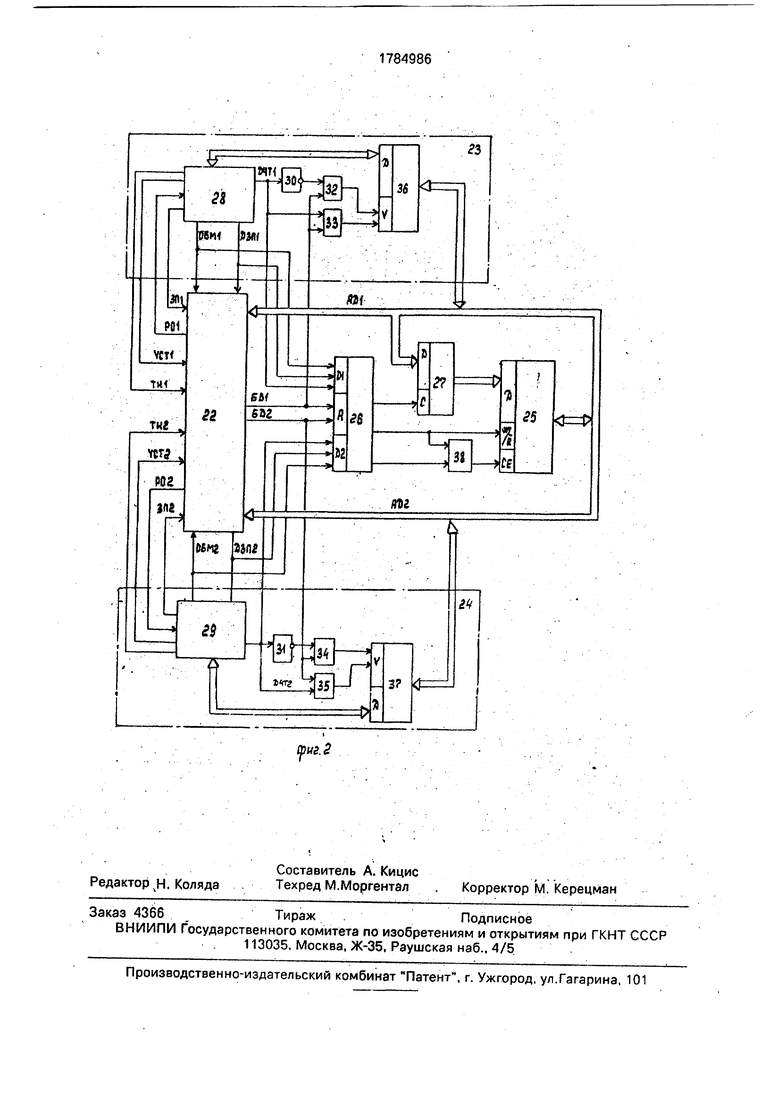

Устройство для обращения двух процессоров к общему блоку памяти (фиг. 1) содержит триггеры 1, 2, элементы И-НЕ 3, 4, генератор импульсов 5, триггеры 6-9, элементы И-НЕ 10,11, триггеры 12, ТЗ, элементы И 14, 15, триггеры 16, 17, дешифраторы 18, 19, элементы И-НЕ 20, 21.

На фиг. 2 приведены устройство 22 для обращения двух процессоров 23 и 24 к общему блоку памяти 25, мультиплексор 26, регистр адреса 27, элемент ИЛИ 38. Первый и второй процессоры 23, 24 содержат соответственно процессорный элемент 28, 29, элементы НЕ 30, 31, элементы ИЛИ 32, 33 и ИЛИ 34, 35, шинные формирователи 36. 37.

В качестве процессорных элементов 28, 29 можно использовать однокристальные микропроцессоры Н1806 ВМ2 (6КО. 347.456 ТУ) с системной магистралью МПИ.

Блок памяти 25 может быть выполнен на микросхемах 537 РУ9А, шинные формирователи 36, 37 - на микросхемах 530 АЛ2, мультиплексор 26 - на основе микросхем 533КП11.

Устройство работает следующим образом. При включении питания процессорные элементы 28, 29 формируют сигналы УСТ 1, УСТ 2, которые, поступая на соответствующие шины установки исходного состояния устройства 22, устанавливают триггеры 8, 9 в состояние О, так как на шинах запроса ЗП1, ЗП2 устройства установлен нулевой потенциал, выходы И-НЕ 3, 4 находятся в состоянии 1.

Первый же сигнал синхронизации обмена ОБМ1, ОБМ2, поступивший соответственно по первой или второй шинам синхронизации устройства 22, установит в 5 состояние О триггеры 1, 2 и 6, 7 соответственно. Установкой потенциала 1 на шинах запрета доступа устройства 22 (сигналы БД1, БД2) доступ процессоров 23,24 к блоку памяти 25 блокирован.

10 Устройство 22 обеспечивает каждому процессору 23, 24 два режима работы с общим блоком памяти 25(независимо от режима работы другого процессора) - первый или второй режим. При необходимости об- 15 мена массивами один из процессоров задает первый режим работы с устройством 22, благодаря чему организуется возможность Захвата этим процессором общей памяти 25 на два последовательных обращения. Во 20 втором режиме устройство 22 обеспечивает процессорам 23, 24 захват магистрали общей памяти 25 только на одно обращение. При этом, как в первом, так и во втором режимах осуществляется временное раздё- 5 ление запросов на обращение к блоку общей памяти 25.

Вид режима работы устройства определяется соответственно состоянием триггеров 12, 13.

0 Для работы в первом режиме процессор (например, 23), выставляет на первой шине адреса АД1 устройства 22 адрес триггера 12, который представляет собой для процессора 23 однобитовый программнодоступ- 5 ный (по записи) регистр , подключенный к магистрали адрес/данные.

Дешифратор адреса 18 дешифрирует адрес, установленный на его входах, и выдает на выходе сигнал уровня 1й, После этого 0 на первую шину синхронизации обмена устройства 22 процессор выдает сигнал ОБМ1, который устанавливает триггер 16 в состояние 1. Затем процессор 23 снимает с магистрали АД1 адрес и устанавливает на 5 подключенном к D-входу триггера 12 разряде магистрали АД1 потенциал 1. Вслед за этим процессор выставляет сигнал ДЗП1, который по первой шине записи данных через элемент И14 устанавливает триггер 12 в 0 состояние 1,

При необходимости синхронизации обмена массивами второй процессор 24 аналогично первому формирует соответствующую последовательность сигналов и ус- 5 танавливает триггер 13 в состояние 1.

Выставленный первым процессором 23 сигнал запроса (ЗП1) по первой шине запроса устройства 22 позволяет импульсу частоты F1 двухфазного генератора импульсов 5 через элемент И-НЕ 3 установить триггер 1

в состояние Т. При установке потенциала О на первой шине запрета доступа (БД1) блокировка доступа к памяти снимается м устройство 22 обеспечивает монопольное использование блока памяти 25 первым процессором 23. Мультиплексор 26 при этом разрешает прохождение на регистр адреса 27 и блок памяти 25 сигналов управления с выходов процессора 23.

Элемент И-НЕ 4 будет при этом закрыт потенциалом с инверсного выхода триггера 1. Передний фронт тактового импульса ТЙ1 процессорного элемента 28 по первой тактовой шине устройства 22 устанавливает триггер 2 в состояние 1, благодаря чему на первой шине разрешения обмена устройства 22 появляется сигнал Р01, уровень О которого позволяет процессору 23 продолжить процедуру обмена. Процессорный элемент 28 снимает сигнал запроса ЗП1 и одновременно выставляет на магистраль адрес/данные АД1 адрес, который по заднему фронту (переход от потенциала 1 к потенциалу О) сигнала синхронизации обмена ОБМ1 фиксируется в адресном регистре 27. Этим же сигналом триггер 2 возвращается в исходное состояние О. Ранее при снятии сигнала запроса ЗП1 первого процессора 23 (переход от потенциала 1 к потенциалу О) триггер 8 через элемент И-НЕ 20 установится в состояние Г1, при этом с его инверсного выхода блокирующий уровень О поступит на четвертый вход элемента И-НЕ 4.

Если процессор23 осуществляет процедуру чтения данных из блока памяти 25, он выставляет сигнал ДЧТ1, который через элемент НЕ 30 и элементы ИЛИ 32,33 открывает шинный формирователь 36 для передачи информации от блока памяти 25 на шины адрес/данные АД процессорного элемента 28. Этот же сигнал, поступая через мультиплексор 26 и элемент ИЛИ 38 на вход разрешения блока памяти 25, переводит его выходы из высокоимпедансного состояния в актиЁное.

Если процессор 23 осуществляет процедуру записи данных в блок памяти 25, процессорный элемент 28 выставляет на шинах АД информацию и затем формирует сигнал ДЗП1, который через открытый мультиплексор 26 устанавливает потенциал О (режим записи) на управляющем входе блока памяти 25. Этот же сигнал через элемент ИЛИ 38 поступает на вход разрешения блока памяти 25.

По окончании процедуры обмена первого процессора 23 с блоком памяти 25 (конец первого обращения) уровень сигнала ОБМ1 изменяется с О на Т, и триггер 1 переходит в исходное состояние О. При этом элемент И-НЕ 4 продолжает оставаться закрытым потенциалом О с инверсного выхода триггера 8. Поэтому при поступлении от второго процессора 24 сигнал запроса ЗП2 до окончания второго обращения первого процессора 23 к общему блоку памяти 25, второй процессор 24 доступ к блоку 25 не получит. Возможность такого доступа

0 сохранится только для первого процессора 23.

При его втором обращении к блоку памяти 25 процессорный элемент 28 выставит сигнал ЗП1 уровня 1й, который через от5 крытый элемент И-НЕ 10 установит триггер

12в исходное состояние О, переводя устройство 22 во второй режим работы.

Импульс частоты 1 двухфазного генератора импульсов 5 через элемент И-НЕ 3 ус0 танавливает триггер 1 в состояние 1, разрешая доступ в блок памяти 25 первому процессору 23. По переднему фронту тактового импульса ТИ1 триггер 2 установится в состояние 1. Получив сигнал разрешения

5 обмена Р01. процессорный элемент 28 снимает сигнал запроса ЗП1 и выставляет на магистрали адрес/данные адрес, а затем и сигнал синхронизации обмена ОБМ1, который вернет триггер 2 в исходное состояние

0 О. Т.к. триггеры 1 и 12 находятся соответственно в состоянии 1 и О, то при снятии сигнала ЗП1 (переход от потенциала Г к потенциалу О) триггер 8 установится в исходное состояние О. При завершении про5 цедуры обращения к блоку 25 процессор 23 снимет сигнал ОБМ1 (переход от потенциала О к потенциалу 1) и установит триггер 1 в исходное состояние О. Тем самым, если к этому моменту времени был установ0 лен сигнал запроса ЗП2 второго процессора 24 он получит доступ к общему блоку памяти 25. Первый же импульс частоты F2, сдвинутой на половину периода относительно частоты F1, установит триггер б в состояние

5 1, закрывая тем самым элемент И-НЕ 3, а также доступ процессора 23 к блоку 25. При получении процессорным элементом 29 сигнала разрешения обмена Р02, он начинает аналогично процессорному элементу 28 вы0 полнять процедуру обмена с блоком памяти 25, При этом в зависимости от состояния триггера 13 обмен будет выполняться либо в первом режиме (два последовательных обращения), либо во втором режиме (одно об5 ращение).

При необходимости начать работу сразу со второго режима процессоры 23,24 должны установить соответственно триггеры 12,

13аналогично описанному ранее в состояние О. После этого процедура захвата общего блока памяти 25 будет осуществляться аналогично изложенному выше с тем отличием, что после завершения обмена с блоком 25 одного из процессоров другой получает возможность тут же выполнить обращение к общему блоку памйти 25. Триггеры 8, 9 в этом режиме вследствие наличия на их D-входах потенциалов О будут постоянно находиться в исходном состоянии О.

В связи с тем, что процессоры независимо друг от друга задают свой режим работы с устройством 22. возможны следующие случаи устройство работает одновременно с обеими процессорами либо в первом, либо - во втором режиме; устройство работает с первым процессором в первом режиме, а с вторым процессором - зо втором, либо, наоборот. Сочетание режимов может варьироваться в зависимости от задач, решаемых конкретной управляющей системой, в которую включено устройство 22.

Например, пусть в общем блоке памяти выделена определенная область под массив информации, который подготавливается первым процессором и по мере его полного обновления обрабатывается вторым процессором. Перед обновлением массива информации первый процессор 23 устанавливает триггер 12 в состояние 1, задавая тем самым первый режим работы устройства 22 с-этим процессором. Со вторым процессором 24 устройство 22 в это время работает, например, во втором режиме .{триггер 13 - в состоянии О). Первый процессор, обратившись к общему блоку памяти, захватывает магистраль общей памяти на два обращения. При первом из них он анализирует квитанцию в почтовом ящике состояний указанного массива и при разрешении доступа в него устанавливает квитанцию, запрещающую второму процессору доступ к массиву информации. При этом же обращении появление сигнала ЗП1 вызывает установку триггера 12 в состояние 1. Т.е. устройство 22 переходит к работе с первым процессором во втором режиме.

При необходимости считывания указанного массива вторым процессором он устанавливает триггер 13 в состояние 1, переводя тем самым работу устройства 22 с ним в первый режим. Далее при обращении к общей памяти второй процессор осуществляет ее захват на два обращения, в первом из которых он анализирует квитанцию в почтовом ящике сообщений указанного массива. Если первый процессор не завер шил еще обновление информации, то квитанция указывает на запрет доступа в

массив второму процессору. При этом второй процессор выполняет еще одно обращение к общей памяти, например чтение произвольной ячейки памяти, необходимое

5 для сброса через открытый элемент И-Н Е 11 триггера 13 в состояние О. Указанная последовательность действий второго процессора будет выполняться до тех пор, пока квитанция не будет указывать на разреше10 ние доступа к массиву, т.е. на завершение обновления информации массива первым процессором.

Если первый процессор за вёршйл обновление массива, то анализ квитанции при

15 первом обращении второго к общей памяти укажет на разрешение доступа к массиву. В этом случае при следующем обращении второй процессор установит квитанцию, запрещающую первому процессору доступ к

0 массиву. При этом же обращении триггер 13 установится в состояние переведя дальнейшую работу устройства 22 с вторым процессором во второй режим.

Представленный пример одной из воз5 можных организаций функционирования заявляемого устройства в системе показывает его способность работать независимо с каждым из процессоров в одном из описанных ранее режимов.

0 Таким образом, захват общего блока памяти на два последовательных обращения независимо друг от друга каждым из двух процессоров позволяет синхронизировать доступ процессоров к общему блоку памяти

5 при обмене массивами.

Формула изобретения Устройство для обращения двух процессоров к общему блоку памяти, содержащее

0 восемь триггеров, два элемента И-НЕ, два дешифратора адреса, два элемента И, генератор импульсов, причем входы первого и второго дешифраторов подключены к первой и второй шинам адреса устройства со5 ответственно, выходы первого и второго дешифраторов адреса соединены соответственно с входами данных первого и второго триггеров, выходы которых соединены соответственно с первыми входами первого

0 и второго элементов И, вторые входы которых соединены соответственно с первой и второй шинами записи устройства, инверсные входы третьего и четвертого триггеров подключены соответственно к первой и вто5 рой шинам разрешения обмена устройства, синхровходы первого и второго триггеров соединены соответственно с с первой и второй шинами синхронизации обмена устройства, выходы первого и второго элементов И-НЕ соединены соответственно с

установочными входами пятого и шестого триггеров, отличающееся тем, что, с целью расширения области использования, в устройство введены девятый и десятый триггеры, с третьего по шестой элементы И-НЕ, причем прямые выходы пятого и шестого триггеров соединены соответственно с входом данных третьего и четвертого триггеров и с первыми входом третьего и четвертого элементов И-НЕ, вторые входы которых соединены соответственно с первой и второй шинами запроса устройства и первыми входами первого, второго и пятого, шестого элементов И-НЕ, вторые входы которых соединены соответственно с первым и вторым выходами генератора импульсов и прямыми выходами седьмого и восьмого триггеров, инверсные выходы которых соединены соответственно с третьими входами второго и первого элементов И-НЕ, четвертые входы которых соединены соответственно с инверсными выходами пятого и шестого триггеров и с первой и второй шинами запрета доступа устройства, синхровходы пятого и шестого триггеров, объединенные с входами сброса соответственно третьего и четвертого триггеров соединены с первой и второй шинами синхронизации

обмена устройства соответственно, синх- ровходы третьего и четвертого триггеров соединены соответственно с первым и вторым тактовыми шинами устройства, входы сброса седьмого и восьмого триггеров соединены с первой и второй шинами установки устройства, входы данных пятого и шестого триггеров соединены с шиной нулевого потенциала устройства, выходы третьего и чет- вертого элементов И-НЕ соединены

соответственно с синхровходами седьмого и восьмого триггеров, входы данных которых соединены соответственно с прямыми выходами девятого и десятого триггеров, входы данных синхровходы и входы сброса которых соединены соответственно с разрядом первой и второй шин адреса уст-, ройства, выходами первого и второго элементов И, выходами пятого и шестого элементов И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения двух процессоров к общему блоку памяти | 1989 |

|

SU1656547A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для синхронизации работы двух процессоров с общим блоком памяти | 1987 |

|

SU1444794A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для сопряжения двух процессоров | 1991 |

|

SU1784983A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Многопроцессорная система | 1988 |

|

SU1522228A1 |

| Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы | 1988 |

|

SU1571606A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении многопроцессорных систем с асинхронным обращением нескольких процессоров к общей памяти. Целью изобретения является расширение области использования. Устройство содержите первого по десятый триггеры, с перво- го по шестой элементы И-НЕ, двухфазный генератор импульсов, первый и второй элементы И, первый и второй дешифраторы адреса. 2 ил.

| Устройство для сопряжения поцессоров с общим блоком памяти | 1984 |

|

SU1241246A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации работы двух процессоров с общим блоком памяти | 1987 |

|

SU1444794A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-06-18—Подача