Изобретение относится к вычислительной технике и может быть использовано при построении двухпроцессорных систем с асинхронным обращением процессоров к

общему блоку памяти. /

Цель изобретения - сокращение аппаратурных затрат.

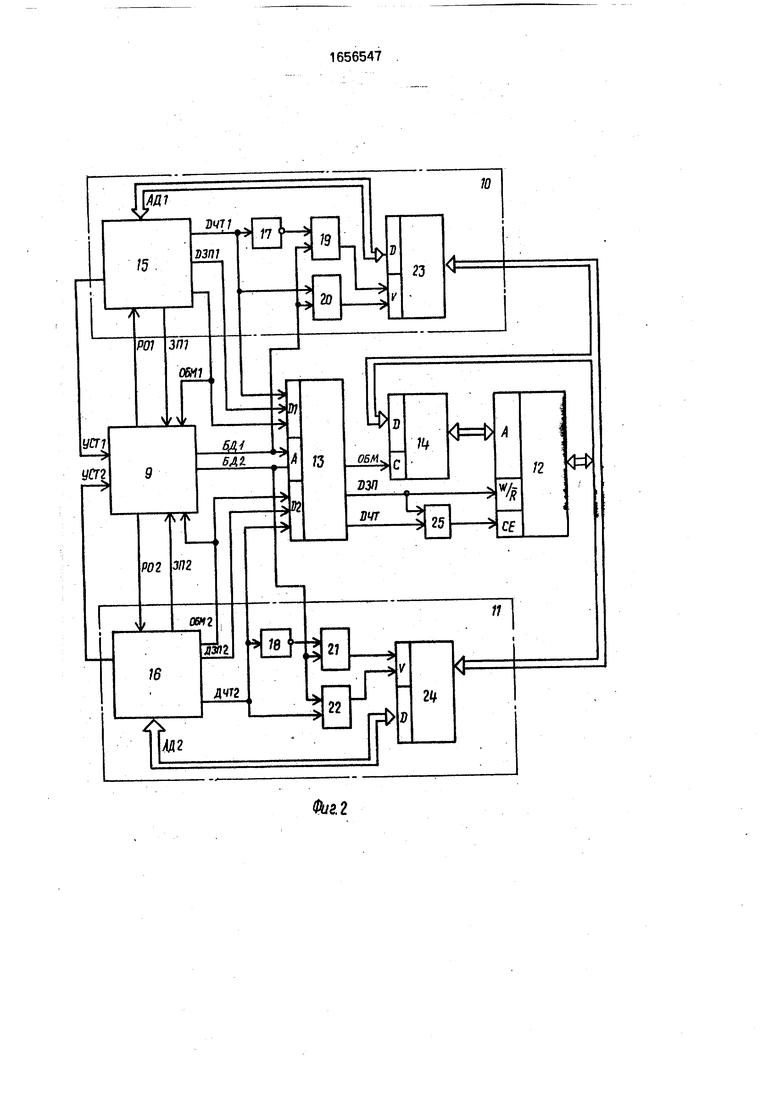

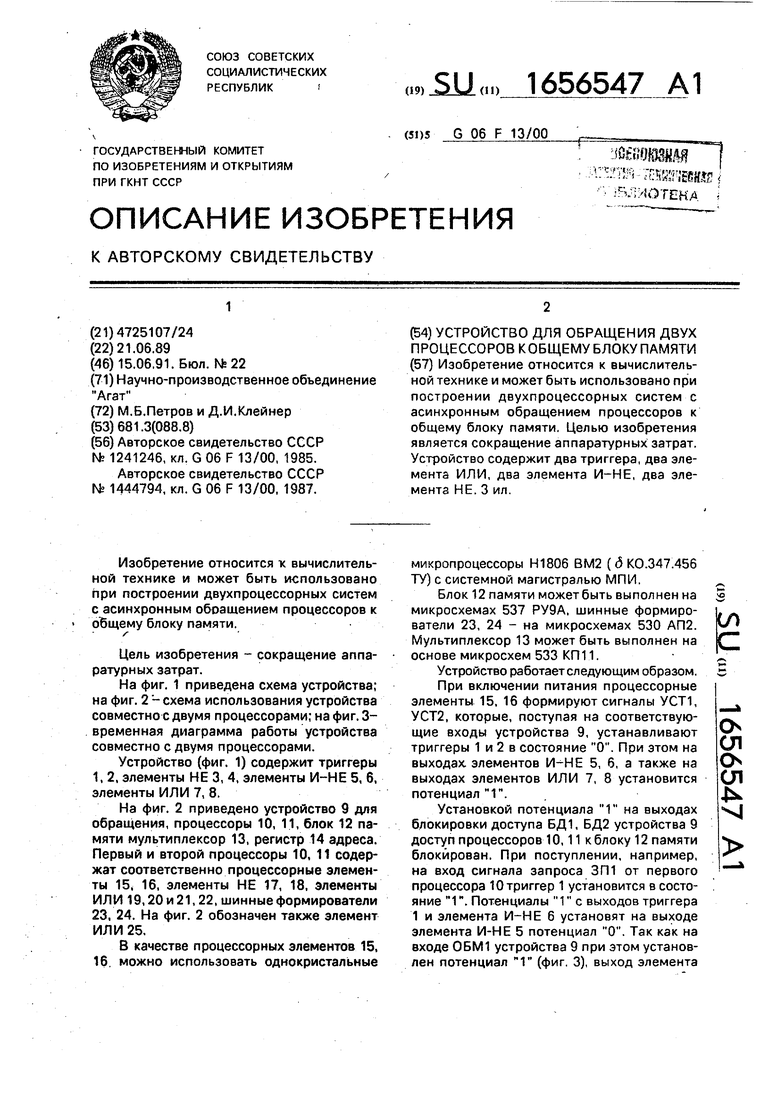

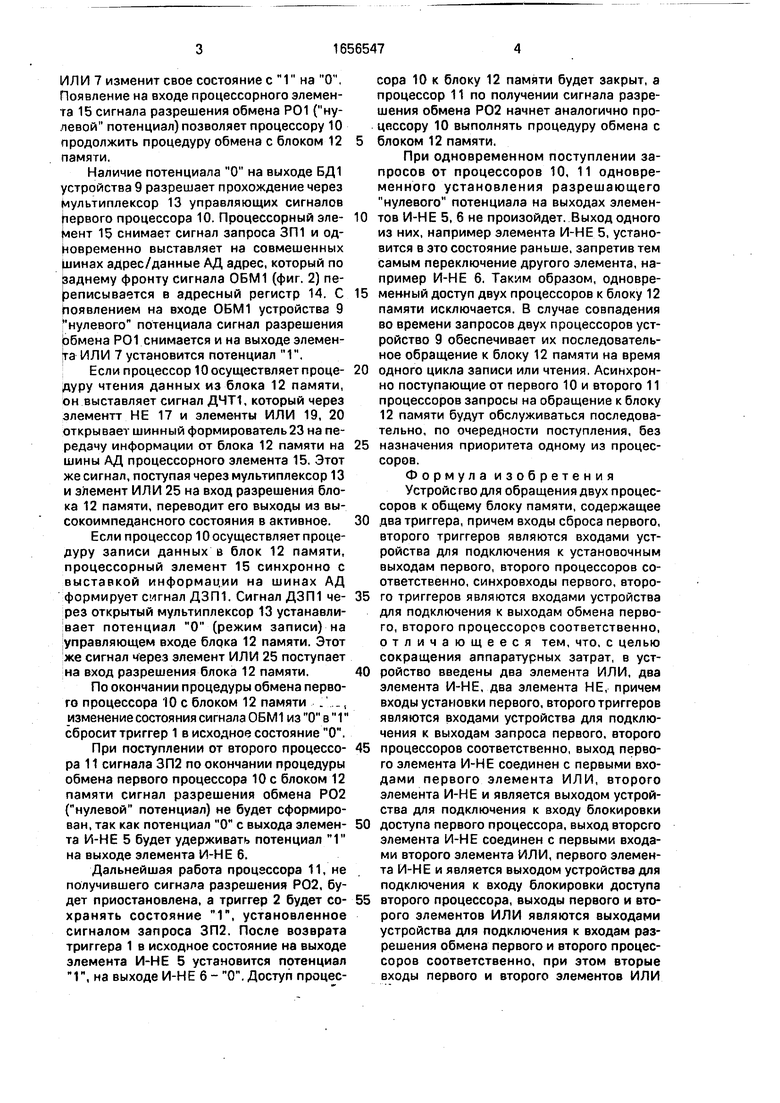

На фиг. 1 приведена схема устройства; на фиг. 2- схема использования устройства совместно с двумя процессорами; на фиг. 3- временная диаграмма работы устройства совместно с двумя процессорами.

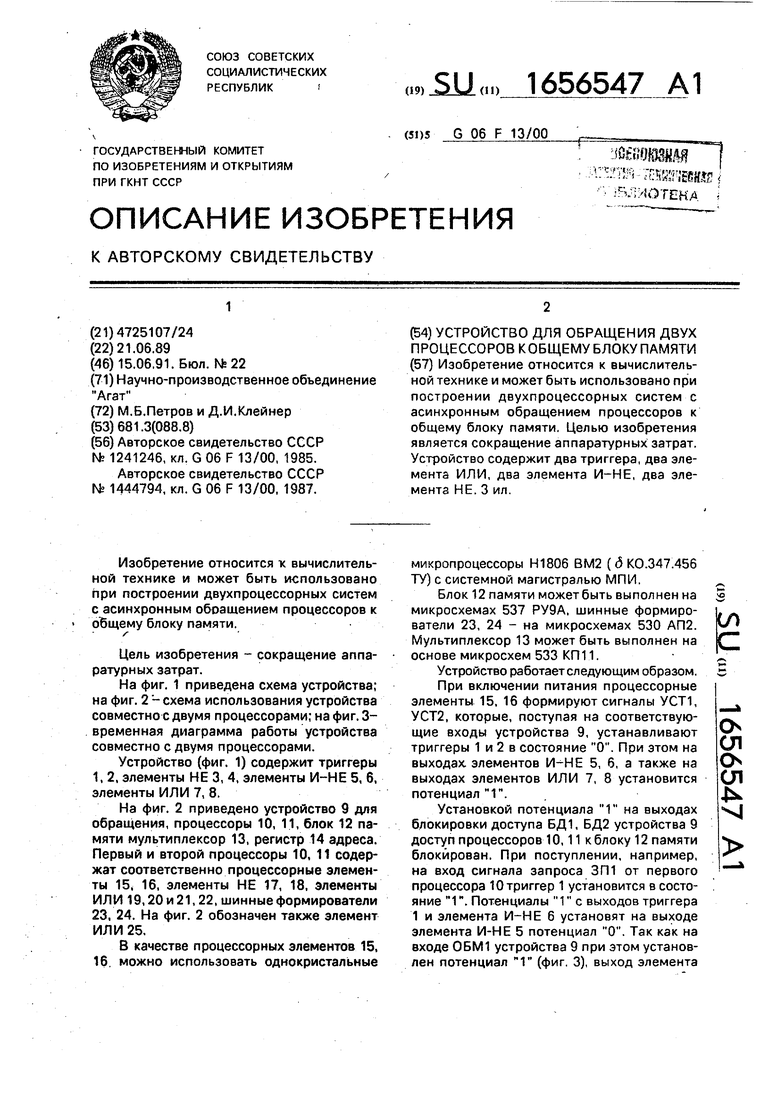

Устройство (фиг. 1) содержит триггеры 1, 2, элементы НЕ 3, 4, элементы И-НЕ 5, 6, элементы ИЛИ 7, 8.

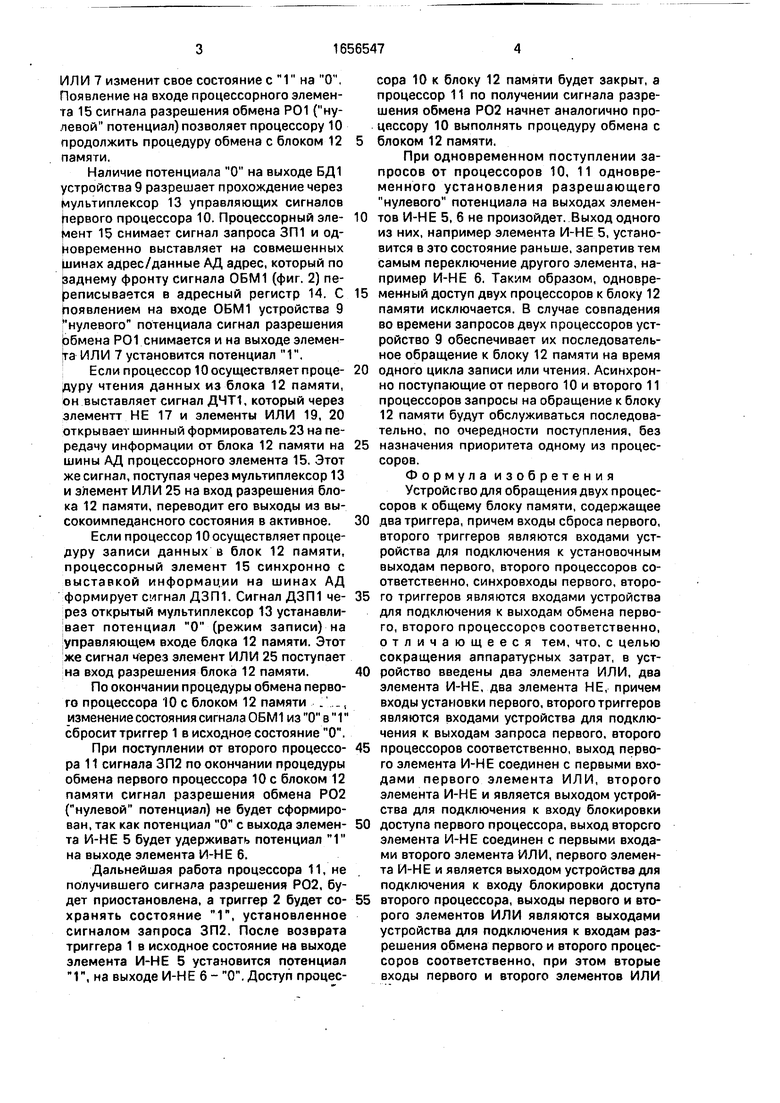

На фиг. 2 приведено устройство 9 для обращения, процессоры 10, 11, блок 12 памяти мультиплексор 13, регистр 14 адреса. Первый и второй процессоры 10, 11 содержат соответственно процессорные элементы 15, 16, элементы НЕ 17, 18, элементы ИЛИ 19,20 и 21,22, шинные формирователи 23, 24. На фиг. 2 обозначен также элемент ИЛИ 25.

В качестве процессорных элементов 15, 16 можно использовать однокристальные

микропроцессоры Н1806 ВМ2 ( д КО.347.456 ТУ) с системной магистралью МПИ.

Блок 12 памяти может быть выполнен на микросхемах 537 РУ9А, шинные формирователи 23, 24 - на микросхемах 530 АП2. Мультиплексор 13 может быть выполнен на основе микросхем 533 КП11.

Устройство работает следующим образом.

При включении питания процессорные элементы 15, 16 формируют сигналы УСТ1, УСТ2, которые, поступая на соответствующие входы устройства 9, устанавливают триггеры 1 и 2 в состояние О. При этом на выходах элементов И-НЕ 5, 6, а также на выходах элементов ИЛИ 7, 8 установится потенциал 1.

Установкой потенциала 1 на выходах блокировки доступа БД1, БД2 устройства 9 доступ процессоров 10, 11 к блоку 12 памяти блокирован. При поступлении, например, на вход сигнала запроса ЗП1 от первого процессора Ютриггер 1 установится в состояние 1. Потенциалы 1 с выходов триггера 1 и элемента И-НЕ 6 установят на выходе элемента И-НЕ 5 потенциал О. Так как на входе ОБМ1 устройства 9 при этом установлен потенциал 1 (фиг. 3), выход элемента

V-

Ј

О

ел о ел

VJ

ИЛИ 7 изменит свое состояние с 1 на О. Появление на входе процессорного элемента 15 сигнала разрешения обмена Р01 (нулевой потенциал) позволяет процессору 10 продолжить процедуру обмена с блоком 12 памяти.

Наличие потенциала О на выходе БД1 устройства 9 разрешает прохождение через мультиплексор 13 управляющих сигналов первого процессора 10. Процессорный эле- мент 15 снимает сигнал запроса ЗП1 и одновременно выставляет на совмешенных шинах адрес/данные АД адрес, который по заднему фронту сигнала ОБМ1 (фиг. 2) переписывается в адресный регистр 14. С появлением на входе ОБМ1 устройства 9 нулевого потенциала сигнал разрешения обмена Р01 снимается и на выходе элемента ИЛИ 7 установится потенциал 1.

Если процессор 10 осуществляет проце- АУРУ чтения данных из блока 12 памяти, он выставляет сигнал ДЧТ1, который через элементт НЕ 17 и элементы ИЛИ 19, 20 открывает шинный формирователь 23 на передачу информации от блока 12 памяти на шины АД процессорного элемента 15. Этот же сигнал, поступая через мультиплексор 13 и элемент ИЛИ 25 на вход разрешения блока 12 памяти, переводит его выходы из вы- сокоимпедансного состояния в активное.

Если процессор 10 осуществляет процедуру записи данных в блок 12 памяти, процессорный элемент 15 синхронно с выставкой информации на шинах АД формирует сигнал ДЗП1. Сигнал ДЗП1 че- рез открытый мультиплексор 13 устанавливает потенциал О (режим записи) на управляющем входе блока 12 памяти. Этот же сигнал через элемент ИЛИ 25 поступает на вход разрешения блока 12 памяти.

По окончании процедуры обмена первого процессора 10 с блоком 12 памяти . , изменение состояния сигнала ОБМ1 из О в 1 сбросит триггер 1 в исходное состояние О.

При поступлении от второго процессе- ра 11 сигнала ЗП2 по окончании процедуры обмена первого процессора 10с блоком 12 памяти сигнал разрешения обмена Р02 (нулевой потенциал) не будет сформирован, так как потенциал О с выхода элемен- та И-НЕ 5 будет удерживать потенциал Г на выходе элемента И-НЕ 6.

Дальнейшая работа процессора 11, не получившего сигнала разрешения Р02, будет приостановлена, а триггер 2 будет со- хранять состояние 1, установленное сигналом запроса ЗП2. После возврата триггера 1 в исходное состояние на выходе элемента И-НЕ 5 установится потенциал Г, на выходе И-НЕ 6 - О. Доступ процессора 10 к блоку 12 памяти будет закрыт, а процессор 11 по получении сигнала разрешения обмена Р02 начнет аналогично процессору 10 выполнять процедуру обмена с блоком 12 памяти.

При одновременном поступлении запросов от процессоров 10, 11 одновременного установления разрешающего нулевого потенциала на выходах элементов И-НЕ 5, 6 не произойдет. Выход одного из них, например элемента И-НЕ 5, установится в это состояние раньше, запретив тем самым переключение другого элемента, например И-НЕ 6. Таким образом, одновременный доступ двух процессоров к блоку 12 памяти исключается. В случае совпадения во времени запросов двух процессоров устройство 9 обеспечивает их последовательное обращение к блоку 12 памяти на время одного цикла записи или чтения. Асинхронно поступающие от первого 10 и второго 11 процессоров запросы на обращение к блоку 12 памяти будут обслуживаться последовательно, по очередности поступления, без назначения приоритета одному из процессоров.

Формула изобретения Устройство для обращения двух процессоров к общему блоку памяти, содержащее два триггера, причем входы сброса первого, второго триггеров являются входами устройства для подключения к установочным выходам первого, второго процессоров соответственно, синхровходы первого, второго триггеров являются входами устройства для подключения к выходам обмена первого, второго процессоров соответственно, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены два элемента ИЛИ, два элемента И-НЕ, два элемента НЕ, причем входы установки первого, второго триггеров являются входами устройства для подключения к выходам запроса первого, второго процессоров соответственно, выход первого элемента И-НЕ соединен с первыми входами первого элемента ИЛИ, второго элемента И-НЕ и является выходом устройства для подключения к входу блокировки доступа первого процессора, выход второго элемента И-НЕ соединен с первыми входами второго элемента ИЛИ, первого элемента И-НЕ и является выходом устройства для подключения к входу блокировки доступа второго процессора, выходы первого и второго элементов ИЛИ являются выходами устройства для подключения к входам разрешения обмена первого и второго процессоров соответственно, при этом вторые входы первого и второго элементов ИЛИ

соединены с выходами первого и второго элементов НЕ соответственно, входы которых соединены с синхровходами первого и второго триггеров соответственно, единичные выходы которых соединены с вто-

рыми входами первого и второго элемент тов И-НЕ соответственно, информационные входы первого и второго триггеров подключены к шине нулевого потенциала устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для синхронизации работы двух процессоров с общим блоком памяти | 1987 |

|

SU1444794A1 |

| Устройство для сопряжения двух микроЭВМ с общей памятью | 1987 |

|

SU1550520A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство для сопряжения двух процессоров через общую память | 1990 |

|

SU1758647A1 |

| Устройство для сопряжения двух процессоров | 1991 |

|

SU1784983A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении двухпроцессорных систем с асинхронным обращением процессоров к общему блоку памяти. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит два триггера, два элемента ИЛИ, два элемента И-НЕ, два элемента НЕ. 3 ил.

Фиг.1

4 - отключенное состоят

..3

| Устройство для сопряжения поцессоров с общим блоком памяти | 1984 |

|

SU1241246A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синхронизации работы двух процессоров с общим блоком памяти | 1987 |

|

SU1444794A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-21—Подача