Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке средств управления и отладки вычислительных систем, в которых осуществляется оперативная коррекция программ при обнаружении физических дефектов и дефектов проектирования, а также при изменении функций, выполняемых системой

Цель изобретения состоит в сокращении объема памяти за счет реализации устройством хранения и выполнения программ коррекции, управляющих алгоритмов и расширении области применения устройства путем выполнения данной коррекции, не прерывая работы устройства.

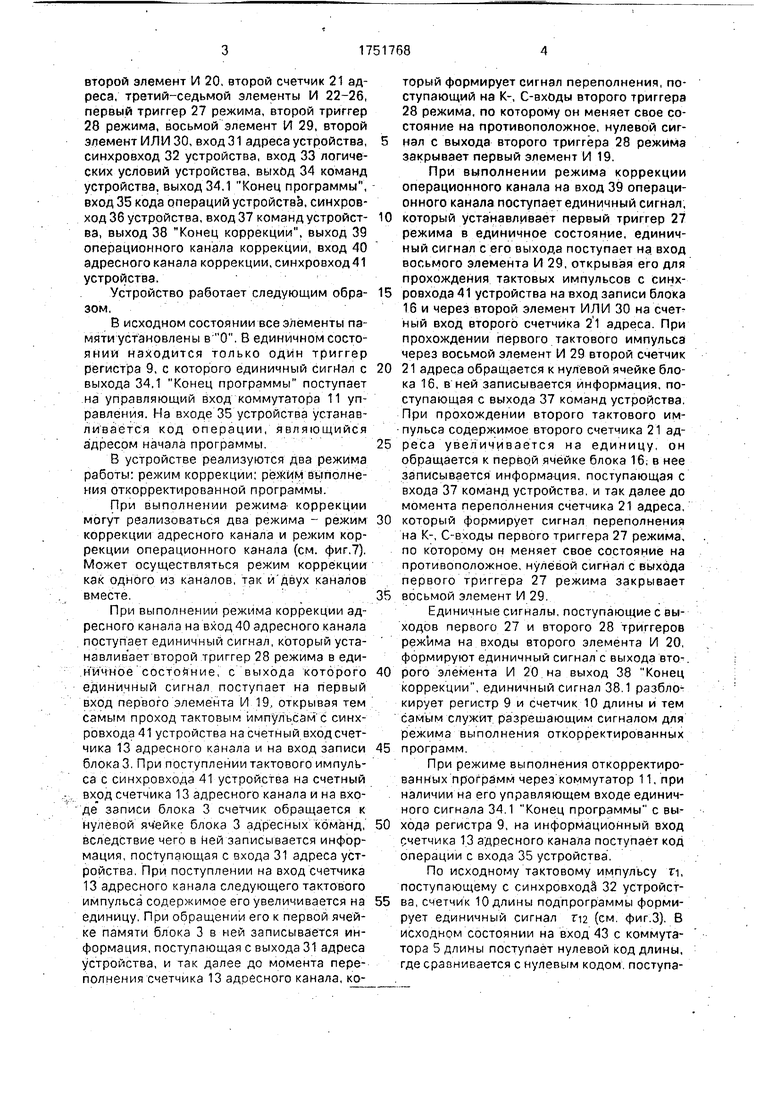

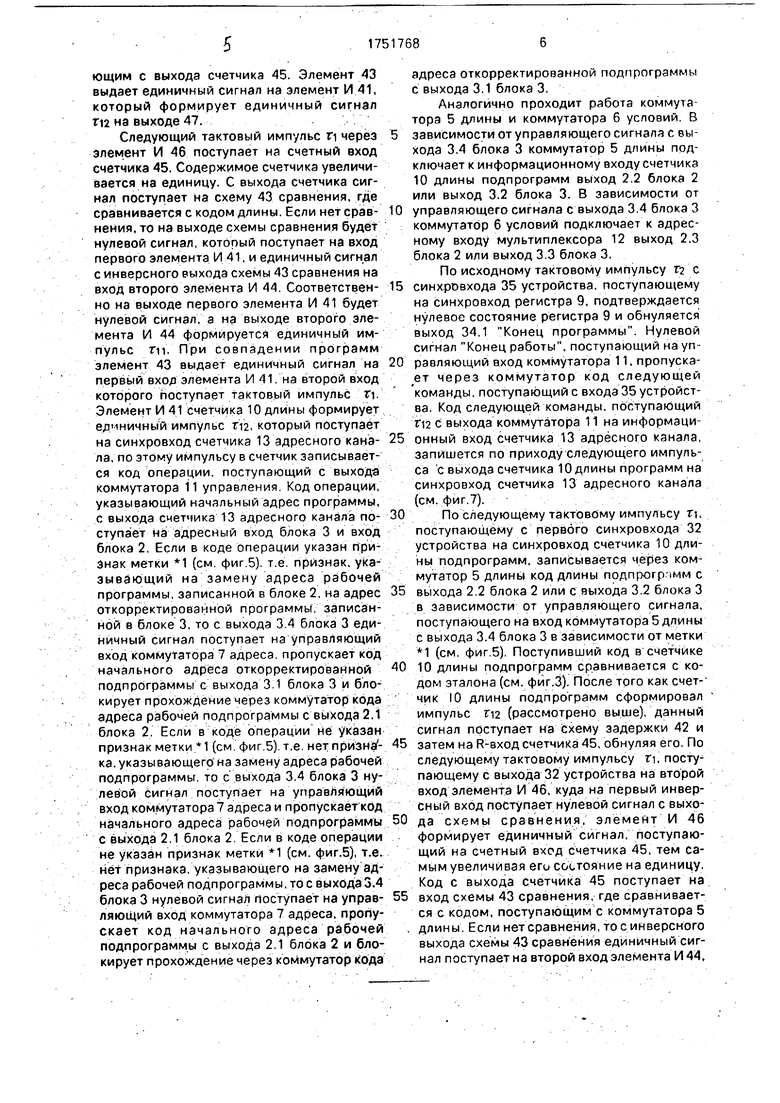

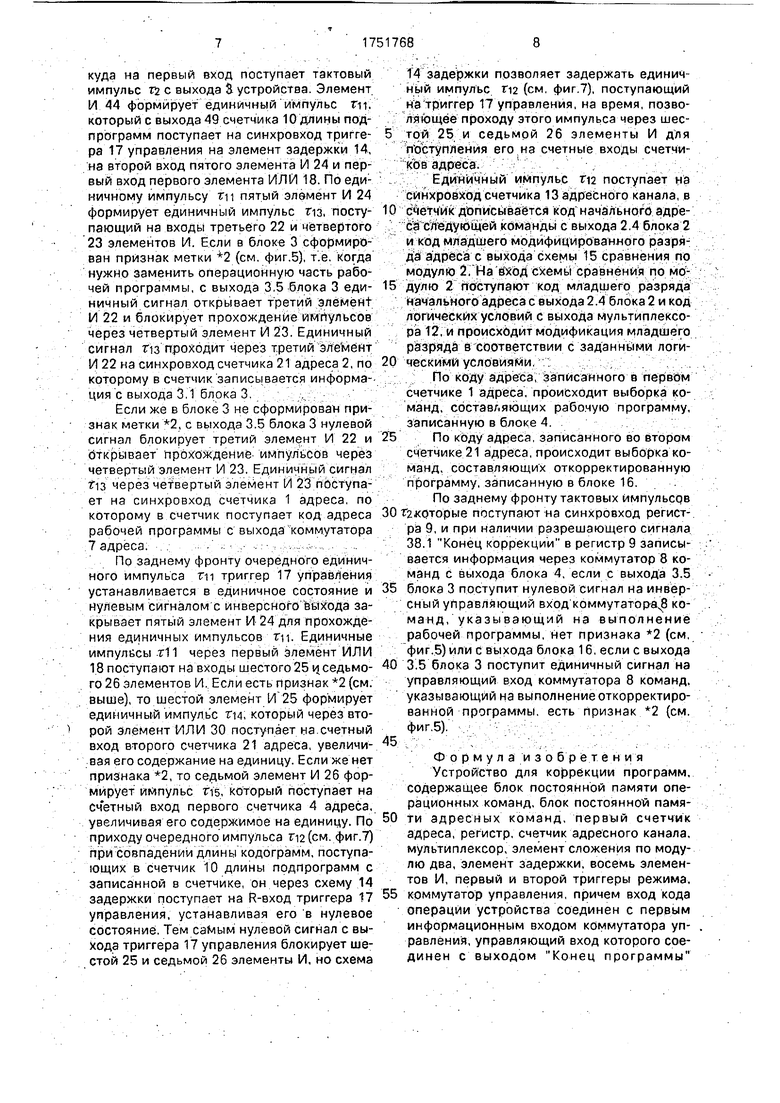

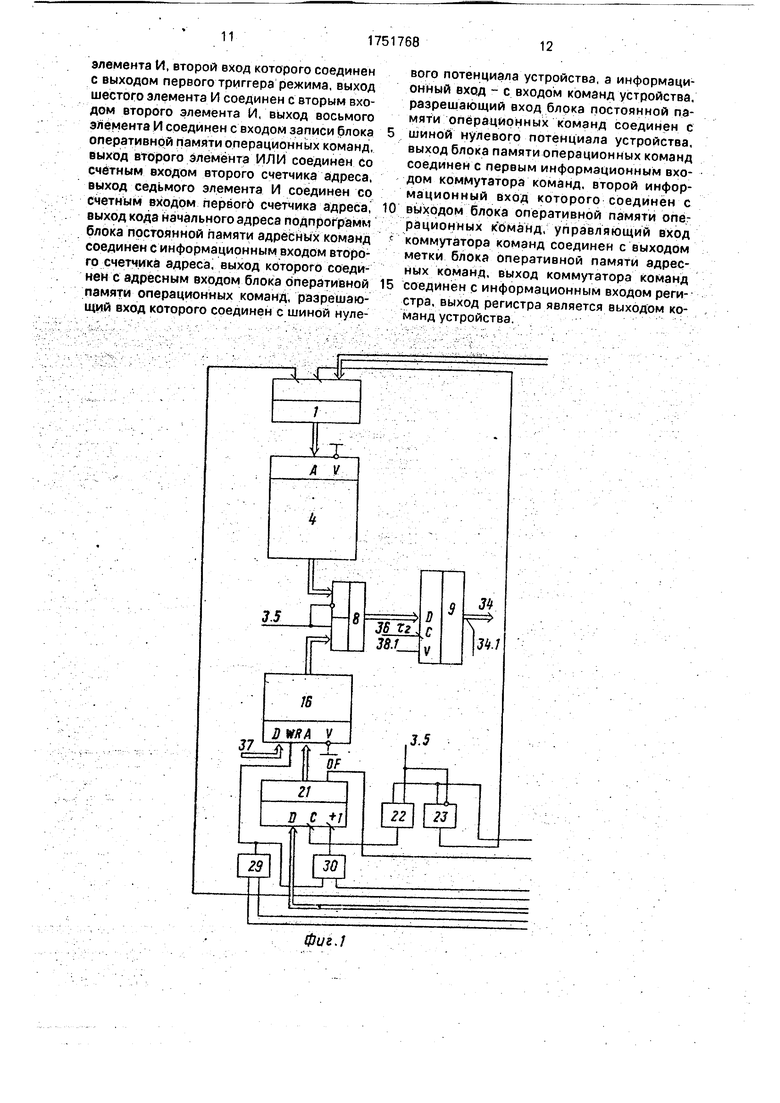

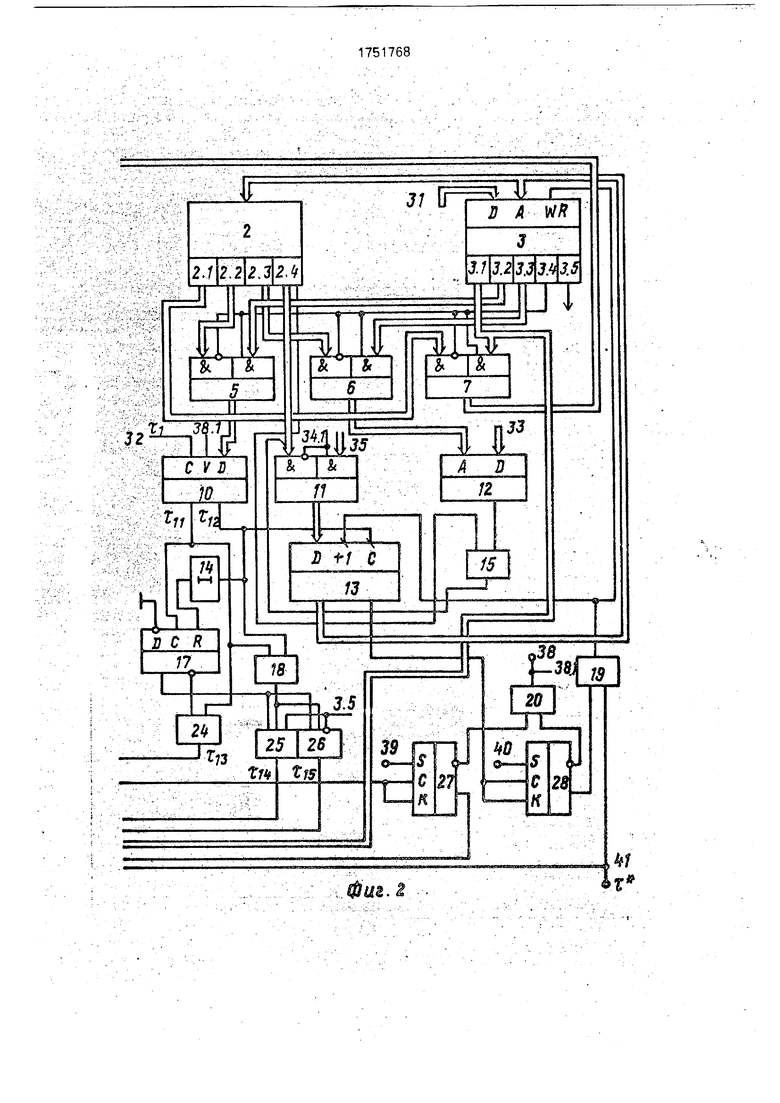

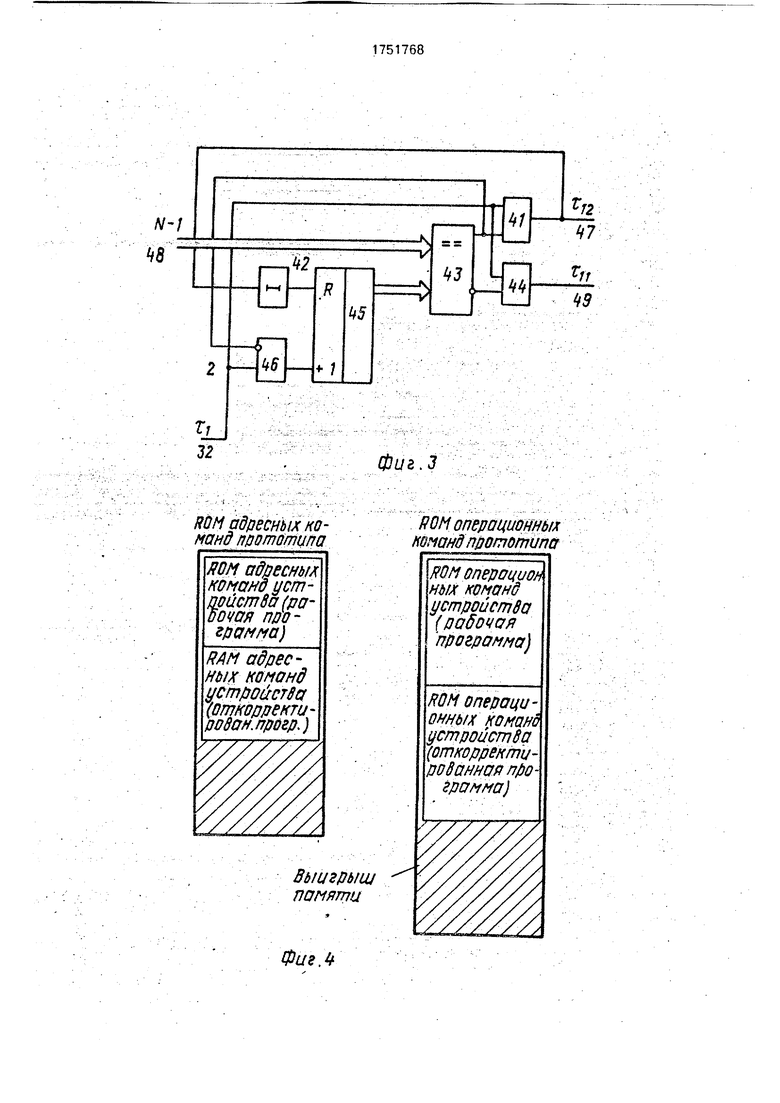

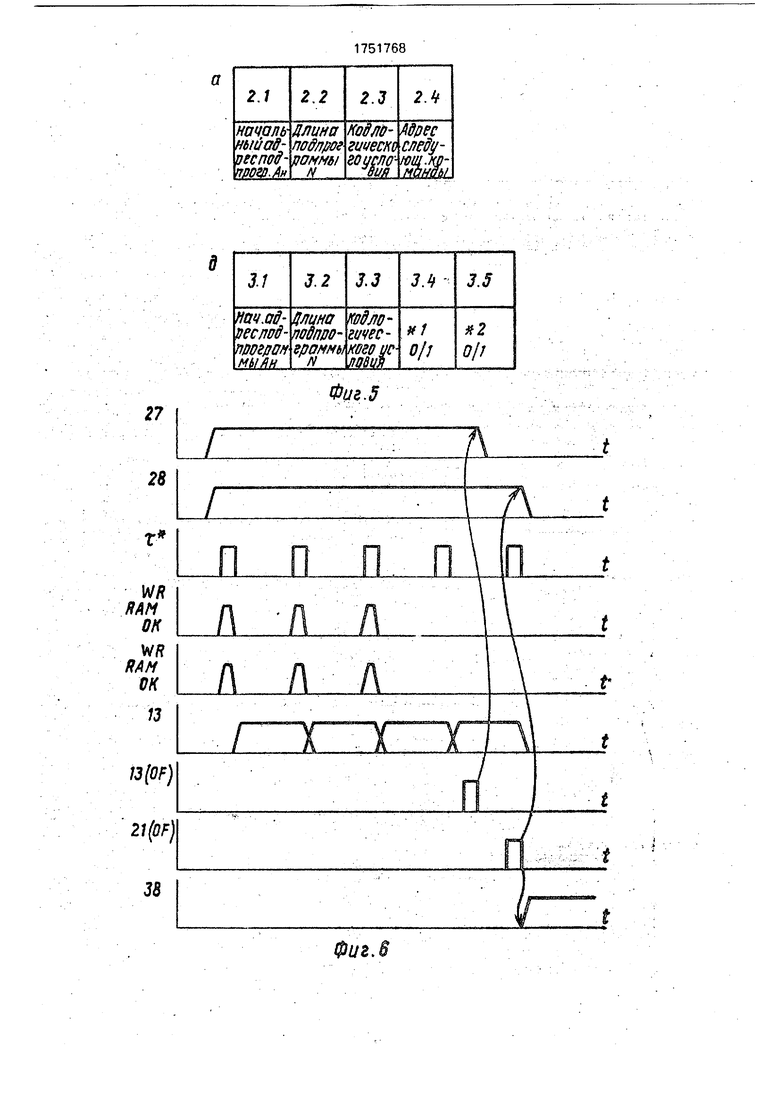

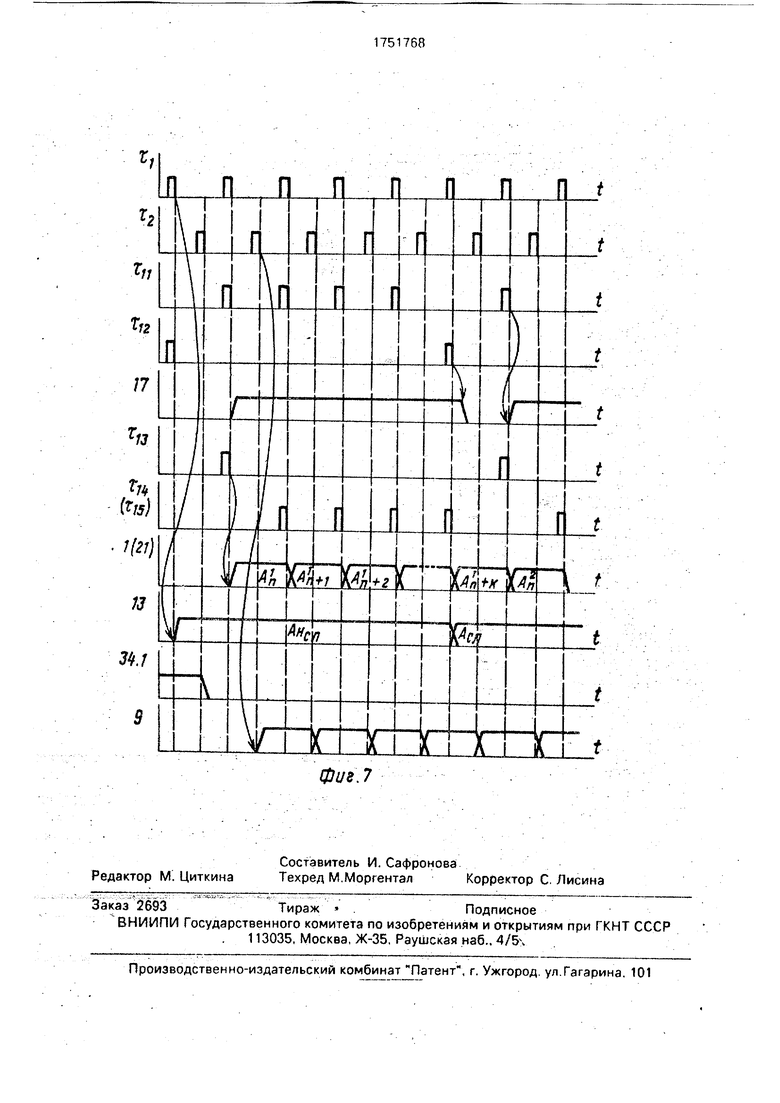

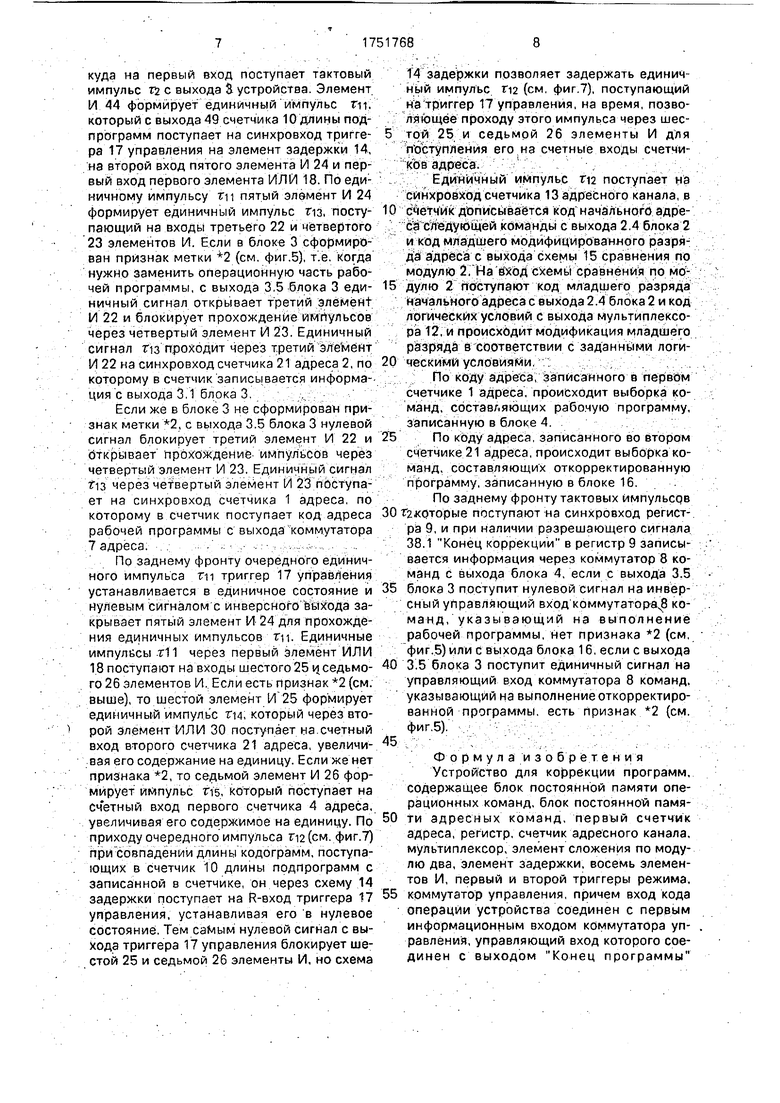

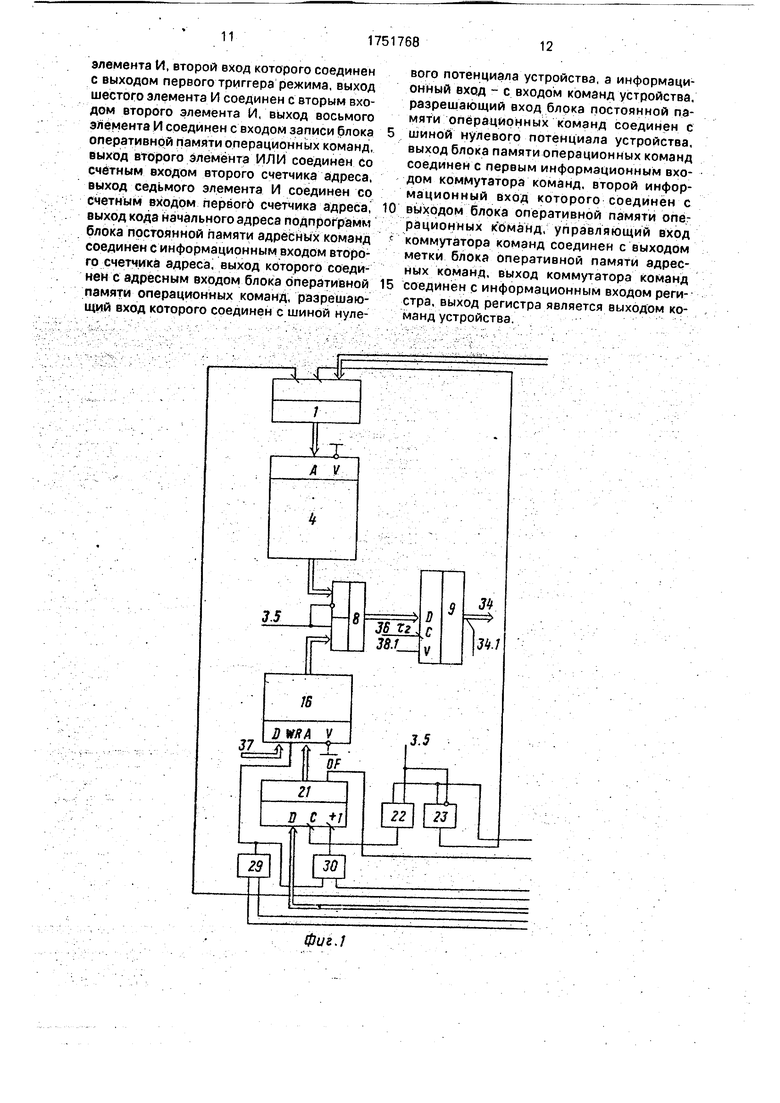

На фиг 1 2 показана функциональная схема устройства на фиг 3 - функциональная схема счетчика длины, на фиг.4 - размещение информации в блоках памяти; на

фиг 5 - форматы команд; на фиг 6 - временные диаграммы работы устройства в режиме коррекции; на фиг 7 - временные диаграммы работы устройства в режиме выполнения откорректированной программы

Устройство содержит (фиг 1) первый счетчик 1 адреса, блок 2 адресных команд постоянной памяти, блок 3 оперативной памяти адресных команд, блок 4 постоянной памяти операционных команд коммутатор 5 длины, коммутатор 6 условий коммутатор 7 адреса коммутатор 8 команд, регистр 9, счетчик 10 длины подпрограммы, коммутатор 11 управления, мультиплексор 12, счетчик 13 адресного канала, элемент 14 задержки, элемент 15 сложения по модулю два, блок 16 оперативной памяти операционных команд, триггер 17 управления, первый элемент ИЛИ 18, первый элемент И 19,

Ч СЯ

vl О 00

второй элемент И 20, второй счетчик 21 адреса, третий-седьмой элементы И 22-26, первый триггер 27 режима, второй триггер 28 режима, восьмой элемент И 29, второй элемент ИЛИ 30, вход 31 адреса устройства, синхровход 32 устройства, вход 33 логических условий устройства, выход 34 команд устройства, выход 34,1 Конец программы, вход 35 кода операций устройства, синхровход 36 устройства, вход 37 команд устройства, выход 38 Конец коррекции, выход 39 операционного канала коррекции, вход 40 адресного канала коррекции,синхровход 41 устройства.

Устройство работает следующим образом,

В исходном состоянии все элементы памяти установлены в О. В единичном состо- янии находится только один триггер регистра 9, с которого единичный сигнал с выхода 34.1 Конец программы поступает на управляющий вход коммутатора 11 управления. На входе 35 устройства устанавливается код операции, являющийся адресом начала программы.

В устройстве реализуются два режима работы: режим коррекции; режим выполнения откорректированной программы.

При выполнении режима коррекции могут реализоваться два режима - режим коррекции адресного канала и режим коррекции операционного канала (см. фиг.7). Может осуществляться режим коррекции как одного из каналов, так и двух каналов вместе.

При выполнении режима коррекции адресного канала на вход 40 адресного канала поступает единичный сигнал, который устанавливает второй триггер 28 режима в единичное состояние, с выхода которого единичный сигнал поступает на первый вход первого элемента И 19, открывая тем самым проход тактовым импульсам с смнх- ровхода 41 устройства на счетный вход счетчика 13 адресного канала и на вход записи блока 3 При поступлении тактового импульса с синхровхода 41 устройства на счетный вход счетчика 13 адресного канала и на входе записи блока 3 счетчик обращается к нулевой ячейке блока 3 адресных команд, вследствие чего в йей записывается информация, поступающая с входа 31 адреса устройства При поступлении на вход счетчика 13 адресного канала следующего тактового импульса содержимое его увеличивается на единицу, При обращении его к первой ячейке памяти блока 3 в ней записывается информация, поступающая с выхода 31 адреса устройства, и так далее до момента переполнения счетчика 13 адоесного канала, который формирует сигнал переполнения, поступающий на К-, С-вхОды второго триггера 28 режима, по которому он меняет свое состояние на противоположное, нулевой сигнал с выхода второго триггера 28 режима закрывает первый элемент И 19.

При выполнении режима коррекции операционного канала на вход 39 операционного канала поступает единичный сигнал,

который устанавливает первый триггер 27 режима в единичное состояние, единичный сигнал с его выхода поступает на вход восьмого элемента И 29, открывая его для прохождения тактовых импульсов с синхровхода 41 устройства на вход записи блока 16 и через второй элемент ИЛИ 30 на счетный вход второго счетчика 21 адреса. При прохождении первого тактового импульса через восьмой элемент И 29 второй счетчик

21 адреса обращается к нулевой ячейке блока 16, в ней записывается информация, поступающая с выхода 37 команд устройства. При прохождении второго тактового импульса содержимое второго счетчика 21 адреса увеличивается на единицу, он обращается к первой ячейке блока 16, в нее записывается информация, поступающая с входа 37 команд устройства, и так далее до момента переполнения счетчика 21 адреса,

который формирует сигнал переполнения на К-, С-входы первого триггера 27 режима, по которому он меняет свое состояние на противоположное, нулевой сигнал с выхода первого триггера 27 режима закрывает

восьмой элемент И 29

Единичные сигналы, поступающие с выходов первого 27 и второго 28 триггеров режима на входы второго элемента И 20, формируют единичный сигнал с выхода второго элемента И 20 на выход 38 Конец коррекции, единичный сигнал 38 1 разблокирует регистр 9 и счетчик 10 длины и тем самым служит разрешающим сигналом для режима выполнения откорректированных

программ

При режиме выполнения откорректированных программ через коммутатор 11, при наличии на его управляющем входе единичного сигнала 34 1 Конец программы с выхода регистра 9, на информационный вход счетчика 13 адресного канала поступает код операции с входа 35 устройства.

По исходному тактовому импульсу п, поступающему с синхровходЗ 32 устройства, счетчик 10 длины подпрограммы формирует единичный сигнал тп (см фиг.З). В исходном состоянии на вход 43 с коммутатора 5 длины поступает нулевой код длины, где сравнивается с нулевым кодом поступающим с выхода счетчика 45. Элемент 43 выдает единичный сигнал на элемент И 41, который формирует единичный сигнал Па на выходе 47.

Следующий тактовый импульс Г1 через элемент И 46 поступает на счетный вход счетчика 45. Содержимое счетчика увеличивается на единицу. С выхода счетчика сигнал поступает на схему 43 сравнения, где сравнивается с кодом длины Если нет срав- нения, то на выходе схемы сравнения будет нулевой сигнал, котопый поступает на вход первого элемента И 41, и единичный сигнал с инверсного выхода схемы 43 сравнения на вход второго элемента И 44 Соответствен- но на выходе первого элемента И 41 будет нулевой сигнал, а на выходе второго элемента И 44 формируется единичный импульс Гц При совпадении программ элемент 43 выдает единичный сигнал на первый вход элемента И 41 на второй вход которого поступает тактовый импульс ri Элемент И 41 счетчика 10 длины формирует единичный импульс па, который поступает на синхровход счетчика 13 адресного кана- ла, по этому импульсу в счетчик записывается код операции поступающий с выхода коммутатора 11 управления Код операции, указывающий начальный адрес программы, с выхода сметчика 13 адресного канала по- ступает на адресный вход блока 3 и вход блока 2 Если в коде операции указан признак метки 1 (см фиг 5) т е признак, указывающий на замену адреса рабочей программы записанной в блоке 2, на адрес откорректированной программы записанной в блоке 3, то с выхода 3 4 блока 3 единичный сигнал поступает на управляющий вход коммутатора 7 адреса пропускает код начального адреса откорректированной подпрограммы с выхода 3 1 блока 3 и блокирует прохождение через коммутатор кода адреса рабочей подпрограммы с выхода 2.1 блока 2 Если в коде операции не указан признак метки 1 (см фиг 5) те нетпризна - ка. указывающего на замену адреса рабочей подпрограммы то с выхода 3 4 блока 3 нулевой сигнал поступает на управляющий вход коммутатора 7 адреса и пропускает код начального адреса рабочей подпрограммы с выхода 2 1 блока 2 Если в коде операции не указан признак метки 1 (см. фиг.5), т.е. нет признака указывающего на замену адреса рабочей подпрограммы, то с выхода 3.4 блока 3 нулевой сигнал поступает на управ- ляющий вход коммутатора 7 адреса, пропускает код начального адреса рабочей подпрограммы с выхода 2 1 блока 2 и блокирует прохождение через коммутатор кода

адреса откорректированной подпрограммы с выхода 3 1 блока 3

Аналогично проходит работа коммута тора 5 длины и коммутатора 6 условий В зависимости от управляющего сигнала с вы хода 3 4 блока 3 коммутатор 5 длины подключает к информационному входу счетчика 10 длины подпрограмм выход 2 2 блока 2 или выход 3.2 блока 3. В зависимости от управляющего сигнала с выхода 3 4 блока 3 коммутатор б условий подключает к адресному входу мультиплексора 12 выход 2.3 блока 2 или выход 3 3 блока 3,

По исходному тактовому импульсу Г2 с синхровхода 35 устройства, поступающему на синхровход регистра 9, подтверждается нулевое состояние регистра 9 и обнуляется выход 34 1 Конец программы Нулевой сигнал Конец работы, поступающий на управляющий вход коммутатора 11. пропускает через коммутатор код следующей команды, поступающий с входа 35 устройства Код следующей команды, поступающий Л2 с выхода коммутатора 11 на информационный вход счетчика 13 адресного канала запишется по приходу следующего импульса с выхода счетчика 10 длины программ на синхровход счетчика 13 адресного канала (см фиг 7)

По следующему тактовому импульсу Гь поступающему с первого синхровхода 32 устройства на синхровход счетчика 10 длины подпрограмм, записывается через коммутатор 5 длины код длины подпрогр мм с выхода 2 2 блока 2 или с выхода 3 2 блока 3 в зависимости от управляющего сигнала, поступающего на вход коммутатора 5 длины с выхода 3 4 блока 3 в зависимости от метки 1 (см фиг 5) Поступивший код в счетчике 10 длины подпрограмм сравнивается с кодом эталона (см. фиг 3) После того как счетчик Ю длины подпрограмм сформировал импульс Г12 (рассмотрено выше) данный сигнал поступает на схему задержки 42 и затем на R-вход счетчика 45, обнуляя его По следующему тактовому импульсу гт. поступающему с выхода 32 устройства на второй вход элемента И 46, куда на первый инверсный вход поступает нулевой сигнал с выхода схемы сравнения, элемент И 46 формирует единичный сигнал, поступающий на счетный вход счетчика 45, тем самым увеличивая его состояние на единицу Код с выхода счетчика 45 поступает на вход схемы 43 сравнения, где сравнивается с кодом, поступающим с коммутатора 5 длины Если нет сравнения, то с инверсного выхода схемы 43 сравнения единичный сигнал поступает на второй вход элемента И 44,

куда на первый вход поступает тактовый импульс тг с выхода S устройства Элемент И 44 формирует единичный импульс Гц, который с выхода 49 счетчика 10 длины подпрограмм поступает на синхровход триггера 17 управления на элемент задержки 14, на второй вход пятого элемента И 24 и первый вход первого элемента ИЛИ 18. По единичному импульсу тц пятый элемент И 24 формирует единичный импульс пз, поступающий на входы третьего 22 и четвертого 23 элементов И. Если в блоке 3 сформирован признак метки 2 (см фиг.5), т.е когда нужно заменить операционную часть рабочей программы, с выхода 3 5 блока 3 единичный сигнал открывает третий элемент И 22 и блокирует прохождение импульсов через четвертый элемент И 23. Единичный сигнал пз проходит через третий эле мент И 22 на синхровход счетчика 21 адреса 2, по которому в счетчик записывается информация с выхода 3 1 блока 3

Если же в блоке 3 не сформирован признак метки 2, с выхода 3 5 блока 3 нулевой сигнал блокирует третий элемент И 22 и открывает прохождение импульсов через четвертый элемент И 23, Единичный сигнал Г13 через четвертый элемент И 23 поступает на синхровход счетчика 1 адреса по которому в счетчик поступает код адреса рабочей программы с выхода коммутатора 7 адреса.

По заднему фронту очередного единичного импульса Гц триггер 17 управления устанавливается в единичное состояние и нулевым сигналом с инверсного выхода закрывает пятый элемент И 24 для прохождения единичных импульсов Гц. Единичные импуль сы т11 через первый элемент ИЛИ 18 поступают на входы шестого 25 и седьмого 26 элементов И Если есть признак 2 (см. выше), то шестой элемент И 25 формирует единичный импульс ri4, который через вто- рой элемент 1/1ЛИ 30 поступает на счетный вход второго счетчика 21 адреса, увеличивая его содержание на единицу. Если же нет признака 2, то седьмой элемент И 26 формирует импульс Tig, который поступает на сч етный вход первого счетчика 4 адреса, увеличивая его содержимое на единицу. По приходу очередного импульса Г12(см фиг.7) при совпадении длины кодограмм, поступающих в счетчик 10 длины подпрограмм с записанной в счетчике, он через схему 14 задержки поступает на R-вход триггера 17 управления, устанавливая его в нулевое состояние Тем самым нулевой сигнал с выхода триггера 17 управления блокирует шестой 25 и седьмой 26 элементы И, но схема

14 задержки позволяет задержать единичный импульс ti2 (см фиг 7), поступающий на триггер 17 управления, на время, позволяющее проходу этого импульса через шестой 25 и седьмой 26 элементы И для поступления его на счетные входы счетчиков адреса.

Единичный импульс Г12 поступает на синхровход счетчика 13 адресного канала, в

счетчик дописывается код начального адреса следующей команды с выхода 2 4 блока 2 и код младшего модифицированного разряда адреса с выхода схемы 15 сравнения по модулю 2, На вход схемы сравнения по модулю 2 поступают код младшего разряда начального адреса с выхода 2.4 блока 2 и код логических условий с выхода мультиплексора 12, и происходит модификация младшего разряда в соответствии с заданными логическими условиями

По коду адреса, записанного в первом счетчике 1 адреса, происходит выборка команд, составляющих рабочую программу, записанную в блоке 4

По коду адреса записанного во втором счетчике 21 адреса, происходит выборка команд, составляющих откорректированную программу, записанную в блоке 16

По заднему фронту тактовых импульсрв

такоторые поступают на синхровход регистра 9, и при наличии разрешающего сигнала 38.1 Конец коррекции в регистр 9 записывается информация через коммутатор 8 команд с выхода блока 4, если с выхода 3.5

блока 3 поступит нулевой сигнал на инверсный управляющий вход коммутатора ко- манд, указывающий на выполнение рабочей программы, нет признака 2 (см фиг.5) или с выхода блока 16 если с выхода

3.5 блока 3 поступит единичный сигнал на управляющий вход коммутатора 8 команд, указывающий на выполнение откорректированной программы есть признак 2 (см фиг 5)

Формула изобретения Устройство для коррекции программ, содержащее блок постоянной памяти операционных команд, блок постоянной памяти адресных команд, первый счетчик адреса, регистр, счетчик адресного канала, мультиплексор, элемент сложения по модулю два, элемент задержки, восемь элементов И, первый и второй триггеры режима,

коммутатор управления причем вход кода операции устройства соединен с первым информационным входом коммутатора управления, управляющий вход которого соединен с выходом Конец программы

регистра, второй информационный вход коммутатора управления соединен с выходом кода адреса следующей команды блока постоянной памяти адресных команд, вход кода логических условий устройства соединен с информационным входом мультиплексора, выход которого соединен с выходом младшего разряда кода адреса следующей команды блока постоянной памяти адресных команд, выход элемента сложения по модулю два соединен с информационным входом счетчика адресного канала, выход счетчика адресного канала соединен с адресным входом блока постоянной памяти адресных команд, выход пятого элемента И соединен с первыми входами третьего, четвертого элементов И, выход четвертого элемента И соединен с синхровходом первого счетчика адреса, инверсный выход второго триггера режима соединен с вторым входом второго элемента И, первый вход синхронизации устройства соединен С вторым входом первого элемента И, первый вход которого соединен с выходом второго триггера режима, выход первого элемента И соединен со счетным входом счетчика адресного канала, отличающееся тем, что, с целью расширения области применения и сокращения объема памяти, устройство дополнительно содержит блок оперативной памяти операционных команд, блок оперативной памяти адресных команд, коммутатор команд, второй счетчик адреса, коммутатор длины, коммутатор условий, коммутатор адреса, счетчик длины подпрограмм, триггер управления, первый, второй элементы ИЛИ, причем второй Ьход синхронизации устройства соединен с синхровходом счетчика длины подпрограмм, третий вход синхронизации устройства соединен с синхровходом регистра, выход блока постоянной памяти кода начального адреса подпрограммы адресных команд соединен с первым информационным входом коммутатора адреса, второй информационный вход которого соединен с выходом кода начального адреса подпрограмм блока оперативной памяти адресных команд, выход кода длины блока постоянной памяти адресных команд соединен с первым информационным входом коммутатора длины, второй информационный вход которого соединен С выходом кода длины блока оперативной памяти адресных команд, выход кода логических условий блока постоянной памяти адресных команд соединен с первым информационным входом коммутатора условий, второй информационный вход которого соединен с выходом кода логических условий блока оперативной памяти адресных команд, выход кода длины блока оперативной памяти адресных команд соединен с управляющими входами коммутатора длины, коммутатора условий,

коммутатора адреса, выход коммутатора длины соединен с информационным входом счетчика длины подпрограмм, первый выход которого соединен с синхровходом триггера управления, с первым входом пер0 вого элемента ИЛИ, второй выход счетчика длины соединен с синхровходом счетчика адресного канала, вторым входом первого элемента ИЛИ, с входом элемента задержки, выход которого еоедтшен с входом сбро5 са триггера управления, инверсный информационный вход которого подключен к шине нулевого потенциала устройства, выход коммутатора условий соединен с адресным входом мультиплексора, выход

0 счетчика адресного канала соединен с адресным входом блока оперативной памяти адресных команд, выход коммутатора адреса соединен с информационным входом первого счетчика адреса, выход первого

5 элемента И соединен с входом записи блока оперативной памяти адресных команд, вход режима коррекции операционного канала устройства соединен с единичным входом первого триггера режима, К- и С-выходы ко0 торого соединены с выходом переполнения второго счетчика адреса, выход режима коррекции адресного канала устройства соединен с единичным входом второго триггера режима, К- и С-входы которого соединены с

5 выходом переполнения счетчика адресного канала, инверсный выход первого триггера режима соединен с первым входом второго элемента И, выход которого соединен с разрешающими входами счетчика длины под0 программ и регистра и является выходом конца режима коррекции устройства, инверсный выход триггера управления соединен с первым входом пятого элемента И, второй вход которого соединен с первым

5 выходом счетчика длины подпрограмм, выход пятого элемента И соединен с первыми входами третьего, четвертого элементов И, второй вход третьего элемента И и второй инверсный вход четвертого элемента

0 И соединены с выходом кода программы блока оперативной памяти адресных команд, выход триггера управления соединен с первыми входами шестого, седьмого элементов И, вторые входы которых соеди5 нены с выходом первого элемента ИЛИ, третьи входы шестого и седьмого элементов И соединены с выходом кода программы блока памяти оперативной адресных команд, первый вход синхронизации устройства соединен с первым входом восьмого

элемента И, второй вход которого соединен с выходом первого триггера режима, выход шестого элемента И соединен с вторым входом второго элемента И, выход восьмого элемента И соединен с входом записи блока оперативной памяти операционных команд, выход второго элемента ИЛИ соединен со счетным входом второго счетчика адреса, выход седьмого элемента И соединен со счетным входом первогб счетчика адреса, выход кода начального адреса подпрограмм блока постоянной памяти адресных команд соединен с информационным входом второго счетчика адреса, выход которого соединен с адресным входом блока оперативной памяти операционных команд, разрешающий вход которого соединен с шиной нуле0

5

вого потенциала устройства, а информационный вход - с входом команд устройства, разрешающий вход блока постоянной памяти операционных команд соединен с шиной нулевого потенциала устройства, выход блока памяти операционных команд соединен с первым информационным входом коммутатора команд, второй информационный вход которого соединен с выходом блока оперативной памяти операционных команд, управляющий вход коммутатора команд соединен с выходом метки блока оперативной памяти адресных команд, выход коммутатора команд соединен с информационным входом регистра, выход регистра является выходом команд устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для программного управления | 1988 |

|

SU1520480A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Программируемый логический контроллер | 1988 |

|

SU1647518A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Генератор функциональных зависимостей | 1983 |

|

SU1130853A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для анализа производительности вычислительных систем | 1990 |

|

SU1711166A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при разработке средств управления и отладки вычислительных систем, в которых осуществляется оперативная коррекция программ при обнаружении физических дефектов и дефектов проектирова- ния. а также при изменении функций, выполняемых системой. Цель изобретения - расширение области применения и сокращение объема памяти Поставленная цель достигается путем дополнительного введения в известное устройство блока оперативной памяти операционных команд, блока оперативной памяти адресных команд, коммутатора команд, второго счетчика адреса, коммутатора длины, коммутатора условий, коммутатора адреса, счетчика длины подпрограмм триггера управления первого и второго элементов памяти ИЛИ 7 ил Ё

Фиг./

Гт 32

RDM адресных команд прототипа

ЛОМ адресных командуст- пристда (ра- бомя программа)

RAM адресных команд устройства (откорректи- робан.прогр.}

Выигрыш понята

Фиг. 4

Фиг.З

РОМ операционных команд прототипа

ЯОМопероцион ных команд устройства (рабочая

программа)

ROM операционных команд устройстба (откорректированная программа)

™ G

«3

Л

о т

с: е

«ч.

slj

1

0

N

sj

-о ел

«

-4

О)

со

Д

Л

Я

I

«я

Л

п

Я

Т,г

L

17

Ј

/

1

д

J

т

t%

1C

л

1

д

1

1

л

Я

п

L

I.

Я

Jl

д

j

U

«-

Vo

i

t

J

| Ткаченко С Н и др Системы отладки микропроцессорных устройств Харьков, 1989 Авторское свидетельство СССР № 1136160,кл G 06 F 11/26, 1985 |

Авторы

Даты

1992-07-30—Публикация

1990-11-29—Подача