Изобретение относится к вычислительной технике и может быть ксполь зовано в системах обработки дискретной информации.

Цель изобретения - повьппение бы- стродействия преобразователя.

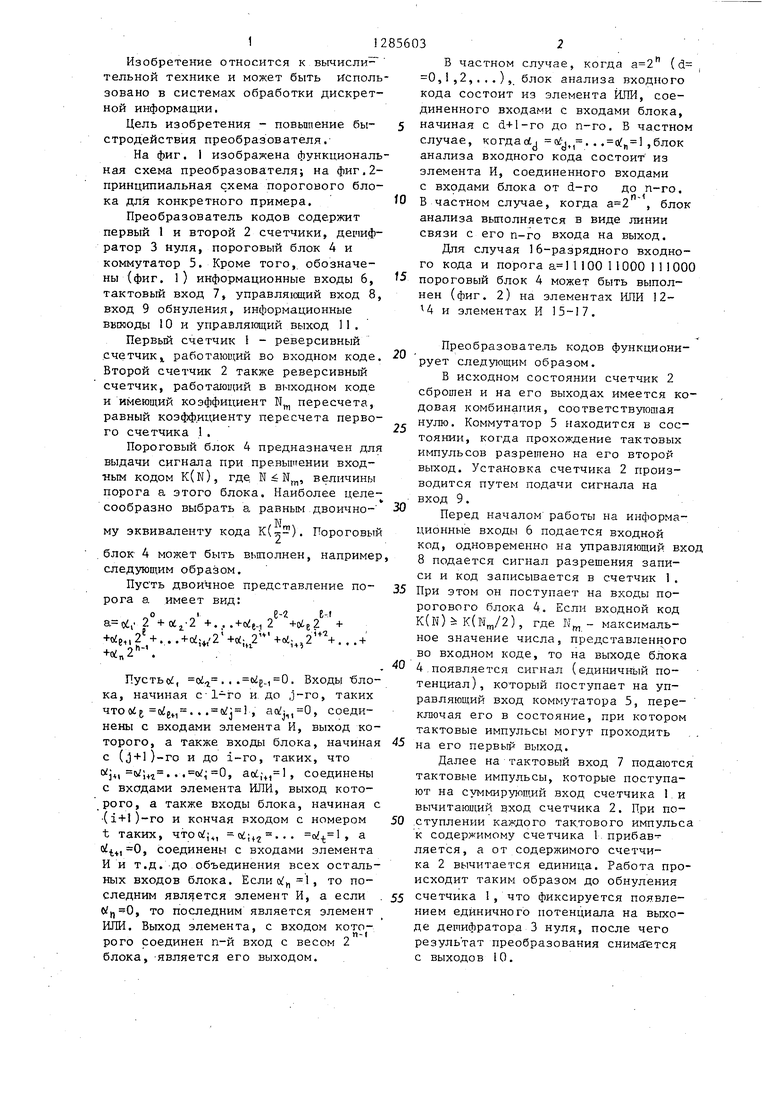

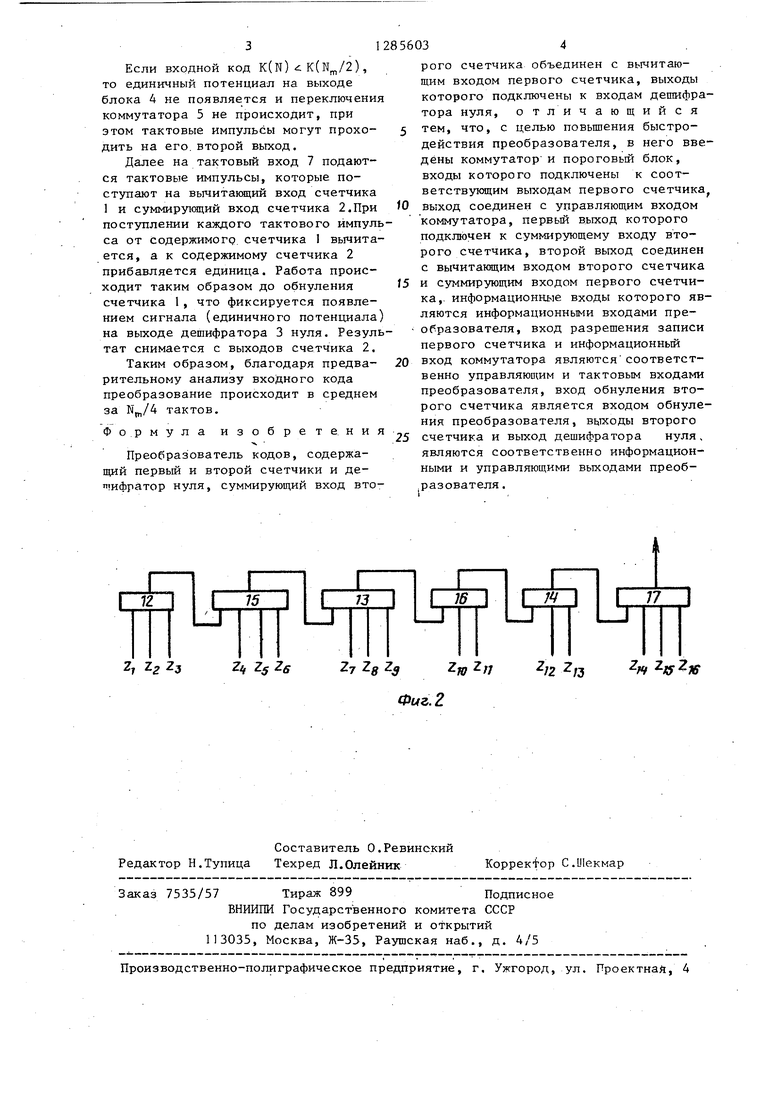

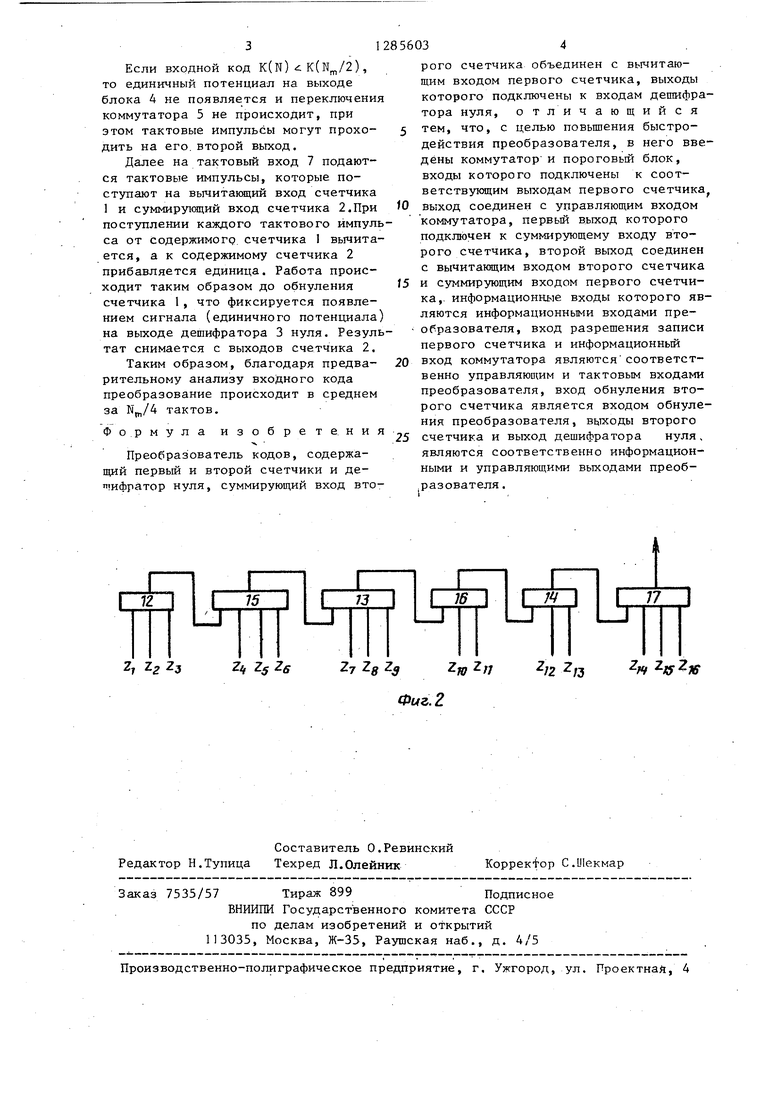

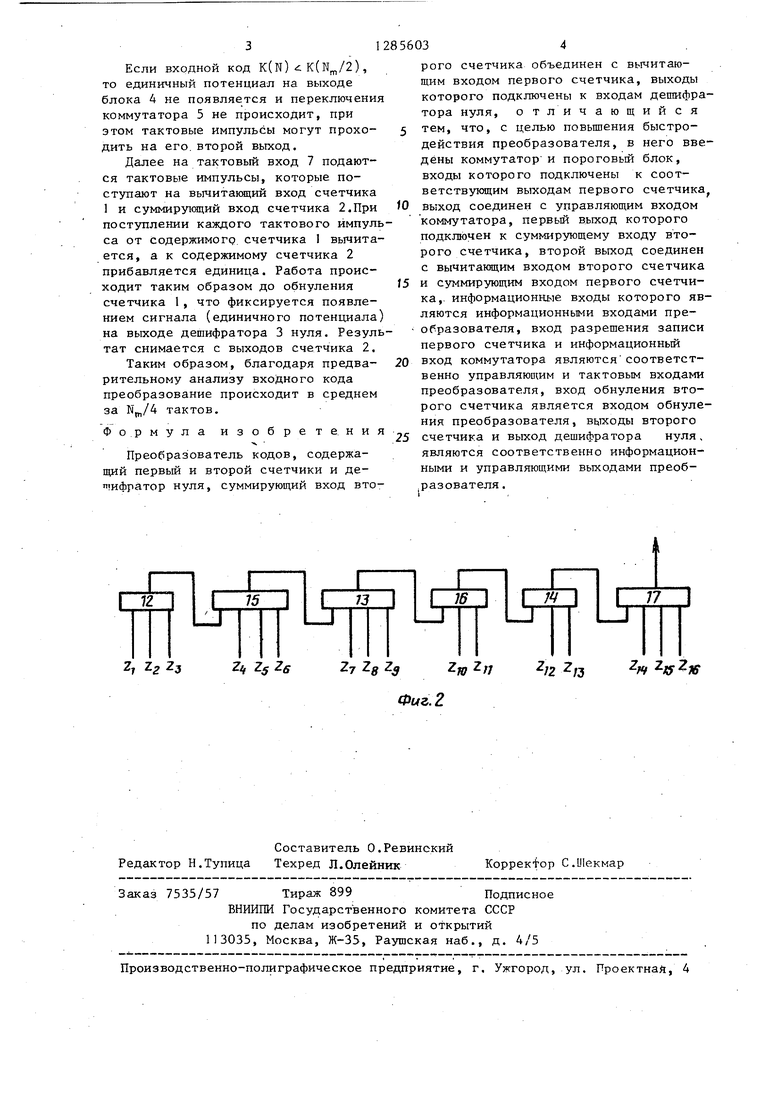

На фиг, 1 изображена функциональная схема преобразователя; на фиг,2- принципиальная схема порогового блока для конкретного примера.

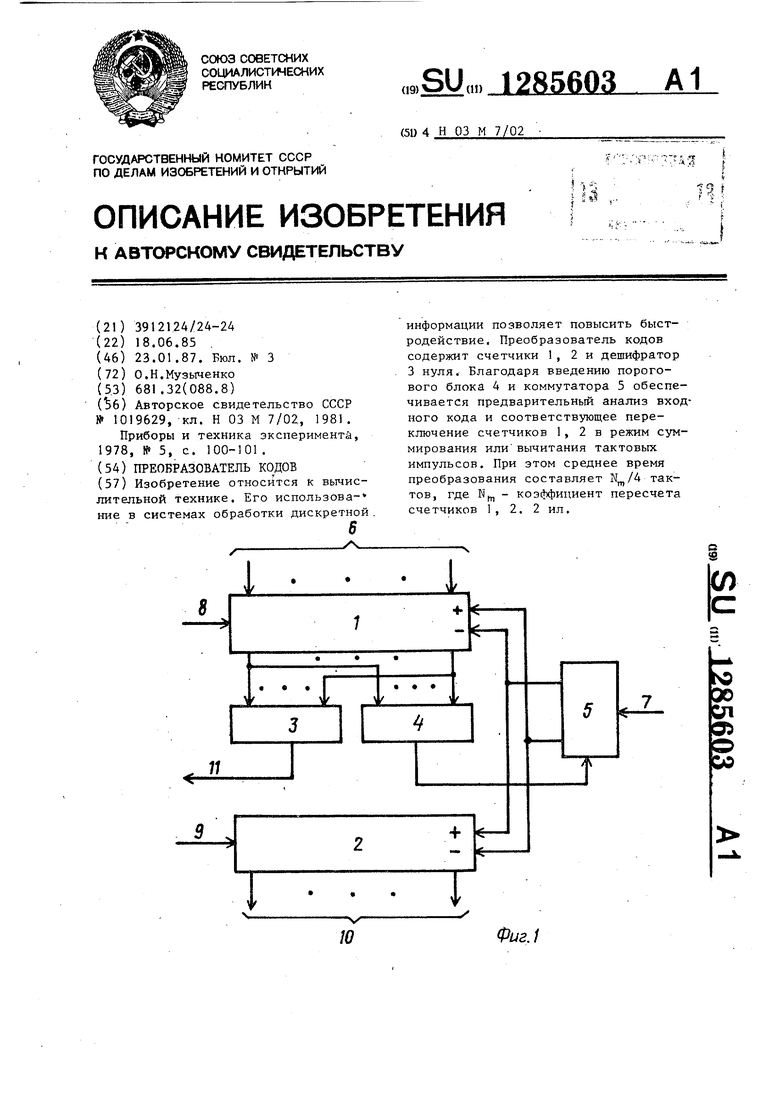

Преобразователь кодов содержит первый 1 и второй 2 счетчики, дешифратор 3 Нуля, пороговый блок 4 и коммутатор 5, Кроме того, обозначены (фиг, 1) информационные входы 6, тактовый вход 7, управляюций вход 8, вход 9 обнуления, информационные ввмоды 10 и управляющий выход 11,

Первый счетчик 1 - реверсивный счетчик работаювдай во входном коде, Второй счетчик 2 также реверсивный счетчик, работающий в выходном коде и имеющий коэффициент N пересчета, равный коэффициенту пересчета первого счетчика 1,

Пороговый блок 4 предназначен для выдачи сигнала при превы1 ении входным кодом K(N), где; N : , величины порога а этого блока. Наиболее целесообразно выбрать а равным .двоично-

му эквиваленту кода К(-), Пороговый

.блок 4 может быть вьшолнен, например следующим образом.

Пусть двоичное представление по- рога а имеет вид:

о . е-2 м

,. 2 +.,.., 2 + +Ые„2Ч,. .+ci;,,24(. 4.oi.,...+

ПустьЫ, oi, . .oiie-i 0. Входы ело- ка, начиная с-1-го и. до j-ro, таких ЧТОСУ: 0(;е, , , , (v;j l , aQ;j,,0, соединены с входами элемента И, выход которого, а также входы блока, начиная с (j+l)-ro и до i-ro, таких, что ) 0 aoi;t, l, соединены с входами элемента ИЛИ, выход кото- рого, а также входы блока, начиная с (i + l)-ro и кончая входом с номером t таких, чтоо;;, йi., ,.. , а oi, 0, соединены с входами элемента И и т.д. до объединения всех остальных входов блока, Ёслис „ 1, то последним является элемент И, а если 0/(,-0, то последним является элемент ИЛИ. Выход элемента, с входом которого соединен п-й вход с весом 2 блока, -является его выходом.

В частном случае, когда (d -О,1,2,,,.), блок анализа входного кода состоит из элемента ИЛИ, соединенного входами с входами блока, начиная с d+1-го до п-го. В частном случае, когдаЫ 0.;,, , . . 1 ,блок анализа входного кода состоит из элемента И, соединенного входами с входами блока от d-ro до п-го. В частном случае, когда , блок анализа вьшолняется в виде линии связи с его п-го входа на выход.

Для случая 16-разрядного входного кода и порога 1 100 1 1000 1 1 100 пороговый блок 4 может быть выполнен (фиг. 2) на элементах 1-ШИ 12- Н и элементах И 15-17,

Преобразователь кодов функционирует следующим образом.

В исходном состоянии счетчик 2 сброшен и на его выходах имеется кодовая комбинация, соответствутошая нулю. Коммутатор 5 находится в состоянии, когда прохождение тактовых импульсов разретено на его второй выход. Установка счетчика 2 производится путем подачи сигнала на вход 9.

Перед началом работы на информационные входы 6 подается входной код, одновременно на управляющий вх 8 подается сигнал разрешения записи и код записывается в счетчик 1. При этом он поступает на входы порогового блока 4. Если входной код К(К) 5: K(), где К - максимальное значение числа, представленного во входном коде, то на выходе блока 4,появляется сигнал (единичиь1Й потенциал), который поступает на управляющий вход коммутатора 5, пере- ключая его в состояние, при котором тактовые импульсы могут проходить на его первый выход.

Далее на тактовый вход 7 подаютс тактовые импульсы, которые поступают на суммируюЕ ий вход счетчика 1. и вычитающий вход счетчика 2. При по- .ступлении каждого тактового импульс к содержимому счетчика 1 - прибавляется, а от содержимого счетчика 2 вычитается единица. Работа происходит таким образом до обнуления счетчика 1, что фиксируется появлением единичного потенциала на выходе дешифратора 3 нуля, после чего результат преобразования сниматвтся с выходов 10.

3

Если входной код K(N) с K(), то единичный потенциал на выходе блока 4 не появляется и переключени коммутатора 5 не происходит, при этом тактовые импульсы могут проходить на его. второй выход.

Далее на тактовый вход 7 подаются тактовые импульсы, которые поступают на вычитакмций вход счетчика 1 и суммирукщий вход счетчика 2.При поступлении каждого тактового импулса от содержимого счетчика I вычитается, а к содержимому счетчика 2 прибавляется единица. Работа происходит таким образом до обнуления счетчика 1, что фиксируется появлением сигнала (единичного потенциала на выходе дешифратора 3 нуля. Резултат снимается с выходов счетчика 2.

Таким образом, благодаря предварительному анализу входного кода преобразование происходит в среднем за тактов.

Формула изобретени

Преобразователь кодов, содержащий первый и второй счетчики и де- п ифратор нуля, суммирующий вход втоП2П

г 73 -

2 2 2з21,2 26ZjZgZgZ Z/7 /2 /3 W

Фиг. 2

Составитель О.Ревинский Редактор Н.Тупица Техред Л.Олейник

Заказ 7535/57 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектнай, 4

fO

J5

20

25

рого счетчика объединен с вычитающим входом первого счетчика, выходы которого подключены к входам дешифратора нуля, отличающийся тем, что, с целью повышения быстродействия преобразователя, в него введены коммутатор и пороговый блок, входы которого подключены к соответствующим выходам первого счетчика, выход соединен с управляющим входом коммутатора, первый выход которого подключен к суммирующему входу второго счетчика, второй выход соединен с вычитающим входом второго счетчика и суммирующим входом первого счетчика,, информационные входы которого являются информационными входами преобразователя, вход разрешения записи первого счетчика и информационный вход коммутатора являются соответственно управляющим и тактовым входами преобразователя, вход обнуления второго счетчика является входом обнуления преобразователя, вьтходы второго счетчика и выход дешифратора нуля, являются соответственно информационными и управляющими выходами преобразователя.

П

I. 7 .{

KoppeKfop С.и1екмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1986 |

|

SU1361723A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Устройство для сортировки | 1989 |

|

SU1661756A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

Изобретение относится к вычислительной технике. Его использова- ние в системах обработки дискретной 6 / п V W информации позволяет повысить быстродействие. Преобразователь кодов содержит счетчики 1, 2 и дешифратор 3 нуля. Благодаря введению порогового блока 4 и коммутатора 5 обеспечивается предварительный анализ входного кода и соответствующее переключение счетчиков 1, 2 в режим суммирования или вычитания тактовых импульсов. При этом среднее время преобразования составляет тактов, где Nf - коэффициент пересчета счетчиков 1, 2. 2 ил. 1 I (Л у V Фиг.1

Авторы

Даты

1987-01-23—Публикация

1985-06-18—Подача