(61)1277370

(21)4130122/24-21

(22)08.10.86

(46)07.04.88. Бюл. № 13

(72)О. Н. Музыченко

(53)621.374(088.8)

(56)Авторское свидетельство СССР № 1277370, кл. Н 03 К 5/24, 1986.

(54)ПОРОГОВЫЙ ЭЛЕМЕНТ

(57)Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении различных устройств обработки дискретной информации. Изобретение позволяет повысить быстродействие порогового элемента, выполненного по предложенной схеме. ПорогоJ7

4 элемент содержит генератор 1 тактовых импульсов, сканирующий мультиплексор 2, содержащий триггер 3, многоканальный преобразователь 4 параллельного кода в последовательный, элемент ИЛИ 5, РО-1 реверсив- ных накопителей 6-1,...,6-(Ро-1), группу РО-1 элементов И 7-1,...,7-(Ро-1), К блоков реверсивных накопителей 8-1,...,8-К, выходной блок 9, счетный блок 10. Выходной блок 9 содержит элемент ИЛИ 11 и элемент И 12. Каждый блок реверсивных накопителей содержит элемент ИЛИ 13, реверсивные накопители 14-1,..., М-Р/, группу элементов И 15-1,...,15-Р/. На чертеже также показаны входные информационные шины 16, выход 17 порогового элемента, выход 18 элемента И 12, 1 з.п. ф-лы, 2 ил.

д

jz 18

€

(/

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1984 |

|

SU1277370A1 |

| Устройство для контроля равновесного кода К из @ | 1987 |

|

SU1559411A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

И-И;--- 16-1 1б

t ---tt

6-Po iB-fpo- i iS-fpo p,} (DU2.f

t ---tt

-fpo- i iS-fpo p,} (DU2.f

16-(Н} i

N

Изобретение относится к автоматике и вычислительной технике, может быть использовано для построения различных устройств обработки дискретной информации и является усовершенствованием изобретения по авт. св. № 1277370.

Цель изобретения - повышение быстродействия порогового элемента.

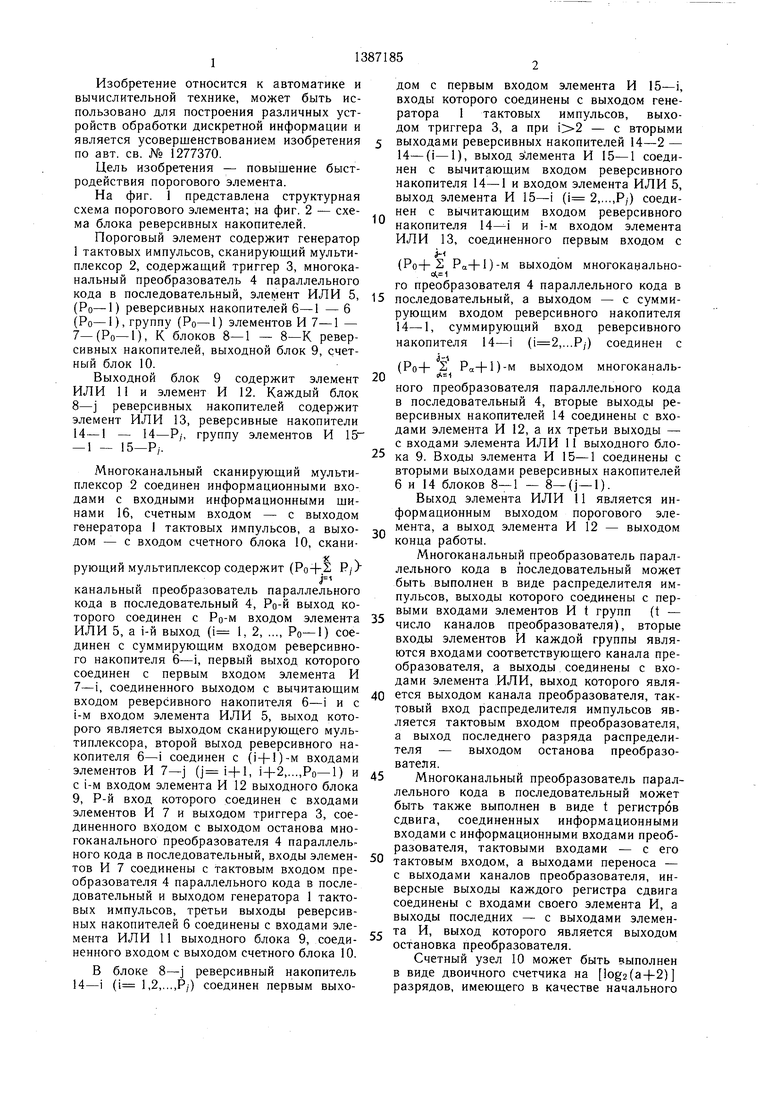

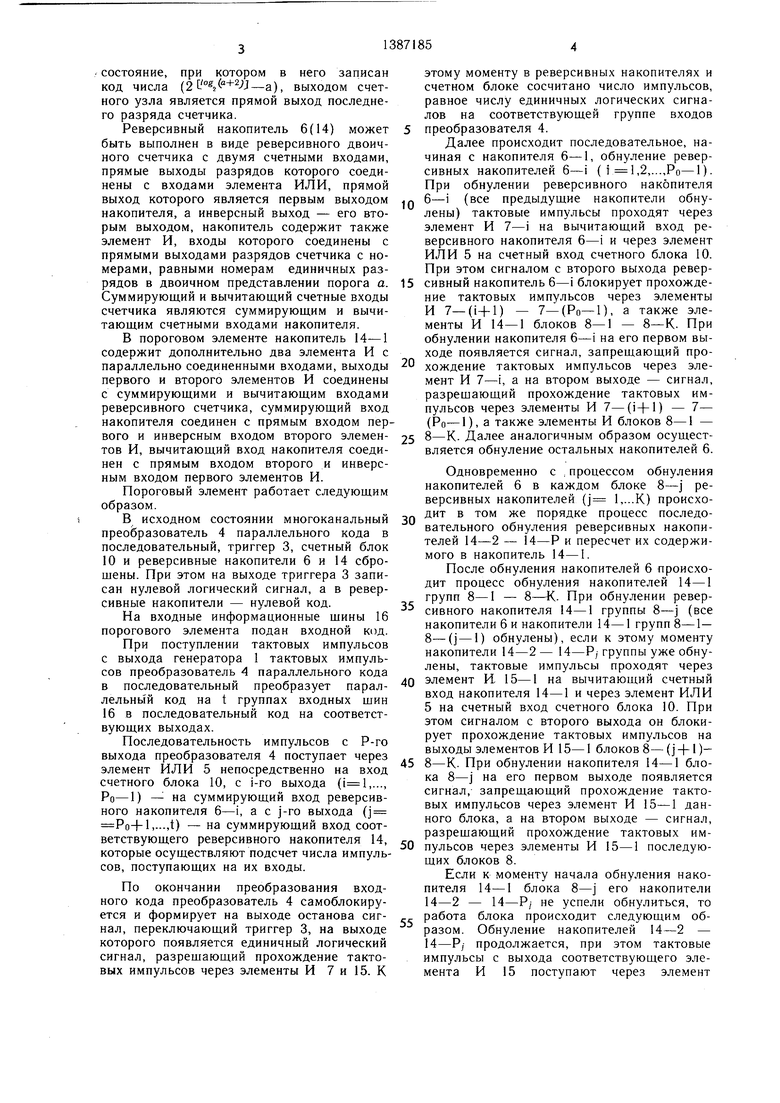

На фиг. 1 представлена структурная схема порогового элемента; на фиг. 2 - схема блока реверсивных накопителей.

Пороговый элемент содержит генератор 1 тактовых импульсов, сканируюший мультиплексор 2, содержащий триггер 3, многоканальный преобразователь 4 параллельного кода в последовательный, элемент ИЛИ 5, (Ро-1) реверсивных накопителей 6-1 - 6 (Ро- 1), группу (РО- 1) элементов И 7- 1 - 7-(Ро-1), К блоков 8-1 - 8-К реверсивных накопителей, выходной блок 9, счетный блок 10.

Выходной блок 9 содержит элемент ИЛИ II и элемент И 12. Каждый блок 8-j реверсивных накопителей содержит элемент ИЛИ 13, реверсивные накопители 14-1 - 14-Ру, группу элементов И IS - 1 - 15-Р/.

Многоканальный сканируюш.ий мультиплексор 2 соединен информационными входами с входными информационными шинами 16, счетным входом - с выходом генератора 1 тактовых импульсов, а выходом - с входом счетного блока 10, сканирующий мультиплексор содержит (Po-fS Р/)

канальный преобразователь параллельного

кода в последовательный 4, РО-Й выход которого соединен с РО-М входом элемента ИЛИ 5, а i-й выход (i 1, 2, ..., РО-1) соединен с суммируюш,им входом реверсивного накопителя 6-i, первый выход которого соединен с первым входом элемента И 7-i, соединенного выходом с вычитающим входом реверсивного накопителя 6-i и с i-M входом элемента ИЛИ 5, выход которого является выходом сканирующего мультиплексора, второй выход реверсивного накопителя 6-i соединен с (i-f-l)-M входами элементов И 7-j (j i+l, i-|-2,...,Po-1) и с i-M входом элемента И 12 выходного блока 9, Р-й вход которого соединен с входами элементов И 7 и выходом триггера 3, соединенного входом с выходом останова многоканального преобразователя 4 параллельного кода в последовательный, входы элементов И 7 соединены с тактовым входом преобразователя 4 параллельного кода в последовательный и выходом генератора 1 тактовых импульсов, третьи выходы реверсивных накопителей 6 соединены с входами элемента ИЛИ 11 выходного блока 9, соединенного входом с выходом счетного блока 10.

В блоке 8-j реверсивный накопитель 14-i (i 1,2,...,Р/) соединен первым выхо0

дом с первым входом элемента И 15-i, входы которого соединены с выходом генератора 1 тактовых импульсов, выходом триггера 3, а при - с вторыми выходами реверсивных накопителей 14-2 - 14-(i-1), выход э лемента И 15-1 соединен с вычитающим входом реверсивного накопителя 14-1 и входом элемента ИЛИ 5, выход элемента И 15-i (i 2Р/) соединен с вычитающим входом реверсивного накопителя и i-м входом элемента ИЛИ 13, соединенного первым входом с

i- (Ро+2 Ра+1)-м ВЫХОДОМ многоканально0 1

го преобразователя 4 параллельного кода в 5 последовательный, а выходом - с суммирующим входом реверсивного накопителя 14-1, суммирующий вход реверсивного накопителя 14-i (,...P/) соединен с

( 2 )-ivi выходом многоканальсЛг1

ного преобразователя параллельного кода в последовательный 4, вторые выходы реверсивных накопителей 14 соединены с входами элемента И 12, а их третьи выходы - с входами элемента ИЛИ 11 выходного бло5 ка 9. Входы элемента И 15-1 соединены с вторыми выходами реверсивных накопителей 6 и 14 блоков 8-1 - 8-(j-1).

Выход элемента ИЛИ 1 является информационным выходом порогового элемента, а выход элемента И 12 - выходом конца работы.

Многоканальный преобразователь параллельного кода в последовательный может быть выполнен в виде распределителя импульсов, выходы которого соединены с первыми входами элементов И t групп (t - число каналов преобразователя), вторые входы элементов И каждой группы являются входами соответствующего канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которого явля0 ется выходом канала преобразователя, тактовый вход распределителя импульсов является тактовым входом преобразователя, а выход последнего разряда распределителя - выходом останова преобразователя.

5 Многоканальный преобразователь параллельного кода в последовательный может быть также выполнен в виде t регистров сдвига, соединенных информационными входами с информационными входами преобразователя, тактовыми входами - с его

0 тактовым входом, а выходами переноса - с выходами каналов преобразователя, инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с выходами элеменг та И, выход которого является выходом остановка преобразователя.

Счетный узел 10 может быть выполнен в виде двоичного счетчика на log2(a-|-2) разрядов, имеющего в качестве начального

0

состояние, при котором в него записан код числа (( +2Л-а), выходом счетного узла является прямой выход последнего разряда счетчика.

Реверсивный накопитель 6(14) может быть выполнен в виде реверсивного двоичного счетчика с двумя счетными входами, прямые выходы разрядов которого соединены с входами элемента ИЛИ, прямой выход которого является первым выходом накопителя, а инверсный выход - его вторым выходом, накопитель содержит также элемент И, входы которого соединены с прямыми выходами разрядов счетчика с номерами, равными номерам единичных разрядов в двоичном представлении порога а. Суммирующий и вычитающий счетные входы счетчика являются суммирующим и вычитающим счетными входами накопителя.

В пороговом элементе накопитель 14-1 содержит дополнительно два элемента И с параллельно соединенными входами, выходы первого и второго элементов И соединены с суммирующими и вычитающим входами реверсивного счетчика, суммирующий вход накопителя соединен с прямым входом первого и инверсным входом второго элементов И, вычитающий вход накопителя соединен с прямым входом второго и инверсным входом первого элементов И.

Пороговый элемент работает следующим образом.

В исходном состоянии многоканальный преобразователь 4 параллельного кода в последовательный, триггер 3, счетный блок 10 и реверсивные накопители 6 и 14 сброшены. При этом на выходе триггера 3 записан нулевой логический сигнал, а в реверсивные накопители - нулевой код.

На входные информационные щины 16 порогового элемента подан входной код.

При поступлении тактовых импульсов с выхода генератора 1 тактовых импульсов преобразователь 4 параллельного кода в последовательный преобразует парал- лельньж код на t группах входных шин 16 в последовательный код на соответствующих выходах.

Последовательность импульсов с Р-го выхода преобразователя 4 поступает через элемент ИЛИ 5 непосредственно на вход счетного блока 10, с i-ro выхода (,..., РО-1) - на суммирующий вход реверсивного накопителя 6-i, а с j-ro выхода (j Po-bl,...,t) - на суммирующий вход соответствующего реверсивного накопителя 14, которые осуществляют подсчет числа импульсов, поступающих на их входы.

По окончании преобразования входного кода преобразователь 4 самоблокируется и формирует на выходе останова сигнал, переключающий триггер 3, на выходе которого появляется единичный логический сигнал, разрешающий прохождение тактовых импульсов через элементы И 7 и 15. К

этому моменту в реверсивных накопителях и счетном блоке сосчитано число импульсов, равное числу единичных логических сигналов на соответствующей группе входов

преобразователя 4.

Далее происходит последовательное, начиная с накопителя 6-1, обнуление реверсивных накопителей 6-i ( i 1,2,...,Ро-1). При обнулении реверсивного накопителя

6-i (все предыдущие накопители обнулены) тактовые импульсы проходят через элемент И 7-i на вычитающий вход реверсивного накопителя 6-i и через элемент ИЛИ 5 на счетный вход счетного блока 10. При этом сигналом с второго выхода ревер5 сивный накопитель 6-i блокирует прохождение тактовых импульсов через элементы И 7-(i+1) - 7-(Ро-1), а также элементы И 14-1 блоков 8-1 - 8-К. При обнулении накопителя 6-i на его первом выходе появляется сигнал, запрещающий про хождение тактовых импульсов через элемент И 7-i, а на втором выходе - сигнал, разрешающий прохождение тактовых импульсов через элементы И 7-(i+1) - 7- (Ро-1), а также элементы И блоков 8-1 -

5 8-К. Далее аналогичным образом осуществляется обнуление остальных накопителей 6.

Одновременно с , процессом обнуления накопителей 6 в каждом блоке 8-j реверсивных накопителей (j 1,...К) происходит в том же порядке процесс последовательного обнуления реверсивных накопителей 14-2 - 14-Р и пересчет их содержимого в накопитель 14-I.

После обнуления накопителей 6 происходит процесс обнуления накопителей 14-1 групп 8-1 - 8-К. При обнулении ревер сивного накопителя 14-1 группы 8-j (все накопители 6 и накопители 14-1 групп 8-1- 8-(j - 1) обнулены), если к этому моменту накопители 14-2 - 14-Р/ группы уже обнулены, тактовые импульсы проходят через

0 элемент И 15-1 на вычитающий счетный вход накопителя 14-1 и через элемент ИЛИ 5 на счетный вход счетного блока 10. При этом сигналом с второго выхода он блокирует прохождение тактовых импульсов на выходы элементов И 15- 1 блоков 8- (j +1 )-

5 8-К. При обнулении накопителя 14-1 блока 8-j на его первом выходе появляется сигнал, запрещающий прохождение тактовых импульсов через элемент И 15-1 данного блока, а на втором выходе - сигнал, разрещающий прохождение тактовых им0 пульсов через элементы И 15-1 последующих блоков 8.

Если к моменту начала обнуления накопителя 14-1 блока 8-j его накопители 14-2 - 14-Р/ не успели обнулиться, то

работа блока происходит следующим образом. Обнуление накопителей 14-2 - 14-PJ продолжается, при этом тактовые импульсы с выхода соответствующего элемента И 15 поступают через элемент

ИЛИ 13 на суммирующий вход накопителя 14-1, одновременно тактовые импульсы проходят через элемент И 15-I на вычитающий вход накопителя 14-1 и через элемент ИЛИ 5 - на счетный вход счетного узла 10. При этом состояния накопителя 14-1 не меняются. Работа продолжается таким образом до обнуления накопителей 14-2 - 14-Р/, после чего оканчивается процесс обнуления накопителя 14-1 в описанном порядке.

Таким образом происходит последовательное обнуление накопителей 14.1 блоков 8-1 - 8-К.

Если во входном коде число единиц меньще порога а, то работа устройства продолжается до обнуления всех накопителей 6 и 14, при этом на выходе 18 элемента И 12 выходного блока 9 формируется единичный сигнал, свидетельствующий об окончании цикла работы, и с выхода 17 элемента ИЛИ 11 выходного блока 9 снимается нулевой сигнал.

Если во входном коде число единиц больше или равно а, а во всех группах входов, соответствующих накопителям одного блока 8, число единиц меньше а, то работа устройства продолжается до накопления в счетном блоке 10 а импульсов, при этом на его выходе появляется единичный сигнал, проходящий через элемент ИЛИ 11 на выход 17 устройства и свидетельствующий об окончании работы.

Если в какой-либо группе входов, соответствующей накопителям одного блока 8, число единиц больше или равно а и до начала обнуления накопителя 14-1 в нем успевает накопиться а импульсов, то на его третьем выходе появляется единичный сигнал, поступающий через элемент ИЛИ 11 на выход-17 устройства и свидетельствующий об окончании работы.

Если в какой-либо подгруппе входов 16-1 число единиц больше или равно а, то в момент накопления в соответствующем накопителе а импульсов на его третьем выходе появляется единичный сигнал, проходящий через элемент ИЛИ 11 на выход 17 устройства и свидетельствующий об окончании работы.

Если входы элемента И 15-1 блока 8-j соединены с вторыми выходами накопителей 14-2 - 14-Р/, то к моменту начала обнуления йакопителя 14-1 блока 8-j накопители 14-2- 14-Р/данного блока не успели обнулиться. при этом они сигналами со своих вторых выходов блокируют прохождение тактовых импульсов через элемент И 15-1 и процесс обнуления накопителя 14-1 не начинается до момента обнуления накопителей 14-2 - 14-Р/.

Формула изобретения

0 повышения быстродействия, в сканирующий мультиплексор введены блоков реверсивных накопителей, каждый из которых содержит (j 1,...,К) реверсивных накопителей, Р/ элементов И и элемент ИЛИ, причем второй выход i-ro реверсивного накопителя j-ro блока (i 1,...,Р,) соединен с входом элемента И выходного блока, первый выход - с первым входом i-ro элемента И, второй и третий входы которого соединены с выходами генератора тактовых импуль0 сов и триггера, выход первого элемента И соединен с входом элемента ИЛИ и вычитающим входом первого реверсивного накопителя, выход i-ro элемента И (,....,P/) соединен с вычитающим входом i-ro реверсивного накопителя и i-м входом элемента

5 ИЛИ j-ro блока, первый вход которого

J-1

соединен с ( Е )-м выходом многоканального преобразователя параллельного кода в последовательный, а выход - с сум- 0 мирующим входом первого реверсивного накопителя блока, суммирующий вход i-ro реверсивного накопителя соединенс

(Р4- 2 Pt-{-)-M выходом многоканального

1

преобразователя параллельного кода в последовательный, входы i-ro элемента И (i 3,...,Ру) блока реверсивных накопителей соединены с вторыми выходами реверсивных накопителей от второго до (i-1)- го блока, а входы первого элемента И - с

вторыми выходами реверсивных накопителей блоков от первого до (j - 1)-го и выходами реверсивных накопителей от первого до (Р-1)-го, входы элемента ИЛИ выходного блока соединены с третьими выходами реверсивных накопителей блоков от первого до К-го.

СЧ1 Ct

Авторы

Даты

1988-04-07—Публикация

1986-10-08—Подача